# Materials Advances

**Accepted Manuscript**

This article can be cited before page numbers have been issued, to do this please use: A. Ciupa, *Mater. Adv.*, 2025, DOI: 10.1039/D5MA01267H.

This is an Accepted Manuscript, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about Accepted Manuscripts in the <u>Information for Authors</u>.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this Accepted Manuscript or any consequences arising from the use of any information it contains.

View Article Online DOI: 10.1039/D5MA01267H

aterials Advances Accepted Manuscrip

### **ARTICLE**

## Assembling a molecular computer: challenges in integrating molecular logic, memory, and interconnects from the "bottom-up"

Received 00th January 20xx, Accepted 00th January 20xx

DOI: 10.1039/x0xx00000x

Alexander Ciupa\*

The advancement of high-performance computing is unlocking the potential of artificial intelligence and machine learning, providing significant benefits to everyday life. Miniaturization of silicon-based transistors is enabling this transformation; however, challenges such as quantum tunneling, contact resistance, and excess power consumption are significant obstacles as we approach the 5 nm limit. Molecular electronics, which replicates the function of electronic components with single molecules, offers an attractive alternative, with the molecular-scale representing the final frontier in miniaturization. Recent progress in molecular logic gates, memory units, and interconnects underscores the potential of molecular electronics to mitigate the excessive power consumption and heat generation associated with current technology. While significant progress has been made, the integration of separate components into functional devices remains limited. This review outlines the challenges of assembling molecular components within a von Neumann architecture. We discuss current challenges, highlighting successful molecular electronic case studies, and then conclude with five milestones to be reached on the journey towards the world's first functional molecular computer.

#### Introduction

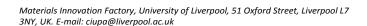

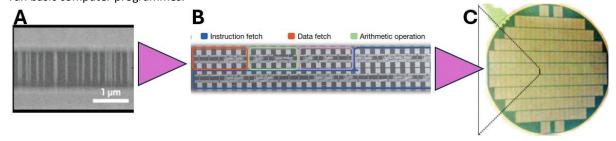

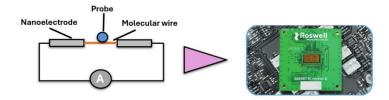

Continual advances in computational technology are fuelling artificial intelligence (AI) and machine learning (ML), which are benefitting society.<sup>1,2</sup> The miniaturization of silicon-based transistors is enabling this transformation with state-of-the-art integrated circuits (ICs) containing billions of transistors approaching 5 nm.3 This trend has historically followed Moore's first law: the number of transistors on a IC doubles approximately every two years.4 Sustaining this progress required increasingly sophisticated fabrication technologies, with the construction of leading-edge fabrication facilities now exceeding \$25 billion.5 Alongside the financial cost of silicon transistor miniaturization, fundamental scientific limitations are becoming apparent. Phenomena such as quantum tunnelling,6 high contact resistance,7 excessive power consumption,8 and heat dissipation9 present formidable challenges. IC demand often outstrips supply with approx. 75% of global manufacturing centred in Asia. 10 This production bottleneck is intensifying political tensions as nations compete for these critical resources. The recent CHIPS Act in the United States of America and the European Chips Act are leading examples. 11,12 We are approaching a computing crossroad requiring research into alternative computing paradigms (Fig. 1A). Quantum computing, which leverages qubits (quantum bits) for computation, has promise in cryptography<sup>13</sup> and niche applications, yet its complex instrumentation and cryogenic operating temperatures limit widespread use.

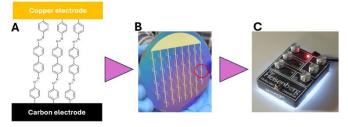

**Fig. 1** The approaching computing crossroad (panel A), electronic component miniaturisation (panel B), and the rise in molecular electronics reported in the literature (panel C).

**Journal Name**

Photonic computing, which utilizes light for computation, is providing advances to datacentres,14 however, the storage of data as photons is limited, and complex fabrication limits mass production.<sup>15</sup> Miniaturization of electronic components underpinned previous advances (Fig. 1B) with molecular electronics, in which individual molecules replicate the function of electronic components, a promising third alternative. 16 First explored in the 1970s, molecular electronics has experienced a resurgence over the past five years (Fig. 1C), with major progress in molecular logic gates, memory elements, and interconnects.<sup>17</sup> This "bottom-up" approach was first envisioned by Richard Feynman in his seminal 1959 lecture "There's plenty of room at the bottom." 18 The assembly of functional molecular electronic devices is now possible with several recent case studies highlighted within. While numerous reviews<sup>19</sup> have discussed individual molecular components, this review specifically outlines challenges on the road towards developing the world's first molecular computer. We discuss the current von Neumann architecture underpinning current computers<sup>20</sup> and discuss how molecular electronics can replicate and improve upon this design. We highlight recent molecular electronic commercial successes to demonstrate that progress is achievable. We conclude with five key milestones on the road towards constructing a fully functional molecular

#### The von Neumann architecture

This article is licensed under a Creative Commons Attribution 3.0 Unported Licence.

Open Access Article. Published on 27 Novemba 2025. Downloaded on 02/12/2025 10:24:46.

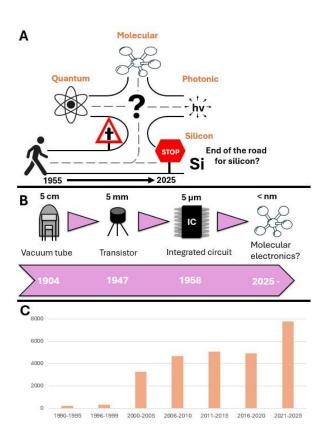

John von Neumann (1903-1957) transformed a variety of scientific fields, including the development of ENIAC (electronic numerical integrator and computer), the world's first general-purpose computer.<sup>20</sup> John von Neumann would later outline a blueprint for modern computers referred to as the von Neumann architecture (Fig. 2A).<sup>21</sup>

**Fig. 2** The von Neumann architecture upon which all modern computers operate (panel A) and the five functions to be replicated with molecular electronics (panel B).

This design involved a control unit that can fetch program instructions from a separate memory component, perform logic operations, and then store the resulting data in a separate part of the memory. A critical feature of this design is the programmability of the memory unit, which allows the installation of new programs or modifications to existing ones, enabling true general-purpose computing. A variety of INPUT/OUTPUT devices issue commands and observe results, while a central control unit coordinates operations and data transfers via a network of interconnects. Although this architecture has served as the backbone of computing for more than 70 years, the most advanced ICs reveal major limitations with this approach. First, the control unit executes tasks sequentially: it must fetch instructions from memory before performing the next operation, such as a logical computation. This sequential process has become a significant bottleneck, with even the most advanced ICs frequently left idle while waiting for instructions and data transfers. This limitation is known as the von Neumann bottleneck.<sup>22</sup> Second, the transfer of data from memory occurs more slowly than the ICs execution speed, referred to as the memory wall.<sup>23</sup> This leads to wasted energy and excess heat generation. Future computing paradigms must avoid such pitfalls. Neuromorphic computing, which mimics brain-like functions by performing operations in parallel, is a leading example.24 For multiple molecular components to function as a cohesive unit, the five challenges (5Cs) in molecular computing must be considered.<sup>25</sup>

#### The five challenges (5Cs) in molecular computing

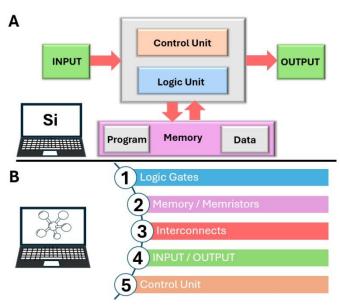

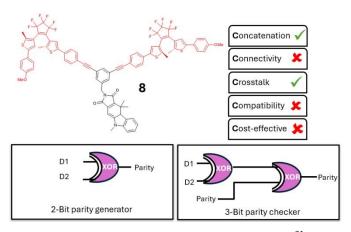

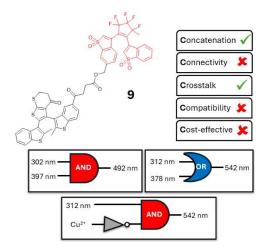

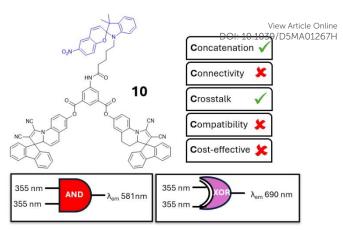

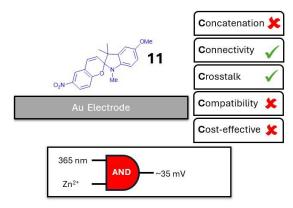

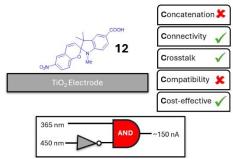

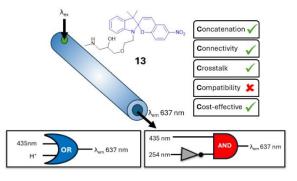

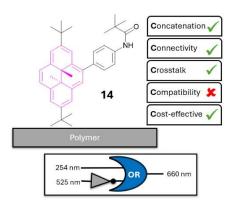

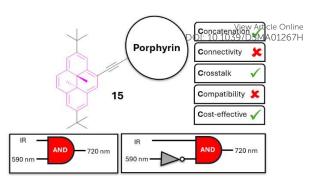

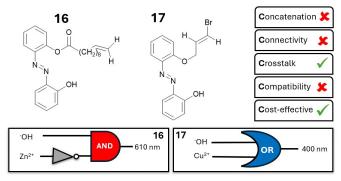

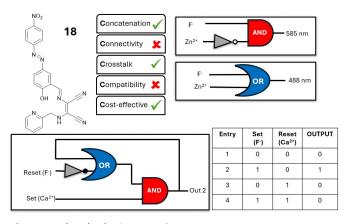

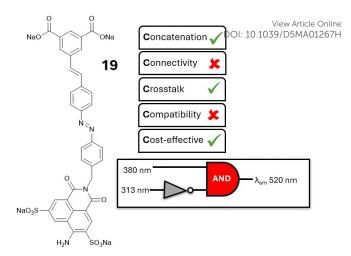

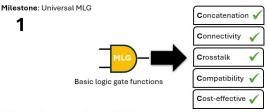

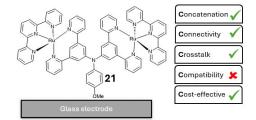

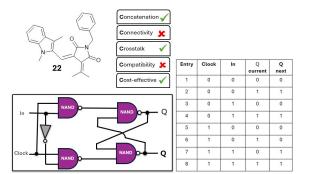

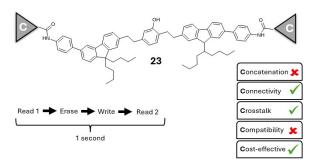

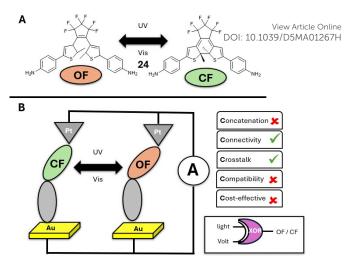

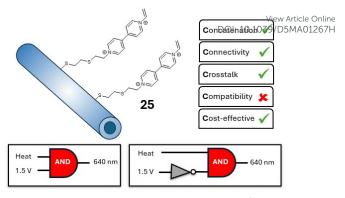

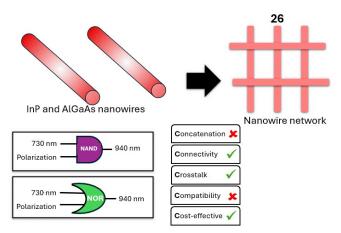

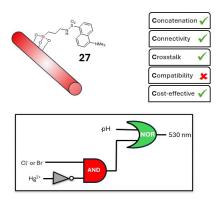

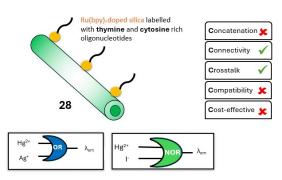

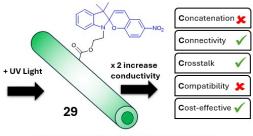

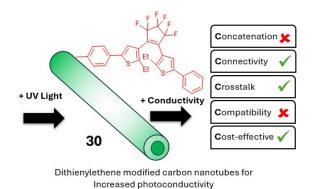

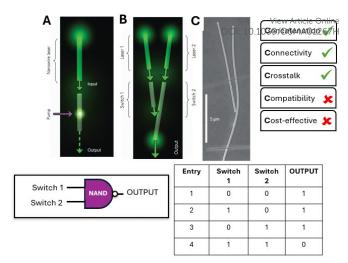

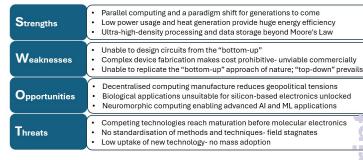

For molecular electronics to become a practical alternative to conventional electron-based electronics, five key challenges collectively known as the 5Cs must be addressed (Fig. 3).25 To replicate the function of silicon-based components, multiple molecular units must operate together as a coordinated system. The connection of these units, known as concatenation, is essential. To pass this challenge, the ability of two or more logic gates functioning together must be clearly demonstrated. The second challenge, connectivity, concerns the transition from solution-phase operation to substrate-bound architectures, enabling complex device fabrication. The chemical attachment of logic gates to at least one surface must be confirmed to meet this objective. Crosstalk refers to unintended signal interference with neighbouring units, which must be minimised. To achieve this challenge, the reported system must operate with clear ON/OFF signals, demonstrating robust, and repeatable operation.

Fig. 3 The five challenges (5Cs) in molecular computing.

Open Access Article. Published on 27 Novemba 2025. Downloaded on 02/12/2025 10:24:46.

**ARTICLE**

Journal Name

Compatibility emphasizes the need for integration with existing electronic technologies. A hybrid era is highly likely, where molecular electronics coexists with conventional approaches—much as photonic integrated circuits (PICs) are already augmenting data centres today. <sup>26</sup> To satisfy this challenge, the reported system must be integrated with existing electronics. The final challenge is cost-effective manufacturing to ensure widespread adoption of the new technology. The use of efficient syntheses using inexpensive reagents and substrates, for example widely available industrial feedstocks, would meet

this challenge. Future molecular electronics should be designed

to be 5C compliant, and we will evaluate current approaches

#### Molecular logic gates

against these metrics.

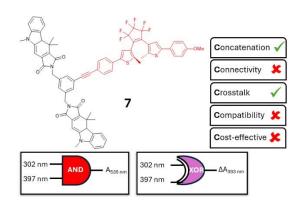

The central feature of any computer is the ability to perform complex operations via the logic unit. This often takes the form of logic gates, of which there are several basic gate designs (Fig. 4).27 These can be combined and assembled into a multitude of configurations to perform the desired tasks, for example, arithmetic. The algebraic logic underpinning these gates was first devised by George Boole in 1847, with each gate described  $\emph{via}$  a truth table.  $^{17c}$  The first molecular logic gate reported by de Silva et al. in 1993 was an AND gate (1 in Fig. 4).28 Anthracenebased 1 only triggered an output if both INPUT 1 (H+) and 2 (Na+) are present. The OUTPUT is fluorescence emission ( $\lambda_{\text{em}}\!)$  at a wavelength of 475 nm. This is an example of a metal-triggered INPUT producing a fluorescence OUTPUT logic gate. The opposite of an AND gate is a NAND (not AND) gate in which any combination of INPUT except both 1 and 2 INPUT together triggers an OUTPUT. Gunnlaugsson et al. reported the first NAND gate in 2000 with Ca2+ and Mg2+ as INPUT 1 and 2, respectively (2 in Fig. 4).29 Numerous other logic gates (3-6, Fig. 4) have been reported, with the majority triggering a fluorescent OUTPUT in the presence of metal INPUT. These examples confirm that molecules can replicate logic gates. In traditional silicon-based logic gates, electrons are both INPUT and OUTPUT allowing the OUTPUT of one logic gate to serve as the INPUT of another, and so on. This facilitates the connection (concatenation) of multiple logic gates. For molecular logic gates to replicate this function, we require homogeneous INPUT and OUTPUT, with light a leading contender. An excellent example, 7, was reported by Andréasson et al. in 2011 based on two photochromes, dithienylethene and fulgimide (red and black units, respectively in Fig. 5).30 Up to 14 different logic gates were reported, performing arithmetic, multiplexing, and functioning as a molecular keypad lock. This system demonstrates concatenation as the OUTPUT from one logic gate serves as the INPUT for another, for example, a half-adder is composed of AND and XOR logic gates. This is a significant result demonstrating gate-to-gate communication without any physical connection highlighting the advantages fully photonic systems provide. Furthermore, the system can be reset using an optical signal, allowing the user to undo the previous operation and reconfigure the system for a different logical operation.

| Logic Gate       | INPUT<br>1                                                                          | INPUT<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OUTPUT                                               |

|------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                  | 0                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                    |

| 1 —              | 0                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                    |

| 2 — AND          | 1                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                    |

|                  | 1                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

| Logic Gate       | INPUT                                                                               | INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OUTPUT                                               |

|                  | 1                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

|                  | 0                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

| 1-NAND 0-        | 0                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

| 2— NAND          | 1                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

|                  | 1                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                    |

| Logic Gate       | INPUT                                                                               | INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OUTPUT                                               |

|                  | 1                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

|                  | 0                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                    |

| OR —             | 0                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

| 2                | _ 1                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

|                  | 1                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                    |

|                  | <u> </u>                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2000                                                 |

| Logic Gate       | INPUT                                                                               | INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ОИТРИТ                                               |

| Logic Gate       | INPUT<br>1                                                                          | INPUT<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ОИТРИТ                                               |

| Logic Gate       | INPUT<br>1                                                                          | <b>INPUT 2</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>OUTPUT</b><br>0                                   |

| Logic Gate       | INPUT<br>1<br>0                                                                     | 1NPUT 2 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0<br>1                                               |

| Logic Gate       | INPUT<br>1<br>0<br>0                                                                | INPUT 2 0 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0<br>1<br>1                                          |

| 1 XOR            | INPUT<br>1<br>0<br>0<br>1                                                           | INPUT 2 0 1 0 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0<br>1<br>1<br>0                                     |

| Logic Gate       | INPUT<br>1<br>0<br>0                                                                | INPUT 2 0 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0<br>1<br>1                                          |

| 1 XOR            | INPUT 1 0 0 1 1 1 INPUT                                                             | 0<br>1<br>0<br>1<br>INPUT<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0<br>1<br>1<br>0                                     |

| 1 XOR            | INPUT 1 0 0 1 1 INPUT 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         | INPUT 2 0 1 1 INPUT 2 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0<br>1<br>1<br>0<br>0<br>OUTPUT                      |

| 1 XOR Logic Gate | INPUT 1 0 0 1 1 1 INPUT 1 0 0                                                       | INPUT 2 0 1 1 INPUT 2 0 0 1 1 INPUT 2 0 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 1 1 0 OUTPUT 1 0 0                                 |

| 1 XOR Logic Gate | INPUT 1 0 0 1 1 INPUT 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         | INPUT 2 0 1 1 INPUT 2 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 1 1 0 OUTPUT                                       |