# Journal of Materials Chemistry C

**REVIEW**

**View Article Online**

Cite this: J. Mater. Chem. C, 2022, **10**, 13372

# Emerging polymer electrets for transistor-structured memory devices and artificial synapses

Ting-Wei Chang, Yun-Shan Li, Naoji Matsuhisa and Chien-Chung Shih \*

Polymer electrets have been widely explored as charge-storage elements in field-effect transistor memory and artificial synaptic devices because of their tailorable molecular structures and processability. Proper design of polymer electrets can enhance the charge injection efficiency and storage time, and the memory implementation can be switched from electrical to optical programming. We comprehensively review state-of-the-art polymer electrets for transistor-structured memory and artificial synapses. We classify the electrets into five types: (1) pendant polymer electrets, (2) block copolymer electrets, (3) conjugated polymer electrets, (4) hybrid polymer composites, and (5) ferroelectric polymer electrets. Their design concepts and working mechanisms are discussed in detail. This review may pave the way for the development of polymer-electret-based transistor memory devices and artificial synapses with unprecedented performance improvements.

Received 20th March 2022. Accepted 20th May 2022

DOI: 10.1039/d2tc01132h

rsc.li/materials-c

### 1. Introduction

Nonvolatile memory devices are widely used in applications such as displays, cellular phones, and computer systems. 1-8 These devices carry necessary data for the operation of modern electronics. With the development of lightweight, portable, and wearable electronics, the demand for flexible memory devices in integrated circuits has increased. For instance, diverse healthcare applications based on wearable devices are emerging. In particular, imperceptible sensor-laden devices with sophisticated layouts have been designed to continuously measure physiological parameters and coupled with data storage devices for advanced applications in personal healthcare. 9-12 In this case, high-performance local memory is required to store the buffer of feedback signals from the body in real time. Accordingly, interest has increased in organic memory devices owing to their intrinsic flexibility and solution processability on flexible and stretchable substrates with adjustable patterns for circuit integration. An objective of next-generation nonvolatile

Ting-Wei Chang

Ting-Wei Chang received bachelor's degree in the Department of Chemical and Materials Engineering from National Yunlin University of Science Technology (NYUST) in 2020. He then joined Dr Chien-Chung Shih's group for master program in 2021. His research focuses on the synthesis of conjugated polymers and their applications on organic field-effect transistors and memory devices.

Yun-Shan Li

Yun-Shan Li is currently undergraduate student in the Department of Chemical and Materials Engineering, National Yunlin University of Science and Technology (NYUST). She joined Dr Chien-Chung Shih's lab in the summer of 2021 for research. Her research focuses on stretchable and patternable micro-supercapacitors.

<sup>&</sup>lt;sup>a</sup> Department of Chemical Engineering and Materials Engineering, National Yunlin University of Science and Technology, Yunlin 64002, Taiwan. E-mail: shihcc@yuntech.edu.tw

<sup>&</sup>lt;sup>b</sup> Electronics and Electrical Engineering, Faculty of Science and Engineering, Keio University, Yokohama 223-8522, Japan

<sup>&</sup>lt;sup>c</sup> Institute of Industrial Science, The University of Tokyo, 4-6-1, Komaba, Tokyo 153-8505, Meguro-ku, Japan

memory devices is achieving ultrahigh-density storage to match the rapid development of the Internet of Things and the urgent demand for information storage in big data technologies. Nevertheless, real-world data generation outpaces storage capacity in digital technologies. 13,14

The continuous data exchange between a processor and memory device produces substantial delays and limits the computing speed and energy efficiency, in an effect commonly known as the von Neumann bottleneck. 15,16 Hence, advanced nonvolatile memory technologies are required to construct parallel and reconfigurable neural networks that can simultaneously process and store information, resembling the function of the human brain. The human brain is composed of approximately 1011 basic units called neurons, which are connected by approximately 10<sup>15</sup> links called synapses.<sup>17</sup> The transmission and processing of voltage pulse signals by synapses is the basis for cognitive and learning functions in the brain. Hardware implementation of synapses and neurons using emerging electronic devices is promising for braininspired computing. Moreover, the development of an electronic device with synaptic functions is essential for constructing neuromorphic computing systems.<sup>18</sup>

Synaptic transistors, which are transistor-structured memory devices with medium volatility, can emulate synapses. 19-22 Depending on their volatility, there are long and short-term memory devices. A synaptic transistor has long-term memory because it exhibits medium volatility and hysteresis under excitation of an external electric field for programming. The gate electrode in the transistor is generally considered as the preterminal that applies action potentials to the synapse, and the active channel that contacts the source/drain electrodes is considered as the post-stimulus. Then, the control of the channel by a presynaptic gate allows signal transmission and transient storage. A synaptic transistor can exhibit multilevel accessible conductance states by regulating multiple presynaptic inputs to obtain an analog-type response. Extensive research has

been devoted to developing synaptic transistors with high density, fast operation, low voltage, and operational reliability. In addition, applications such as electronic skins and implantable electronics require flexible synaptic transistors that are nontoxic, harmless, and biocompatible.23-25

Over the past two decades, new materials and device architectures have been proposed to address problems in organic memory devices. The device architecture mainly comprises a two-terminal resistive memory and three-terminal transistor memory.<sup>8,26</sup> A typical resistive memory device generally consists of two electrodes enclosing a switching layer for toggling between high and low resistances in response to an external voltage. Although resistive memory can provide high storage capacity, fast speed, short access time, and low power consumption, signal transmission and programming cannot be performed collectively, restricting its applicability for artificial synapses owing to the interfering learning and forgetting functions. On the other hand, three-terminal transistor memory, such as organic field-effect transistor (OFET) memory, can receive and read stimuli concurrently while showing similar advantages to resistive memory, being promising for integrated neuromorphic systems. This type of memory is considered as a new generation of portable high-density storage device owing to its flexibility, light weight, and compatibility with complementary logic circuits.13

OFET memory can be classified into three categories according to the charge-storage mechanism of the memory layer: (1) floating-gate OFET memory, 27,28 (2) polymer-electret-based OFET memory, 29,30 and (3) ferroelectric OFET memory. 31 Polymer electrets possess unique advantages, such as high mechanical strength, high flexibility, and processability.3 Thus, polymerelectret-based OFET memory devices are compatible for fabrication by solution processes including spin coating, dip coating, spray coating, and inkjet printing without requiring vacuum deposition. A polymer electret can temporarily capture electrons or holes to hold a quasi-permanent electric field

Naoji Matsuhisa

Dr Naoji Matsuhisa received his PhD degree from the Department of Electrical Engineering and Information Systems in the University of Tokyo in 2017. After his studies, he then worked as a postdoc in the Department of Materials Science and Engineering at Nanyang Technological University in Singapore, and theDepartment of Chemical Engineering at Stanford University in the U.S. In April 2020, he joined to the Department of Electronics and Electrical Engineering at Keio

University as an Assistant Professor. In April 2022, he became an Associate Professor in Institute of Industrial Science at the University of Tokyo. He has developed stretchable electronic materials and the devices.

Chien-Chung Shih

Dr Chien-Chung Shih is an Assistant Professor of Chemical and Materials Engineering at National Yunlin University of Science and Technology (NYUST). He received his PhD degree in Chemical Engineering from National Taiwan University in 2016 and joined Prof. Wen-Chang Chen's group as a postdoc researcher from 2016-2019. Prior to joining faculty, he conducted his postdoc research and worked with Prof. Zhenan Bao at Stanford University from 2019 to

2021. His research focuses on conjugated polymers and their applications in field-effect transistors, transistor-structured memory, phototransistors and sorting of single-walled carbon nanotubes.

under external bias. Even if the voltage of the gate electrode is removed, the change in conductance can be retained to some extent, resulting in bidirectional shifts in the threshold voltage. Compared with ferroelectric and floating-gate transistor memory, electret-based transistor memory shows higher writing and erasing speed, higher on/off current ratio, larger memory window, and higher stability.<sup>32</sup> Furthermore, polymer electrets provide transistors with extensible sensory functionalities such as tactile memory and photonic memory by their tunable molecular structure. For example, multistate photonic transistor memory has been achieved using conjugated polymer electrets to form the dielectric layer. Then, the channel conductance of the transistor can be gradually controlled via photogenerated electrons from the electret and is preserved after removing light. 33,34 Moreover, multilevel storage in the transistor can enhance capacity, reduce memory space, and emulate synapses for brain-inspired computing.35,36 Therefore, numerous studies have been focused on exploiting memory characteristics and photonic synaptic behaviors.37

In this review, we analyze representative polymer electrets and their composites for OFET memory devices and correlate chemical structures, morphology, charge transport, and memory characteristics. We begin by providing a brief introduction of the working mechanisms of transistor memory and

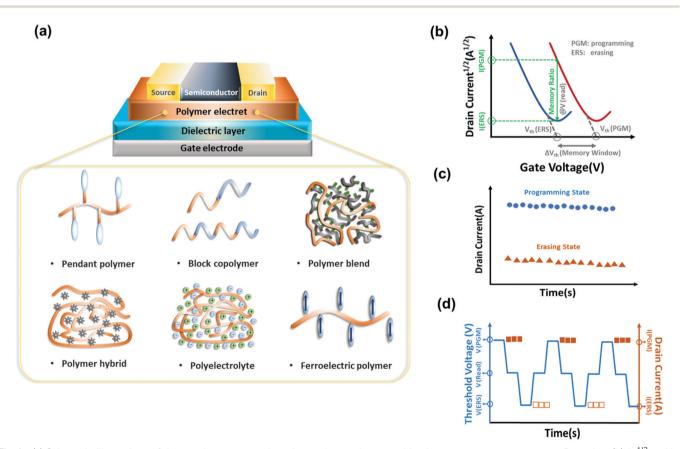

neuromorphic transistors. Next, research progress of transistor memory devices using various polymers as charge storage layers, including pendant polymer electrets, block copolymer electrets, conjugated polymer electrets, ferroelectric polymer electrets, and hybrid nanocomposite electrets is summarized (Fig. 1a). Recent developments in artificial synapses constructed on OFET memory devices based on polymer electrets are then highlighted. Finally, we outline the challenges and outlook for future developments on organic transistor memory devices.

## 2. Working principles of memory

### 2.1 OFET memory

An OFET can have a top or bottom gate and top or bottom contact according to the relative contact position of the active layer and source/drain electrodes. Basically, the OFET is characterized by the drain-source current  $(I_{ds})$  according to the gate-source voltage  $(V_{gs})$  and  $I_{ds}$  according to the drain-source voltage  $(V_{ds})$ , which form the transfer and output curves, respectively. Current  $I_{ds}$  on both logarithmic and linear scales according to voltage  $V_{gs}$  can be depicted by transfer characteristics to extract important performance parameters. Current

Fig. 1 (a) Schematic illustrations of the transistor memory based on polymer electrets with a bottom-gate top-contact configuration. (b)  $I_{\rm ds}^{1/2}$  vs.  $V_{\rm qs}$ curve under applied voltage bias that can determine the memory window and memory ratio. (c) Retention time test and (d) endurance cycles on OFET memory devices.

$I_{\rm ds}$  in the saturation region can be obtained from the transfer curves as follows:

$$I_{\rm ds} = \frac{WC_{\rm i}}{2L} \mu (V_{\rm gs} - V_{\rm th})^2$$

where W and L represent the width and length of the channel region, respectively,  $\mu$  and  $C_i$  are the mobility and capacitance per unit area of dielectric film, respectively, and  $V_{th}$  is the threshold voltage. In the curve of  $I_{

m ds}^{1/2}$  according to  $V_{

m gs}$ , the slope is linearly proportional to the square root of mobility. Thus, when a sufficient  $V_{gs}$  is applied, the charge-capture layer develops a stable built-in electric field that stores charge carriers and produces hysteresis, establishing operation program. This state can be eliminated by applying a reverse gate bias, establishing operation erase (Fig. 1b). Current  $I_{ds}$  in the programmed and erased states represent 1 and 0, respectively.

Several parameters are used to determine the OFET memory characteristics, including the memory window, memory ratio, retention, and endurance ability. The V<sub>th</sub> shift between the programmed and erased states is defined as the memory window, which is one of the most important parameters in OFET memory for distinguishing the information storage level. The retention measures the ability of a memory device to preserve the programmed and erased states without losing the trapped charges through the leakage path over time (Fig. 1c). Commercial OFET memory devices are expected to maintain reliability over 10 years at room temperature, while current studies show results on the order of 10<sup>3</sup> to 10<sup>6</sup> s. <sup>4</sup> The memory endurance can be evaluated by repeated program/ erase cycles (Fig. 1d). The ideal endurance is over 10<sup>6</sup> cycles for nonvolatile secondary storage. However, the typical endurance results for OFET memory are range in 10<sup>2</sup>–10<sup>5</sup> cycles.<sup>2</sup>

#### 2.2 Biological synapses and synaptic transistors

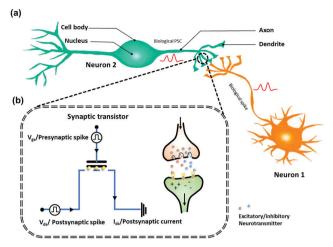

A synaptic transistor is a three-terminal device with a structure similar to that of a transistor-structured memory.38,39 In a synaptic transistor, operation program is on the gate and decoupled from the operation read on the channel, enabling the synaptic transistor to simultaneously execute learning functions and signal transmission. The physically separated configuration of terminals endows synaptic transistor memory with low nonlinearity and variability, being suitable for fast and accurate training of artificial neural networks. As shown in Fig. 2a, the gate and source/drain are commonly used as the presynaptic and postsynaptic terminals, respectively. To simulate the behavior of biological synapses, voltage pulses are applied to the gate electrode, resembling presynaptic spikes on the presynaptic membrane. The mobile charges in the channel are regarded as neurotransmitters (Fig. 2b). 19 Channel conductance is regarded as the synaptic weight (W), whose changes are known as synaptic plasticity. In neurology, synaptic plasticity depends on the activity on either or both sides of a synapse. Generally, synaptic plasticity is divided into short- and long-term plasticity. Short-term plasticity corresponds to a transient modification in the synaptic strength after stimulation, lasting from tens of milliseconds to a few minutes,

Fig. 2 (a) Schematic demonstration of biological neuron and synapse structure. (b) Schematic diagram of the synaptic OFET memory devices.

whereas long-term plasticity is a persistent modification in the synaptic strength, lasting from hours to years. Short-term plasticity is required for transmission, encoding, and filtering of neural signals, whereas long-term plasticity establishes more permanent changes in the neural loop to contribute to memory and learning.40 In addition, there are two forms of synaptic responses, namely, potentiation (excitatory postsynaptic current - EPSC) and depression (inhibitory postsynaptic current -IPSC), which are linked to the strengthening and weakening of the synaptic weight, respectively. The abovementioned synaptic functions form the foundation for implementing bioinspired models of neural processing.41

The operation of synaptic transistors can be divided into two types according to the source of stimulation. For electrical stimulation, based on transistor-structured memory, charges can tunnel from the semiconductor channel to the chargetrapping site under an applied gate voltage, and the captured charges in the floating gate or interface induce control of the channel conductance. For light stimulation, upon exposure to light, excitons are generated, separated, and finally captured in the charge-trapping sites or interface defects, modulating the channel conductance. By engineering the trapping levels in terms of the interfacial effect and/or bulk trapping, synaptic transistors can be operated in volatile or nonvolatile modes according to the amplitude, frequency, and number of gate inputs, ensuring short- and long-term plasticity within a single memory cell. Synaptic transistors may lead to new paradigms to address complicated artificial intelligence problems, such as pattern recognition and classification, bipedal locomotion control, and decision-making.

# Development of polymer electrets for transistor-structured memory devices

A polymer electret is a dielectric material that can acquire a quasi-permanent electrical charge. A polymer electret below the

Table 1 Summary of OFET memory performances based on polymer electrets

|                    | Electret                                | Channel        | Operation mode <sup>a</sup>              | $\Delta {V_{\rm th}}^b$ | $I_{\rm on}/{I_{\rm off}}^c$ | Retention          | Ref. |

|--------------------|-----------------------------------------|----------------|------------------------------------------|-------------------------|------------------------------|--------------------|------|

| Pendant polymer    | PαMS                                    | Pentacene      | EW EE (±70 V)                            | 26                      | 10 <sup>5</sup>              | $> 10^5 \text{ s}$ | 29   |

|                    | PS                                      | Pentacene      | EW EE (±70 V)                            | 22                      | $10^{5}$                     | $> 10^5 {\rm s}$   | 29   |

|                    | PVN                                     | Pentacene      | EW EE (±70 V)                            | 27                      | $10^{6}$                     | $> 10^5 {\rm s}$   | 29   |

|                    | PVN                                     | PDVT-10        | EW EE $(\pm 40 \text{ V})$               | 37                      | $10^{6}$                     | _                  | 43   |

|                    | P(St-co-Pys)                            | Pentacene      | EW EE $(\pm 100 \text{ V})$              | 41                      | $10^{5}$                     | $> 10^4 {\rm s}$   | 44   |

|                    | FPS                                     | $C_{12}$ -BTBT | EW EE (±100 V)                           | 76                      | $10^{6}$                     | $> 10^4 {\rm s}$   | 45   |

|                    | P(St-Fl)                                | BPE-PTCDI      | EW EE (±100 V)                           | 81                      | $10^{3}$                     | $> 10^5 {\rm s}$   | 46   |

|                    | PVTT                                    | BPE-PTCDI      | EW EE (±100 V)                           | 43                      | $10^{2}$                     | $> 10^5 {\rm s}$   | 46   |

| Block copolymer    | MH-b-PS                                 | Pentacene      | EW EE (±50 V)                            | 26                      | $10^{8}$                     | $> 10^4 {\rm s}$   | 47   |

|                    | $MH-b$ -PStFl $_n$                      | Pentacene      | EW EE (±50 V)                            | 37                      | $10^{8}$                     | $> 10^4 {\rm s}$   | 48   |

|                    | PS-b-P4VP(FM)                           | Pentacene      | EW EE $(\pm 100 \text{ V})$              | 46                      | 10 <sup>7</sup>              | $> 10^5 {\rm s}$   | 49   |

|                    | P3HT <sub>44</sub> -b-P <sub>ison</sub> | _              | EW EE (±100 V)                           | 62                      | $10^{5}$                     | $> 10^4 \text{ s}$ | 50   |

|                    | Sol-PDI                                 | Pentacene      | PW (640 nm) EE (60 V)                    | 7                       | $10^{5}$                     | $> 10^4 {\rm s}$   | 51   |

| Conjugated polymer | PFO NPs                                 | Pentacene      | EW EE $(\pm 50 \text{ V})$               | 21                      | $10^{6}$                     | $> 10^4 {\rm s}$   | 52   |

|                    | $poly(PEGMA)_m$ -b- $poly(DB3VT)_n$     | Pentacene      | EW EE $(\pm 50 \text{ V})$               | 34                      | $10^{5}$                     | $> 10^4 {\rm s}$   | 53   |

|                    | β-PFO                                   | Pentacene      | EW $(-80 \text{ V})$ PE $(\text{white})$ | 57                      | $10^{3}$                     | $> 10^4 {\rm s}$   | 54   |

|                    | PFO/PS blend                            | Pentacene      | PW (405 nm) EE (-30 V)                   | 21                      | $10^{6}$                     | $> 10^4 {\rm s}$   | 34   |

|                    | F8BT/PMMA                               | $C_{10}$ -DNTT | PW (455 nm) EE (-60 V)                   | 14                      | $10^{3}$                     | $> 10^4 {\rm s}$   | 55   |

|                    | PFO <sub>5k</sub> -b-PS <sub>22k</sub>  | Pentacene      | PW (405 nm) EE (-40 V)                   | 21                      | 104                          | $> 10^4 \text{ s}$ | 33   |

|                    | PFO-b-POXD                              | BPE-PDI        | EW (-60 V) PE (254 nm)                   | 20                      | 10 <sup>5</sup>              | $> 10^4 \text{ s}$ | 56   |

|                    | $PF-b-P_{iso}$                          | Pentacene      | PW (405 nm) EE (-40 V)                   | 33                      | 10 <sup>6</sup>              | $> 10^4 \text{ s}$ | 57   |

|                    | TPA-CN-TPE                              | Pentacene      | pEW pEE (±100 V) (365 nm)                | 42                      | 10 <sup>4</sup>              | $> 10^4 \text{ s}$ | 58   |

|                    | Poly(CD)                                | Pentacene      | EW $(-90 \text{ V})$ PE (white)          | 82                      | $10^{3}$                     | $> 10^4 { m s}$    | 59   |

<sup>&</sup>lt;sup>a</sup> EW: electrical writing; PW: photowriting; EE: electrical erasing; PE: photoerasing; pEW: photoassisted electrical writing; pEE: photoassisted electrical erasing. <sup>b</sup>  $\Delta V_{\text{th}}$ : memory window. <sup>c</sup>  $I_{\text{on}}/I_{\text{off}}$ : memory ratio.

channel provides field-assisted transfer of charges from the channel to the polymer and localization of these charges by deep traps in the polymer. The resulting immobilization of the transferred charge by deep traps in the polymer produces a  $V_{\rm th}$ shift, which can enhance charge storage of a memory device. The storage of charges in polymer electrets can be explained by the orientation of permanent dipoles and charge trapping by structural defects or boundaries. The characterization of charge-trapping materials in polymer electrets involves surface properties, dielectric properties, and molecular structure properties.<sup>3</sup> In a polymer electret-based system, because the transport of charge carriers occurs in the first few monolayers of organic semiconductors adjacent to the interface of the gate dielectrics, the morphology of the charge-trapping layer affects the growth of the deposited semiconductor thin films regarding aspects such as crystallinity, grain size, grain boundaries, and packing orientation, which in turn influence the transport and retention of trapped charges.

Several approaches can be used to achieve memory characteristics in transistors using polymeric materials, which can be divided into (1) pendant polymer electrets, (2) block copolymer electrets, (3) conjugated polymer electrets, (4) hybrid polymer composites, and (5) ferroelectric polymer electrets. In this section, we analyze the advantages and disadvantages of different systems based on polymer electrets. Tables 1 and 2 summarizes the OFET memory characteristics of representative polymer electrets and their nanocomposite, respectively. Small molecules are preferred for the use as channel materials because they can be processed in vacuum deposition, and this prevents the damage of the polymer electrets from the solvent during spin-coating of polymer semiconductor solution.

### 3.1 Pendant polymer electrets

The charge storage capacity of a polymer is determined by the chemical structure of its constitutively repeating units. We first

Table 2 OFET memory device performance based on polymer hybrid nanocomposite

|                | Electret                    | Channel   | Operation mode <sup>a</sup>                    | $\Delta {V_{ m th}}^b$ | $I_{\rm on}/I_{\rm off}{}^c$ | Retention            | Ref. |

|----------------|-----------------------------|-----------|------------------------------------------------|------------------------|------------------------------|----------------------|------|

| Polymer hybrid | PS-b-P2VP/Au NP             | РЗНТ      | EW EE (±100 V)                                 | 43                     | $10^{5}$                     | >10 <sup>4</sup> s   | 62   |

|                | PVPK/ZnO NP                 | Pentacene | EW EE (±70 V)                                  | 58                     | $10^{6}$                     | $> 10^4 {\rm s}$     | 63   |

|                | PVPy/Au@Ag NR               | Pentacene | pEW pEE (±50 V) (660 nm)                       | 20                     | $10^{3}$                     | $> 10^4 {\rm s}$     | 65   |

|                | N(PTPMA) <sub>3</sub> /PCBM | Pentacene | EW EE (±50 V)                                  | 33                     | $10^{5}$                     | $> 10^4 {\rm s}$     | 64   |

|                | PAVP/SM                     | Pentacene | EW EE ( $\pm 100 \text{ V}$ )                  | 78                     | $10^{5}$                     | $> 10^4 { m s}$      | 66   |

|                | PVN/C <sub>60</sub>         | Pentacene | EW (70 V) PE (350 nm)                          | 21                     | $10^{5}$                     | $> 10^4 {\rm s}$     | 67   |

|                | PMMA/TIPS                   | P3HT      | pEW EE $(\pm 60 \text{ V})$ $(645 \text{ nm})$ | 31                     | $10^{5}$                     | $> 10^{3} \text{ s}$ | 68   |

|                | PI/TPA-SM                   | Pentacene | pEW pEE (±100 V) (365 nm)                      | 37                     | $10^{5}$                     | $> 10^4 { m s}$      | 69   |

|                | PS/PVSK NCs                 | Pentacene | PW (450 nm) EE (-60 V)                         | 7                      | $10^4$                       | $> 10^6 {\rm s}$     | 70   |

|                | PS-b-PEO/PVSK NCs           | P3HT      | PW (520 nm) EE (-60 V)                         | _                      | $10^4$                       | $> 10^4 {\rm s}$     | 71   |

<sup>&</sup>lt;sup>a</sup> EW: electrical writing; PW: photowriting; EE: electrical erasing; PE: photoerasing; pEW: photoassisted electrical writing; pEE: photoassisted electrical erasing. <sup>b</sup>  $\Delta V_{\text{th}}$ : memory window. <sup>c</sup>  $I_{\text{on}}/I_{\text{off}}$ : memory ratio.

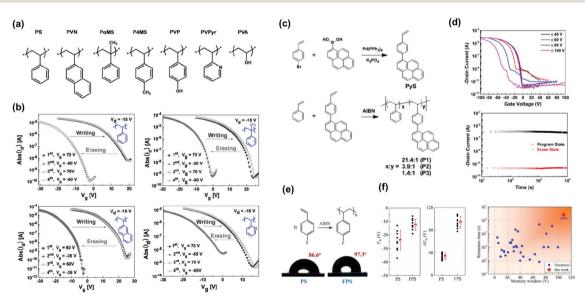

analyze pendant polymer electrets with charge-trapping elements in their side chains. Styrenic polymers were the first electret-based systems to be studied in detail. Baeg et al. selected polymers ranging from hydrophobic (nonpolar) to hydrophilic (polar) to establish a polymer electret layer in pentacene-based transistor memory devices (Fig. 3a).29 The devices exhibited an adjustable  $V_{\rm th}$  shift by applying a positive voltage bias, indicating that electrons were transferred from pentacene to the polymer layer and subsequently trapped deep within the benzene units. They also found that nonpolar polymers are superior chargeable dielectrics because the transferred and trapped charges in the polar pendant group can be dissipated rapidly through the conducting pathway derived from the moisture in the atmosphere or residual ions and impurities in hydrophilic polymers. In addition, the memory window and retention time were inversely proportional to the hydrophilicity and polarity of the pendant polymer electret, as shown in Fig. 3b.

The findings of Baeg et al. were confirmed by Wang et al. They designed polymers consisting of pendant hydroxyethyl methacrylate and naphthalene groups in various ratios.<sup>42</sup>

The memory device using polymer electrets with more hydroxy groups in the side chain exhibited inferior charge retention ability. Additional blocking layers were required to prevent charge leakage. Liu et al. reported random copolymers comprising pendant styrene and 4-(1-pyrenyl)-styrene moieties (P(St-co-Pys)) in different molar ratios (Fig. 3c).44 With the strong hole-trapping ability of hydrophobic pyrene units, the OFET memory revealed clear ambipolar trapping behavior, contributing to a large memory window (41.8 V with a high memory ratio of 10<sup>5</sup> and a long retention time above 10<sup>4</sup> s) (Fig. 3d). Lu et al. synthesized styrenic polymers modified with

a fluorine atom, poly(4-fluorostyrene) (FPS), for the chargetrapping layer, as depicted in Fig. 3e. 45 The fluorinated benzene ring in the side chain offered a large storage density and potentially accommodated charges in the bulk deep-trap states. Notably, the memory device achieved a high memory window of 100 V (Fig. 3f). The increased trap density and trap energy for both electrons and holes in the poly(4-fluorostyrene) contributed to a high sheet charge density of  $6.8 \times 10^{12} \text{ cm}^{-2}$ .

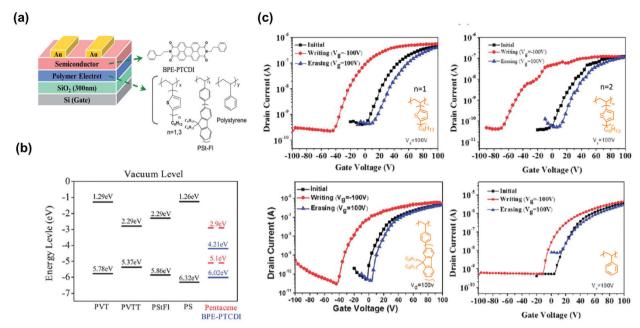

In addition to styrenic polymers, polymers using short  $\pi$ -conjugated moieties as the pendant group have been used as the electret layer in transistor memory. Chen et al. reported polymer electrets of linear polystyrene (PS) para-substituted with  $\pi$ -conjugated oligofluorenes.<sup>60</sup> The fluorene units provided vacancies for hole trapping, and the memory windows of the device were enhanced with increasing conjugation length. The longest fluorene side group created a small barrier to facilitate the injection of electrons from pentacene due to lower lowest unoccupied molecular orbital (LUMO) level and smallest band gap. The reflecting program/erase current switch of the devices was maintained for over 100 cycles, showing high stability and full reversibility. A similar structure was designed with one or three thiophene units in the side chain (Fig. 4a). Given the higher highest occupied molecular orbital (HOMO) level and stronger electron-donating properties of the thiophene units, more holes were transferred from the n-type semiconducting N,N'-bis(2-phenylethyl)perylene-3,4,9,10-bis(dicarboximide) (BPE-PTCDI) layer to the electret layer (Fig. 4b).<sup>46</sup> The memory device using PVTT electret showed memory window of 81 V, on/off current ratio of 3.6  $\times$  10<sup>3</sup>, which is higher than that of PVT whose memory window and on/off current ratio are 49 V and  $1.2 \times 10^2$ , respectively (Fig. 4c). Hence, tuning the

Fig. 3 Styrenic polymers as the charge trapping layer. (a) Chemical structure of styrenic polymer electrets; PS, PVN, PaMS, P4MS, PVP, PVPyr, and PVA. (b) Reversible  $V_{th}$  shift in transfer plots of the OFET memory devices with various styrenic polymer gate electrets. Reproduced with permission.<sup>29</sup> Copyright 2008, Wiley-VCH. (c) Synthetic routes for P(St-co-Pys) polymers. (d) Transfer characteristics after electrical writing and erasing (top) and retention test (bottom) of the memory device comprising [P(St-co-Pys)] polymer electret. Reproduced with permission.<sup>44</sup> Copyright 2016, Wiley-VCH. (e) Chemical and physical characterization of FPS. (f) Statistics of  $V_{th}$  and  $V_{th}$  shift for PS and FPS (left) and Memory window and retention time of polymeric gate dielectrics applied in OFETs (right). Reproduced with permission. 45 Copyright 2020, The Royal Society of Chemistry.

Fig. 4 (a) Device architecture of the BPE-PTCDI thin film based OFET memory (left) and chemical structures of polymer electrets with conjugated side chain (right). (b) Energy level diagram of polymer electrets, BPE-PTCDI semiconductor. (c) Vth shifts in transfer curves for the BPE-PTCDI OFET memory device. Reproduced with permission.<sup>46</sup> Copyright 2013, The Royal Society of Chemistry.

pendant conjugation length/strength allows to control the magnitude of the memory window.

#### 3.2 Block copolymer electrets

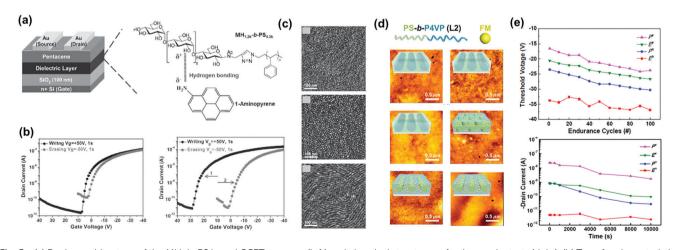

Direct contact between a polymer electret and semiconducting channels may result in the loss of trapped charges during reading. To prevent this problem, block copolymers have been used as electrets, in which charge-trapping elements are surrounded by insulated segments through a microphase separation nanostructure, thereby prolonging retention. Chiu et al. reported green electrets made of a sugar-based block copolymer, maltoheptaose-block-PS (MH-b-PS), to form the memory layer (Fig. 5a).47 The hydrophilic and abundant hydroxyl maltoheptaose block was employed as a chargetrapping site, while the hydrophobic PS block served as both a matrix and tunneling layer. The resulting devices possessed a more positive  $V_{\rm th}$  shift than that of the PS thin film owing to the electron-trapping ability of the hydroxyl groups of the maltoheptaose blocks (Fig. 5b). Amphiphilic block copolymers can produce ordered self-assembly morphologies by manipulating the Flory-Huggins interaction parameter. Fig. 5c shows the surface morphologies of MH-b-PS for as-cast and solvent

Fig. 5 (a) Device architecture of the MH-b-PS based OFET memory (left) and chemical structures of polymer electrets (right). (b) Transfer characteristics after electrical writing and erasing of the memory device comprising MH-b-PS polymer electret. (c) AFM phase images of the MS-b-PS film with different solvent annealing time. Reproduced with permission.<sup>47</sup> Copyright 2014, Wiley-VCH. (d) AFM images and schematic illustration of the PS-b-P4VP/ ferrocene electret thin film after solvent annealing. (e) Endurance cycles and retention tests of memory devices based on the PS-b-P4VP/ferrocene polymer electret. Reproduced with permission.<sup>49</sup> Copyright 2015, American Chemical Society.

annealed processes by a tetrahydrofuran/H2O mixture for 8 and 12 h, respectively. The morphologies exhibited less-ordered spheres, packed dots, and horizontal cylindrical structures. Interestingly, the electrical switching characteristics of the memory depended on the electret morphology. A polymer electret with a horizontal cylinder structure enabled a high charge-trapping density owing to the larger contact area with the semiconducting layer.

A memory device using MH-b-PS with a cylindrical structure showed a higher memory window than the PS electret and had a superior charge retention longer than 10<sup>4</sup> s without current leakage. Maltoheptaose block copolymers comprising pendantconjugated fluorene moieties (MH-b-PStFl<sub>n</sub>) have subsequently been used as electrets for transistor memory with ambipolar trapping. 48 Under memory operation, a large negative  $V_{th}$  shift was observed after introducing pendant-conjugated fluorene moieties, indicating hole carrier trapping. In addition, the memory characteristics of MH-b-PStFl<sub>n</sub>-based memory devices

could be modulated through fabrication, thin-film morphology, and  $\pi$ -conjugation length of the pendant group. Liu et al. then reported a transistor memory based on supramolecular PS-blockpoly(4-vinylpyridine) (PS-b-P4VP) containing hydroxyl-functionalized ferrocene small molecules (FM) as charge-trapping sites. 49 The block copolymer acted as a template for defining FM nanoscale trapping sites with different morphologies (Fig. 5d). The nanocomposites formed electrets for memory devices with stable charge retention, as indicated by program/erase cycles and charge retention tests (Fig. 5e). Overall, memory characteristics can be easily tailored by controlling the morphology of the block copolymer and hybrid nanocomposite thin films.

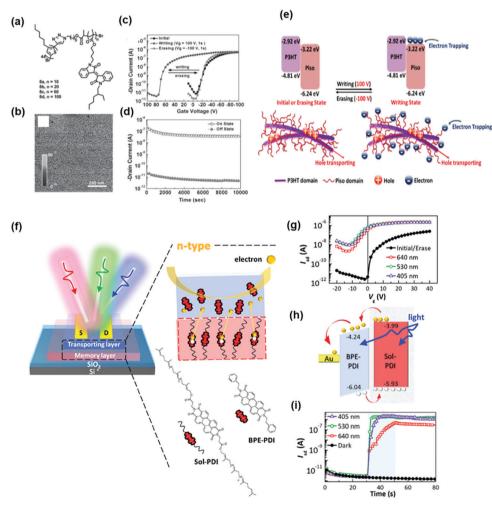

Another advantage of using a block copolymer electret is that it simplifies fabrication of transistor memory devices. Wang et al. synthesized donor-acceptor rod-coil diblock copolymers of poly(3-hexylthiophene) (P3HT)-block-poly(pendant isoindigo) (Piso) P3HT44-b-Pison (Fig. 6a) and employed them as semiconductor for transistor memory to integrate charge-

Fig. 6 (a) Chemical structure and (b) AFM phase images of P3HT<sub>44</sub>-b-P<sub>ison</sub> polymers. (c) Transfer characteristics after electrical writing and erasing of the memory device using  $P3HT_{44}$ -b- $P_{ison}$  as the channel and memory layer simultaneously. (d) Retention time test of the memory device. (e) Illustration of energy levels of P3HT rod and  $P_{iso}$  coil and the proposed mechanism. Reproduced with permission. <sup>50</sup> Copyright 2016, Wiley-VCH. (f) Device architecture and chemical structure of sol-PDI. (g) Transfer characteristics after electrical writing and photoerasing of the memory device. (h) Energy-level diagram and working mechanism. (i) Transient characteristics of the phototransistor memory. Reproduced with permission. <sup>51</sup> Copyright 2020, Wiley-VCH.

transport and charge-trapping properties into a single channel layer.<sup>50</sup> P3HT was intended for charge transport, and pendant Piso blocks with different ratios were used as charge storage elements in OFET memory devices. The polymer thin film showed a well-distributed nanofibrillar structure, as shown in Fig. 6b, contributing to the high carrier mobility when used as the channel. Fig. 6c shows the transfer characteristics of the device with P3HT<sub>44</sub>-b-P<sub>iso100</sub>. During writing, several electrons were induced at the LUMO level of Piso by the positive electric field, leading to a positive  $V_{\rm th}$  shift. This is because the generated electrons in the P<sub>iso</sub> domain induce extra holes accumulated in the P3HT channel before scanning. On the other hand, the trapped electrons at the Piso coil could be erased using a negative voltage bias, and  $V_{\rm th}$  was shifted back to its initial state, as illustrated in Fig. 6d. The stability of the memory device was not affected by the channel integration and trapping ability. The stable data retention and endurance ability obtained from long-term stability and write-readerase-reread cycle tests are shown in Fig. 6e. Recently, Chiang et al. developed phototransistor memory using a conjugated block copolymer as the dielectric layer. They synthesized a block polymer of solanesol-functionalized perylenediimide (PDI) and employed it as an electret in an n-type (BPE-PDI) transistor. 51 Fig. 6f shows the device architecture and chemical structures of the solanesol-functionalized perylenediimide and BPE-PDI. Fig. 6g shows the typical transfer curves of n-type transport behavior in the initial/erase state of the devices. A negative  $V_{\rm th}$  shift was observed in the corresponding programmed state after photo-programming. The photogenerated electrons migrated through the semiconductor, leaving the counterpart photogenerated holes behind the coil segment,

thus altering the conductance states in the active channel (Fig. 6h). Furthermore, the self-assembled behavior induced by thermal annealing defined the trapping sites and tunneling regions in the conjugated cores and side chains, respectively, enabling a fast response with an excellent memory ratio of 105 over 10<sup>4</sup> s and high sensitivity to multiband light illumination (Fig. 6i). In general, tuning the feasibility of block copolymer electrets is beneficial for obtaining desired electronic properties.

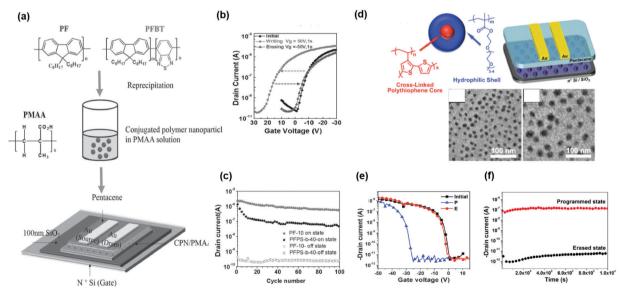

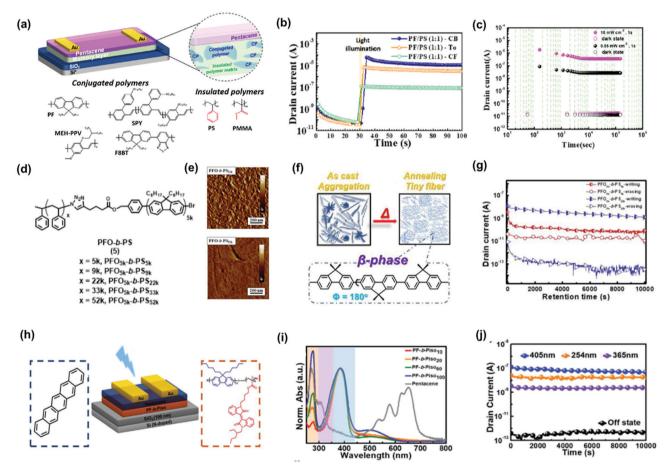

### 3.3 Conjugated polymer electrets

Conjugated polymers used as charge-trapping elements can increase the memory performance because, in principle, they can be controlled by adjusting the energy-level alignment between the energy structure of the semiconducting layer and that of the polymer electret layer. In other words, charge injection can also be controlled by the molecular structure of polymers. When conjugated polymers are used as chargetrapping media, the formation of isolated nanodomains is essential to overcome charge leakage in conjugated polymer electrets and achieve a long retention time in nonvolatile memory. Shih et al. reported organic floating-gate electrets based on conjugated polymer nanoparticles (CPNs).<sup>52</sup> A stable poly(9,9-di-n-octylfluorenyl-2,7-diyl) (PFO) nanoparticle (NP) solution was fabricated using reprecipitation, and the solution was blended with an insulated polymer for fabrication. Then, a thin electret layer beneath the semiconductor was prepared by simple spin coating (Fig. 7a). CPNs formed an isolated trapping center for charge storage, similar to floating gates. The transistor memory device revealed a controllable  $V_{\rm th}$  shift (Fig. 7b), indicating effective electron trapping by the PFO CPNs. The memory device showed stable retention and writing/erasing endurance (Fig. 7c)

Fig. 7 (a) Schematic configuration of the CPNs based OFET memory and chemical structures of PFO and PFBT. (b) Transfer characteristics after electrical writing and erasing of the memory device using PFO CPNs as nano-floating gates. (c) Retention time test of the memory device. Reproduced with permission. 52 Copyright 2015, Wiley-VCH. (d) Chemical structure of cross-linked nanoparticles and corresponding TEM images of the spin-coat thin films. (e) Transfer characteristics after electrical writing and erasing of the memory device using  $poly(PEGMA)_m$ -b- $poly(DB3VT)_n$  as nano-floating gates. (f) Retention time test of the memory device. Reproduced with permission. 53 Copyright 2016, The Royal Society of Chemistry.

which could be attributed to the formation of  $\beta$  phase in PFO CPNs. The crystalline  $\beta$  phase contains planar zigzag conformation which results in an extended conjugation length and smaller band gap. The interfaces between amorphous and β-phase could act as charge trapping sites due to the potential barrier produced by the different LUMO energy levels and physical defects, and this improve charge storage density and stability. Lo et al. reported a strategy for producing CPN polymer electrets without requiring an additional CPN preparation step. The polymer poly(PEGMA)<sub>m</sub>-bpoly(DB3VT)<sub>n</sub> existed in the form of core-shell NPs after crosslinking (Fig. 7d).<sup>53</sup> The unique core-shell structure effectively eliminated charge leakage from the cross-linked cores of rigid poly(DB3VT) because the soft shells of the poly(PEGMA) segments prevented direct contact between the cores and semiconducting layer. The resulting device had a memory window of 34 V, retention ability over 104 s, and endurance of over 100 cycles (Fig. 7e and f).

Conjugated polymer electrets provide optoelectronic properties that enable the implementation of light programmable/

erasable transistor memory, called photonic transistor memory. The charge-trapping capacity of OFET memory devices can be further improved through light-assisted programming. In addition, photonic programming is more adequate than electrical programming for achieving multilevel data storage with high discrepancy, as it avoids the drawback of destructive reading during electrical reading. Ling et al. used PFO as a photoluminescent polymer electret for phototransistor memory devices.<sup>54</sup> They found that β-conformation is beneficial for electron trapping, thereby enhancing memory stability. This result is in accordance with the earlier discussion on CPNbased transistor memory devices. Photonic OFET memory with β-phase PFO could be light reset and showed a larger memory window of 44.8 V for an electrical writing time of 20 ms with an acceptable memory ratio of 10<sup>3</sup> over 8000 s. The same approach was used by Chiu et al., revealing an improved memory ratio of 10<sup>7</sup> over 4000 s under electrical writing and photo-assisted electrical erasing using 405 nm light.<sup>61</sup> However, the semiconducting nature of PFO deteriorated the stability of the trapped

Fig. 8 (a) Device architecture and chemical structures of the conjugated polymers and insulated polymers in the polymer blend electrets. (b) Transient characteristics of the photonic memory. (c) Retention time test of the memory device. Reproduced with permission.<sup>34</sup> Copyright 2019, American Chemical Society. (d) Synthetic route of PFO-b-PS BCPs (e) AFM phase images of the annealed polymer films. (f) Schematic illustration of the morphology and the properties of the annealed polymer films. (f) Schematic illustration of the morphology and the properties of the annealed polymer films. (f) Schematic illustration of the morphology and the properties of the annealed polymer films. (f) Schematic illustration of the morphology and the properties of the annealed polymer films. (f) Schematic illustration of the morphology and the properties of the annealed polymer films. (f) Schematic illustration of the morphology and the properties of the propechanges for the polymer films after thermal annealing. (g) Retention time test of the memory devices. Reproduced with permission.<sup>33</sup> Copyright 2021, The Royal Society of Chemistry. (h) Device architecture and chemical structure of the materials in the channel and memory layers. (i) UV-vis absorption spectra of  $PF-b-P_{iso}$  and pentacene. (j) Retention time test of the photonic memory device after light exposure. Reproduced with permission.<sup>57</sup> Copyright 2021, Wiley-VCH.

charges, and destructive readout with gate bias was necessary for operation. Shih and Chen et al. proposed a blend of conjugated polymers and insulated polymers as photoactive polymer electrets to improve memory performance, obtaining a multilevel photoresponse. The constituent conjugated polymers included PFO, poly[2-methoxy-5-(2-ethylhexyloxy)-1,4-phenylenevinylene], poly[(9,9-di-n-octylfluorenyl-2,7-diyl)-alt-(benzo[2,1,3]thiadiazol-4,8-diyl)] (F8BT).<sup>34</sup> The constituent insulated polymers, including PS and poly(methyl methacrylate) (PMMA) along with their chemical structures and device architectures are shown in Fig. 8a. The phase-separation morphology of the blend film could be modulated by different solvents, as shown in Fig. 8b. In addition, a high contact area between the conjugated and insulated polymers with a discrete distribution could be achieved using chlorobenzene as the solvent. As a photoactive electret, the photogenerated electrons from the conjugated polymer could be transferred to the proximate insulated polymers, and photogenerated holes were transduced to the pentacene channel for photoinduced electron trapping during photo-writing. To achieve electrical erasing, holes were injected from the pentacene channel to recombine with trapped electrons. The device exhibited a high memory ratio of  $5 \times 10^4$  over 10<sup>5</sup> s (Fig. 8c) under light illumination with a wavelength of 405 nm and intensity of 5 mW cm<sup>-2</sup>. Later, Xu et al. applied a conjugated/insulated polymer blend of F8BT/PMMA into a threelevel phototransistor memory, in which the memory states were defined using gate bias to obtain a 0-to-1 state transition and gate bias with light illumination to obtain a 1-to-2 state transition.<sup>55</sup> The memory device had exceptional memory ratios of  $10^3$  (0-2 state) and  $10^2$  (0-1 state) over  $2 \times 10^4$  s.

Conjugated block polymers comprising insulated segments as electrets provide photonic memory effects similar to those of the polymer blend, while increasing stability. In fact, the severe phase separation observed in the conjugated/insulated polymer blends can be eliminated, thus improving the memory performance. Chen et al. synthesized block copolymers of PFO<sub>5k</sub>block-PS<sub>n</sub> with different PS lengths (Fig. 8d) and used them as photoactive electrets in pentacene-based phototransistor memory.<sup>33</sup> The polymer exhibited a well-dispersed microphaseseparated morphology, which stabilized the trapped electrons at the interface of the PFO and PS domains. As shown in Fig. 8e, PFO-block-PS22k possessed an enhanced PS content and exhibited a smoother surface than PFO-block-PS5k, which had a fiber-like structure with a low PS content. In addition to the morphological changes, PFO achieved β-conformation when incorporated in block copolymers (Fig. 8f), thereby improving the stability of trapped electrons, agreeing with the results reported by Ling et al. By optimizing the PS content of the memory device, a more stable photoresponse and memory window could be achieved, as shown in Fig. 8g. Notably, a memory device composed of PFO-block-PS22k achieved a high memory ratio of 10<sup>4</sup> with a retention time over 10<sup>4</sup> s. Subsequently, block copolymers composed of PFO and poly(vinylphenyl oxadiazole) (PFO-b-POXD) were used as electrets to investigate the influence of the donor-acceptor effect on memory performance (Fig. 8h).<sup>56</sup> The memory could be triggered by light with

wavelengths from 254 to 405 nm according to the absorption region (Fig. 8i). A memory device composed of PFO-b-POXD and BPE-PDI exhibited efficient electrical writing/photo-erasing behavior with a high memory ratio of 105 and a retention time over 10<sup>4</sup> s under illumination by 254 nm light with a low intensity of 1 mW cm<sup>-2</sup> (Fig. 8j). Chen et al. reported a panchromatic memory device using pentacene as the channel and block copolymers composed of PFO and P<sub>iso</sub> as the electret.<sup>57</sup> Complementing the photoresponsivity of the PFO to blue light, Piso served as an insulated coil and ultraviolet (UV)-active polymer, allowing the memory device to respond to UVC (254 nm) and UVA (365 nm) light with memory ratios of 10<sup>3</sup> and 10<sup>4</sup>, respectively. Notably, the photoinduced electrons in the pentacene channel could be transduced into the block copolymer electret without assistance of gate bias, thus allowing the memory device to achieve memory ratios of 10<sup>4</sup> and 10<sup>2</sup> under green and red light, respectively. These results indicate that trimming electron-donating/accepting groups in polymer electrets not only modulates the energy levels and optical absorption but also regulates the polarity and storage of the charges trapped within the electrets.

Aggregation-enhanced-emission polymers have been employed in photonic transistor memory devices. Cheng et al. introduced an electret composed of an aggregation-enhanced-emission active polyamide (TPA-CN-TPE) that emitted strong green light under UV irradiation for subsequent absorption by a pentacene channel.<sup>58</sup> The photoinduced excitons in the channel could be separated with the assistance of a gate bias, leading to substantial shifts in the threshold voltage that could be considered as photowriting. Their memory device could be erased by applying a reverse gate bias to achieve a high memory ratio of 104 over 10<sup>4</sup> s. On the other hand, an aggregation-enhanced-emission inactive aromatic polyimide film exhibited very weak luminescence because it had a much stronger intramolecular chargetransfer effect than that of TPA-CN-TPE. Subsequently, Chen et al. reported an aggregation-caused-quenching active polymer electret of poly(carbazole-dioxazine) (Poly(CD)).59 Owing to its strong holetrapping capability, an ultrahigh memory window of 82 V could be achieved by electrically writing a Poly(CD)-based device. In photo-erasing, Poly(CD) efficiently generated excitons under light illumination to eliminate the trapped charges in the electret. Owing to the reported research progress, polymer materials and their derivatives are being increasingly applied to versatile information storage.

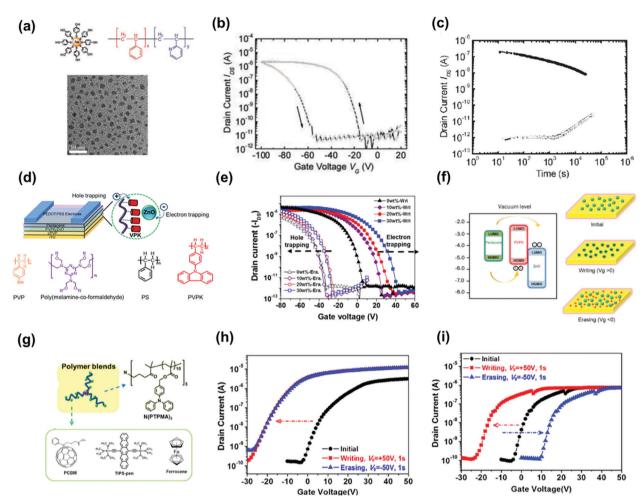

#### 3.4 Hybrid polymer nanocomposites

Hybrid floating-gate electrets consisting of conducting/semiconducting nanomaterials blended with a polymer matrix provide several advantages for transistor memory. For instance, the memory window can be enhanced owing to the additional charge-trapping moieties inside the polymer electret. In addition, the combination of polymer electrets and photoactive nanomaterials contributes to versatile optoelectronic functionalities such as light sensing, multibit data storage, and neuromorphic computing. We analyze three types of nanomaterials that have been employed as floating gates: (1) metallic/semiconducting NPs, (2) small organic molecules, and (3) perovskite nanocrystals (NCs). The use of NPs in

Fig. 9 (a) Schematic representation of Au NPs with multiple H-bond-donating groups, chemical structure of PS-P2VP, and TEM image of Au NPs. (b) Dual sweeping I-V curve of the device using electret comprising 40% Au NPs. (c) Retention time test of the memory devices. Reproduced with permission. <sup>62</sup> Copyright 2012, American Chemical Society. (d) Schematic configuration of the OFET memory device and the chemical structure of the polymer matrix. (e) Transfer characteristics after electrical writing and erasing of the memory device using PVPK/ZnO as nano-floating gates. (f) Mechanisms and energy band diagrams under positive and negative bias. Reproduced with permission.<sup>63</sup> Copyright 2015, Springer Nature. (q) Chemical structure of n-polymer dielectric of N(PTPMA)<sub>3</sub> and organic materials of PCBM, TIPS-pen, and ferrocene. Transfer characteristics after electrical writing and erasing of the memory device with (h) N(PTPMA)<sub>3</sub> and (i) 5 wt% PCBM:N(PTPMA)<sub>3</sub> as electrets. Reproduced with permission.<sup>64</sup> Copyright 2014, American Chemical Society.

polymer nanocomposites requires control over both their distribution and loading within the matrix. Watkins et al. reported a hybrid floating-gate electret comprising poly(styrene-b-2-vinyl pyridine) (PS-b-P2VP) and hydroxy-thiophenol-functionalized gold NPs (Fig. 9a).62 The NPs were confined to the selfassembled domains through hydrogen bond interactions with pyridine groups and yielded a well-ordered composite. The resulting device containing 40% gold NPs had a preliminary memory window above 60 V and current ratio of 10<sup>5</sup> over 100 h under a programming voltage of 100 V for 1 s (Fig. 9b and c). The drawback of using NPs as nano-floating gates is the decrease in the transparency of the electret owing to surface plasmon resonance.

Shih et al. used a wide-bandgap zinc oxide NP blend with a poly(9-(4-vinylphenyl) carbazole) (PVPK) polymer matrix as the memory layer to construct transistor memory.<sup>63</sup> Fig. 9d shows the device and material structures. The device based on hybrid

electret exhibited electric bistability owing to the electron trapping of zinc oxide NPs and hole trapping in PVPK, as illustrated in Fig. 9e and f. The fabricated transistor memory devices exhibited a memory window of 60 V with a retention time over 10<sup>4</sup> s and a relatively high transparency of 90% at a wavelength of 500 nm. The reduced transparency of NP hybrid electrets, on the other hand, suggests the potential to construct light-responsive memory devices. Zhou et al. reported a hybrid floating-gate electret comprising gold-silver core shell nanorods (Au@Ag NR) uniformly distributed in poly(vinylpyrrolidone) (PVPy).65 The plasmon resonance effect of nanorods could be manipulated by varying either the size of the gold cores or the thickness of the silver shells to achieve strong absorbance and a wide-spectrum response range from the visible to the near-infrared region. The resulting memory device had acceptable memory windows of 20 V after 104 s under memory programming using photo-assisted writing/erasing with gate bias. In addition, the memory device possessed tunable multilevel data storage with light assistance.

Small molecules provide advantages such as easy synthesis, low-cost solution processing, and controlled molecular weight and morphology, making them good candidates for molecular floating gates. Fullerene materials ( $C_{60}$  and [6,6]-phenyl  $C_{61}$ butyric acid methylester-PCBM) are the most used n-type small molecular floating gates because of their nanoscale structures and low-lying LUMO energy levels. Liu et al. used common organic molecules such as ferrocene as donors blended into the polymer matrix to serve as the charge storage layer in copper-phthalocyanine-based transistor memory.<sup>72</sup> The charge could tunnel through the insulator polymer to an organic donor when copper phthalocyanine contacted the small molecules. The carriers were stored, and the device exhibited a sharp increase in conductivity/memory switching after the charge transfer. Chiu et al. constructed nonvolatile OFET memory devices using a blend electret with N(PTPMA)<sub>3</sub> and PCBM (Fig. 9g).<sup>64</sup> They found that the memory feature can be changed from a write-once/read-many-type device using N(PTPMA)<sub>3</sub> as the electret to a flash type by adding PCBM increased from 0 to 5 wt% (Fig. 9h and i). Chou et al. reported a

supramolecular polymer electret made of poly(4-vinylpyridine) coupled with high loading of small molecules of phenol, 2-naphthol, and 2-hydroxyanthracene through hydrogen bond interactions as a charge-trapping layer. 66 Owing to the electronaccepting ability of the benzene ring, the device using electret containing 50% of 2-naphthol showed a large positive  $V_{th}$  shift of 61 V after applying a positive gate bias of 100 V for 1 s. The memory windows of these devices were significantly enhanced by increasing the conjugation size of the molecules. Moreover, a superior memory ratio of more than  $10^7$  over  $10^4$  s was achieved in the memory devices. Floating-gate electrets comprising a photoactive molecule have been used in memory devices to realize photo-writing/-erasing without gate bias. Park et al. reported a pentacene-based FET memory using a poly(2vinylnaphthalene) (PVN)/C60 hybrid electret with dual-mode storage and photoinduced erasing effects under 350 nm UV light (Fig. 10a).<sup>67</sup> When exposed to light, C<sub>60</sub> generated excitons, and these photoexcited carriers contributed to eliminate trapped charge carriers, resulting in the photo-induced recovery of the OFET performance (Fig. 10b). The memory devices showed good memory current switching with repeated programing/erasing processes over 100 cycles and retention times of more than 10<sup>5</sup>

Fig. 10 (a) Device architecture and (b) transfer characteristics after electrical writing and photoerasing of the memory device comprising floating gate electret of PVN and C<sub>60</sub>. Reproduced with permission.<sup>67</sup> Copyright 2017, American Chemical Society. (c) Schematic diagram of the organic phototransistor memories and chemical structures of PA, PI and SM used in the electret layer. (d) Absorption spectra of SM and pentacene and emission spectra (excited at 365 nm) of PA and PI thin films. Reproduced with permission.<sup>69</sup> Copyright 2019, The Royal Society of Chemistry. (e) Device configuration of the PVPK NCs based photomemory. (f) TEM images of the MAPbBr<sub>3</sub>/PS composite film. (g) The operating mechanism of the nonvolatile perovskite-based photomemory. Reproduced with permission.<sup>70</sup> Copyright 2017, Wiley-VCH. (h) Schematical illustration of the aggregations at the interface of pentacene and hybrid perovskite-based layers and illustration of NCs embedded in the polymer matrix. (i) Transfer characteristics after photo writing and electrical erasing of the memory device comprising. Reproduced with permission. 73 Copyright 2018, The Royal Society of Chemistry.

s both for the hole- and electron-storage modes. The memory characteristics can be improved by controlling the optical absorption of the incorporated organic molecules, polymer electret, and channel material as well as the energy alignment between them. Shiono et al. proposed a P3HT-based transistor memory device using a PMMA/6,13-bis(triisopropylsilylethynyl) (TIPS) pentacene blend layer as the electret. 68 Photocarriers were generated in both the P3HT film and PMMA/TIPS blend layer. Given the multiple absorption and appropriate energy alignment between P3HT and TIPS pentacene, the memory device could perform photo-assisted electrical writing/erasing with blue/ green/red light in a memory window of 25-30 V with a memory ratio of  $10^2$ – $10^3$  over 3000 s. Liou *et al.* investigated the polymer electret effects on phototransistor memory using triphenylamine-based small molecules (TPA-SM) and polyamide (PA) or polyimide (PI) as the polymer matrix (Fig. 10c).<sup>69</sup> During UV-assisted electrical writing, the photoluminescence emissions produced by the photogating molecules were absorbed by the top pentacene, as confirmed by the absorption spectra (Fig. 10d), thus producing photoinduced excitons that were transduced into holes and electrons. PI produced a wider bandgap than PA, potentially improving charge trapping. Overall, memory devices fabricated from PI and TPA units have demonstrated high memory ratios of 10<sup>5</sup> over 10<sup>4</sup> s, outperforming hybrid electrets based on a PA matrix.

Photoactive floating-gate electrets based on metal NPs or organic molecules usually require a high incident light density or long exposure time for photo-writing/-erasing possibly owing to their weak photoresponses. Thus, photoactive materials with higher absorption coefficients or exciton lifetimes, such as perovskite NCs, can be incorporated. Perovskite NCs possess strong photoluminescence emission capabilities, low exciton binding energies, intense light-harvesting capabilities, and long exciton lifetimes, being promising photogates for floating-gate electrets. Owing to their compelling properties, perovskite NCs have been developed for phototransistor memory applications. Chen et al. inserted a hybrid composite comprising perovskite (MAPbBr<sub>3</sub>) NCs and PS beneath a pentacene semiconductor in a phototransistor memory (Fig. 10e).<sup>70</sup> The in situ formation of perovskite NCs in polymer matrices provided a uniform thin film in which NCs were embedded into PS matrices (Fig. 10f). Photoexcitation occurred in the NCs under exposure to irradiation, and photoinduced carriers were generated. Owing to the energy level difference between perovskite and pentacene, the holes were transferred to pentacene and served as charge carriers in the active channel, while the electrons were trapped in the noncontinuous NCs to inhibit the trapped-charge dissipation. The photo-programmed photo-memory could be erased by applying a negative gate bias to prompt hole injection from pentacene to perovskite, as illustrated in Fig. 10g. The device exhibited acceptable photoresponsivity and stable memory ratios of 10<sup>4</sup> over 120 days. The effects of the polymer matrix on the performance of transistor memory were then reported by Ercan et al. They used poly-(4-vinylphenol), PMMA, and poly(methacrylic acid) PMAA as polymer matrices blended with MAPbBr3 NCs to evaluate the

structure-performance relation in phototransistor memory.<sup>73</sup> They found that the size of NCs can be modulated by using different polymer matrices during the in situ formation because of the dissimilar chemical interactions between the host polymers and perovskite (Fig. 10h). The photoresponse, including the on/off current ratio and memory windows, increased as the size of the embedded perovskite NCs decreased (Fig. 10i). This photoresponse can be attributed to the enhanced photo-induced charge transfer across the dielectric/pentacene interface. The results reveal the importance of choosing a suitable polymer matrix for a hybrid nanocomposite and may contribute to the optimization of memory devices. In addition to evenly distributed perovskite NCs, spatially addressable NCs in an insulated polymer matrix have also been investigated. Chang et al. used PS-blockpolyethylene (PS-b-PEO) as an insulating matrix for perovskite NCs.<sup>71</sup> By manipulating the interfaces and self-assembled morphology of the floating-gate electret, they achieved ultrafast charge transfer rate, efficiency, and memory response with an acceptable memory ratio of 10<sup>2</sup> under 5 ms light exposure. With their rapid development, floating-gate electrets with polymer dots, inorganic quantum dots, and perovskite NCs may contribute to the advancement of high-performance phototransistor memory devices.

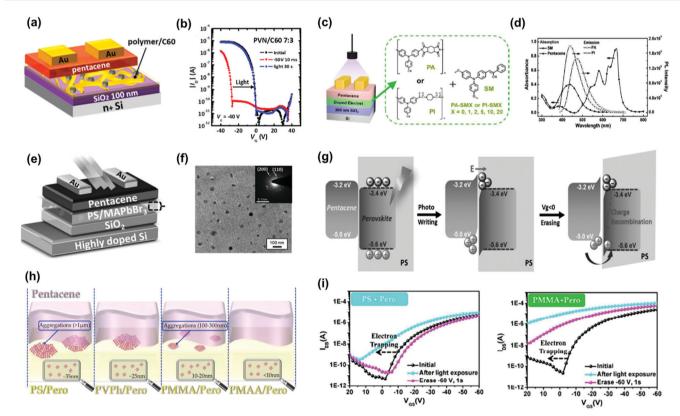

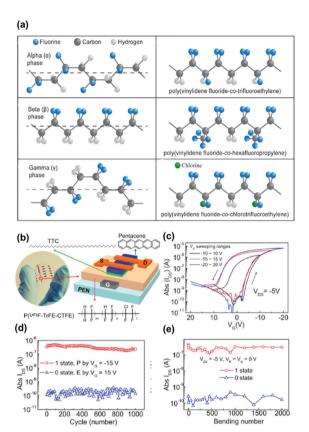

#### 3.5 Ferroelectric polymer electrets

Ferroelectric polymers are attractive dielectric materials for memory applications. Memory devices based on ferroelectric polymers offer various advantages such as low power consumption, durability, fast switching, and thermal stability. Unlike charge-storage polymer electrets, ferroelectric transistor memory (FeTM) relies on the polarization of functional groups. It exhibits spontaneous and reversible electric polarization upon the application of an external electric field and retains the polarization state after removing the electric field. The two polarizations correspond to two distinct current states of 0 and 1 for data storage. The most attractive ferroelectric polymers are fluorinated polymers consisting of a highly polar dipole, CH<sub>2</sub>CF<sub>2</sub><sup>-.74</sup> The prototypical ferroelectric polymer is polyvinylidene fluoride (PVDF), which has four crystalline phases,  $\alpha$ ,  $\beta$ ,  $\gamma$ , and  $\delta$ , as shown in Fig. 11a. Although  $\alpha$ -PVDF is the most stable phase, it constitutes a non-ferroelectric material given the absence of polarization. On the other hand,  $\beta$ -,  $\gamma$ -, and  $\delta$ phase crystals are ferroelectric, with the β phase being the easiest to obtain and most widely used PVDF. For creating the β phase, other monomers, such as trifluoroethylene (TrFE), chlorofluoroethylene, and hexafluoropropylene, are introduced for random copolymerization of PVDF. Fluorine atoms are larger than hydrogen and impart more steric hindrance while increasing the defect density. For example, with the addition of TrFE into the PVDF chain, the unit cell size increases and easily allows the formation of the  $\beta$  phase with all-trans conformation.<sup>74</sup> In addition, the copolymerization of PVDF with TrFE helps improving the polymer crystallinity, and only crystalline regions can present ferroelectricity. The dipole moments in amorphous regions have random directions and will countervail each other, leading to a net zero polarization. The properties of the ferroelectric bulk and ferroelectric/semiconductor interface have key

Fig. 11 (a) Chemical structure of alpha phase, beta phase and gamma phase conformations of poly(vinylidene fluoride), as well as the chemical structure of poly(vinylidene fluoride-co-trifluoroethylene), poly(vinylidene fluoride-co-hexafluoropropylene) and (poly(vinylidene fluoride-cochlorotrifluoroethylene)). (b) The photograph of arrays of the flexible ferroelectric OFET memory. (c) Transfer characteristics of the ferroelectric OFET with a 7 nm thick TTC passivation layer. (d) Endurance property and (e) mechanical bending durability of the device. Reproduced with permission.<sup>77</sup> Copyright 2018, Elsevier.

effects on the memory performance. Much effort has been devoted to improve the performance of FeTM regarding aspects such as mobility, operating voltages, endurance cycles, retention time, and multibit data storage, aiming to achieve practical applicability. 75,76

The thin-film morphology of a ferroelectric film is essential in the interface with semiconductors. Kang et al. applied confined crystallization to prepare a ferroelectric polymer film. The confined crystallized polymer reduced the gate leakage current and facilitated ferroelectric polarization switching.<sup>78</sup> Laudari et al. developed a textured poling method by applying a lateral electric field near the gate electrode, dramatically reducing the gate leakage current and increasing the charge transport in FeTM.<sup>79</sup> Nguyen et al. fabricated a nonvolatile FeTM device using pentacene as the semiconductor layer and poly(vinylidenefluoride-trifluoroethylene) (P(VDF-TrFE)) as the gate insulator.80 They improved the surface roughness by changing the crystallinity of the P(VDF-TrFE) film via annealing at 140 °C. A 10<sup>4</sup> on/off switching current ratio was maintained for 5000 s. On the other hand, Xu et al. deposited a long-chain alkane molecule, tetratetracontane, as a protective layer on a

poly(vinylidenefluoride-trifluoroethylene-chlorotrifluoroethylene)terpolymer (P(VDF-TrFE-CTFE)) film surface to protect the interfacial trap and improve the crystalline quality of a pentacene film (Fig. 11b).<sup>77</sup> The device could be operated under a voltage of 15 V, mobility of up to 0.5 cm<sup>-2</sup> V<sup>-1</sup> s<sup>-1</sup>, and stable programming/ erasure over 1000 cycles. They achieved a storage retention and durability of 6000 s and excellent mechanical bending durability (Fig. 11c-e). Song et al. presented an FeTM using 2,7dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) as the semiconductor layer and PMMA as the buffer layer. 81 The surface roughness of the PMMA/P(VDF-TrFE) surface was reduced from 3.6 to 2.7 nm by increasing the PMMA concentration from 0.08 wt% to 0.1 wt%. They obtained a carrier mobility up to  $5.6 \text{ cm}^{-2} \text{ V}^{-1} \text{ s}^{-1}$  and an on/off ratio of  $10^6$ . The device exhibited a switching time of approximately 3.0 ms from the off to on state. FeTM using a blended layer of ferroelectric and polymer to improve performance has also been proposed. Kim et al. fabricated FeTM using a P(VDF-TrFE)/PMMA blended buffer layer to improve the electrical performance. The memory device with the buffer layer showed an improvement by a factor of 25 in the oncurrent compared with the use of a single layer, prolonged memory retention (10<sup>3</sup> s), and a higher on/off switching current ratio of 104.

Research progress has facilitated the development of FeTM based on PVDF materials. The fabrication of PVDF-based memory devices has emerged as a promising research direction, providing a technical solution for next-generation wearable devices owing to their remarkable advantages in terms of data storage, easy fabrication, low cost, and flexibility.

# 4. Polymer based OFET memory for artificial synapses

Transistor-structured memory devices has been proposed for emulating synaptic functions of biological synapses because of their complex multilevel and dynamical plastic behaviors. Generally, synaptic transistors can be divided into four types according to their charge storage medium and operation mechanism: (1) electrolyte-gated, (2) polymer electrets-gated, (3) ferroelectric-gated, (4) floating gates. Polymeric materials play important role in their development. Besides, mimicking the synaptic functions of polymeric materials provides opportunity for realizing the ultrathin and conformable artificial synapse due to their inherent advantages, such as softness, low-temperature processability, and even biocompatibility. And this pave the way to building next-generation, wearable, intelligent electronic systems that can mimic the synaptic operations of the human brain. This section reviews the contribution of polymers as various functional components for synaptic transistors.

### 4.1 Electrolyte-gated synaptic transistors

Polymer electrets doped with ions, called organic electrolytes, have been employed as the dielectric layer in ion-gated synaptic transistors. As a gate dielectric material, thin-film transistors with electrolytes can resemble synaptic characteristics,

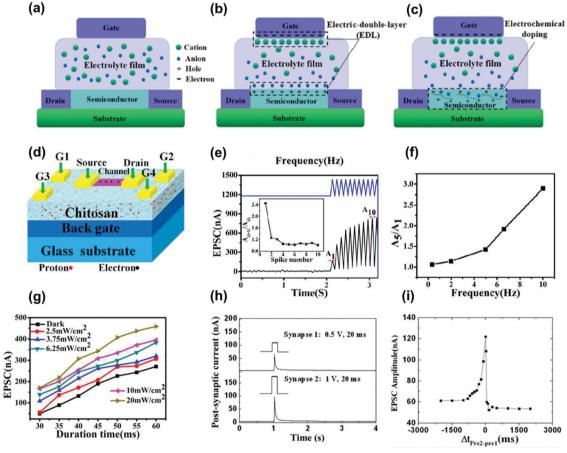

including short-term memory, long-term memory, and nonlinear summation. Fig. 12a shows a schematic of an ion-gate neuromorphic structure. The freely mobile ions in the electrolyte can be directed and concentrated under the induction of an electric field. The operation of ion-gate neuromorphic transistors is mainly divided into two types: electrostatic coupling and electrochemical doping/de-doping.19 In ion-impermeable semiconductor materials, ions move in the electrolyte and accumulate at the electrolyte/gate electrode and electrolyte/channel layer interfaces under the action of an electric field. Owing to electrostatic coupling, carriers with opposite signs and equal charges can be induced on the channel layer and electrode side, forming a dense electric double layer at the interface (Fig. 12b). Owing to the large capacitance of the electrolyte gate, the pulse voltage that must be applied to the gate can be small. Therefore, ion-gate neuromorphic transistors can achieve low power consumption when emulating synaptic activity. In ion-permeable semiconductor materials (Fig. 12c), ions can penetrate the channel layer from the electrolyte under a relatively large electric field, directly changing the channel conductance and establishing electrochemical doping. When a large electric field is applied in the reverse direction, ions that penetrate the channel layer return to the electrolyte, establishing electrochemical de-doping. <sup>19</sup> In synaptic electronics, electrostatic coupling and electrochemical doping/de-doping are commonly used to emulate short- and long-term plasticity, respectively.

A variety of organic electrolytes have been used to fabricate ion-gate neuromorphic devices. 85,86 Organic electrolyte materials can be applied to flexible devices because of their inherent characteristics, and the functional groups of organic materials can be selected according to electron and photon conduction properties required for neuromorphic devices. Moreover, polymer materials can easily achieve ion penetration under an electric field. The doped ions of an organic polymer electrolyte can penetrate deeply by trapping under an electric field given the large free volume of the polymer. Zheng et al. fabricated synaptic transistors using a chitosan polymer electrolyte as the gate dielectric, which is a cationic biopolymer

Fig. 12 (a) The distribution state of ions in the electrolyte without electric field. (b) Ions move in the electrolyte and accumulate at the electrolyte/gate electrode and electrolyte/channel layer interface under the induction of the electric field, forming an EDL. (c) lons penetrate from the electrolyte into the channel layer under the action of a large electric field to achieve electrochemical doping. Reproduced with permission. <sup>19</sup> Copyright 2021, Wiley-VCH. (d) The schematic diagram of SnO<sub>2</sub> nanowire-based neuron transistor gated by the chitosan film on FTO glass substrate. (e) EPSC measured as a function of time by applying spikes (2.0 V, 50 ms, 9t = 50 ms). (f) EPSC amplitude ratio plotted as a function of presynaptic spike frequency. (g) The light density dependent EPSC amplitude. Reproduced with permission.<sup>82</sup> Copyright 2016, The Royal Society of Chemistry. (h) EPSCs triggered by pre-synaptic spikes 1 (0.5 V, 20 ms) and pre-synaptic spikes 2 (1 V, 20 ms), respectively. (i) Measured EPSC measured plotted as a function of time is plotted as a function of  $\Delta t(p_{pre2-pre1})$  between the two pre-synaptic spikes. Reproduced with permission. <sup>83</sup> Copyright 2014, The Royal Society of Chemistry.

derived from chitin deacetylation.<sup>87</sup> This electrolyte is a nontoxic, harmless, and degradable organic material with a good electric double-layer effect. The capacitance-frequency relation of chitosan films showed that the capacitance decreased as the frequency increased owing to the formation of an electric double layer on the chitosan/metal electrode. The device exhibited a low operating voltage of 1.5 V, large switching ratio of 10<sup>5</sup>, and field-effect mobility of 8.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Gou et al. used chitosan as the gate dielectric to fabricate synaptic transistors (Fig. 12d).82 They simulated paired-pulse facilitation and high-pass filtering in the short-term memory characteristics of synapses (Fig. 12e and f). In addition, they studied the influence of photon density on postsynaptic current intensity and found that EPSC values triggered by the presynaptic pulse were gradually improved with the light intensity (Fig. 12g). Meanwhile, Wu et al. prepared a synaptic transistor on a paper substrate using chitosan as the gate dielectric material.<sup>83</sup> They simulated the short-term plasticity of synaptic transistors with functions including paired-pulse facilitation, dynamic filtering, and spatiotemporal signal processing. Fig. 12h shows the EPSC triggered by presynaptic spikes 1 (0.5 V, 20 ms) and 2 (1 V, 20 ms). Fig. 12i shows the EPSC amplitude according to

$\Delta t$ (pre2-pre1). For  $\Delta t$  = 0, both the pre- and postsynaptic neurons were simultaneously active, and the EPSC amplitude showed the largest increase over the entire  $\Delta t$  range because of the synchronous activation of both spikes. This change gradually decreased as the relative timing of both spikes increased regardless of their temporal order, mimicking the symmetry of the Hebbian learning rule.