Cite this: *Nanoscale*, 2022, **14**, 4887

## Application of patterned sapphire substrate for III-nitride light-emitting diodes

Shengjun Zhou, \*†<sup>a</sup> Xiaoyu Zhao, †<sup>a</sup> Peng Du, <sup>a</sup> Ziqi Zhang, <sup>a</sup> Xu Liu, <sup>a</sup> Sheng Liu\*<sup>b</sup> and L. Jay Guo \*<sup>c</sup>

Recent decades have witnessed flourishing prosperity of III-nitride emitters in solid-state lighting and high-resolution displays. As one of the widely used substrates, sapphire shows superiority for heteroepitaxial growth of III-nitride light-emitting diode (LED) structure, due to the advantages of stability, low cost, high mechanical strength, as well as mature fabrication technology. However, realization of efficient LEDs grown on sapphire substrate is impeded by high density of defects in epilayers and low light extraction efficiency. The emergence of patterned sapphire substrate (PSS) turns out to be a promising and effective technology to overcome these problems and enhance the LED performances. In this review, we first introduce the background and recent advances of PSS applied in III-nitride visible and ultraviolet LEDs are. Then, we summarize the fabrication methods of PSS, together with novel methods to define nanometre-scale patterned structures. We further demonstrate the effect of PSS that contributes to reduce the threading dislocation density (TDD) of epilayers in detail. Meanwhile, mechanism of light extraction efficiency enhancement by adopting PSS is presented based on numerical analysis. Next, we explore the influence of PSS structural parameters (e.g. pattern size, pattern shape and aspect ratio) on LED performances, spanning from visible to deep ultraviolet UV emission region. Finally, challenges and potential prospects in PSS for future LED development are proposed and forecasted as well.

Received 14th December 2021,

Accepted 9th February 2022

DOI: 10.1039/d1nr08221c

[rsc.li/nanoscale](http://rsc.li/nanoscale)

<sup>a</sup>Center for Photonics and Semiconductors, School of Power and Mechanical Engineering, Wuhan University, Wuhan 430072, China. E-mail: zhousj@whu.edu.cn

<sup>b</sup>The Institute of Technological Sciences, Wuhan University, Wuhan, 430072, China.

E-mail: victor\_liu63@vip.126.com

<sup>c</sup>Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI, 48109, USA. E-mail: guo@umich.edu

†These authors contributed equally to this work.

**Shengjun Zhou**

Prof. Shengjun Zhou is a Professor at School of Power and Mechanical Engineering, Wuhan University. He received his Ph.D. degree from Shanghai Jiao Tong University in 2011. From 2014–2015, he was a research fellow at University of Michigan, Ann Arbor. His research interests focus on the growth and device fabrication of GaN-based LEDs. He has authored over 83 publications in peer-reviewed journals and conference proceedings.

**Xiaoyu Zhao**

Xiaoyu Zhao received his M.S. degree in 2020 from Institute of Semiconductor, University of Chinese Academy of Sciences. He is now a Ph.D. candidate at School of Power and Mechanical Engineering, Wuhan University. His research interests focus on the development of high-efficiency long-wavelength LEDs.

red for InN, showing great potential in wide range of applications.<sup>6–12</sup> For instance, white LEDs combining blue or UV LEDs with wavelength-converting phosphors have great advantages over traditional incandescent and fluorescent lighting sources by providing lower energy consumption, longer lifetime, higher brightness, and environmental sustainability.<sup>13–15</sup> Integration of red, green and blue (RGB) micro-LEDs has been highlighted not only for high color rendition white illumination, but for full-color displays, wearable devices, high-brightness augmented-reality (AR) and visual reality devices.<sup>16–19</sup> Recently, III-nitride micro-LEDs play an important role in the biomedical area, due to its outstanding biocompatibility, low heating property and stability.<sup>20,21</sup> Moreover, there has been unprecedented development of UV-LEDs due to potential applications in UV sensing, optical data storage, sterilization.<sup>22–26</sup>

Nowadays, metal-organic chemical vapor deposition (MOCVD), molecular beam epitaxy (MBE) and hydride vapor phase epitaxy (HVPE) are commonly implemented methods for the epitaxial growth of LED structures.<sup>27–32</sup> Relying on the substrate used and the material grown, epitaxial growth can be categorized as homoepitaxial and heteroepitaxial growth. Nevertheless, the former is hindered by the high cost of large-scale single crystals as substrates despite obtaining high-quality films.<sup>33</sup> Heteroepitaxial growth on foreign substrate, such as sapphire, silicon and silicon carbide,<sup>34–37</sup> is commercially available with a large market. Among them, sapphire has attracted much attention not only for its low cost, but various sizes, optical transmittance, excellent physical and chemical stability as well. However, LEDs grown on *c*-plane sapphire substrate suffer from high density of defects in epilayers, which arises from the large mismatch of lattice constant and thermal expansion coefficient between sapphire and GaN, degrading external quantum efficiency (EQE) and further device performance.<sup>28</sup> Besides, EQE of LEDs is also related to light-extraction efficiency (LEE). Because of the considerable refractive index difference between epitaxial structure and air, only a few photons could transmit outside, while a large number of photons are trapped inside the epitaxial structure.<sup>38</sup>

Peng Du

*Peng Du received his B.S. degree in 2020 from Wuhan University. He is currently pursuing the master's degree with the School of Power and Mechanical Engineering, Wuhan University. His research interests focus on the simulation, fabrication, and design for AlGaN-based deep ultraviolet LEDs.*

These trapped photons are reabsorbed and eventually transformed to heat, accelerating the device degradation. To tackle these problems, patterned sapphire substrate (PSS) technology, which features artificial structures,<sup>29,39,40</sup> has attracted great attention and achieved tremendous progress owing to its superiority over flat sapphire substrate (FSS) in several aspects.

(1) Patterns on PSS can be designed and fabricated with different structural parameters.

(2) Unlike normal ELO technique, there is no additional growth interruption during the growth process on PSS.

(3) PSS is a versatile platform applicable for growth of visible and UV LED structures.

(4) PSS effectively reduces the density of threading dislocation in epilayers, resulting in an increased internal quantum efficiency (IQE).

(5) PSS enhances the LEE by increasing the probability of light scattering, reducing light trapping in the LED.

Besides the aforementioned advantages, the roles of strain relaxation and suppression of quantum-confined Stark effect (QCSE) are also reported for PSS.<sup>41</sup> Nowadays, benefiting from PSS, excellent achievements have been made from visible III-nitride LEDs to UV LEDs: EQE of blue LED increases to 84.3% and correspondingly fabricated white LED has a high luminous efficacy of 249 lm W<sup>–1</sup> at an injection current of 20 mA.<sup>13</sup> Blue micro-LED grown on PSS sustains a high EQE above 40% even on the ultrasmall scale (0.01 mm<sup>2</sup>)<sup>42</sup> and red micro-LED exhibits high light output power density of 1.76 mW mm<sup>–2</sup> at 50 A cm<sup>–2</sup>.<sup>43</sup> As for UV LED, threading dislocation density (TDD) was reduced by approximately 50% and LEE was enhanced by 6.8% when PSS was further replaced by patterned sapphire with silica array, thereby leading to increment of 23.4% in EQE.<sup>24</sup>

As remarkable breakthroughs have been achieved in this field, there lacks a systematic review of the subject, which inspires this review (Fig. 1). We first introduce the recent advancements of PSS used for LEDs with emphasis on its advantage. Then, we present normal procedures and main methods of PSS fabrication together with emerging techniques. Next, we provide a detailed discussion of mechanisms

Ziqi Zhang

*Ziqi Zhang received his M.S. degree in 2021 from Shandong University. He is currently a Ph.D. candidate at School of Power and Mechanical Engineering, Wuhan University. His research interests focus on the fabrication of high-efficiency LEDs.*

Fig. 1 Application of patterned sapphire substrate for III-nitride light-emitting diodes.

that PSS enables the reduction of dislocation density in epi-layers and the enhancement of LEE both for visible and UV LEDs. Afterwards, PSSs with different structure parameters and their influence on LED performance are presented. Finally, we discuss the challenges on the present stage and put forward the future directions of the PSS technology for efficient and high-performance LEDs.

## 2. Fabrication methods

With the development of PSS, fabrication methods of PSS have become critical issues. In this section, the related fabrication methods including etching processes and pattern transfer techniques for micrometre-scale and nanometre-scale patterns are introduced.

Sheng Liu

Prof. Sheng Liu received his B.S. degree from Nanjing University of Aeronautics and Astronautics, China in 1983, and Ph.D. degree from Stanford University, USA in 1992. He is currently a professor at the School of Power and Mechanical Engineering, Wuhan University, with joint appointment at the Institute of Technological Science. His current research interests focus on the areas of LEDs, MEMS, optoelectronics, sensor and electronics packaging. He has authored or co-authored more than 300 publications in peer-reviewed journals and conference proceedings.

He is a Fellow of IEEE and a Fellow of ASME. He serves on the Editorial Board of *Science Bulletin* and *Microsystems & Nanoengineering*.

### 2.1 Etching methods

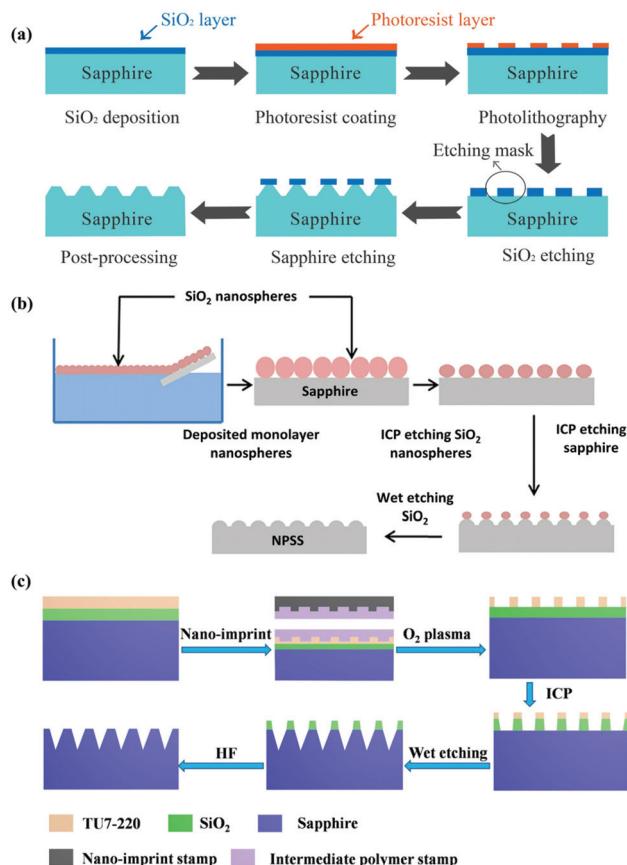

Fig. 2a shows the commonly used fabrication process for PSS, in which dry etching and wet etching are the main methods to transfer the pattern of mask onto the sapphire.

**2.1.1 Dry etching.** Several dry etching techniques such as inductively coupled plasma (ICP), and reactive ion etching (RIE) are applied to fabricate micrometre-scale PSS (MPSS). Before etching, a layer of mask such as Ni,  $\text{SiN}_x$ ,  $\text{SiO}_2$ , etc. is deposited on the top of sapphire, and then photoresist is spin-coated onto the sample.<sup>46–50</sup> By standard photolithography, a pattern is defined on the photoresist layer. The mask layer is then opened by ICP or RIE. Finally, the pattern is transferred from the mask onto the sapphire by ICP or RIE. The etching gas,  $\text{BCl}_3/\text{Cl}_2$ , is commonly used.<sup>51,52</sup> PSS with specified parameters can be obtained by controlling the flux of the etching gas and etching time.

Hsu *et al.*<sup>46</sup> deposited a 500 nm-thick Ni layer on the *c*-plane of the sapphire substrate, and then the stripe-shaped Ni patterns were defined along the [1–100] direction by standard lithography. By selecting the flow rate ratio  $\text{BCl}_3/(\text{Cl}_2 + \text{BCl}_3)$  properly, the 3  $\mu\text{m}$ -width and 100 nm-depth stripe patterns were prepared, and the corresponding spacing between two stripes was 3  $\mu\text{m}$ . At 20 mA, 35% enhancement in light output power (LOP) of LED grown on the PSS was achieved compared with that of LED grown on FSS, which may be ascribed to the reduced TDD and the improved LEE.<sup>53</sup>

Chang *et al.* fabricated LED on hemisphere-shaped PSS by combining photolithography, ICP and RIE. Firstly, the patterned polymethyl methacrylate (PMMA) was obtained by photolithography.<sup>47</sup> By using the thermal reflow technique, the spacing between PMMA patterns was reduced to form the hemisphere-shaped PMMA. The PMMA patterns were subsequently transferred to the  $\text{SiN}_x$  film by RIE, and the sapphire substrate was then etched by  $\text{BCl}_3$  plasma using ICP. Finally,

L. Jay Guo

L. Jay Guo is a Professor at the University of Michigan, Ann Arbor. Prof. Guo's research covers polymer-based photonic devices and sensor applications, flexible transparent conductors, nanophotonics, hybrid photovoltaics and photodetectors, to nanomanufacturing technologies, and are contributed by students from Electrical Engineering and Optics, Macromolecular Science & Engineering, Applied Physics, and Mechanical Engineering. He has over 270 journal publications, and a H-index of 80 (by google scholar). He recently completed his Associate Editorship of *Optica* and currently an Associate Editor of *IEEE J. Photovoltaics*, and serves on the Editorial Advisory Board of *Advanced Optical Materials*.

**Fig. 2** (a) The fabrication process flow for PSS. (b) The fabrication process flow for NPSS by self-assembled SiO<sub>2</sub> nanosphere monolayer template. Reproduced with permission.<sup>44</sup> Copyright 2014, American Institute of Physics Publishing. (c) The fabrication process flow for NPSS by nanoimprint lithography. Reproduced with permission.<sup>45</sup> Copyright 2016, Springer Nature Publishing Group.

the hemisphere-shaped PSS with 4.3  $\mu\text{m}$ -diameter and 0.5  $\mu\text{m}$ -spacing was produced. What's more, by adjusting the thickness ratio between SiN<sub>x</sub> and PMMA, researchers also fabricated the LED on stripe-shaped PSS. They found that the GaN grown on hemisphere-shaped and stripe-shaped PSS demonstrated similar TDDs, but the LOP of LED grown on hemisphere-shaped PSS was 13% higher than that of LED grown on stripe-shaped PSS. The improved LEE is owing to the inclined facets of hemisphere-shaped PSS. Wang *et al.* used standard lithography technology combined with the dry etching process to fabricate a periodic hole pattern array on *c*-plane sapphire.<sup>48</sup> The diameter of the hole was 3  $\mu\text{m}$  and the corresponding spacing between two patterns was also 3  $\mu\text{m}$ . The LED grown on the proposed PSS with an optimum pattern depth (1.5  $\mu\text{m}$ ) demonstrated  $\sim$ 21% enhancement in LOP at 20 mA compared with that grown on FSS.

We have combined BCl<sub>3</sub>/Ar plasma chemistry and SiO<sub>2</sub> mask to fabricate patterns with several micrometres period on sapphire substrate.<sup>54</sup> It is noted that the increase of BCl<sub>3</sub> gas flow in pure BCl<sub>3</sub> gas chemistry rapidly increased sapphire etch

rates, which reached the maximum value when gas flow was 50 sccm. Then, the further increased BCl<sub>3</sub> gas flow slowly decreased the etch rate. Moreover, the etch rate increased as the operating pressure decreased. Additionally, we have investigated the effect of input process parameters such as the ICP power/RF power, operating pressure, and Cl<sub>2</sub>/BCl<sub>3</sub> gas mixing ratio on the etch characteristics of GaN films.<sup>55</sup> The optimum ICP etching conditions (300 W ICP power/100 W RF power, 70 sccm of total flow rates, 90% Cl<sub>2</sub>/10% BCl<sub>3</sub>) for defining the mesa during the LED device fabrication were presented, which was also feasible for patterning of the sapphire substrate using the same plasma chemistry. Based on these findings, we applied thermally reflowed photoresist technique and BCl<sub>3</sub>-based ICP etching process to fabricate cone-shaped PSS for achieving highly efficient and reliable high power LEDs.<sup>56</sup>

**2.1.2 Wet etching.** Apart from dry etching, wet etching is also applied to fabricate PSS. The sapphire substrate covered with an etching mask is etched with a mixed acid solution during the wet etching process.<sup>57-59</sup> A relatively high etching temperature is required, due to the fact that sapphire is highly resistive to acids at room temperature.<sup>60</sup>

Li *et al.*<sup>61</sup> prepared LED on pyramid-shaped PSS fabricated by wet etching. The sapphire substrate with patterned SiO<sub>2</sub> mask was immersed into H<sub>2</sub>SO<sub>4</sub> solution and the constant etching temperature was 250 °C. Three types of PSS with average sizes of 4.8, 4.0 and 2.2  $\mu\text{m}$  were prepared. They found that the dihedral angle between *c*-plane sapphire and side-plane of the pyramid increased with the decreasing size of the pyramid. The highest LOP was obtained in the LED with the smallest size of PSS.

Wang *et al.* investigated the effect of V-shaped PSS produced by the wet etching process on the LED performances.<sup>62</sup> Firstly, a SiO<sub>2</sub> layer with a thickness of 300 nm was prepared on the sapphire surface, and then the SiO<sub>2</sub> layer was etched by standard lithography. By controlling the etching time, the sapphire substrate was then etched at 400 °C with stripe SiO<sub>2</sub> as mask and H<sub>2</sub>SO<sub>4</sub> as the etching solution. The residual SiO<sub>2</sub> layer was removed by HF solution. The ridge width and period of PSS were 3.5 and 6.5  $\mu\text{m}$ , respectively. They found that the V-shaped PSS effectively reduced the contact area between the GaN layer and substrate during the epitaxial growth, leading to reduced TDDs and enhanced crystalline quality of epilayers. Furthermore, Wu *et al.*<sup>63</sup> found that the crystalline quality of GaN became better with the decreasing pattern spacing of V-shaped PSS because most of the growth of GaN was initiated from *c*-plane. However, it was difficult for GaN to grow on the sapphire when the pattern spacing was less than 0.41  $\mu\text{m}$ , resulting in the degradation of crystalline quality of GaN.

In general, dry etching technique is capable of producing an anisotropic profile more efficiently compared with wet etching.<sup>64</sup> However, dry etching suffers from the inherently strong physical component so that it has a low etch-selectivity between sapphire and the etching mask. In addition, ion bombardment may lead to contamination and damage to the surface of the sapphire substrate, which is detrimental to the

quality of epitaxial layers.<sup>65</sup> By contrast, wet etching possesses relatively high etch-selectivity and reduces the cost of fabricating PSS as compared to dry etching.

## 2.2 Nanometre-sized patterns transfer techniques

**2.2.1. Nanosphere and anodic aluminium oxide techniques.** Although micrometre-scale patterns can be fabricated by conventional photolithography together with the etching process, the implementation of nanometre-scale patterns requires techniques with higher resolution. Laser holography,<sup>66,67</sup> electron beam lithography<sup>68</sup> and focused ion beam<sup>69</sup> were proposed to realize the nanometre-scale patterns, but they may take the advantage of performance improvement to be offset by the increased fabrication cost and low throughput.<sup>70,71</sup> In this regard, nanosphere,<sup>72,73</sup> and anodic aluminium oxide (AAO) techniques<sup>74,75</sup> have been adopted to fabricate the nanometre-scale PSS (NPSS) owing to their low cost and high throughput.

Zhang *et al.* proposed a self-assembly technology where a layer of  $\text{SiO}_2$  nanospheres with a diameter of 600 nm was coated on the sapphire substrate.<sup>44</sup> Then the  $\text{SiO}_2$  nanospheres serving as the dry-etching mask were shrunk by the ICP etching process with  $\text{CF}_4$  (Fig. 2b).  $\text{SiO}_2$  nanospheres with different intervals (0, 50, and 120 nm) were obtained by controlling different etching time (0, 90, and 180 s). Chen *et al.* fabricated NPSS by nanosphere lithography.<sup>73</sup> The polystyrene spheres were spun uniformly onto the surface of sapphire substrate, then the sapphire substrate was etched by using a mixture of  $\text{Cl}_2$  and  $\text{BCl}_3$  gases. The diameter, depth, and spacing of the proposed PSS were 450, 150 and 50 nm, respectively. Results of high-resolution X-ray diffraction and etch-pit density measurement inferred the improved crystalline quality of GaN epilayers. In addition, the LOP was increased by 30% and 11% for the LED on NPSS compared with the ones on PSS and on MPSS, respectively.

**2.2.2 Nanoimprint lithography.** Nanoimprint lithography (NIL) is of interest for fabricating nanopatterns with high-throughput and high-resolution, which avoids limitations set by light diffraction or beam scattering, as well as expensive equipment in conventional techniques.<sup>76–78</sup> NIL has been applied to fabricate nanoscale patterns on the sapphire substrate for LEDs<sup>45,79</sup> and beneficial for other optoelectronic devices, including organic LEDs and solar cell as well.<sup>80–83</sup> The fabrication process flow for NPSS *via* NIL is shown in Fig. 2c. First,  $\text{SiO}_2$  layer is deposited on the sapphire substrate serving as a hard mask. Second, imprint resist (IR) is spin-coated on the top of  $\text{SiO}_2$  layer. After that, IR is imprinted by patterned hard mold with subsequent process of heating and UV curing. After removing the residual IR layer, RIE is used to transfer the defined pattern on the  $\text{SiO}_2$  layer. Finally, sapphire substrate is wet-etched and  $\text{SiO}_2$  mask is removed. Nanoimprinting finds its applications in PSS. For instance, NIL and ICP etching were used to fabricate uniform and periodic NPSS with hexagonal protrusion patterns.<sup>84</sup> Blue LED fabricated on such substrate achieved 2-fold and 2.8-fold increase in PL and EL intensity, respectively, compared with LED on FSS.

## 3. Effects of PSS on LEDs

It is well-known that EQE is a key performance parameter for III-nitride LEDs, which can be calculated by:

$$\text{EQE} = \text{IQE} \times \text{LEE} \quad (1)$$

Among various strategies proposed to improve EQE, the PSS technique has attracted much attention, because it can improve the IQE and LEE simultaneously.<sup>85</sup> In this section, we discuss the effects of PSS on LED performances from two aspects.

### 3.1 Dislocation density reduction by PSS

Heteroepitaxial growth of III-nitrides on sapphire substrate gives rise to strained films consisting of a high density of defects due to the large mismatch in the lattice and thermal expansion coefficients between the *c*-plane sapphire substrate and epilayers. Several types of defects have been reported, including threading dislocation,<sup>86</sup> stacking fault,<sup>87</sup> point defect,<sup>88</sup> V-pit,<sup>89,90</sup> trench defects<sup>91</sup> and misfit dislocations.<sup>92</sup> In particular, dislocations and point defects serve as non-radiative recombination centres that introduce the defect levels into the bandgap of III-nitrides and reduce the possibility of radiative recombination by capturing carriers, finally degrading the IQE of LEDs.<sup>93–96</sup> Moreover, fundamental bottlenecks including efficiency droop<sup>97</sup> and green gap<sup>98</sup> encountered by III-nitride LEDs are found to be closely related with dislocation density, which adversely affects IQE and thus degrades optoelectronic properties of LED devices.

To reduce the TDD in epilayers, a number of growth techniques have been investigated, consisting of epitaxial lateral overgrowth (ELO) technology and its derivatives, pendoepitaxy (PE) and facet-controlled epitaxial lateral overgrowth (FACELO).<sup>100–102</sup> Generally, in the conventional ELO, GaN layer with thickness of several micrometres is first grown on substrate and then  $\text{SiN}_x$  or  $\text{SiO}_2$  patterned masks are used to realize subsequent selective growth process.<sup>103</sup> This technology, however, requires a growth interruption, which is time-consuming and easily introduces contaminations.<sup>104</sup> In contrast, PSS technology that could be prepared before the epitaxial growth leads to single continuous growth process without contamination induced by mask. Employment of PSS enables significant reduction of TDDs at the interface between epilayers and substrate as well as LEE enhancement of LEDs.

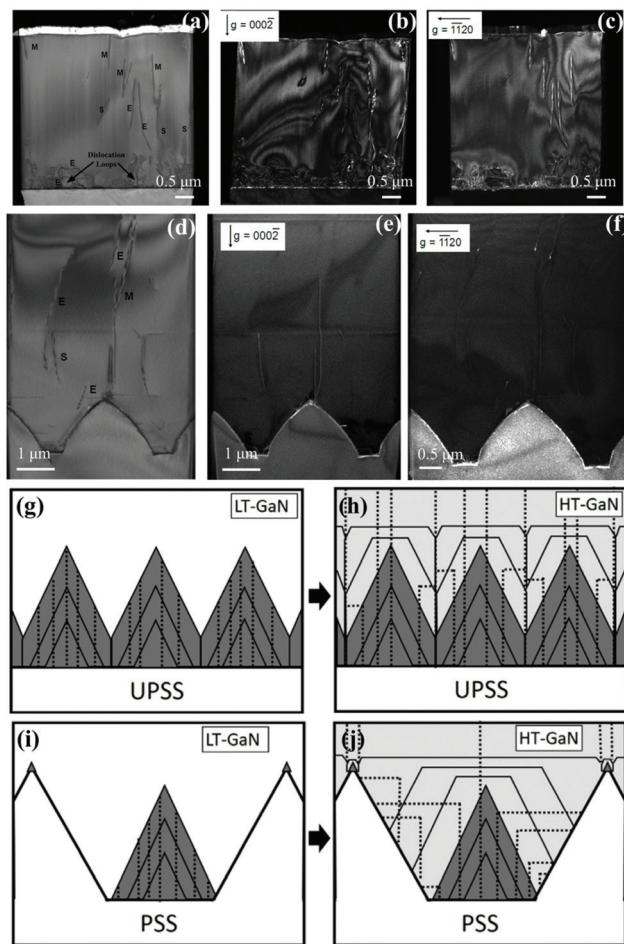

Using low-temperature-(LT)-deposited GaN or AlN as buffer layer is an important method to diminish the lattice mismatch in the early development of LEDs.<sup>1,3</sup> Through transmission electron microscopy (TEM) observation in Fig. 3a–f, we found that density of both screw dislocation and edge dislocation in GaN epilayer grown on PSS was much less than that in GaN epilayer grown on FSS.<sup>56</sup> Compared to LED grown on FSS, LED grown on PSS showed higher sub-threshold forward-bias voltage and lower reverse leakage current, resulting in an enhancement in device reliability. Moreover, by adopting stripe-shaped  $\text{SiO}_2$  distributed current blocking layer, LOP of

**Fig. 3** TEM images of GaN epitaxial layer grown on (a–c) FSS and (d–f) PSS. Reproduced with permission.<sup>56</sup> Copyright 2015, Elsevier. Formation and propagation mechanism of dislocation with (g–h) FSS and (i–j) PSS. Reproduced with permission.<sup>99</sup> Copyright 2018, Elsevier.

LED grown on PSS was further increased by 13%, which was attributed to the uniform current spreading.

Nie *et al.* explained mechanisms of dislocation formation and propagation in LED structures grown on FSS and PSS.<sup>99</sup> For the case of FSS (Fig. 3g and h), dislocations originate from the internal pyramids and pyramid boundaries, while dislocations generated from the boundary coalescence could not be annihilated with the subsequent high temperature growth mode. In contrast, for the case of PSS (Fig. 3i and j), more spacings are provided for epitaxially lateral overgrowth (ELOG), and the number of initial islands is reduced, resulting in dislocation bending and minimization of island coalescence. V-defects associated with dislocations could be well minimized by adopting PSS. Moreover, the thickness of LT-GaN is found to affect the subsequent growth of GaN films due to the different nucleation sites during three-dimensional (3D) growth on PSS.

Another choice to improve the crystalline quality is to take the advantages of *ex situ* sputtered AlN nucleation layer (NL) over LT-GaN/AlN from the aspect of a lower TDD in epilayers

and one-step growth. Chang *et al.* compared the GaN growth on high aspect ratio PSS with *in situ* LT-AlN NL and *ex situ* sputtered AlN NL.<sup>105</sup> With *in situ* LT-AlN NL, the GaN growth occurs on the *c*-plane and pattern region, and the laterally overgrown GaN from both regions subsequently coalesces, causing the creation of irregular voids. However, with the sputtered AlN NL, a different growth behaviour is observed that the sputtered AlN NL not only increases vertical growth from *c*-plane region, but also suppresses lateral growth from the cone region, leading to high-quality GaN epilayers without void formation and enhancement in LOP by 47.7%. Moreover, by adjusting growth modes, different GaN growth behaviours occurred on the PSS with sputtered AlN NL.<sup>106</sup> Under “tsunami” growth mode, GaN grows into truncated pyramid shape, which facilitates the dislocation bending from flat area toward inclined planes, and especially the dislocation propagation in grains on the conical surface is inhibited. However, under “rising tide” growth mode, dislocations on the conical surface have the possibility to extend upward. Accordingly, the GaN layer grown under “tsunami” growth mode has a lower TDD than that grown under “rising tide” growth mode.

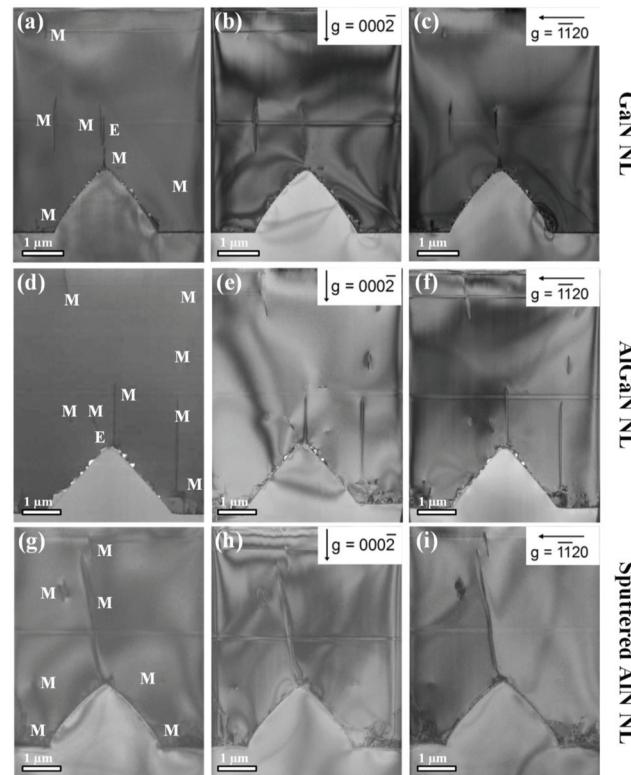

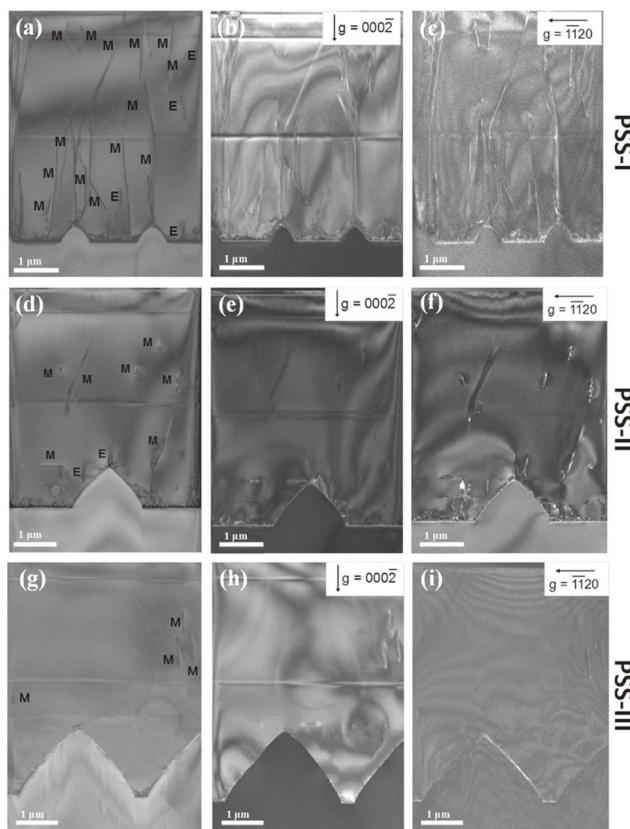

We reported and compared UV LEDs grown on *ex situ* sputtered AlN NL/PSS, *in situ* LT-GaN NL/PSS and LT-AlGaN NL/PSS.<sup>107</sup> It was found that the UV LED on *ex situ* sputtered AlN NL/PSS exhibited the lowest TDD among three types of UV LEDs (Fig. 4a–i). The LOP of the UV LED on *ex situ* sputtered

**Fig. 4** Cross-sectional TEM images of UV LEDs grown on (a–c) LT-GaN NL/PSS, (d–f) LT-AlGaN NL/PSS and (g–i) sputtered AlN NL/PSS. The edge (E) and mixed (M) type dislocations are marked. Reproduced with permission.<sup>107</sup> Copyright 2017, Springer Nature Publishing Group.

AlN NL/PSS was 11.2% higher than that of the UV LEDs on *in situ* LT-AlGaN NL/PSS, which could be attributed to the reduced TDD in the active region grown on *ex situ* sputtered AlN NL/PSS. The results indicated that the introduction of *ex situ* sputtered AlN NL/PSS was an effective method to enhance the performance of UV LED.

By using *ex situ* sputtered AlN NL/PSS, we further investigated the effect of PSS size on the GaN-based UV LED performance.<sup>108</sup> The bottom diameter/height/spacing values of cone-shaped PSS were 0.73  $\mu\text{m}$ /0.46  $\mu\text{m}$ /0.27  $\mu\text{m}$ , 1.8  $\mu\text{m}$ /1.1  $\mu\text{m}$ /0.2  $\mu\text{m}$ , and 2.7  $\mu\text{m}$ /1.7  $\mu\text{m}$ /0.3  $\mu\text{m}$  for PSS-I, PSS-II, and PSS-III, respectively. The fill factor was defined as the ratio of the pattern area to the total area. The calculated fill factors for PSS-I, PSS-II, and PSS-III were 0.4, 0.65 and 0.71, respectively. It was found that the increasing pattern size of PSS could lead to the reduced TDD (Fig. 5a–i). That was because the flat *c*-plane area of the bottom of PSS decreased when the size of PSS increased, thereby resulting in the decrease in the initial density of GaN islands and the longer lateral growth time of GaN epilayers. As a result, the LOP of UV LED grown on PSS with fill factor of 0.71 was 131.8% higher than that of the UV LED grown on PSS with a fill factor of 0.4.

Fig. 5 Cross-sectional TEM images of UV LEDs grown on (a–c) PSS I, (d–f) PSS II and (g–i) PSS III. The screw (S), edge (E), and mixed (M) type dislocations are marked. Reproduced with permission.<sup>108</sup> Copyright 2017, Institute of Physics.

The effect of isoelectronic Al doping in GaN buffer layer on UV LED crystalline quality and optoelectronic properties was also investigated.<sup>109</sup> It was found that the overall TDD and the background carrier concentration could be reduced in the isoelectronically Al-doped GaN buffer layer as compared to undoped GaN buffer layer. Especially, the screw-type dislocation density was effectively reduced by isoelectronic Al doping. With optimum isoelectronic Al doping concentration of 0.18% in GaN buffer layer, UV LED exhibited 7.6% increase in LOP due to the improved crystalline quality.

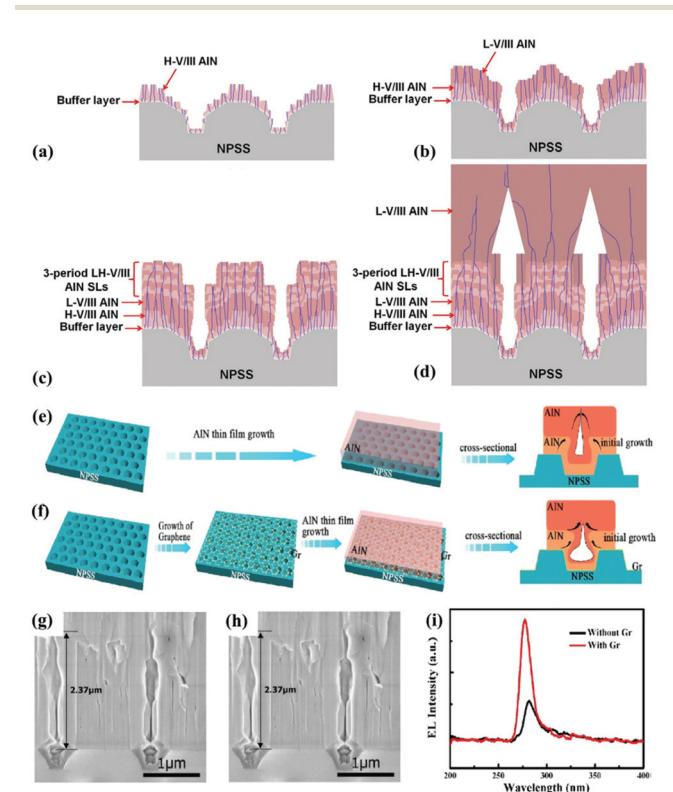

To straightforward understand the dislocation annihilation mechanism, schematic illustrations of growth evolution for ELOG of AlN epilayers on NPSS are exhibited in Fig. 6.<sup>110</sup> The dislocations are marked as blue colour. The V/III ratio strongly affects the surface mobility of Al adatoms that usually accompanies the transition of the growth mode between 3D and 2D mode.<sup>111</sup> At initial growth stage in Fig. 6a, AlN with high V/III ratio (H-V/III AlN) is grown on NPSS dominated by 3D growth mode. The high V/III ratio facilitates the formation of island crystals with abundant crystal boundaries to suppress the elongation of dislocations.<sup>112</sup> However, there are still a number of dislocations existing in H-V/III AlN layer. Therefore, AlN

Fig. 6 (a–d) Schematic illustrations of growth evolution for AlN epilayers on NPSS. Reproduced with permission.<sup>110</sup> Copyright 2018, Elsevier. Schematic diagrams of AlN growth on (e) bare NPSS and (f) Gr/NPSS. Cross-sectional schematic diagrams of AlN films grown on (g) bare NPSS and (h) Gr/NPSS. (i) EL spectra of the DUV-LEDs with and without the graphene interlayer. Reproduced with permission.<sup>116</sup> Copyright 2019, American Institute of Physics Publishing.

layer with low V/III ratio (L-V/III AlN) is deposited on the H-V/III AlN because the low V/III ratio facilitates the 2D growth of AlN epilayer by smoothening the surface. Owing to the transition of growth mode from 3D to 2D, some dislocations are terminated by merging with each other in Fig. 6b. After that, a 3-period AlN superlattices with alternating high and low V/III ratios (LH-V/III AlN SL) structure is deposited on the L-V/III AlN. Because SL layers can bend dislocations,<sup>113</sup> most dislocations are eliminated in the 3-period LH-V/III AlN SL structure in Fig. 6c. In addition, some dislocations could also be terminated on the internal surface of arrow-shaped ELOG voids in Fig. 6c and d. Ultimately, the thick L-V/III AlN is deposited on AlN SLs to flatten the AlN epilayer surface. It is noted that few dislocations eventually propagate through the thick L-V/III AlN in Fig. 6d.

Newly emerging quasi-van der Waals epitaxial (QvdWE), which opens the door to growing high-quality III-nitride materials on hybrid substrates made of 2D materials and sapphire, has been adopted to overcome lattice mismatch limitation and achieve flexible devices.<sup>114,115</sup> Chang *et al.* reported the growth of high-quality AlN films on NPSS by graphene (Gr)-assisted QvdWE.<sup>116</sup> It is found that AlN exhibits the 3D longitudinal island growth mode and the lateral coalescence of the AlN nucleation islands is relatively slow, hard to cover the NPSS at a thin growth thickness (Fig. 6e and g). In contrast, because Al adatoms diffuse easily on the surface of Gr/NPSS, AlN prefers the lateral 2D growth mode, leading to rapid and lateral coalescence with a thin and flat AlN film (Fig. 6f and h). Benefiting from the Gr interlayer, a reduction of TDD and 2.6 times enhancement in EL intensity have been achieved in DUV-LEDs grown on Gr/NPSS (Fig. 6i).

### 3.2 LEE enhancement by PSS

**3.2.1 Mechanism.** The large refractive index difference between GaN ( $n = 2.5$ ) and air ( $n = 1$ ) will lead to total internal reflection (TIR) at GaN/air interface. The incident angle of light at the GaN/air interface can be calculated using Snell's law:

$$n_{\text{GaN}} \sin \phi = n_{\text{air}} \sin \Phi \quad (2)$$

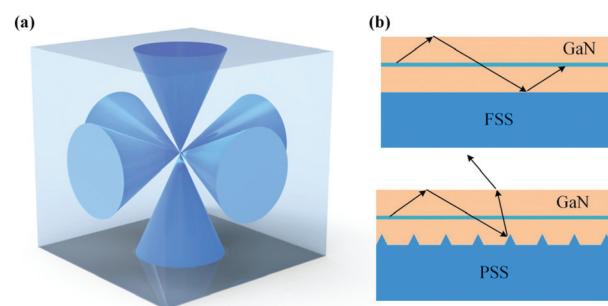

For LEDs, critical angle ( $\phi_c$ ) of TIR is calculated to be  $23.6^\circ$  when the  $\Phi$  is  $90^\circ$ . In other words, light with an incident angle less than  $23.6^\circ$  can escape from GaN into air, whereas light with an incident angle exceeding  $23.6^\circ$  will be reflected back. Similarly, the  $\phi_c$  of TIR at GaN ( $n = 2.5$ )/sapphire ( $n = 1.7$ ) interface can be estimated to be  $42.8^\circ$ , indicating that light will also be reflected back at GaN/FSS interface. The light escape cone is defined by the  $\phi_c$  of TIR, which takes the luminous point as the vertex and  $2\phi_c$  as the apex angle, as is shown in Fig. 7a. Only lights emitted inside the light escape cone can escape from semiconductor chip into air.

For LEDs grown on sapphire substrate, the polarization modes of light can be characterized as transverse-electric (TE) polarized mode and transverse-magnetic (TM) polarized mode by the direction of electric field relative to the  $c$ -axis. The

Fig. 7 Schematic of (a) light escape cone for LED and (b) light trajectories in LEDs with FSS and PSS.

visible and near-infrared lights are mainly TE polarized, where the electric field vector is perpendicular to  $c$ -axis.<sup>117</sup> However, for UV lights and particularly for deep UV lights, TM-polarized lights increase with the increment of Al composition in AlGaN QWs or decrement of emission wavelength, where the electric field vector is parallel to  $c$ -axis. Compared with TE-polarized lights, TM-polarized lights are affected by TIR more greatly, due to large incident angle caused by lateral propagation mode.<sup>118</sup> In addition, the p-GaN layer used for ohmic contact exhibits a strong absorption of UV lights.<sup>119,120</sup> These detrimental factors cause the light to be trapped in semiconductor chip and finally reabsorbed by epilayers or electrodes, thereby deteriorating the light extraction of LEDs. However, the light scattering effect of PSS can modify the light path, which will raise the probability of light entering into the escape cone, as shown in Fig. 7b. As a result, more lights can propagate into air and thus improve the LEE of LEDs.<sup>29,40</sup>

**3.2.2 Simulation methods.** Generally, ray-tracing and finite-difference time-domain (FDTD) methods are widely used to numerically investigate the parameters of PSS patterns (*e.g.* geometry, spacing, and size) that affect the LEE of LEDs. The classical ray-tracing is focused on the behaviours of optical rays, including reflection, transmission, and light absorption.<sup>121</sup> It is worth noting that the ray-tracing method is an approximate theory, which will lose accuracy when structural size of patterns on PSS is smaller than the wavelength or even reaches the nano scale.<sup>122</sup> The FDTD method is based on wave optics, which directly divides the space with fine mesh for solving Maxwell's equations to investigate the wave propagation.<sup>123</sup> This method can be used for calculation involving subwavelength structures with complex shape. However, compared to ray-tracing method, the simulation areas of FDTD method is much smaller (typically a few micrometres), due to the limited computational memory and simulation-time.<sup>124</sup> The LEE can be calculated by:<sup>125,126</sup>

$$\text{LEE} = \frac{P_{\text{out}}}{P_{\text{total}}} \quad (3)$$

where  $P_{\text{out}}$  is the emitted optical power out of the LED and  $P_{\text{total}}$  is the total optical power generated by the light source.

## 4. Influence of structural parameters of PSS on LED properties

As mentioned above, patterns on PSS could be fabricated with different sizes (from microscale to nanoscale), different shapes (cone, hemisphere, stripe, volcano, *etc.*) and other related structural parameters (diameter, height, spacing, slanted angle, *etc.*). Herein, we will describe representative examples, comparing and illustrating the influence of PSS structural parameters on the LED performances based on experimental and simulation results, which are summarized in Table 1.

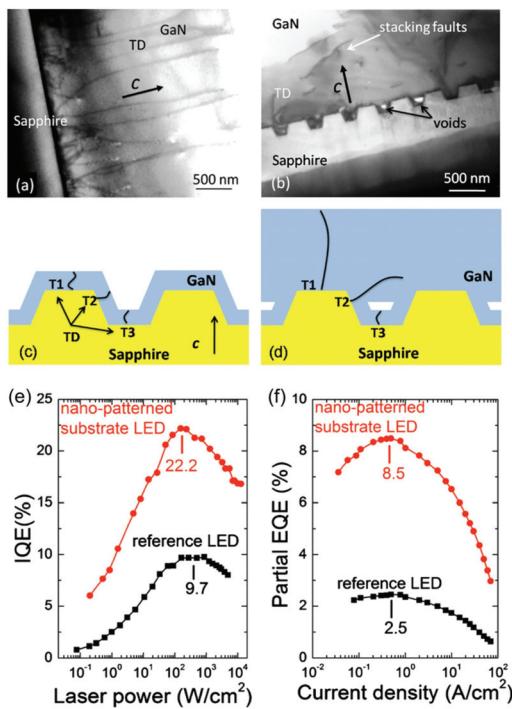

### 4.1 LEDs on PSS with micrometre-scale and nanometre-scales patterns

NIL was used to fabricate NPSS with hexagonal array of cylindrical holes, whose diameter was 250 nm and period was 450 nm.<sup>127</sup> From the TEM analysis (Fig. 8a and b), a lower TDD of  $3.6 \times 10^8 \text{ cm}^{-2}$  was found at NPSS/GaN interface and the existence of void indicated the overgrowth in lateral direction. The mechanism of TD formation is illustrated as follows

(Fig. 8c and d). TDs generated from the bottom of the etched sapphire ( $T_3$ ) are mostly interrupted by voids, and TDs generated from the inclined plane change direction to propagate within the growth plane ( $T_2$ ). Only TD generated from the unetched region of NPSS ( $T_1$ ) will propagate to the active region. Benefiting from the decreased TDD, both IQE and EQE of NPSS LED were increased as compared to FSS LED (Fig. 8e and f). Furthermore, photonic crystal effect is possibly induced at GaN/PSS interface. The photonic crystal is an ordered, periodic structure made up of materials with alternating refractive indices, in which light propagation could be effectively controlled.<sup>128,129</sup> In this NPSS strategy, the LEE enhancement is not only related to the light scattering, but also to the constructive interference of scattered light, which contributes to better LED performance compared to MPSS and FSS.<sup>130,131</sup>

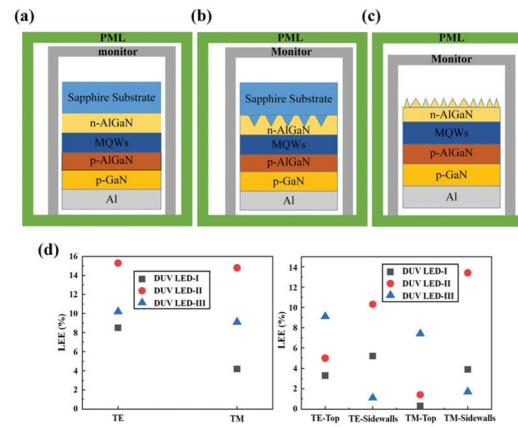

Except for visible LEDs, NPSS also enhances LEE of DUV LEDs, due to the increment of extraction for TM-polarized lights. In our previous study, we have investigated the LEE of DUV LEDs using FDTD method.<sup>132</sup> The results showed that NPSS could enhance the LEE of TM-polarized lights significantly, as compared to FSS. Furthermore, the LEE of flip-chip

**Table 1** Summary of the impact of PSS structural parameters on LED properties

| Shape                   | Pattern size ( $\mu\text{m}$ )                  | Properties                                                                     | Ref. |

|-------------------------|-------------------------------------------------|--------------------------------------------------------------------------------|------|

| Cylindrical hole        | Diameter/period: 0.25/0.45                      | TDD reduction: 44%<br>EQE enhancement: 260% (20 mA)                            | 127  |

| Cone                    | Height/bottom diameter/interval: 0.5/0.7/0.3    | LEE enhancement: 78%                                                           | 132  |

| Cone                    | Height/bottom diameter/interval: 1.5/2.5/0.5    | Reduced TDD                                                                    | 56   |

| Cone                    | Height/bottom diameter/interval: 0.15/0.45/0.05 | Enhanced crystalline quality<br>EQE Enhancement: 30% (20 mA)                   | 134  |

| Cone                    | Height/bottom diameter/interval: 1.5/2.7/0.2    | TDD reduction: 76%                                                             | 135  |

| Cone                    | Height/bottom diameter/interval: 1.7/2.7/0.3    | Reduced TDD<br>EQE enhancement: 130% (20 mA) (compared with smaller-sized PSS) | 108  |

| Cone                    | Height/bottom diameter/interval: 1.2/3.0/6.0    | Reduced TDD                                                                    | 49   |

| Cone                    | Height/bottom diameter/interval: 1.5/3.0/1.0    | LOP enhancement: 34% (20 mA)                                                   | 161  |

| Cone                    | Height/bottom diameter/interval: 1.6/2.65/3.0   | LEE enhancement: 60%<br>LOP enhancement: 82% (20 mA)                           | 150  |

| Stripe                  | Groove width/spacing/depth: 3.0/5.0/0.9         | Reduced TDD (compared with smaller-depth PSS)                                  | 137  |

| Stripe                  | Groove width/ridge width/depth: 3.0/3.0/1.5     | LOP enhancement: 20% (20 mA)                                                   | 138  |

| Pillar                  | Height/diameter/period: 0.1/0.11/0.25           | EQE enhancement: 30% (100 mA)                                                  | 146  |

| Volcano                 | Diameter/spacing/depth: 2/1.0/1.5               | LEE enhancement: 62%                                                           | 139  |

| Volcano                 | Diameter/spacing/depth: 0.4/1.0/0.5             | TDD reduction: 30%<br>LEE enhancement: 21% (compared with cone-shaped NPSS)    | 141  |

| Volcano                 | Diameter/spacing/depth: 5.0/9.0/0.4             | LEE enhancement: 103%<br>LOP enhancement: 40% (350 mA)                         | 142  |

| Volcano                 | Diameter/spacing/depth: 2.2/3.0/0.6             | LEE enhancement: 21%                                                           | 79   |

| Hemisphere              | Diameter/spacing/height: 0.5/0.2/0.2            | EQE enhancement: 27% (20 mA)                                                   | 148  |

| Hemisphere              | Diameter/spacing/height: 3.5/0.8/1.2            | LOP enhancement: 14% (350 mA)                                                  | 162  |

| Spherical cap           | Radius/height/edge spacing: 3.4/2.78/1.7        | EL intensity enhancement: 15% (compared with cone-shaped PSS)                  | 154  |

| Concave hole            | Average diameter/depth: 0.2/0.1                 | LEE enhancement: 60%                                                           | 74   |

| Concave hole            | Diameter/depth/spacing: 3.0/1.5/3.0             | EQE enhancement: 20% (20 mA)                                                   | 147  |

| Hexagonal hole          | Diameter/period: 0.65/1.0                       | Reduced TDD                                                                    | 45   |

| Hexagonal hole          | Depth/period: 0.2/1.0                           | TDD reduction: 92.65% (compared with pillar-shaped NPSS)                       | 144  |

| Double-side hole        | Diameter/depth/spacing: 3.0/1.0/3.0             | LOP enhancement: 53% (350 mA)                                                  | 158  |

| Truncated pyramid       | Height/bottom diameter/interval: 0.4/0.4/0.4    | EQE enhancement: >50% (20 mA)                                                  | 41   |

| Double-side hemisphere  | Diameter/height/spacing: 0.16/0.05/0.1          | TM-polarized LEE enhancement: 11.2 times                                       | 159  |

| Moth-eye microstructure | Height/bottom diameter/interval: 1.75/2.5/3.0   | LEE enhancement: 200%                                                          | 160  |

The “TDD reduction”, “EQE enhancement”, “enhanced crystalline quality”, “reduced TDD” and “LEE enhancement” statements in column “properties” refer to the III-nitride films or LEDs grown on PSS compared with those grown on FSS if no special instructions.

**Fig. 8** Cross-sectional TEM of the epitaxial GaN/sapphire interface on (a) FSS and (b) NPSS. Schematics show (c) early and (d) late phases of the TD (T1, T2, T3) formation on NPSS. (e) IQE as a function of excitation power density. (f) EQE as a function of current density for NPSS LED. Reproduced with permission.<sup>127</sup> Copyright 2011, American Institute of Physics Publishing.

LED on NPSS was estimated to be about 15%, which was ~50% higher than that of flip-chip DUV LED with rough n-AlGaN surface (Fig. 9). Recently, it is reported that the combination of NPSS and meshed p-GaN can remarkably increase the LEE for both the TE-polarized and the TM-polarized light.<sup>133</sup>

NPSS shows better LEE due to the increased number of patterns that increase the probability of light scattering. However, smaller pattern size of PSS not always leads to better LED performance. In the situation of GaN grown on PSS-2  $\mu\text{m}$  (diameter/spacing/depth: 2  $\mu\text{m}$ /2  $\mu\text{m}$ /1.5  $\mu\text{m}$ ), PSS-3  $\mu\text{m}$  (diameter/spacing/depth: 3  $\mu\text{m}$ /3  $\mu\text{m}$ /1.5  $\mu\text{m}$ ), NPSS (diameter/spacing/depth: 450 nm/50 nm/150 nm) and FSS corresponding to Fig. 8a-d, GaN film on NPSS shows a higher etch-pit density and broader full-width at half-maximums (FWHMs) of the  $\omega$  scan rocking curve for both (002) and (102) planes.<sup>134</sup> It indicates that the crystalline quality does not show an absolute dependence on the pattern size, and epilayers grown on MPSS show better crystal quality than NPSS in some cases.<sup>135</sup>

As the parameters of patterns for sapphire substrate will remarkably influence LEE, the LEE of LEDs on PSS is expected to be further improved when the pattern size varies from the micrometre to nanometre. However, it is noted that the strong diffraction induced by near-wavelength-scale patterns will not enhance the LEE of LEDs effectively.<sup>136</sup> On the contrary, micro-scale patterns at a specific aspect ratio (defined as the ratio of

**Fig. 9** Simulation model of (a) flip-chip DUV LED on FSS (DUV LED-I), (b) flip-chip DUV LED on NPSS (DUV LED-II), and (c) flip-chip DUV LED with roughed n-AlGaN surface (DUV LED-III). (d) Simulated LEE of DUV LED-I, DUV LED-II, and DUV LED-III. Reproduced with permission.<sup>132</sup> Copyright 2020, Institute of Physics.

the structure height to the structure width) and subwavelength-scale patterns will contribute to marked enhancement of LEE.

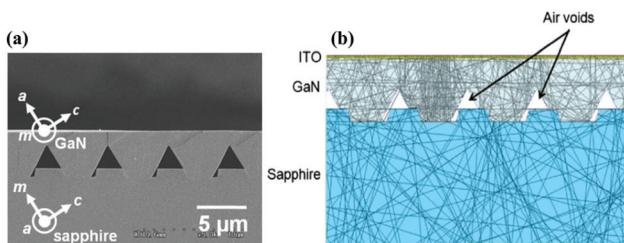

## 4.2 LEDs on PSS with various shapes

**4.2.1 Cone-shaped PSS.** Soh *et al.*<sup>49</sup> prepared blue LEDs on cone-shaped PSS and the corresponding etching mask was a monolayer of polystyrene microsphere. The cone-shaped PSS featured 1.2  $\mu\text{m}$ -height and 3  $\mu\text{m}$ -cone base width. The estimated IQEs for LEDs grown on the PSS and FSS were 56% and 50%, respectively. This enhancement was associated with the reduced TDDs in GaN films on PSS. The growth mode difference between GaN grown on cone-shaped PSS and GaN grown on FSS was explored.<sup>50</sup> The GaN growth on cone-shaped PSS was only initiated from the etched basal surface corresponding to the *c*-plane. However, the growth of GaN on flat-top-shaped PSS started both on the unetched and etched regions simultaneously, thus increasing the time required for forming a smooth surface over the patterned regions. We formed the air voids structure between cone-shaped PSS and GaN layer by combining laser scribing with  $\text{H}_3\text{PO}_4$ -based hot chemical etching.<sup>52</sup> The simulation results based on ray-tracing method showed that the LEE of LEDs on PSS with embedded air voids was significantly enhanced.

**4.2.2 Stripe-shaped PSS.** Pan *et al.* prepared PSS with stripes along the  $[1-100]_{\text{sapphire}}$  and  $[11-20]_{\text{sapphire}}$  orientations as well as with 0.2, 0.5, and 0.9  $\mu\text{m}$ -deep grooves.<sup>137</sup> They found that the increased integrated PL intensity and reduced etch pit densities could be realized when the groove depth increased from 0.2 to 0.9  $\mu\text{m}$ . A deeper groove may lead to a wider lateral growth region and thus the crystal quality of epilayers was improved. What's more, due to the anisotropic growth, two major lateral growths could proceed near the two edges of the ridge for the stripe along the  $[1-100]_{\text{sapphire}}$  direction, resulting in a lower TDD and higher LOP in LED. Lee

*et al.* fabricated stripe-shaped PSS with parallel stripes along the  $[1-100]_{\text{sapphire}}$  direction.<sup>138</sup> They demonstrated that LOP of UV LED on stripe-shaped PSS was increased by 20% in comparison with FSS. It is noteworthy that stripe-shaped PSS is particularly important for semipolar LEDs fabrication, which will be introduced in section 4.5.

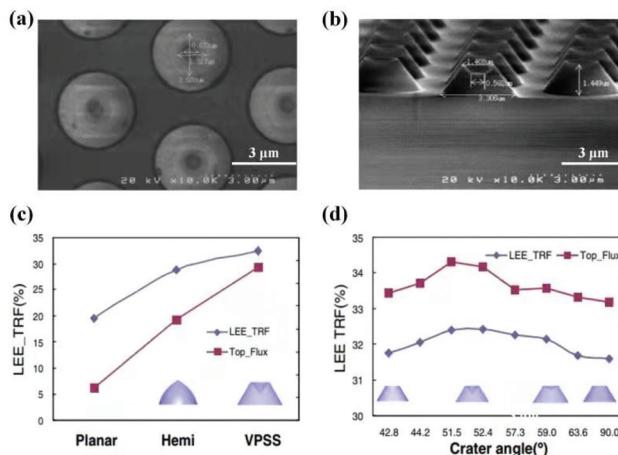

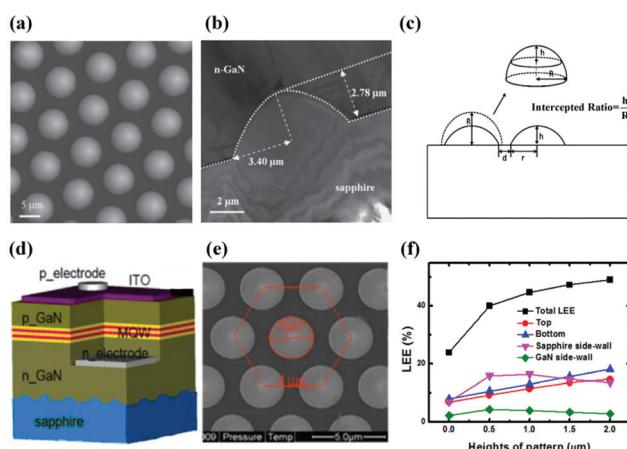

**4.2.3 Volcano-shaped PSS.** The volcano-shaped PSS was first demonstrated by Kim *et al.* and fabricated using conventional photolithography process.<sup>139</sup> Compared to hemispherical/cone-shaped PSS, volcano-shaped PSS favours better scatter efficiency due to the more faceted sidewalls. The crater angle of the volcano is found to affect LEE through ray-tracing simulation. The volcano-shaped PSS with optimized crater slope angle ( $\sim 50^\circ$ ) was used to further enhance the LEE of UV LEDs emitting at 380 nm, which was 1.6 times larger than that of LEDs on hemispherical-shaped PSS (Fig. 10).

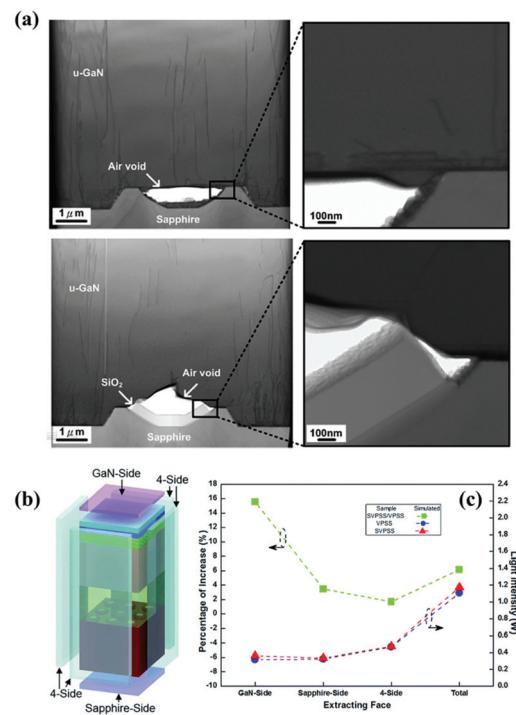

After that, simplified fabrication methods of volcano-PSS, such as colloidal monolayer templating and NIL were employed.<sup>79,140,141</sup> Embedding  $\text{SiO}_2$  layer in volcano-shaped PSS, which suppressed the GaN growth, could result in fewer threading dislocations in GaN epilayer.<sup>142</sup> Conical air voids were formed in the crater, which decreased the residual compressive strain and improved LEE. The simulation results based on FDTD method showed that the conical air voids could turn the light path towards the top surface, due to the large difference in refractive index at the air/GaN interface. Meanwhile, the silica layer can mitigate the refractive index mismatch between the GaN and air, thereby improving LEE of light trapped in the conical air voids (Fig. 11).

**4.2.4 Comparison of different shaped PSS.** Trapezoid-shaped and cone-shaped PSS were used to fabricate LEDs.<sup>143</sup> The growth mechanism is much different for epilayers grown on two PSSs. Because of the larger tilted surface, cone-shaped PSS favours the lateral coalescence of GaN epilayers that tend to grow on the window region than wing region at the initial

Fig. 10 (a-b) SEM images of volcano-shaped PSS. (c-d) Simulated LEE as a function of crater angle and the LEE of FSS, hemispherical and volcano-shaped PSS. Reproduced with permission.<sup>139</sup> Copyright 2010, Institute of Physics.

Fig. 11 (a) TEM images of LEDs grown on volcano-shaped PSS (VPSS) and volcano-shaped PSS with embedded  $\text{SiO}_2$  (SVPSS). (b) Schematic of different receiver positions in the simulation. (c) Light intensity and percentage increase in light intensity of LEDs grown on the VPSS and SVPSS. Reproduced with permission.<sup>142</sup> Copyright 2015, Royal Society of Chemistry.

stage as well as the TDs bending. This further leads to the strain relaxation and improved crystalline quality. Liu *et al.* compared growth behaviors of AlN on hole-shaped and pillar-shaped NPSS.<sup>144</sup> TDD of AlN film grown on the hole-shaped NPSS was  $4.87 \times 10^8 \text{ cm}^{-2}$ , which was over one order of magnitude lower than that of AlN film grown on the pillar-shaped NPSS ( $6.63 \times 10^9 \text{ cm}^{-2}$ ). The coalescence area was considered as the key factor for high-quality AlN epilayer. They demonstrated that AlN film on the hole-shaped NPSS possessed smaller coalescence area than that on the pillar-shaped NPSS. Therefore, a relatively high IQE of up to 73.9% was achieved in AlGaN MQWs on hole-shaped NPSS. Furthermore, the residual strain of AlN on hole-shaped NPSS was found to be tensile after complete coalescence, because NPSS patterns could directly influence the strain states associated with crystal merging behaviors during ELOG of AlN film.<sup>145</sup> As a result, AlN on hole-shaped NPSS with tensile strain facilitated the realization of high-quality epilayer with a relatively flat surface for fabrication of high-performance UV LEDs.

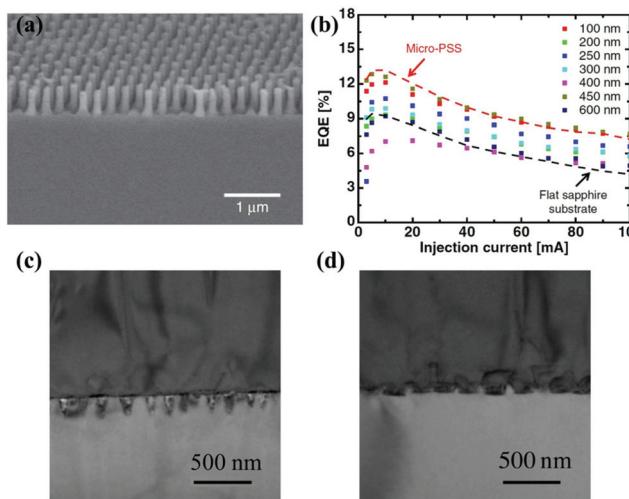

### 4.3 LEDs on PSS with various structural parameters

**4.3.1 Height/depth.** For pillar-shaped PSS, different pattern heights were fabricated by Okada *et al.* to investigate the influence on LEDs (Fig. 12a).<sup>146</sup> It was found that pattern height affected the surface emission of LEDs and highest emission

**Fig. 12** (a) SEM image of NPSS with pillar height of 600 nm. (b) EQEs of LED chips on nano-PSSs as a function of injection current. Reproduced with permission.<sup>146</sup> Copyright 2013, Institute of Physics Publishing. TEM images of the GaN thin films grown on (c) high aspect ratio and (d) low aspect ratio NPSS. Reproduced with permission.<sup>149</sup> Copyright 2016, Elsevier.

intensity was obtained at a pillar height of 250 nm. The utilization of such PSS improved LEE and efficiency droop of LEDs, indicating the advantage of PSS over FSS (Fig. 12b). Hole-shaped PSSs were fabricated with the same diameter of 3 μm, spacing of 3 μm and varying etching depths from 0.5 to 1.5 μm.<sup>147</sup> Among them, PSS with etching depth of 1.5 μm was found to achieve best LED performance with EQE of 14.1%. Besides, LED on PSS showed 63% improvement in the emission intensity compared to LED on FSS.

**4.3.2 Diameter.** Zhang *et al.* prepared NPSS with various hole diameters by changing the ICP etching conditions, corrosive liquid ingredients and wet etching time.<sup>45</sup> They found that benefiting from the NPSS and effective control of lateral growth, AlN epilayer on NPSS completely coalesced in a low thickness compared to AlN on MPSS. Experimental results show that crystalline quality of AlN grown on NPSS could be greatly improved by adopting optimized hole diameter of 650 nm. Almost all the TDs generated from the AlN/NPSS interface could be eliminated *via* bending TDs by image force.

**4.3.3 Aspect ratio.** The aspect ratio reflects the relationship between the height (depth) and diameter of PSS patterns. Different aspect ratios (depth/diameter) of concave NPSS were prepared using dry etching with an AAO etching mask.<sup>74</sup> LED on high ratio aspect NPSS had inferior luminous intensity due to the void formation that caused the emitted photons to remain trapped inside the LED structure. In contrast, the inclined sidewall of low ratio aspect concave NPSS contributed to the increased GaN coverage area and suppressed the void formation, eventually resulting in the more efficient LED grown on such NPSS. Kao *et al.* fabricated hemispherical-shaped NPSS with different aspect ratios (diameter/height) from 2 to 2.5 *via* NIL.<sup>148</sup> The LOP of LEDs on NPSS increased

from 12.6 to 14.4 mW and EQE increased from 19.4% to 23.5% (@20 mA) with the increased aspect ratio, arising from the enhanced LEE.

Aspect ratio of NPSS was demonstrated to induce different growth behaviours and improve the crystal quality.<sup>149</sup> For NPSS with high aspect ratios (height/diameter: 2) shown in Fig. 12c, GaN growth started from both the flat-top and bottom of patterns. Nevertheless, the quick-merging GaN obstructed the continuous GaN growth on the bottom of patterns, leading to the void formation. Consequently, TDs generated from the bottom of patterns were prevented. As for the NPSS with low aspect ratio (height/diameter: 0.7) in Fig. 12d, the growth on the bottom and top of the patterns took place simultaneously until the GaN film filled the whole patterns without voids. The competition of lateral growth and vertical growth increased edge-type TDD. Accordingly, high aspect ratio NPSS induced a higher proportion of lateral growth, thereby enabling the better crystal quality due to TD bending. Besides, high aspect ratio NPSS improved electrical properties including mobility and concentration in GaN films in comparison with low aspect ratio NPSS and bare sapphire.

**4.3.4 Spacing.** Zhang *et al.* investigated the effect of the pattern spacing on the LED performance.<sup>44</sup> NPSSs with various spacings of with 0, 50, and 120 nm were fabricated using self-assembled SiO<sub>2</sub> nanosphere monolayer template. The LEE of LEDs was found to first increase and then decrease with the increasing spacings. Compared to LEDs on FSS, the EQEs of LEDs on NPSS with 0, 50 and 120 nm-spacing exhibit an enhancement of 43.3%, 50.6%, and 39.1%, respectively. QCSE in MQWs could be suppressed by shortening the pattern spacing, arising from the compressive strain relaxation with shorter spacing.

LEEs of blue LEDs grown on truncated pyramidal shaped-NPSS with various spacing (200, 400, 600, and 800 nm) were in the range of 38% to 42%, which were higher than that of LEDs grown on FSS (~29%).<sup>41</sup> LED grown on the 200 nm-spacing NPSS presented the maximum EQE of 54% at 25 mA, while the maximum EQE of LED grown on FSS was 35% at 49 mA.

**4.3.5 Symmetry.** The pattern symmetry of PSS also influences the LED performance. Two types of PSS symmetry including square lattice and hexagonal lattice arrangement were fabricated.<sup>150</sup> Owing to the higher symmetry of PSS with hexagonal lattice arrangement (HLAPSS), LED grown on HLAPSS shows relaxed compressive strain more than that on PSS with square lattice arrangement (SLAPSS). Besides, compared to SLAPSS, HLAPSS results in weaker QCSE in MQWs, which alleviates the efficiency droop and leads to higher LOP of LEDs.

**4.3.6 Slanted angle.** For triangle pyramidal-shaped PSS, different slanted angles could be achieved by controlling the wet etching time.<sup>151</sup> The crystalline quality and optoelectronic properties of LEDs on PSS were improved with decreasing slanted angle from 57.4° to 31.6°. It was attributed to the larger lateral growth area of GaN with decreased slanted angle of patterns, thereby improving the crystalline quality. In addition, the LEE increased with decreasing slanted angle. As

a result, LED on PSS with the slanted angle of 31.6° exhibited the highest light intensity and LOP.

#### 4.4 Comprehensive comparison of LEDs on PSS with different structural parameters

The improvement of LEE using PSS is attributed to light scattering effect, which will be influenced by the geometric parameters of patterns. Jang *et al.* theoretically investigated pattern shapes (cylindrical, conic, and hemispherical patterns) and sizes (height and diameter) of PSS based on the ray-tracing method, pointing out that the LED on hemispherical PSS (1.5 μm-height and 4.5 μm-diameter) showed the best light extraction efficiency.<sup>152</sup> Another optimization of hemispherical PSS by combining ray-tracing and FDTD methods has implied that the optimal radius for the hemispherical patterns is around the emission wavelength of the devices.<sup>153</sup> The hemispherical patterns can modulate the angles of reflection and transmission, which reduces incidence angles of light at GaN/air and sapphire/air interfaces and thereby improved the light extraction. Wang *et al.* proposed spherical cap-shaped PSS based on the hemispherical PSS.<sup>154</sup> They confirmed that spherical cap-shaped PSS with specific intercepted ratio and edge spacing could improve the LEE of LED more effectively, as compared to hemispherical PSS (Fig. 13a-c).

Moreover, the cone-shaped PSS is widely applied. It has been reported that the LEE of blue LEDs (~455 nm) grown on cone-shaped PSS was increased with the pattern height, whereas the LEE tended to be saturated when height was over 1.5 μm due to the reduction of emission from the sidewall (Fig. 13d-f).<sup>155</sup> Additionally, LEE of LEDs with cone-shaped PSS mainly hinged on the microstructure surface slope, which increased with increasing slope and reached a plateau when the slope exceeded 0.6.<sup>156</sup>

Fig. 13 (a) SEM and (b) TEM images of spherical cap-shaped PSS and (c) schematic of spherical cap-shaped PSS with specific intercepted ratio ( $h/R$ ) and edge spacing. Reproduced with permission.<sup>154</sup> Copyright 2013, Institute of Physics. (d–e) Schematic of LED with cone-shaped PSS and simulated LEE as a function of pattern heights. Reproduced with permission.<sup>155</sup> Copyright 2011, John Wiley and Sons.

We have reported that microstructures (cone, truncated cone, hemisphere, and pyramid) on the top surface of sapphire substrate can enhance the LEE of flip-chip blue micro-LEDs *via* designing their shapes and heights.<sup>157</sup> However, we also suggest that surface texture is less efficient than the PSS for increasing the LEE in an encapsulated LED. This is because the effect of surface texture is almost eliminated, due to the small refractive index difference between sapphire substrate and encapsulation. Furthermore, the double-side PSS was reported to enhance the LEE of LEDs.<sup>158</sup> Notably, the double-side PSS with macrodome-shaped array were numerically analyzed using FDTD method, which can achieve ~2.6 times and ~11.2 times enhancement in LEE of TM-polarized lights for 230 and 280 nm DUV LEDs, respectively.<sup>159</sup> What is more, the moth-eye microstructure on the backside of sapphire substrate can significantly weaken the TIR at the sapphire/air interface and enlarge the light extraction angle, which approximately doubled the LEE of DUV LEDs.<sup>160</sup>

#### 4.5 Semipolar III-nitride LED on PSS

III-nitride LEDs grown on *c*-plane sapphire suffer from QCSE owing to the strong built-in polarization field, which reduces the electron–hole wavefunction overlap and the radiative recombination rate, thereby severely decreasing the IQE.<sup>163</sup> To overcome this problem, bulk GaN substrate has been confirmed to be successful for the growth of efficient semipolar LED. The bulk GaN is typically prepared by HVPE or ammonothermal growth and subsequently sliced to desired orientation as free-standing GaN substrate. Considering the high fabrication cost and limited size available, it is not practical for mass production to satisfy commercial application demand. Therefore, pursuing appropriate foreign substrates for epitaxial growth is highly desirable. Semipolar GaN could be selectively grown on the sidewalls of stripe-shaped PSS,<sup>164,165</sup> similar as GaN grown on the inclined sidewalls of stripe-patterned silicon.<sup>166</sup>

Song *et al.* achieved purely nitrogen polar semipolar (20–21) GaN epilayers on the inclined *c*-plane sidewalls of patterned (22–43) sapphire substrates.<sup>167</sup> A 490 nm LED fabricated on (20–21) GaN showed a reduced blueshift compared to LED grown on *c*-plane GaN. To grow high-quality semipolar GaN, Ge doping was introduced during the growth.<sup>87</sup> Ge doping was found to suppress the occurrence of N-polar GaN (000–1) facets, leading to the elimination of SFs generated in (000–1) facet. Blue LED grown on SF-free similar GaN exhibited a similar LOP as the LED on GaN bulk substrate. Currently, (20–21) blue LED on PSS was reported to exhibit IQE up to 52%.<sup>168</sup> It is well known that high Indium content is required for LEDs with long-wavelength emission. Inevitably, indium clusters form in InGaN QWs because of the spinodal decomposition, which severely affects the uniformity of QWs. Previous work by Li *et al.* illustrated In-cluster-free (11–22) GaN by controlling the nucleation facet size to around 500 nm and optimizing three consecutive procedures to form air voids.<sup>169</sup> A record BSF density of  $70 \text{ cm}^{-1}$  and TD density of  $5 \times 10^7 \text{ cm}^{-2}$  were achieved.

Okada *et al.*<sup>170</sup> evaluated the LEE of semipolar (11–22) green LED on *r*-plane (1–102) PSS by ray-tracing method (Fig. 14). The results showed that the air voids between the GaN and *r*-plane PSS acted as a light-scattering structure, which reflected larger number of rays towards the top surface. As a result, the LEE of LED on the *r*-plane PSS was 68.5%, which was higher than that of the LED (60.0%) on PSS without air voids. Later, efficient semipolar (11–22) green micro-LED was fabricated, which showed a smaller blueshift than *c*-plane LED and especially a size-independent EQE of 2%, paving a way for large-area display application.<sup>171</sup>

Polarized phosphor-free white semipolar LEDs on (20–21) GaN/patterned sapphire template has been presented, which showed a LOP of 3.9 mW at 100 mA and especially a high 3 dB modulation bandwidth of 660 MHz for visible light communication application.<sup>172</sup> The light radiation distribution pattern of white LED could be defined by the pattern morphology of PSS, leading to better white-light package efficiency and uniform illumination.<sup>173,174</sup> Besides, semipolar green micro-LED showed small blue-shift and size-independent peak EQE of 2%. An interesting strategy combining semipolar micro-LED with perovskite nanocrystals was proposed for both visible light communication and full-color display.<sup>175</sup>

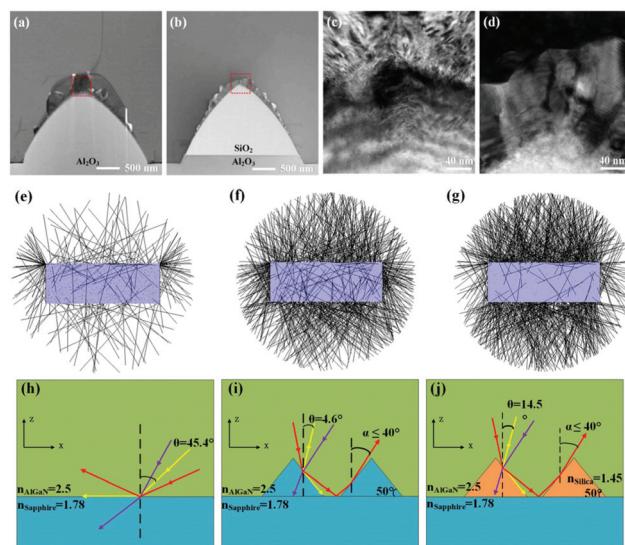

#### 4.6 PSS derivatives

**4.6.1 Patterned sapphire with silica array.** Our previous study has demonstrated that replacing the sapphire patterns with silica array is an effective way to improve the crystal quality and the LEE.<sup>24</sup> Experimental results show reduced TDD in the epilayers grown on patterned sapphire with silica array (PSSA) due to preferable vertical growth mode and reduced misfit at the coalescence boundary. Cross-sectional scanning transmission electron microscopy (STEM) images in Fig. 15a–d elucidate the growth behaviors of AlGaN epilayer on PSS and PSSA. As the AlGaN epilayer grows, most of pre-existing dislocations formed at the initial stage will be bent and finally be terminated on the surface of silica cone patterns. Compared to PSS, PSSA can effectively prevent pre-existing dislocations in AlGaN epilayer sequentially propagating upward. By comparison, the parasitic crystals on the AlN/Al<sub>2</sub>O<sub>3</sub> cone patterns are larger. The dislocations are observed on the boundary of parasitic crystals on the cone patterns surface (Fig. 15a). In

Fig. 14 (a) Cross-sectional SEM images of (11–22) GaN layer on *r*-plane PSS. (b) Ray tracing result of (11–22) LED structure on *r*-plane PSS with embedded air voids. Reproduced with permission.<sup>170</sup> Copyright 2011, John Wiley and Sons.

Fig. 15 Cross-sectional STEM images of AlGaN grown (a) on PSS and (b) PSSA. (c) Enlarged STEM images of the marked areas in (a) and (d) that in (b). Cross-sectional ray-tracing images of top-emitting UV LEDs on (e) FSS, (f) PSS, and (g) PSSA. Schematic illustration of light trajectories in top-emitting UV LEDs on (h) FSS, (i) PSS, and (j) PSSA. Reproduced with permission.<sup>24</sup> Copyright 2019, Elsevier.

Fig. 15c, the enlarged STEM image of parasitic crystals on AlN/Al<sub>2</sub>O<sub>3</sub> cone patterns is dominated by moiré fringes and bright/dark contrast due to the misfit and strain localization. Unlike the parasitic crystals on AlN/Al<sub>2</sub>O<sub>3</sub> cone patterns, those on AlN/SiO<sub>2</sub> cone patterns show columnar grain structure in Fig. 15d. The dislocations are injected from the stress concentration edge to relax some misfit strain. Benefiting from the reduced TDD and enhanced LEE, EQE of UV LEDs on PSSA is 2 times higher than that of devices on the FSS and increased by 26.1% as compared to the devices on PSS at 150 mA. Owing to the larger refractive index contrast at the cone-shaped silica/sapphire interface, PSSA reflects more light rays into the escape cone on the top facet to improve the LEE of top-emitting UV LEDs. The light trajectories in top-emitting UV LEDs on FSS, PSS, and PSSA are shown in Fig. 15h–j. The  $\phi_c$  of TIR at AlGaN/FSS interface is 45.4°. Lights with incident angle exceeding 45.4° will be reflected back to the AlGaN epilayer, where most of lights are lost due to the internal absorption. In cone-shaped PSS, because the base angle of the cone is approximately 50°, lights reflected at cone/AlGaN interface will finally propagate to the top surface with an incident angle  $\leq 40^\circ$ . As a result, the incident angle of majority lights could be less than the  $\phi_c$  of TIR at AlGaN/air interface (23.6°) and thus be extracted. Furthermore, the range of incident angle for TIR at AlGaN/silica cone interface ( $\theta < 14.6^\circ$ ) is larger than that of incident angle for TIR at AlGaN/sapphire cone interface ( $\theta < 4.6^\circ$ ), indicating that PSSA is more effective to reflect the lights into the escape cone in comparison with PSS.

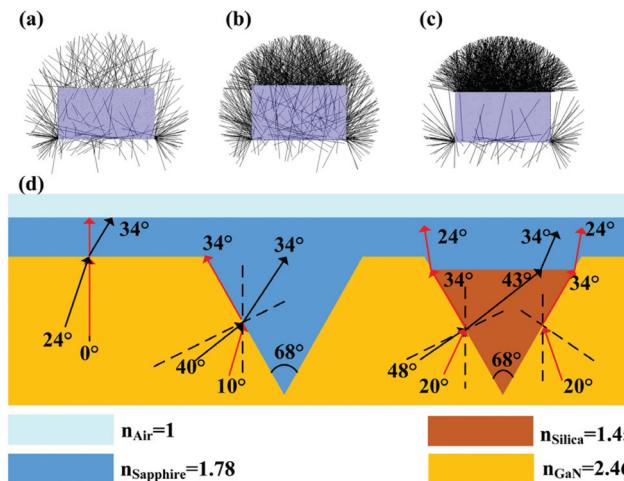

We have also proposed PSSA substrate to improve LEE of flip-chip blue LEDs.<sup>176</sup> The light trajectories in flip-chip blue LEDs on FSS, PSS, and PSSA are shown in Fig. 16. Since the  $\phi_c$

**Fig. 16** Cross-sectional ray-tracing images of flip-chip blue LEDs on (a) FSS, (b) PSS, and (c) PSSA. (d) Schematic illustration of light trajectories in flip-chip blue LEDs on FSS, PSS, and PSSA. Reproduced with permission.<sup>176</sup> Copyright 2020, Optical Society of America.

of TIR at sapphire/air interface is calculated to be  $34^\circ$ , lights propagated from GaN or silica into sapphire with an incident angle less than  $34^\circ$  can finally escape from sapphire into air. That is, the extraction angle of light for FSS, PSS and PSSA is  $(0^\circ, 24^\circ)$ ,  $(10^\circ, 40^\circ)$  and  $(20^\circ, 48^\circ)$ , respectively. Consequently, PSSA will enhance the extraction probability of lights with incident angle larger than the  $\phi_c$  of TIR at the GaN/sapphire interface ( $\sim 46^\circ$ ). Additionally, the refraction angle of lights at sapphire/GaN interface is between  $0^\circ$  and  $34^\circ$ , whereas that of lights at silica/GaN interface is between  $0^\circ$  and  $24^\circ$ . In other words, light emission of the flip-chip LED on PSSA is more collimated, as compared to the flip-chip LED on PSS.

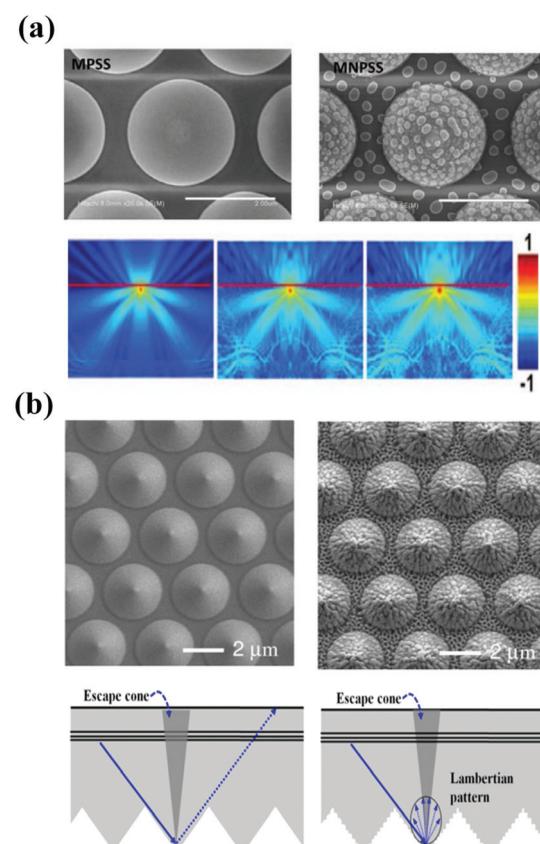

**4.6.2 Nano-micro complex PSS.** Nano-micro complex PSS (NMCPSS), which refers to the embedding nanopatterns onto the microscale PSS, is also a promising pathway for achieving LEDs with high LEE.<sup>177–180</sup> The nanopatterns embedded on micrometre-scale PSS will act as Lambertian pattern, which can diffuse lights into escape cone.<sup>177</sup> Cheng *et al.* utilized Ni etching mask to form nano patterns distributed on the spacing and inclined surface of PSS.<sup>178</sup> The simulated LEE of LEDs with NMCPSS based on FDTD methods is  $\sim 63\%$  higher than that of LED on FSS and  $20.4\%$  higher than that of MPSS (Fig. 17a). Zhou *et al.* found that green LED on nano-micro complex PSS showed  $28.6\%$  increase in LOP (@20 mA) mainly due to the enhanced LEE.<sup>180</sup> Ke *et al.* made use of AAO etching mask to embed nanohole patterns on MPSS.<sup>179</sup> Results indicate that compared to MPSS, such hybrid PSS effectively reduces TDD and strain in epilayers, leading to lower non-radiative recombination rate and efficiency droop. The maximum EQE values of MPSS-LED and NMCPSS-LED are  $31.7\%$  and  $46.2\%$ , respectively (Fig. 17b). Besides, the simulated LEE of LED with NMCPSS based on FDTD methods is  $\sim 33.3\%$  higher than that of LED with conventional PSS, which is similar to the enhancement in intensity of EL and PL.

**Fig. 17** (a) Top-view SEM images of MPSS and NMCPSS and cross-sectional FDTD simulation images of light intensity distribution of FSS, MPSS- and NMCPSS-based LEDs. Reproduced with permission.<sup>178</sup> Copyright 2013, Institute of Physics. (b) Top-view SEM images and light tracing schematic diagrams of MPSS and NMCPSS. Reproduced with permission.<sup>179</sup> Copyright 2016, American Chemical Society.

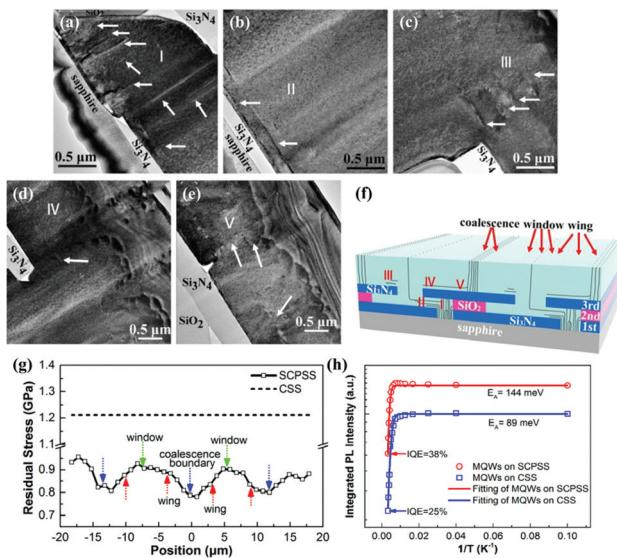

**4.6.3 Serpentine channel PSS.** Hu's group developed a serpentine channel patterned mask for *c*-plane sapphire substrate (SCPSS) *via* depositing three layers of  $\text{Si}_3\text{N}_4$  and  $\text{SiO}_2$ .<sup>181</sup> Multiple-modulation ELOG technique was adopted to achieve high-quality GaN (Fig. 18a-f). Most dislocations generated in the bottom windows terminate inside the serpentine channel mask (region I), while others propagating vertically are blocked by the overhanging top  $\text{Si}_3\text{N}_4$  mask. There are low TDs perpendicular to the mask surface in region III and IV, and only few dislocations are observed to run laterally atop the edges of  $\text{Si}_3\text{N}_4$  mask. The latter terminate in region V and combine with other TDs at the coalescence boundary. Consequently, serpentine channel plays an important role to reduce dislocation density by blocking and bending dislocations. Besides, GaN epilayers on SCPSS exhibit periodical spatial variations on the stress state (Fig. 18g). MQWs on SCPSS show decreased stress value as well as  $52\%$  increase in IQE compared to MQWs on conventional sapphire substrate (Fig. 18h). Later, InGaN interlayer and modified SCPSS without meeting-front have been adopted to further reduce TDs and compressive stress.<sup>182</sup>

**Fig. 18** (a–e) Cross-sectional TEM bright field images with [01–10] zone axis of region I–V on SCPSS and (f) corresponding schematic diagram of dislocation evolution. (g) Stress distribution of MQW sample on SCPSS is compared with the MQW sample on conventional sapphire substrate (CSS). (h) Normalized integrated PL intensity of MQW emission as a function of temperature from 10 to 300 K for the MQW samples on SCPSS and CSS. Reproduced with permission.<sup>181</sup> Copyright 2016, American Chemical Society.

## 5. Summary and prospect

With the increasing demands for energy-saving and high-performance lighting sources, III-nitride LEDs are undoubtedly presumed to be the next-generation candidate with great potential. Development of heteroepitaxy technology provides a versatile route that III-nitride LEDs could be grown on low-cost foreign substrates. Particularly profiting from QvdWE,<sup>183</sup> LED devices fabricated on the sapphire and glass have been successfully achieved in recent years.<sup>184,185</sup> However, there are still bottlenecks lying ahead to achieve efficient III-nitride LEDs with regards to improving crystal quality and LEE. Currently, PSS technology acting as an effective method addresses the aforementioned issues simultaneously. Compared to FSS, the reduction of TDD by using PSS arises from the different growth behaviour. For epilayers grown on PSS, ELOG prevents a portion of TDs from propagating towards MQWs and leads to TDs bending, eventually decreasing the TDD. Notably, efforts devoted to optimizing growth techniques combined with PSS are indispensable for crystalline quality improvement. Furthermore, the mechanism of enhancing LEE by PSS is attributed to the increased chance of scattering light out of LED structure. The role of PSS closely associates with its structural parameters, such as pattern size, shape and aspect ratio, which have a considerable influence on the LED performance. Patterns with various structural parameters could be obtained by utilizing one certain or integrated method. Although PSS has shown remarkable significance for LEDs, there is still a long way to go for the further research. We believe that PSS

technology applied in the LED field may develop towards the following directions in the future.

### 5.1 Integrated fabrication method for large-scale and uniform PSS with complicated patterns

Inspired by volcano-shaped PSS, we find the necessity of combining conventional etching methods with nanoimprint or nanosphere technique to explore the potential value of PSS. On the one hand, the crystal quality is expected to be improved for epilayers grown on PSS featuring complicated patterns. This is because the increased facets provide more nucleation sites for the subsequent ELOG. On the other hand, benefiting from the increased facets, more light will be scattered out of the LED structure, thus leading to higher LEE. Undoubtedly, integrated method is needed in the manufacture of complicated patterns on PSS. It should be mentioned that the pattern uniformity undergoes serious degradation through multiple processing steps, therefore it is hard to achieve large-scale PSS to meet the demands in practical applications. The research will center around how to make use of the advantages of various fabrication methods and at the same time introduce as little damage or contamination as possible. In order to achieve this goal, more in-depth investigation of PSS process condition is required.

### 5.2 Optimizing the structural parameters of PSS for specific LED application

In spite of vigorous efforts for presenting the superiority of PSS than FSS, comparison of different PSS types for LEDs is insufficient. Besides, same PSS type with changing structural parameter is yet to be investigated for LEDs. The practical significance of this project is that an appropriately designed PSS contributes to maximize the LED efficiency and we need to take the LED structure, growth mode, growth conditions, and other factors into consideration. It is hard to draw any firm conclusion about which type or structural parameter of PSS is the best for LED applications. Furthermore, reasonable optimization based on experiments together with the numerical simulation will provide reliable evidence and encourage the development of high-efficiency LED grown on PSS.

### 5.3 PSS derivatives and emerging technique with QvdWE