Cite this: *Mater. Adv.*, 2023,

4, 5882

## Computing of neuromorphic materials: an emerging approach for bioengineering solutions

Chander Prakash,<sup>†\*abc</sup> Lovi Raj Gupta,<sup>acd</sup> Amrinder Mehta,<sup>†a</sup> Hitesh Vasudev,<sup>ad</sup> Roman Tominov,<sup>ce</sup> Ekaterina Korman,<sup>ce</sup> Alexander Fedotov,<sup>ce</sup> Vladimir Smirnov<sup>ce</sup> and Kavindra Kumar Kesari <sup>ID</sup><sup>†\*af</sup>

The potential of neuromorphic computing to bring about revolutionary advancements in multiple disciplines, such as artificial intelligence (AI), robotics, neurology, and cognitive science, is well recognised. This paper presents a comprehensive survey of current advancements in the use of machine learning techniques for the logical development of neuromorphic materials for engineering solutions. The amalgamation of neuromorphic technology and material design possesses the potential to fundamentally revolutionise the procedure of material exploration, optimise material architectures at the atomic or molecular level, foster self-adaptive materials, augment energy efficiency, and enhance the efficacy of brain-machine interfaces (BMIs). Consequently, it has the potential to bring about a paradigm shift in various sectors and generate innovative prospects within the fields of material science and engineering. The objective of this study is to advance the field of artificial intelligence (AI) by creating hardware for neural networks that is energy-efficient. Additionally, the research attempts to improve neuron models, learning algorithms, and learning rules. The ultimate goal is to bring about a transformative impact on AI and better the overall efficiency of computer systems.

Received 22nd July 2023,

Accepted 17th October 2023

DOI: 10.1039/d3ma00449j

[rsc.li/materials-advances](http://rsc.li/materials-advances)

## 1. Introduction

The human brain's ideas and architecture are used as models in the developing field of neuromorphic computing, which aims to create highly specialized and efficient computing systems.

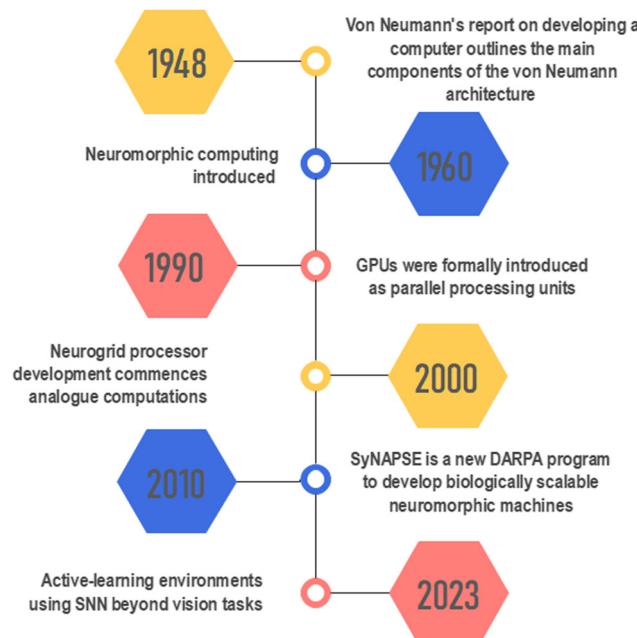

An overview of the major milestones and advances in neuromorphic computing and intelligent computing discovery can be seen in (Fig. 1). This has allowed for the development of powerful artificial intelligence (AI) systems that can process large amounts of data quickly and accurately. The very term "neuromorphic" was coined by Carver Mead in the late 1980s. Neuromorphic computing has the potential to revolutionize the way AI systems are designed and utilized.<sup>1–3</sup> It has already been

used in a variety of applications, from medical diagnostics to autonomous vehicles.

The neural networks of the human brain are mimicked by these systems, also referred to as neuromorphic computers. By drawing on the brain's capacity for parallel information processing, handling complex patterns, and environment adaptation, neuromorphic computers seek to get around some of the drawbacks of conventional computing systems.<sup>4</sup> For pattern recognition, sensory processing, and cognitive computing tasks, it uses specialized hardware and software implementations. Artificial neural networks, which are computational models that imitate the activity of organic neurons, are one of the main components of neuromorphic computers.<sup>6,7</sup> These networks are made up of interconnected "neurons," or nodes, that process and send data using electrical signals. Neuromorphic systems can accomplish high-performance computing using less energy than traditional von Neumann computers by emulating the parallel processing and connectivity of brain networks. Artificial intelligence, robotics, neurology, and cognitive science are a few of the domains that neuromorphic computing has the potential to change.<sup>8–11</sup> Researchers and engineers may create more effective and intelligent systems to process and comprehend complicated data patterns, learn from experience, and adapt to new conditions by utilizing the capability of neuromorphic computers. Although neuromorphic computing exhibits enormous promise, it is still a developing

<sup>a</sup> Research & Development Cell, Lovely Professional University, Phagwara-144411, India. E-mail: chander.mechengg@gmail.com

<sup>b</sup> Mukesh Patel School of Technology Management and Engineering, SVKM'S Narsee Monjee Institute of Management Studies, Mumbai, India

<sup>c</sup> Research Laboratory of Neuroelectronics and Memristive Nanomaterials (NEUROMENA Lab), Institute of Nanotechnologies, Electronics and Equipment Engineering, Southern Federal University, Russia

<sup>d</sup> School of Mechanical Engineering, Lovely Professional University, Phagwara-144411, Punjab, India

<sup>e</sup> Institute of Nanotechnologies, Electronics and Equipment Engineering, Southern Federal University, Taganrog 347922, Russia

<sup>f</sup> Department of Applied Physics, School of Science, Aalto University, Espoo, Finland.

E-mail: kavindra.kesari@aalto.fi

<sup>†</sup> Authors equally contributed.

area, and actual applications for neuromorphic computers are still in the planning stages.<sup>12–15</sup>

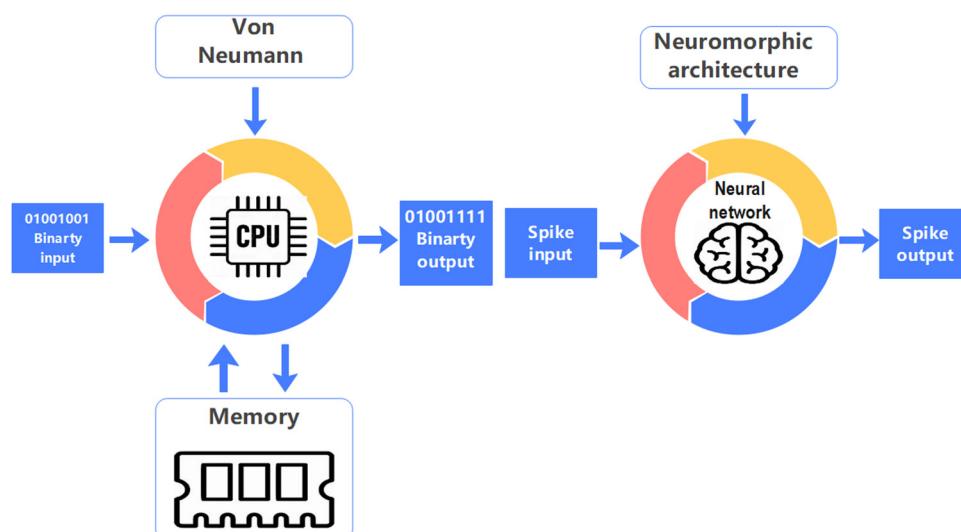

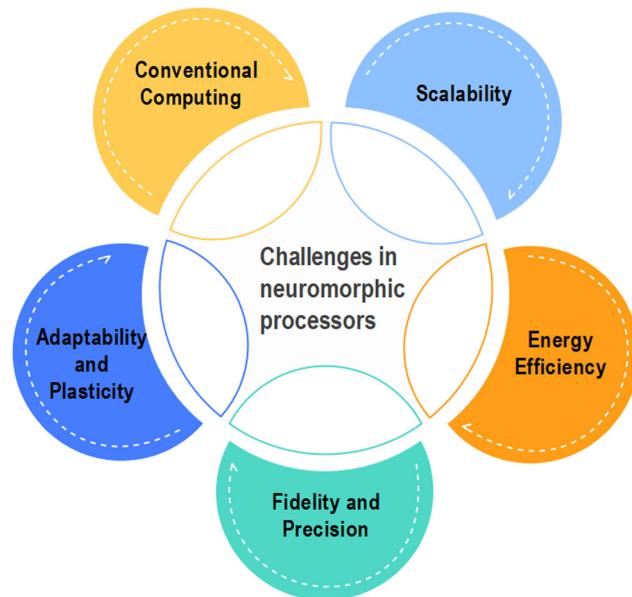

There is still hope for major developments in this field due to continuous research and advancements. Major breakthroughs in neuromorphic computing could revolutionize the way that computers are used and could open up possibilities for new and innovative applications. The potential for this technology is immense, and its development could have a profound effect on the computing industry. As seen in (Fig. 2), neuromorphic computers differ from conventional computing designs in numerous key operational ways. Here are some significant points of distinction.<sup>16</sup>

Traditionally, one action at a time is carried out by traditional computers as process information sequentially. In

contrast, neuromorphic computers are built to make use of parallelism and are motivated by the brain's capacity to handle several inputs at once. Complex tasks with imprecisely defined conditions and noisy input data can be processed more quickly and effectively using neuromorphic architectures since they can run calculations in parallel across numerous nodes or neurons.<sup>17–20</sup> In order to mimic the behavior of artificial neural networks, which are made up of interconnected nodes (neurons), neuromorphic computers were created. Emulation enables neuromorphic computers to carry out more effectively tasks like pattern recognition, machine learning, and cognitive computing. Traditional computers, on the other hand, employ a more generalized architecture that is not tailored to these activities.<sup>21–23</sup>

**Chander Prakash**

*Chander Prakash: Prof. Prakash serving Dean, Research and Development and Professor at SVKM'S Narsee Monjee Institute of Management Studies, Mumbai, India. He served as Dean, Research & Development/School of Mechanical Engineering at Lovely Professional University, India. He did his PhD in Mechanical Engineering at Panjab University, Chandigarh. His research interests are bio-manufacturing, surface modification of bio-materials and*

*computer modeling and simulation. He has published over 350 scientific articles in peer-reviewed journals. He is a highly cited researcher with 7022 citations (H-index 47). He is one of the Top 1% of leading scientists in Mechanical and Aerospace Engineering in India, as per Research.com.*

**Lovi Raj Gupta**

*Lovi Raj Gupta: Dr Lovi Raj Gupta is the Pro Vice Chancellor, Lovely Professional University. He holds a PhD in Bioinformatics. He did his MTech in Computer-Aided Design & Interactive Graphics from IIT, Kanpur and BE (Hons) Mechanical Engineering from MITS, Gwalior. His research interests are in the areas of Robotics, Mechatronics, Bioinformatics, Internet of Things (IoT), AI & ML using Tensor Flow (CMLE) and Gamification. He has authored 7*

*books along with several scientific articles. He has been appointed as Leading Scientist in Mega Project on Neuromorphic and memristive Materials by Russian Federation at Southern Federal University SFedU, Russia.*

**Amrinder Mehta**

*Mr Amrinder Mehta is a Deputy Superintendent in the Research and Development Cell (RDC) at Lovely Professional University in Phagwara, Punjab, India. In 2015, he received his master's degree from Lovely Professional University in Phagwara, Punjab, India, and is currently pursuing his PhD Surface Engineering/ Thermal Spraying is one of his research interests (HVOF, FLAME SPRAY, COLD SPRAY, AND PLASMA SPRAY). He is currently*

*working on Nano-structured||Multi-modal||High entropy alloys coatings for high-temperature oxidation and corrosion resistance—Thermal Barrier Coatings (TBCs) and Microwave material processing.*

**Hitesh Vasudev**

*Prof. Hitesh Vasudev is working as a Professor in the Department of Mechanical Engineering, Lovely Professional University (LPU), Phagwara, Punjab, India. He has received his PhD degree from Guru Nanak Dev Engineering College, Ludhiana-India. His research areas includes Surface Engineering/ Thermal Spraying. Currently working on the development of Nano-structured materials and hybrid materials. He has won*

*the Research Excellence Award for three consecutive years (2019, 2020, 2021 & 2022) at LPU. He has published over 100 indexed papers, 15 conference papers, 4 books, and 25 book chapters. He also consistently appeared in the top 2% of researchers as per Stanford Study in 2023.*

Fig. 1 Intelligent computing discovery and advancement timeline.<sup>1–5</sup>

To solve this problem, energy-efficient neuromorphic computer architectures were designed. These make use of the idea of spiking neural networks, in which calculations are based on the transmission of electrical spikes that resemble the firing of brain neurons. Compared to typical computing designs, which frequently use more energy for sequential processing and data movement, this method can dramatically minimize the amount of energy used. The ability to change their internal connections in response to experience or training makes neuromorphic

computers excellent at adaptive learning. The system can learn from data and adapt to changing situations thanks to a property known as plasticity. Traditional computers do not have the natural adaptability and plasticity of neuromorphic systems, despite being capable of learning through software algorithms.<sup>24–26</sup> Real-time integration and processing of sensory data is a strong suit for neuromorphic computers. Rapid sensory input processing is essential for decision-making in applications like robotics, where this capability is very useful. To accomplish a similar level of real-time sensory integration on traditional computers, more hardware and complicated algorithms are frequently needed. It is crucial to remember that while neuromorphic computing has several benefits, it is not meant to completely replace conventional computing architectures. It is better suited for certain tasks that benefit from parallelism, pattern recognition, and real-time adaptability, and it does not replace conventional computing methods; rather, it augments them. A more diverse and potent computer ecosystem may be possible by combining the two computing paradigms. By combining the strengths of both neuromorphic and conventional computing, it is possible to create powerful and efficient computing architectures. This could have a significant impact on the development of AI and machine learning applications that are more powerful and faster than ever before.<sup>27–29</sup>

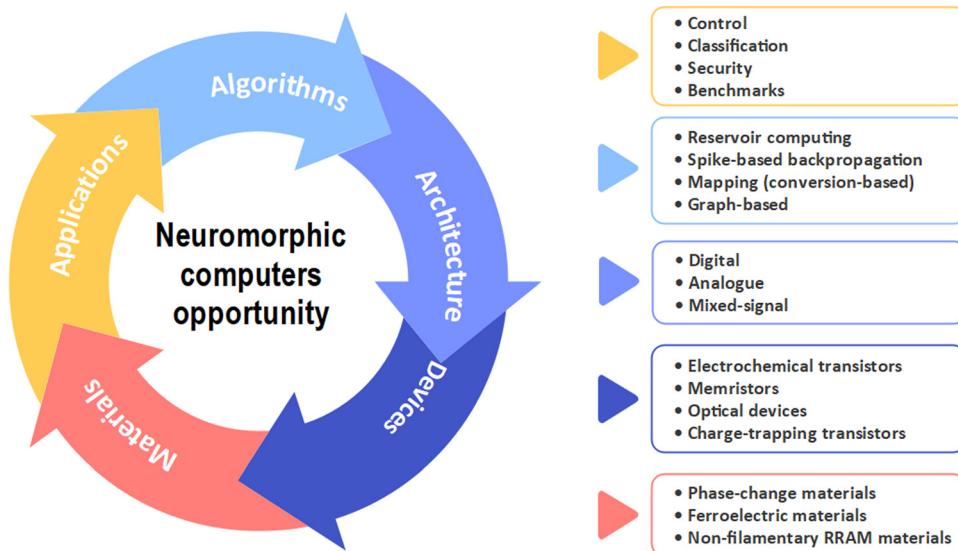

In neuromorphic computing, most research is focused on the hardware systems, devices, and materials mentioned above. However, to fully utilize neuromorphic computers in the future, to exploit their unique computational characteristics, and to drive their hardware design, neuromorphic algorithms and applications must be utilized. Therefore, it is necessary to study and develop neuromorphic algorithms and applications that

Alexander Fedotov

industry, micro- and nanosystems engineering, nanoelectronics, carbon nanotubes, hybrid carbon nanostructures, composite nanomaterials, and MEMS technologies. He published over 100 scientific papers, including 44 papers indexed in Scopus/WoS (Hirsch Index – 10), 101 papers indexed by RSCI. Since 2020, Prof. Fedotov is Head of the PhD Degree in Electronic component base of micro- and nanoelectronics, quantum devices.

*Prof. Alexander Fedotov, PhD, serving Director of the Institute of Nanotechnologies, Electronics and Equipment Engineering, Southern Federal University (SFedU), Rostov-on-Don – Taganrog, Russia. Prof. Fedotov is also a leading scientist at the Research Laboratory Neuroelectronics and Memristive Nanomaterials founded at SFedU with the support of the Russian Government in 2022. His research interests lie in the field of the nanotechnology*

Kavindra Kumar Kesari

*Dr Kavindra Kesari is a Senior Researcher in the Department of Applied Physics, Aalto University and the University of Helsinki, Finland. He obtained a Doctoral degree in Biotechnology and received Junior and Senior Research fellowships during his Doctoral studies at Jawaharlal Nehru University, New Delhi, India. He is actively involved working in material-based neuro and cancer biology research. He has published over 150 papers (H-index 36: Google Scholar) in reputed scientific journals, 30 book chapters, 7 books, and presented over 40 papers at national and international scientific meetings. He is acting as Commissioner at the ICBE EMF, USA, since 2021 and Honorary Faculty Member for NGCEF, New South Wales, Australia, since 2020.*

can be used to optimize the hardware design and maximize the use of neuromorphic computers, taking into account the unique computational characteristics of neuromorphic computers. Electronics, telecommunications, and computing all use analog and digital signal representation or processing techniques, which are two distinct types. Here is a quick description of each idea.<sup>30–33</sup> Continuous signals or data that fluctuate smoothly and indefinitely over time or place are referred to as analog. In analog systems, physical quantities like voltage, current, or sound waves are used to represent information. Analog signals can take on any value within a continuous range, which distinguishes them from digital signals.<sup>34</sup> An analog clock with moving hands, for instance, depicts time passing constantly as the hands move across the dial. Contrarily, the term “digital” describes discrete signals or data that are represented using a limited number of symbols or values. A series of 0 s and 1 s, commonly referred to as bits, are used in digital systems to represent information in binary form. Digital tools like computers can manipulate and process these bits. Digital signals are discrete in nature and have values that can only exist at certain levels. For instance, a digital clock uses incrementally changing digits to show the current time. The way information is expressed and processed is where analog and digital differ most.<sup>35–37</sup> Digital signals are discrete and have a finite number of values, but analog signals are continuous and can theoretically have an endless number of values. Advantages of digital signals include improved precision, resistance to noise, and the capacity to store and analyze significant volumes of data. However, there are still a lot of applications for analog signals, particularly in fields like audio and video where maintaining the continuity of the signal is crucial for accurate reproduction. Analog signals are also used for control systems, where a real-time response is required. It is proposed in this work that all types of hardware implementations – digital, mixed analog-digital, and analog – are neuromorphic, but here we restrict our attention to spiking neuromorphic computers, *i.e.* those that implement spike-based neural

networks. While analog systems are more efficient in some tasks, digital systems are more reliable and easier to scale.<sup>38–40</sup> Digital systems can also be more easily modified, allowing for more customizability. Overall, the choice between analog and digital systems depends on the nature of the task and the desired goals.

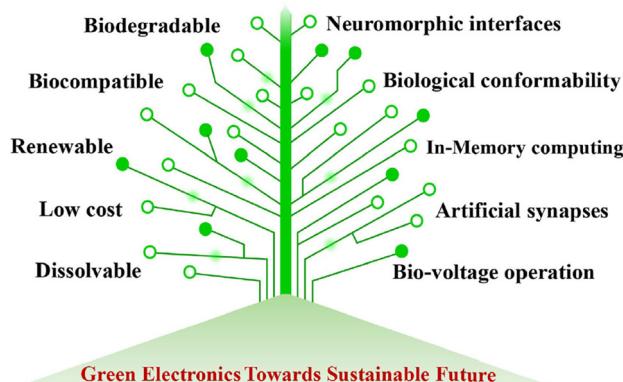

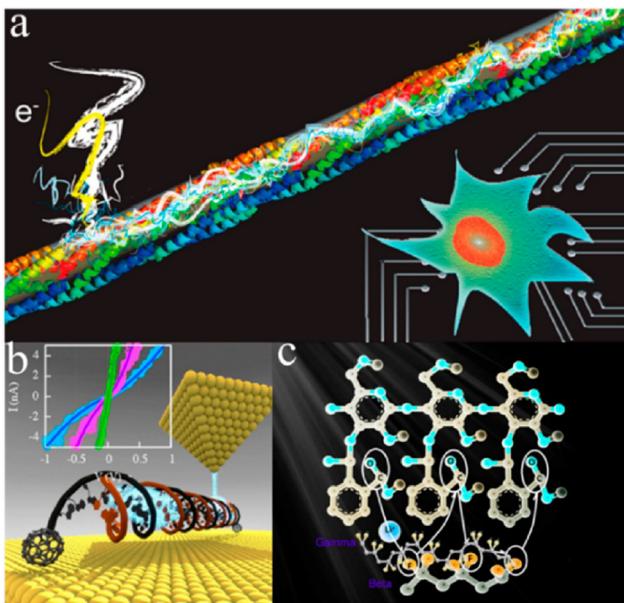

Biomaterials are substances that have been developed to interact with living tissues and organs and other biological systems. They are suitable for use in biomedical applications because they have certain qualities. Some of the essential traits of biomaterials are depicted in (Fig. 3). Biocompatible materials are those that do not have negative effects or are hazardous when they come into contact with live tissues. They should not provoke an inflammatory response of the immune system. Bioactive qualities can be found in biomaterials, which means they can interact with biological systems and encourage particular cellular responses. Bioactive substances, for instance, can promote cell adhesion, proliferation, and differentiation. The mechanical characteristics of the tissues or organs where biomaterials are implanted should match those of the biomaterials themselves.<sup>41–44</sup> This guarantees compatibility and lessens strain on the tissues in the area.

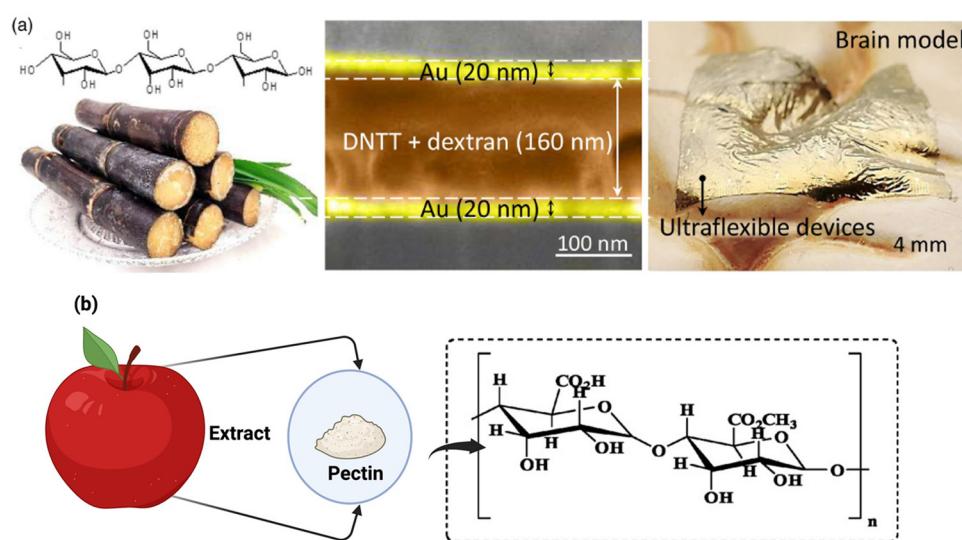

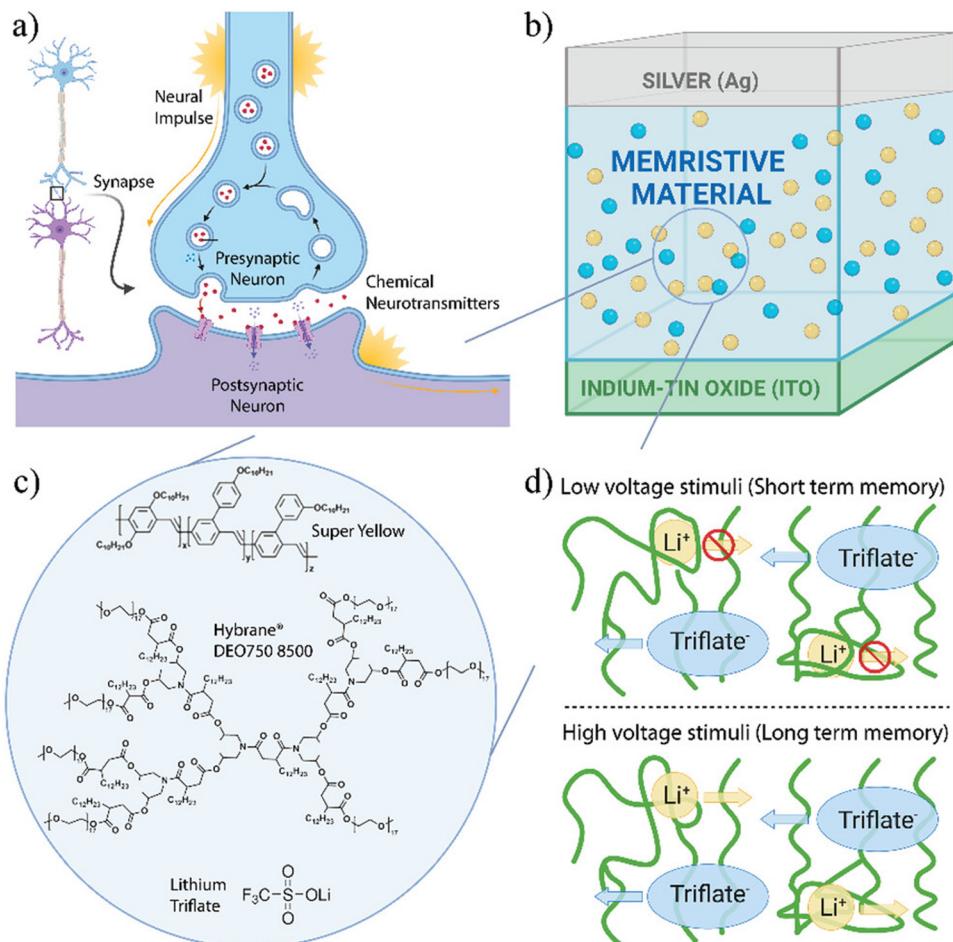

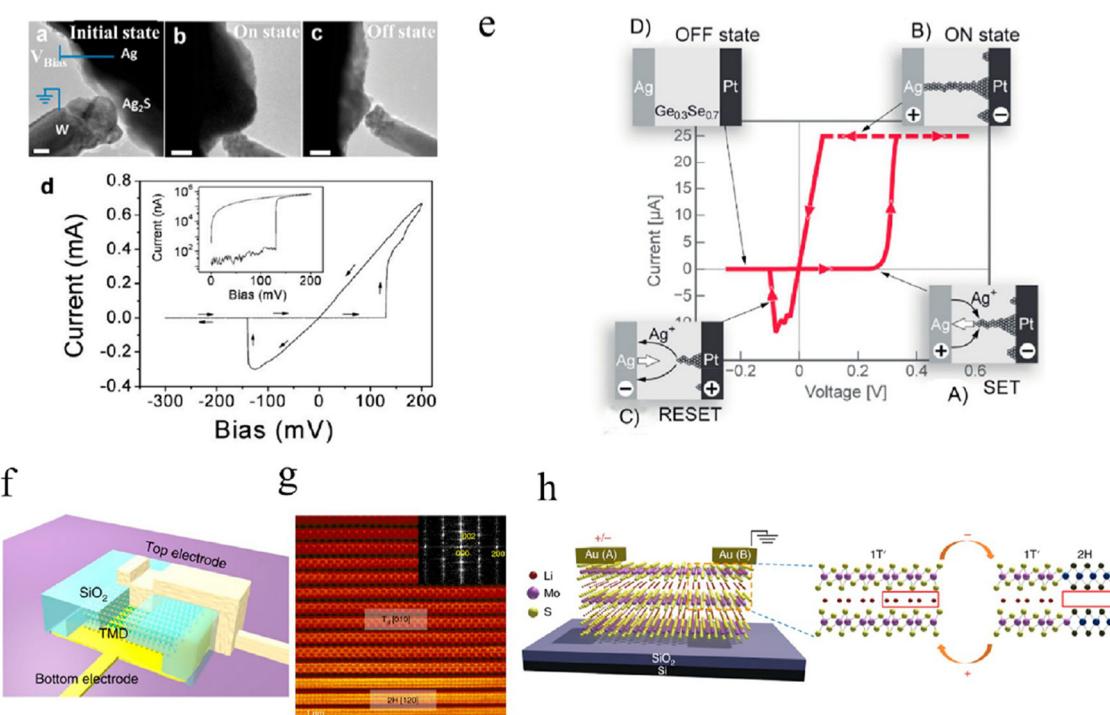

Biomaterials may need to deteriorate gradually over time depending on the use. Degradable biomaterials can be made to degrade gradually, enabling the body to progressively absorb them or regenerate tissue. For interactions with cells and tissues, biomaterials' surface characteristics are essential. Surface alterations can regulate interactions such as protein binding and cell adhesion. As shown in Fig. 4 a type of electronic device called biomaterial-based ultra-flexible artificial synaptic device imitates the operation of organic synapses present in the human brain. Biomaterials, which are substances that interact with biological systems in a functional and compatible way, are used in the construction of these devices.<sup>45</sup> Replicating the synaptic connections between neurons in the brain in biomaterial-based ultra-flexible artificial synaptic devices is

Fig. 2 Von Neumann architecture vs. neuromorphic architecture.

### Biomemristors for Bio-realistic Applications

### Green Electronics Towards Sustainable Future

Fig. 3 Overview of memristors with biomaterials for bio-realistic features.<sup>45</sup>

their main objective to enable them to carry out functions including learning, memory, and information processing.<sup>47</sup>

Typical components of these devices include flexible substrates, conductive substances, and synaptic elements. There are many benefits of using biomaterials in these devices. First, they can interact with biological systems without harming them or being rejected, biomaterials are biocompatible. This is crucial for creating technological innovations that can easily meld with organic tissues, including the brain. Second, biomaterials may display characteristics that are similar to those of the brain's actual synaptic connections.<sup>51–53</sup> For instance, some biomaterials can modify electrical signals and enhance ion transport, replicating the actions of real synapses. Additionally, because of their extreme flexibility, which enables them to adapt to irregular surfaces and move with mechanical deformations, these devices are useful in areas where standard

rigid electronics would be ineffective or harmful.<sup>54–57</sup> Although this field of study is still in its early stages, engineers and scientists are working hard to create ultra-flexible artificial synaptic devices based on biomaterials.<sup>58,59</sup> By enabling effective and biocompatible brain-inspired computing systems, these gadgets have the potential to transform such areas as neuromorphic computing, brain-machine interfaces, and artificial intelligence. These devices could also revolutionize healthcare by providing an efficient platform for drug delivery and personalized treatments.<sup>60,61</sup> In addition, they could be used to restore motor, sensory, and cognitive function in patients with neurological diseases.

## 2. Integration of neuromorphic computing with material design

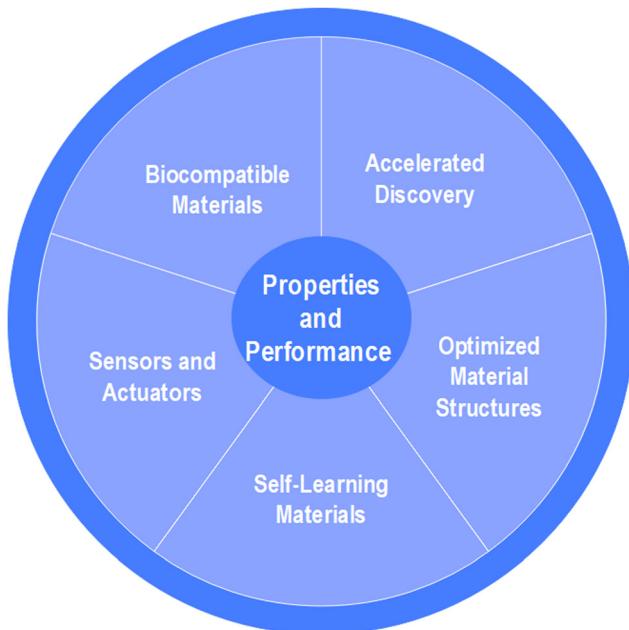

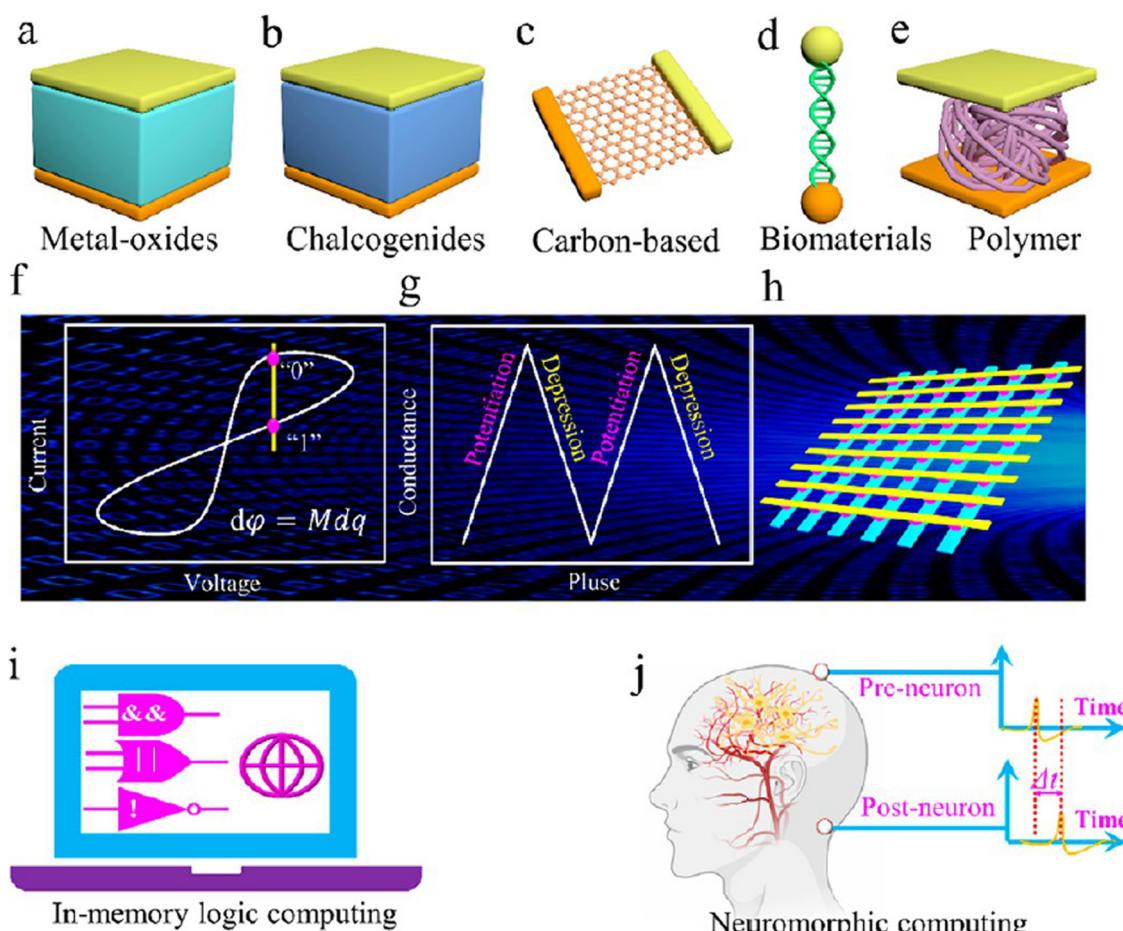

The amalgamation of neuromorphic computing and material design has the capacity to fundamentally transform the process of material development, resulting in the creation of innovative materials that exhibit improved characteristics and performance. Neuromorphic computing, drawing inspiration from the structural organisation of the human brain, facilitates the effective and adaptable processing of information.<sup>62</sup> As shown in (Fig. 5) the qualities and performance of the generated materials are affected by neuromorphic computing and material design.

When integrated with material design, it has the potential to influence materials in several manners. The utilisation of neuromorphic computing has the potential to greatly enhance the efficiency of material discovery by expediting the process. The utilisation of simulation and prediction techniques enables the estimation of material properties by leveraging existing data, hence mitigating the necessity for significant experimental investigations.<sup>63</sup> The utilisation of neuromorphic algorithms enables the optimisation of material structures at

Fig. 4 Biomaterial-based artificial synaptic devices with ultraflexibility: (a) ultraflexible organic synaptic transistors based on dextran;<sup>48–50</sup> (b) organic synaptic transistors based on pectin from apples.

Fig. 5 Material design and neuromorphic computing change the properties and performance of the materials.

the atomic or molecular scale. This phenomenon has the potential to facilitate the development of materials possessing customised characteristics, such as enhanced strength, conductivity, or thermal stability. Self-learning materials refer to educational resources that are designed to facilitate independent learning. These materials are typically created to enable individuals to acquire knowledge. Materials that are integrated with neuromorphic computing can dynamically adjust and respond to varying environmental conditions.<sup>64</sup> Organisms possess the ability to acquire knowledge from their surroundings and modify their characteristics, accordingly, rendering them remarkably versatile and receptive. Energy efficiency is a notable characteristic of neuromorphic systems, and this attribute can be utilised to develop materials that exhibit enhanced energy efficiency. For instance, the advancements discussed can have advantageous implications for smart energy storage and conversion materials. Sensors and actuators can be effectively implemented using materials engineered with neuromorphic computing capabilities, enabling them to exhibit exceptional sensitivity and responsiveness.<sup>65</sup> These entities possess the ability to perceive and react to alterations in their surroundings or external stimuli, rendering them highly advantageous in domains such as robotics and healthcare. The integration of neuromorphic computing with materials has the potential to enhance the development of brain–machine interfaces (BMIs). The functionality of these interfaces is contingent upon the utilisation of biocompatible materials that effectively engage with neural impulses, hence facilitating a seamless exchange of information between the brain and external equipment.<sup>66</sup>

## 2.1. Enhanced material characterization

The utilisation of neuromorphic approaches has the potential to increase the processes involved in material characterization,

hence facilitating a more comprehensive understanding and predictive capability about the behaviour of materials across varying situations. The utilisation of materials including neuromorphic computation holds potential for application in drug discovery and delivery systems. Drug release profiles can be adjusted, resulting in enhanced efficacy and focused therapeutic interventions. The integration of neuromorphic computing into materials enables the monitoring of their health and integrity.<sup>67</sup> These systems can identify instances of damage or deterioration, commence the necessary repair procedures, or alert users of maintenance requirements. The utilisation of neuromorphic techniques holds promise in the advancement of biocompatible materials for medical implants, as well as the development of materials that emulate biological systems for diverse applications.<sup>68</sup> The utilisation of neuromorphic computing has the potential to expedite the exploration and development of quantum materials possessing distinctive electrical characteristics that are of utmost importance in the fields of quantum computing and advanced electronics. In general, the amalgamation of neuromorphic computing and material design exhibits potential in the development of materials that possess not only significant optimisation but also adaptability, energy efficiency, and the ability to react to dynamic circumstances.<sup>69</sup> The adoption of an interdisciplinary approach has the potential to revolutionise multiple industries and create novel opportunities in the fields of material science and engineering. These materials have the potential to be integrated into existing devices and systems, allowing for more efficient and adaptive operations. Furthermore, the interdisciplinary approach is likely to open new areas of research and collaboration, leading to further advancements in technology.

## 3. Overview of neuromorphic algorithms

Artificial neural networks that imitate the structure and operation of the human brain are called neuromorphic artificial neural networks (ANNs). The phrase “neuromorphic” describes the design approach of replicating the structure and computational principles of the human brain. Neuromorphic artificial neural networks (ANNs) are built to operate on specialized hardware known as neuromorphic chips or processors, as opposed to ordinary artificial neural networks which are normally implemented on conventional computing systems. These chips utilize the parallelism and low power consumption characteristics found in biological neural networks to effectively process neural network computations. Spiking neural network models, which use discrete spikes or pulses of activity to represent and transfer information, are frequently used in neuromorphic ANNs. Traditional artificial neural networks use continuous activation levels in contrast to this. Spiking neural networks (SNN) result in various advantages including event-driven computing, effective temporal information encoding, and increased energy efficiency. These are thought to be more physiologically realistic. An emerging area of research called

Table 1 Comparison of the characteristics of ANNs, SNNs, and biological neural networks

| S. no. | Properties                    | Biological NNs    | SNNs              | ANNs    |

|--------|-------------------------------|-------------------|-------------------|---------|

| 1      | Representation of information | Spikes            | Spikes            | Scalars |

| 2      | Learning model                | Neural plasticity | Plasticity        | BP      |

| 3      | Platform                      | Brain             | Neuromorphic VLSI | VLSI    |

“neuromorphic computing” intends to create hardware and software architectures for computers that are modeled after the structure and operation of the human brain.

The word “neuromorphic” is a combination of “neuro,” which refers to the brain and nervous system, and “morphic,” which denotes the imitation or resemblance of a particular form or structure. In Table 1, biological neural networks, ANNs, and SNNs are contrasted. ANNs are composed of multiple layers of interconnected neurons. SNNs imitate the behavior of neurons in the brain using spikes of electrical signals to

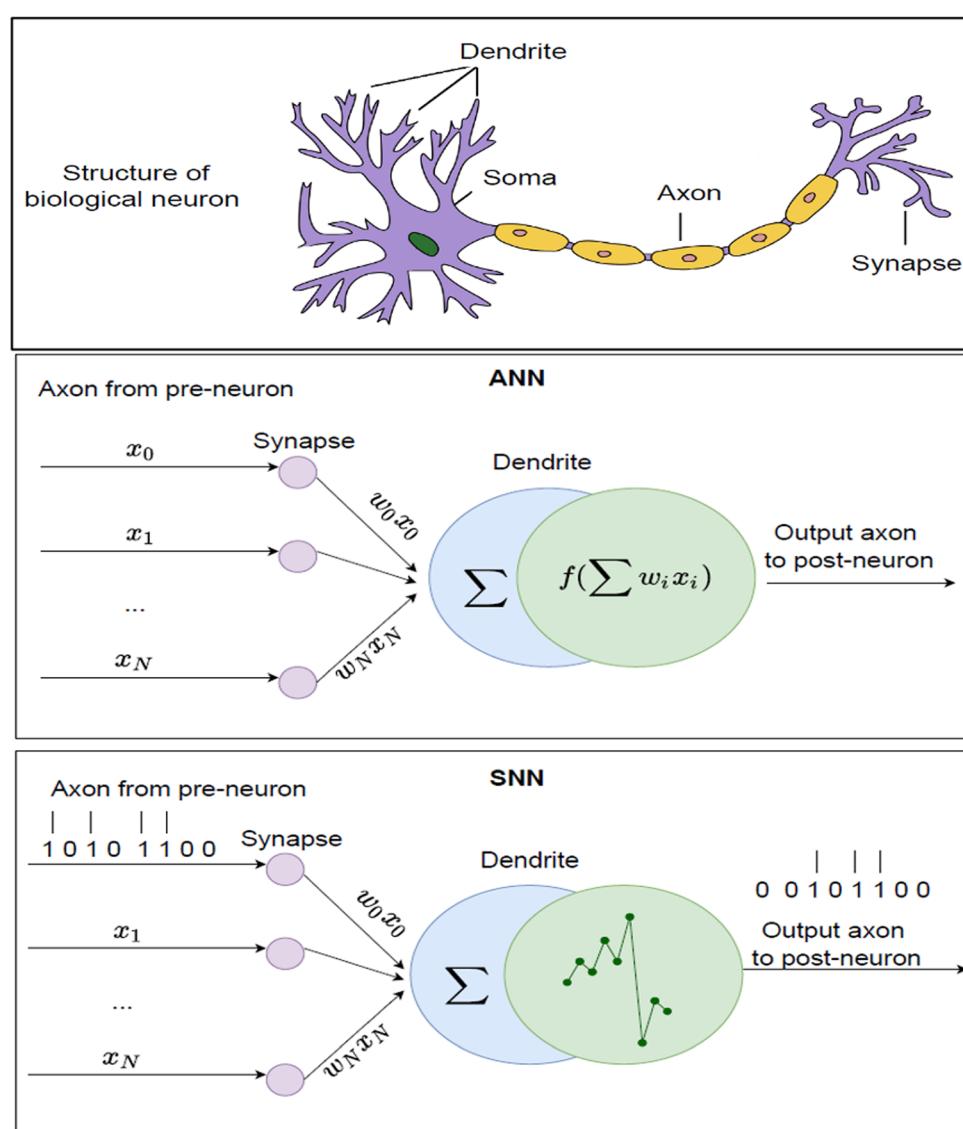

represent data. Both types of networks are used in machine learning for pattern recognition and data analysis. As shown in Fig. 6, biological neurons, ANNs, and SNNs differ from each other. Biological neurons are processing units in the brain, ANNs are artificial neurons that simulate the functions of biological neurons, and SNNs are a type of ANN that mimics the behavior of biological neurons using spiking signals.

Biological neurons are connected by synapses and communicate by exchanging electrical signals. In contrast, ANNs are connected by weighted connections and communicate by

Fig. 6 Analysis of the biological neuron, ANN, and SNN.<sup>70</sup>

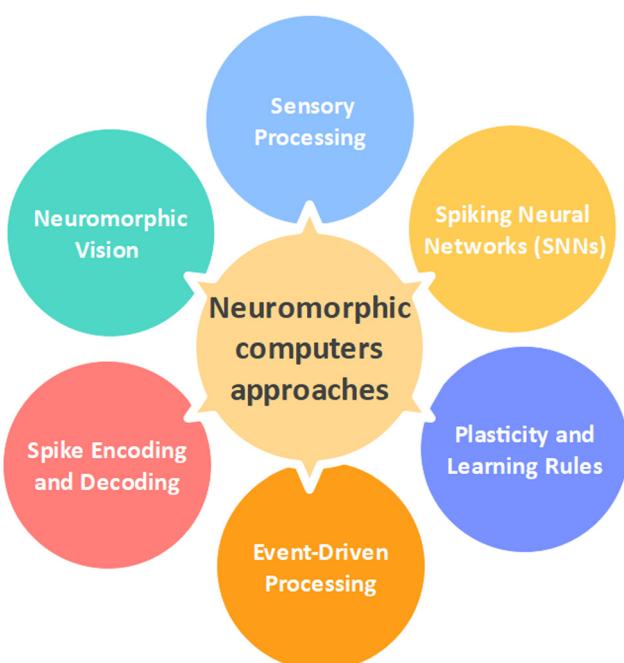

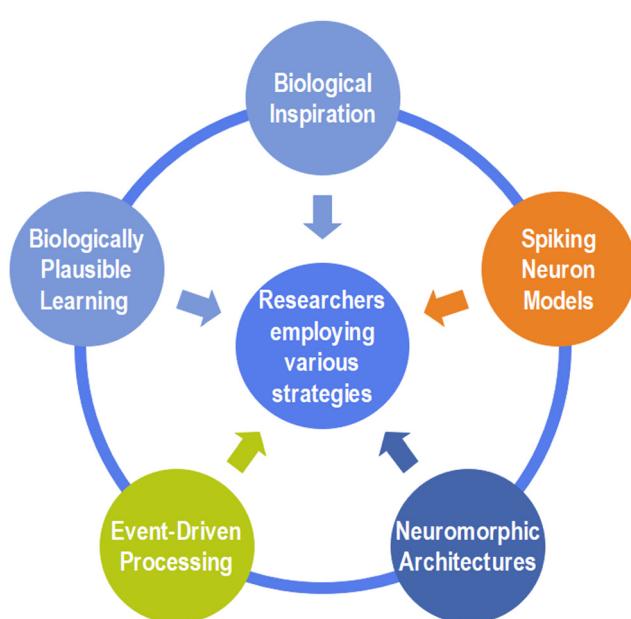

exchanging numerical values. SNNs communicate by exchanging spike trains, which more closely resemble the behavior of biological neurons. These systems' specialized hardware and built-in algorithms allow them to carry out tasks like pattern recognition, sensory processing, and learning very effectively and in parallel.<sup>71–74</sup> Algorithms for neuromorphic computers have been developed using a variety of strategies, as shown in Fig. 7.

Neuromorphic computing systems are becoming increasingly popular due to their ability to quickly process large amounts of data and perform tasks that traditional computers may not be able to do as easily. These systems also have the potential to significantly reduce energy consumption in the future. Spiking neural networks are a type of artificial neural network that simulates both the timing and behavior of individual neurons. It can benefit from the hardware's event-driven design, making it well-suited for neuromorphic computing. The firing rates and synaptic weights of the neurons are calculated by SNN algorithms to carry out operations like classification, grouping, and prediction. Plasticity mechanisms modeled after biological synapses are frequently included in neuromorphic computers, enabling them to adjust to and learn from the input data.<sup>75–78</sup> The synaptic weights between neurons are modified by algorithms based on Hebbian learning, spike-timing-dependent plasticity (STDP), or other biologically inspired learning rules. These algorithms give the system the ability to self-organize, discover patterns, and enhance its functionality over time. The event-driven processing strategy used by neuromorphic computing is one of its fundamental characteristics. The system responds to events or changes in the input rather than processing data continuously.

To effectively manage incoming spikes or events and propagate them through the network, triggering the necessary computations and reactions, algorithms are devised. Spike encoding and decoding methods are essential because neuromorphic computers frequently work on spiking brain activity.<sup>79–81</sup> The time and intensity of spikes are represented by spike trains, which are created by spike encoding methods from continuous data. Spike decoding algorithms, on the other hand, evaluate the spiking activity produced by the system to extract significant information or produce suitable outputs. Vision and sensory processing tasks are particularly well suited for neuromorphic computers.

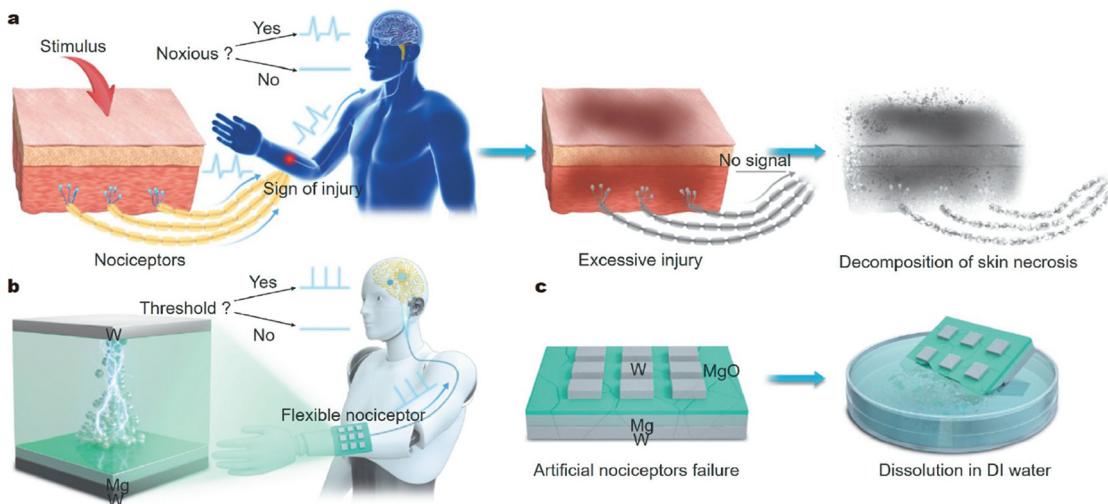

To extract features and make sense of the input, hierarchical processing is a common component of the algorithms used for these applications. These algorithms make it possible to recognize objects, detect motion, and identify gestures. It is crucial to remember that research in the subject of neuromorphic computing is still ongoing, and new techniques and algorithms are constantly being created. The examples show some typical methods, but researchers may also investigate creative algorithms and modifications.<sup>83–85</sup> This research is pushing the boundaries of what is possible and is revolutionizing the way we interact with machines. It has the potential to unlock new capabilities and applications that were previously impossible. As technology continues to evolve, it will create exciting new opportunities for exploration and development. A simplified schematic illustration demonstrating how biological nociceptors detect an external stimulus and send the signal to the brain *via* the spinal cord is illustrated in (Fig. 8). The illustration starts with an external stimulus operating on a particular bodily part, such as heat, pressure, or chemicals.<sup>86</sup> Specialized sensory nerve endings called nociceptors are present throughout the body. They are in charge of recognizing and reacting to unpleasant or potentially dangerous stimuli.

The nociceptors in the afflicted area are activated when the external stimuli reach a specific threshold value. On their membrane, these nociceptors have particular receptors that react to various stimuli. The nociceptors produce electrical signals in the form of action potentials after they are engaged. An electrical impulse that travels along nerve fibers in an all-or-nothing fashion is known as an action potential. The action potential is produced by nociceptors, a type of sensory neuron, and it moves down their nerve fibers. These neurons have lengthy extensions called axons that can travel great distances to convey electrical messages. As the nociceptors enter the spinal cord, their axons converge and form bundles. Within the vertebral column, the spinal cord is a long, cylindrical substance. The nociceptors' axons join other neurons inside the spinal cord to form synapses. Electrical signals are changed into chemical messages at synapses.<sup>87–89</sup> The presynaptic terminals of sensory neurons release neurotransmitters, which then bind to receptors on the postsynaptic neurons. The ascending spinal cord pathways receive the nociceptive signal *via* synaptic transmission. Higher brain areas, in particular the thalamus and somatosensory cortex, receive the signal *via* these pathways, which is where pain perception and interpretation take place.

Fig. 7 Neuromorphic computer approach algorithms.

**Fig. 8** Diagram of biological nociceptors that detect external stimuli in (a). An action potential is transmitted from the spinal cord to the brain when the biological signal produced by painful stimuli is greater than the threshold value. Additionally, after extensive skin damage, the nociceptors lose their ability to send signals and their ability to perceive pain. The skin eventually turns necrotic, peels off, decomposes, and vanishes on its own. (b) Realization of biodegradable and biocompatible nociceptive emulators. (c) In order to mimic the skin necrosis's breakdown, the artificial nociceptors that did not work disintegrate in DI water.<sup>82</sup>

The transmitted signal is processed and interpreted by the brain once it gets there, which causes the impression of pain or discomfort. This knowledge is combined with other sensory and cognitive inputs by the brain to produce the proper response or behavioral output. It is crucial to remember that the many mechanisms involved in nociception and pain perception are simplified in this schematic picture. The real mechanisms are more complex and entail interacting with different neuronal types, neurotransmitters, and areas of the brain.<sup>90–93</sup> This is why it is so important to research the neurobiological basis of pain and to develop therapies to target these underlying mechanisms. Additionally, research into the complex relationship between the mind and body can further help us to understand the subjective experience of pain.

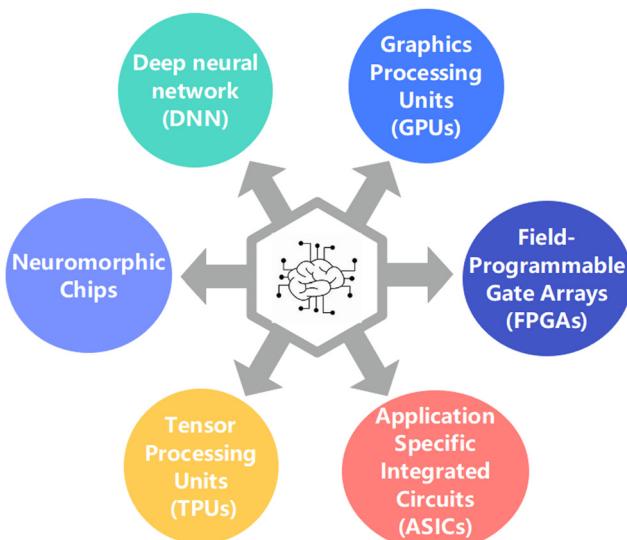

### 3.1. Hardware acceleration for neural network

The use of specialized hardware and architectures created to speed up the execution of neural network algorithms is known as hardware acceleration for neural networks. The performance, effectiveness, and scalability of neural network calculations as opposed to general-purpose computing platforms like CPUs or GPUs are all goals of these hardware solutions. There are various kinds of hardware accelerators frequently utilized for neural networks, as depicted in (Fig. 9). These hardware accelerators can be designed to optimize a variety of tasks, from training and inference to data processing and feature extraction. It has the potential to drastically reduce the computational cost of neural networks, making them more accessible and efficient. GPUs have been routinely utilized to accelerate neural networks. GPUs are excellent at parallel processing and can execute large-scale matrix operations, which are essential for neural network computations.<sup>94–97</sup> GPUs were initially created for producing visuals. GPU support in deep learning frameworks like TensorFlow and PyTorch enables neural network models to make use of GPU acceleration. Reconfigurable integrated circuits, or FPGAs, can be made to do particular computations. It has the benefit of versatility, enabling hardware architects to create designs specifically suited to neural network algorithms. When properly optimized, FPGAs can deliver exceptional performance and energy efficiency for particular neural network models.<sup>98–101</sup>

ASICs are specially designed chips created for a specific use. By enhancing the hardware architecture for neural network operations, ASICs are created for neural network acceleration to offer great performance and energy efficiency. Although ASICs can improve performance noticeably, lack FPGAs' versatility. TPUs are specialized ASICs created by Google to accelerate neural network computations. TPUs are built to manage the demands of deep learning workloads and excel at executing matrix operations. This hardware is excellent for training and inference activities in neural networks being optimized for high

**Fig. 9** Types of hardware for acceleration of neural network devices.

throughput and energy efficiency.<sup>102,103</sup> The architecture of the brain served as inspiration for the invention of neuromorphic chips, which mimic the actions of neurons and synapses.

These specialized processors imitate the massively parallel and energy-efficient processing found in the brain to speed up neural network computations. Neuromorphic chips, which are still in the research and development stage, have the potential to produce extremely effective and brain-inspired computing. The particular neural network model, performance needs, power considerations, and cost considerations are only a few of the variables that influence the choice of hardware accelerator. It is important to note that these accelerators are not mutually exclusive and that different parts of neural network computation, such as training and inference, can be optimized by combining them in a system.<sup>104-106</sup> The design of the system is also important as it can affect performance, power consumption, and cost. It is important to consider the trade-offs between the different options before making a decision. Ultimately, the best hardware accelerator for a given task will depend on the specific neural network model and the desired performance.<sup>107</sup> The performance metrics and applicability of different models, applications, and hardware generations can exhibit variability. According to the data shown in Table 2, a comparative analysis is conducted. The appropriateness of each accelerator is contingent upon various criteria, including the architecture of the neural network, the size of the model, the distinction between training and inference, and the specific environment in which the deployment takes place.<sup>108</sup> Furthermore, the hardware environment is constantly changing, as newer iterations of accelerators emerge, providing enhanced levels of performance and efficiency. When making specific deployment decisions, it is crucial to evaluate these criteria in conjunction with the hardware features to ascertain the most appropriate accelerator for a certain application.<sup>109</sup>

In addition, seeking information from up-to-date documentation and analysing benchmarking results provided by hardware makers can offer a more accurate and detailed understanding of the present status of these technologies.

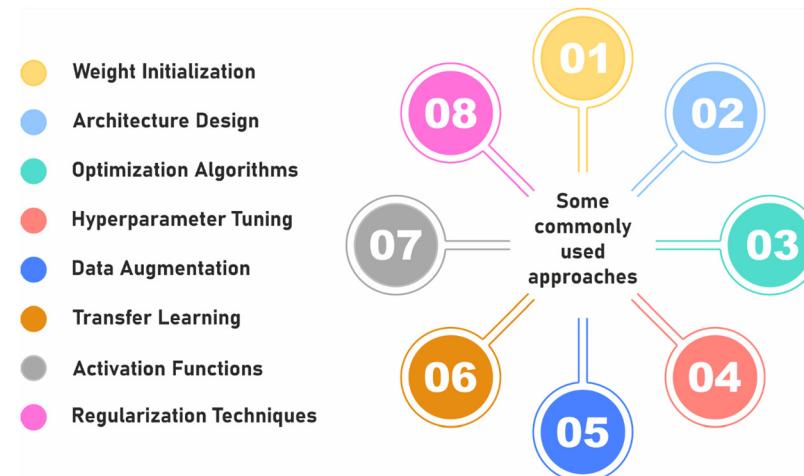

### 3.2. Design and optimization methodologies for neural network

Numerous approaches are used in the design and optimization of neural networks with the goal of enhancing their functionality,

effectiveness, and generalization potential. Here are a few typical methods, as seen in (Fig. 10). Each of these approaches is intended to improve the performance of the neural network in some way.

The number and layout of layers, the different types of neurons, and the connectivity patterns all fall under the category of a neural network's architecture. Convolutional, recurrent, or attention layers, as well as the number of layers and hyperparameters like the number of neurons or filters, must be chosen in order to design an effective architecture. To improve the architecture design, strategies like transfer learning and network pruning can be used. For effective learning, a neural network's weights must be initialized. The initial weights can be set using a variety of techniques, including random initialization. Faster convergence during training is encouraged by proper weight initialization, which helps prevent problems like vanishing or exploding gradients.<sup>123-125</sup> The neural network models are given non-linearities *via* activation functions, which enables them to learn intricate patterns. Sigmoid, tanh, ReLU (rectified linear unit), and its derivatives such as Leaky ReLU and ELU (exponential linear unit), are examples of common activation functions. The ability of the network to model complicated relationships and steer clear of problems like the "vanishing gradient" problem can be impacted by selecting the proper activation function. Regularization techniques help neural networks become more generic by preventing overfitting. Techniques like dropout, batch normalization, L1 and L2 regularization (weight decay), and others can be used. Regularization enhances performance on unobserved data, reduces noise during training, and controls model complexity. During training, optimization methods are crucial in updating the weights of the network. While Adam, RMSprop, and AdaGrad offer advances in convergence time and managing complex loss landscapes, Stochastic Gradient Descent (SGD) is a widely used technique. During the optimization process, these algorithms strike a balance between the exploration and exploitation trade-offs. Different hyperparameters in neural networks, such as learning rate, batch size, and regularization strength, have a big impact on how well they perform.<sup>126-128</sup> To obtain the optimum performance, hyperparameter tuning entails systematically looking for the finest possible combination of hyperparameters. To efficiently scour the

Table 2 Comparative analysis of hardware accelerator

| Hardware accelerator | Performance metrics                                                                | Energy efficiency                                                     | Ideal application scenarios                                                                                                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPU                  | High throughput<br>Parallel processing<br>Wide ecosystem, mature support           | Moderate to high<br>Varied based on load<br>Suitable for data centers | Deep learning training and inference <sup>110</sup><br>Complex, large-scale neural networks <sup>111</sup><br>General-purpose deep learning tasks <sup>112</sup>                                                                         |

| FPGA                 | Low-latency, reprogrammable<br>Efficient for specific tasks                        | High<br>Varied based on design                                        | Customizable neural networks <sup>113</sup><br>Edge devices, IoT, real-time processing <sup>114</sup>                                                                                                                                    |

| ASIC                 | High hardware flexibility<br>Extremely efficient                                   | Energy-efficient custom designs<br>Very high                          | Prototyping and research <sup>115</sup><br>Specific, well-defined tasks <sup>116</sup>                                                                                                                                                   |

| TPU                  | High throughput<br>Minimal power consumption                                       | Typically, fixed design<br>Very high                                  | Inference acceleration, dedicated AI chips <sup>117</sup><br>Consumer electronics, embedded systems <sup>118</sup>                                                                                                                       |

| Neuromorphic chip    | Customized for neural networks<br>Low power consumption<br>Event-driven processing | Energy-efficient data centers<br>Extremely high<br>Ultra-low          | Large-scale deep learning inference <sup>119</sup><br>Google cloud AI, tensor flow applications <sup>120</sup><br>Brain-inspired computing, spiking networks <sup>121</sup><br>Neuromorphic research, cognitive computing <sup>122</sup> |

Fig. 10 Commonly used approaches for optimization.

hyperparameter space, methods like grid search, random search, or Bayesian optimization can be applied.

By performing random data transformations like rotations, translations, or flips to the input data, data augmentation techniques improve the amount and diversity of the training dataset. By exposing the neural network to a larger variety of variations and lowering the likelihood of overfitting, data augmentation aids in the neural network's ability to generalize.<sup>130–132</sup> Transfer learning bootstraps the training of new models on smaller or related datasets by using pre-trained models on big datasets. Transfer learning can drastically save training time and boost neural network performance by transferring knowledge from the pre-trained model, especially when training data is few. To produce predictions, model ensembling mixes many neural network models. By utilizing various models and their complementing capabilities, it aids in increasing the robustness and generalization of the predictions. Prediction averages, model stacking, or the use of bagging and boosting are other assembling strategies. In a neural network, quantization reduces the precision of the weights and activations, which results in less memory consumption and faster computations. Pruning strategies find and eliminate unused links or neurons in a network, shrinking the size of the model and speeding up inference without significantly sacrificing performance. These approaches can be mixed and customized according to the particular needs and limitations of the neural network application because they are not mutually exclusive.<sup>133–135</sup> The optimum design and optimization procedures for a particular neural network task are usually determined through empirical evaluation, iteration, and experimentation. This allows for a wide variety of neural network designs and architectures, enabling developers to choose the best approach for their particular application. Different activation functions can also be used to improve the performance of the network and to ensure that the network can learn complex patterns.<sup>136</sup> Finally, regularization methods can be used to reduce overfitting and improve generalization. The electrical transmission of a neuronal impulse and the release of neurotransmitters into the synaptic cleft are depicted in (Fig. 11).

The presynaptic neuron, which transmits the electrical signal or impulse, is shown first in the diagram. It is made up of a cell body, dendrites (which take input from neighboring neurons), and axons (which send output to neighboring neurons). Having the ability to act when an input signal or stimulus hits a threshold, the presynaptic neuron produces an action potential, a quick change in electrical potential.<sup>129</sup> This electrical signal moves toward the synaptic terminal along the axon. The synaptic terminal, also known as the axon terminal, is a specialized structure that lies at the end of the axon of the presynaptic neuron. Neurotransmitter-filled synaptic vesicles can be found in this terminal. A sequence of events is started when the action potential reaches the synaptic terminal. Neurotransmitters are released into the synaptic cleft as a result of these events, which cause synaptic vesicles and the presynaptic membrane to fuse. The presynaptic and postsynaptic neurons are separated by a little region called the synaptic cleft. It divides the two neurons and blocks their direct electrical communication. Small dots in the diagram indicate the released neurotransmitters as they diffuse over the synaptic cleft. It travels from one side of the synaptic membrane to the other. The released neurotransmitters can bind to particular receptors on the postsynaptic neuron's membrane. These receptors are made to identify and respond to particular neurotransmitter molecules.<sup>137–139</sup> When neurotransmitters attach to postsynaptic receptors, the postsynaptic neuron undergoes several chemical and electrical changes. The postsynaptic neuron can be excited or inhibited by this activation, depending on the neurotransmitter and receptor types. A postsynaptic potential is produced when neurotransmitters bind to postsynaptic receptors. The postsynaptic neuron may either depolarize (excitatory) or hyperpolarize (inhibitory) in response to this potential. The postsynaptic neuron will produce its electrical signal if the postsynaptic potential meets the threshold for an action potential. The neuronal impulse will then continue to be sent as this signal travels through the postsynaptic neuron's axon. It is crucial to highlight that the details of neurotransmitter release, receptor binding, and

Fig. 11 Release of neurotransmitters into the synaptic cleft between the presynaptic and postsynaptic neurons during the electrical transmission of a neural impulse.<sup>129</sup>

signal transmission are not included in this simplified representation of synaptic transmission.<sup>140–142</sup> Even so, it offers a broad grasp of electrical impulse transmission and highlights the critical function neurotransmitters play in synaptic communication. Without neurotransmitter release, synaptic transmission would not occur. The role of neurotransmitters in the communication between neurons cannot be overstated. Thus, neurotransmitters are essential for efficient synaptic transmission of electrical impulses. These neurotransmitters are released into the synaptic cleft, which then binds to neurotransmitter receptors on the postsynaptic neuron, allowing the electrical impulse to be transmitted. Without neurotransmitters, the transmission of electrical impulses cannot take place.<sup>143,144</sup>

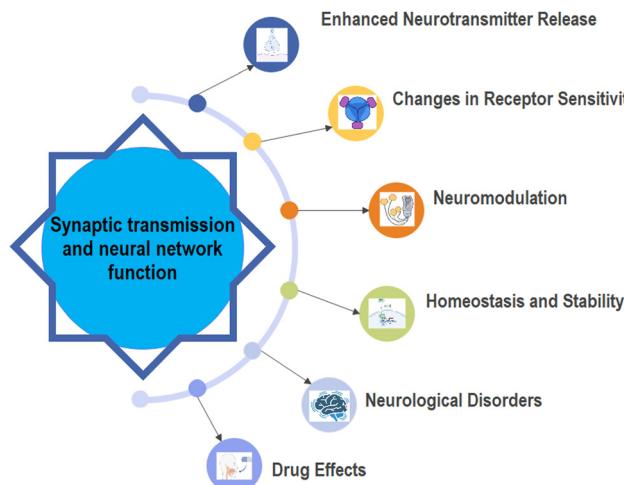

### 3.3. Synaptic transmission and the functioning of brain networks

Changes in the levels of neurotransmitters or the sensitivity of receptors can have a substantial effect on the effectiveness of synaptic communication. Consequently, this can have significant consequences for the general operation of brain networks. The impact of alterations in neurotransmitter dynamics on

synaptic transmission and neural network function is illustrated in (Fig. 12).<sup>145</sup> These changes can lead to changes in behavior, as well as malfunctions in cognitive and affective processes. Additionally, these changes can lead to the development of neurological disorders, such as anxiety and depression.<sup>146</sup>

Enhanced neurotransmitter release refers to the phenomenon when there is an increase in the concentration of neurotransmitters within the synaptic vesicles or an enhancement of the processes responsible for their release. This can result in the amplification of synaptic signals, leading to better neuronal communication. This phenomenon may yield a higher degree of efficacy in the transmission of information among neurons, thereby fostering improved network connection and facilitating the process of learning.<sup>147</sup> On the other hand, a reduction in neurotransmitter release can lead to a weakening of synaptic transmission. This phenomenon can weaken the synaptic connections between neurons, which could decrease the overall functionality of neural networks, difficulties in the process of learning, or hindered transmission of signals.<sup>148</sup> Modifications in the sensitivity of post-synaptic receptors can yield substantial consequences. Enhanced receptor sensitivity has the potential to induce heightened neurotransmitter responses, hence optimising

Fig. 12 Pertains to synaptic transmission and the functioning of brain networks.

synaptic transmission efficiency. A reduction in sensitivity might result in a diminished reaction, compromising the efficiency of transmission. Synaptic plasticity refers to the capacity of synapses to undergo long-term potentiation or long-term depression, which involves alterations in neurotransmitter concentrations and receptor sensitivities.<sup>149</sup> These changes play a crucial role in the strengthening or weakening of synapses over time. The aforementioned processes are fundamental to the acquisition of knowledge and the establishment of memory, hence playing a crucial role in the adaptive functioning of neural networks. Neuromodulation refers to the process by which certain neurotransmitters function as neuromodulators, exerting their influence on synaptic connections within a wider network, hence altering their strength. Changes in the amounts of neuromodulators or the sensitivities of receptors can impact the neural network's general functioning, hence altering many cognitive processes such as attention, arousal, and mood.<sup>150</sup> The maintenance of homeostasis and stability in neuronal systems involves the regulation of neurotransmitter concentrations and receptor sensitivities by neurons and neural networks, which serves to stabilise the overall activity of the network. The dysregulation of these processes has the potential to result in various disorders, such as epilepsy, in which an overabundance of excitation impairs the stability of neural networks. Neurological and mental illnesses often exhibit changes in neurotransmitter systems.<sup>151</sup> For instance, dysregulation of dopamine levels has been linked to the manifestation of neurological disorders such as Parkinson's disease and schizophrenia. These illnesses frequently present themselves as disturbances in the functionality and behaviour of networks. Pharmaceutical substances that specifically interact with neurotransmitter systems, such as antidepressants or anxiolytics, have the potential to influence the process of synaptic transmission and the overall functionality of neural networks.<sup>152</sup> The therapeutic actions of medications are mostly attributed to their impact on neurotransmitter concentrations and receptor sensitivity. In brief, modifications in the levels of neurotransmitters and the sensitivities of receptors are pivotal factors in influencing the efficacy and

adaptability of synaptic communication. The alterations described profoundly impact neural networks' operational capabilities, exerting influence on critical functions such as learning, memory, behaviour, and the progression of neurological and psychiatric disorders.<sup>153</sup> Comprehending the complicated dynamics involved in synaptic transmission is of paramount importance in elucidating the intricacies of brain functionality and malfunctions. New insights into synaptic transmission can lead to the development of more effective treatments for neurological disorders and an improved understanding of brain processes. This knowledge can be used to develop new treatments for mental health disorders and to advance our understanding of neurological diseases.<sup>154</sup>

### 3.4. Architectural implications for memory technologies

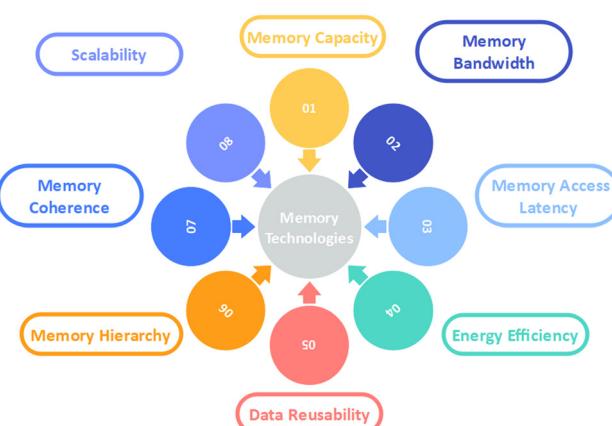

An essential component of neural networks' effective operation is memory technology. For neural network systems, the memory technology chosen can have a big architectural impact. Here are a few important things to keep in mind, as indicated in (Fig. 13).

To store model parameters, intermediate activations, and training data, neural networks frequently need a lot of memory. The memory technology ought to have enough capacity to satisfy the network's memory needs. A variety of memory technologies, from on-chip caches to off-chip memory modules or even distributed memory systems, offer varied capacities. In neural networks, there is a lot of data transfer between the memory and the processing units. The rate at which information can be read from or written to memory is referred to as memory bandwidth. To swiftly feed data to the processor units and avoid memory bottlenecks that could impair overall performance, high memory bandwidth is essential.<sup>155–158</sup> The memory technology should offer sufficient bandwidth to satisfy the neural network's computing needs. The amount of time it takes to read or write data from memory is known as memory access latency. Frequent memory accesses in neural networks can cause noticeable delays and affect overall performance. On-chip caches and high-speed memory interfaces are two memory technologies with low access latency that can assist in reducing this latency and provide quicker data access.

Energy usage is a major concern when it comes to neural networks because they frequently demand large-scale memory

Fig. 13 Some types of memory technologies.

operations. Low-power SRAM (static random access memory) and developing non-volatile memory technologies are two examples of memory technologies that have excellent energy efficiency and can assist neural network architectures using less power. Data reuse patterns in neural networks show that the same data is accessed repeatedly during various phases of computation. Cache hierarchies or scratchpad memories are examples of memory systems that facilitate effective data reuse and can lessen the frequency of memory accesses while enhancing speed. Memory hierarchies, which offer various layers of memory with variable capacities, bandwidths, and latencies, can be advantageous for neural networks. Neural networks can optimize the trade-off between capacity, bandwidth, and latency by using a hierarchy of memory technologies, including on-chip caches, high-bandwidth memory, and bigger off-chip memory.<sup>159</sup> Memory coherence refers to providing consistency and synchronization between memory copies across various processing units or nodes in multi-node or distributed neural network systems. Data integrity in such architectures must be maintained *via* memory technologies that support effective memory coherence techniques, such as distributed memory systems or coherence protocols. Memory systems must facilitate scalability as neural networks get bigger and more complicated. Scalable memory technologies make it simple to increase memory space and bandwidth in order to support larger models or datasets. Technologies like memory interconnects, distributed memory systems, or memory modules with extensible capacities can help to accomplish this scalability. These considerations must be carefully taken into account when choosing memory technology for neural network topologies to strike a balance between performance, energy efficiency, and scalability. It frequently calls for a trade-off analysis based on the precise needs, limitations, and accessible technological solutions. Additionally, choices in architectural design for neural network systems are still influenced by current developments in memory technologies.<sup>160–162</sup> This is why developers need to stay up to date with current trends and advancements in-memory technology. Furthermore, it is essential to have an in-depth knowledge of the trade-offs involved when selecting memory solutions to ensure the best performance and scalability of the neural network.

### 3.5. Memory bandwidth in neural networks and the frequent data transfer

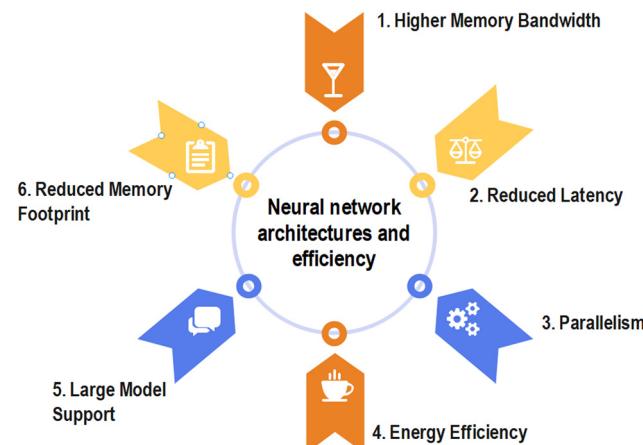

The importance of memory technology advancements cannot be overstated when it comes to tackling the efficiency issues related to data transfer in neural networks. Furthermore, these advancements can have substantial architectural consequences for upcoming artificial intelligence systems.<sup>163</sup> The influence of advances in memory capacity on neural network topologies and efficiency is seen in Fig. 14. Memory advancements allow neural networks to process more data, leading to higher accuracy rates. In addition, memory advancements can lead to more scalable AI systems, allowing for greater performance.<sup>164</sup> Finally, memory advancements can help reduce the latency and power consumption of AI systems, making them more efficient.

Fig. 14 Bandwidth affects the architecture and performance of neural networks.

The concept of higher memory bandwidth refers to the increased rate at which data may be sent between the computer's memory and other components, such as the processor. Potential advancements in-memory technologies in the future could potentially yield increased memory bandwidth, hence facilitating accelerated data transfers between memory and computing units. This phenomenon can lead to a decrease in data transfer bottlenecks and expedite the process of training and inference in neural networks.<sup>165</sup>

The concept of reduced latency refers to the decrease in the amount of time it takes for data to travel from its source to its destination. Advancements in memory technologies have the potential to reduce memory access latency, hence facilitating expedited data retrieval. This holds significant importance in real-time applications and when working with extensive neural network models. Parallelism is a rhetorical device that involves the repetition of grammatical structures, and words.<sup>166</sup> The augmentation of memory bandwidth has the potential to enhance the level of parallelism in neural network topologies. Models that possess a greater number of parallel processing units can effectively process data, resulting in accelerated training and inference processes. The concept of energy efficiency refers to the ability to achieve a certain level of energy output while minimising the amount of energy input. The development of memory technologies that exhibit increased bandwidth while concurrently minimising power usage has the potential to enhance the energy efficiency of neural network hardware.<sup>167</sup> The significance of this is paramount for mobile and edge devices that possess constrained power allocations. The concept of large model support refers to the implementation of techniques and strategies to address the challenges associated with training and deploying large-scale machine learning models. The progress in-memory technology can facilitate the utilisation of more extensive neural network models, resulting in enhanced memory capabilities. Larger models frequently exhibit superior performance, albeit necessitating increased memory bandwidth to sustain optimal efficiency.<sup>168</sup> Advancements in memory technologies have the

potential to result in decreased memory footprints for neural network models. The consideration of memory restrictions is crucial in applications that are deployed on edge devices. The concept of in-memory processing refers to the practice of doing data processing tasks directly within the computer's main memory, as opposed to the barrier between memory and processing units can be blurred by emerging memory technologies, such as resistive RAM (RRAM) and processor-in-memory (PIM) architectures.<sup>169</sup> This has the potential to significantly improve data transfer efficiency by reducing the necessity of data movement between these units. Potential advancements in-memory technology in the future could potentially incorporate enhancements and refinements specifically tailored to neural network workloads, hence enabling the utilisation of more streamlined and effective data access patterns.<sup>170</sup> This has the potential to enhance the utilisation of memory bandwidth. The concept of heterogeneous memory architectures refers to the use of diverse types of memory inside a computing system. The potential emergence of advanced memory technologies could potentially pave the way for the creation of heterogeneous memory architectures, wherein several forms of memory, such as high-bandwidth memory and non-volatile memory, are seamlessly integrated inside a unified system. This has the potential to provide a harmonious equilibrium between a substantial data transfer rate and the ability to accommodate a large volume of information.<sup>171</sup> Neuromorphic computing refers to a branch of computer science that aims to develop computer systems and architectures inspired by structure and functionality. The utilisation of in-memory technologies has the potential to facilitate the advancement of neuromorphic computing systems, which aim to replicate the intricate memory and computation relationships observed in the human brain. These systems have the potential to facilitate the development of AI architectures that are both extremely efficient and inspired by the functioning of the human brain.<sup>172</sup> AI-specific memory solutions: an exploration of memory technologies tailored for artificial intelligence applications. Memory makers have the potential to develop customised solutions that are specifically designed to meet the requirements of artificial intelligence (AI) and neural network workloads. These methods have the potential to enhance memory bandwidth and optimise access patterns for artificial intelligence (AI) activities.<sup>173</sup> The progress made in memory technology holds the potential to effectively tackle the issues associated with data transmission efficiency in neural networks. These advancements have the potential to enhance the efficiency, speed, and energy efficiency of AI hardware architectures, hence facilitating the implementation of larger and more proficient neural network models.<sup>174</sup> The significance of these innovations cannot be overstated, given the ongoing expansion of AI applications across diverse sectors such as autonomous vehicles, healthcare, and beyond.

## 4. Machine learning algorithms

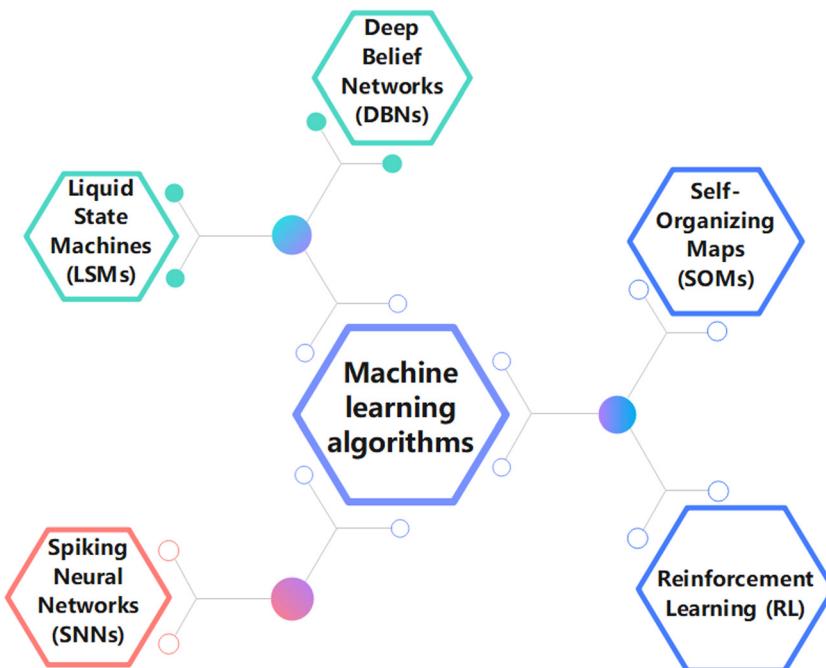

Machine learning algorithms that mimic the structure and operation of the human brain are known as neuromorphic

algorithms. They are necessary to carry out tasks like pattern recognition, decision-making, and learning. These algorithms create effective and scalable solutions for machine learning issues by utilizing the concepts of neuroscience and computational models of neural networks. As demonstrated by neuromorphic machine learning algorithms in (Fig. 15), these algorithms have the potential to revolutionize the field of artificial intelligence and enable machines to do complex tasks.<sup>175–177</sup>

Artificial neural networks known as "spiking neural networks" (SNNs) process information primarily using discrete-time spikes. The timing and intensity of neuronal activity are represented by spikes, means by which neurons in SNNs exchange information with one another. Modeling temporal dynamics and asynchronous processing benefit greatly from SNNs.<sup>178</sup> Recurrent neural networks called liquid state machines (LSMs) are influenced by the dynamics of biological neural networks. It is made up of a sizable group of randomly connected neurons, or "liquid," which gives the network a vibrant and dynamic input space. LSMs have been applied to a variety of tasks, including time-series prediction, robot control, and voice recognition.<sup>179</sup> The capability of deep neural networks and probabilistic graphical models are combined in hierarchical generative models called deep belief networks (DBNs). These are made up of several interconnected layers of neurons, where the upper layers record increasingly abstract representations and the lower layers record low-level characteristics. DBNs can be developed using supervised learning after being trained using unsupervised learning techniques like restricted Boltzmann machines (RBMs).<sup>180</sup> Unsupervised learning methods called self-organizing maps (SOMs) organize data based on similarity and topology. They map the high-dimensional input data onto a grid of neurons to produce a low-dimensional representation of it. SOMs have been applied to feature extraction, visualization, and clustering. Although not entirely, neuromorphic principles can be used to implement reinforcement learning (RL) algorithms.<sup>181–183</sup>

With the help of interaction with the environment and learning to base decisions on rewards or penalties, RL is a paradigm for learning. Neuromorphic RL algorithms try to imitate the adaptability and learning processes of living things. These are but a few illustrations of neuromorphic machine-learning techniques. To enhance the capabilities of artificial intelligence systems, researchers are exploring novel models and methodologies that are inspired by the brain. These models and methodologies are being used to provide AI systems with more efficient problem-solving and decision-making capabilities. This could lead to more powerful AI systems that can learn from their environment and make decisions more quickly and accurately.<sup>184–186</sup>

A popular strategy in neuromorphic systems, especially in spiking neural networks (SNNs), is to encode inputs in terms of spike rates, latency, and neuron population. Here is a brief description of the signal encoding applications of these parameters.<sup>187</sup> The frequency or rate of spikes released by neurons over a predetermined length of time is used in this encoding strategy to represent the information. A certain

Fig. 15 Neuromorphic machine learning algorithms.

feature or signal component may be more strongly present when the spike rate is higher than when it is lower, indicating either its absence or a weaker signal component. SNNs may encode a range of signal intensities or levels by adjusting the neurons' spike rates. The term "latency encoding" describes the representation of data using the precise timing or temporal pattern of spikes.<sup>188–190</sup> The intervals between spikes contain information on the temporal organization of the input or the relative timing of events. The SNN may be made to record temporal relationships and synchronize with time-varying data because neurons can be made to respond to particular temporal patterns. Distributing a signal's representation among several neurons is a necessary step in the encoding of information in terms of the neuron population. By firing spikes in response to particular characteristics or components of the signal, each neuron in the population contributes to the overall encoding.<sup>191–193</sup> The SNN can simultaneously encode many aspects or dimensions of the input signal by altering the activity of various neurons within the population. To provide richer representations of information in neuromorphic systems, several encoding strategies are frequently coupled. For instance, depending on the strength of a signal, a neuron population's spike rate may change, and the precise timing of spikes within that population might reveal further details about the temporal structure. In neuromorphic systems, decoding techniques are employed to extract the encoded data from spike trains.<sup>194</sup> These algorithms decode the encoded signal and carry out operations like pattern recognition, classification, or control by analyzing the spike rates, temporal patterns, and population activity. It is crucial to keep in mind that the precise encoding and decoding techniques can change based on the application and design decisions made in a specific neuromorphic system. Different signal kinds or

computing tasks may respond better to various encoding strategies.<sup>195–197</sup> Neuromorphic computing also requires a careful consideration of the degree of the complexity of the encoding scheme, as well as the hardware resources available for implementing the decoding operations. Ultimately, the choice of encoding and decoding techniques should be tailored to the specific computing task and the available hardware resources.

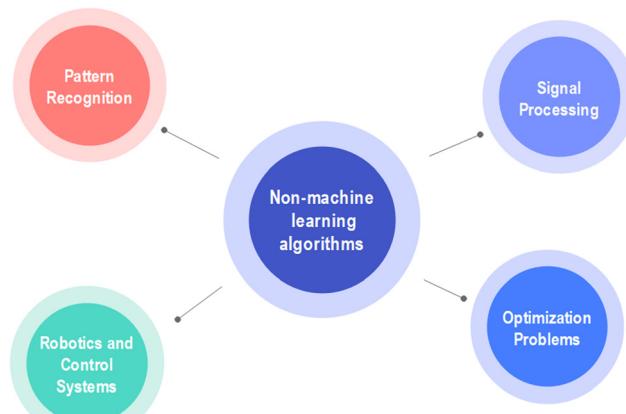

## 5. Non-machine learning algorithms

Neuromorphic computers can be used for a variety of non-machine learning algorithms in addition to machine learning algorithms. Beyond machine learning, other computer activities might benefit from the behavior and principles of biological neural networks, which is the goal of neuromorphic computing. A few instances of non-machine learning algorithms are displayed in (Fig. 16). These algorithms, such as neural networks, incorporate biological principles of neurons and synapses to enable computers to process data more efficiently. Neuromorphic computing can also be used to identify complex patterns in data or to detect anomalies in datasets.<sup>198–200</sup> Signal processing tasks including audio and video processing, image and voice recognition, and sensor data analysis can be performed using neuromorphic computers. By utilizing the computational ideas of neural networks, neuromorphic systems' parallel and distributed architectures can enable effective and immediate signal processing. Combinatorial optimization, resource allocation, and scheduling are a few examples of optimization issues that can be solved with neuromorphic computing. Neuromorphic systems' capacity to explore huge solution areas concurrently may have advantages in the more effective solution of challenging

Fig. 16 Neuromorphic computers for non-machine learning algorithms.

optimization issues. In robotics and control systems, neuromorphic computers can be utilized for motor control, sensor integration, and decision-making activities.

Spiking neural networks' event-driven design may be useful for the real-time control and feedback loops needed in robotics applications. Neuromorphic computers can be used for pattern recognition tasks in a variety of fields, such as bioinformatics, pattern matching, and anomaly detection, in addition to machine learning methods. Recognizing complicated patterns and spotting abnormalities might benefit from the capacity to record temporal dynamics and analyse data in parallel. Biological systems, such as the brain, can be studied further using neuromorphic computers.<sup>201–203</sup> Researchers can investigate computer representations of neural processes and acquire insights into how biological neurons and networks function. It is vital to understand that while neuromorphic computers can be used for non-machine learning algorithms, the brain and neural networks serve as the primary sources of inspiration for their architecture and design. As a result, the effectiveness of these systems and their applicability for particular non-machine learning activities may vary

depending on the nature of the given case and on the form in which the neuromorphic system is being implemented. Therefore, it is essential to thoroughly evaluate the architecture and design of a neuromorphic system before attempting to utilize it for a specific task. Additionally, the parameters of the system should be tuned to the particular problem to ensure optimal performance.

## 6. Different encoding strategies in neuromorphic systems

The utilisation of various encoding procedures holds significant importance in the representation of information inside neuromorphic systems. Neuromorphic systems endeavour to replicate the cognitive processes of the brain and frequently use techniques such as spike rates, latency, and neuron population to encode and convey information.<sup>204</sup> The impact of each of these tactics on information representation is demonstrated in Fig. 17.

Spike rate coding is predicated on the temporal frequency of neuronal spikes. Elevated spike rates may indicate the existence or intensity of a particular characteristic or signal. For instance, an elevated frequency of neuronal firing in response to a sensory stimulus may suggest heightened intensity or significance. Spike rate coding is a method of representing continuous variables analogously, rendering it well-suited for jobs that necessitate accurate analogue information representation. Temporal patterns refer to the fluctuations in spike rates observed over a period.<sup>205</sup> These variations play a crucial role in encoding temporal patterns and sequences of events, hence facilitating the processing of dynamic information. The concept of latency coding involves the representation of information through the timing of neuronal spikes about a particular event or stimulus. The encoding of information is achieved through the precise timing of spike onset.<sup>206</sup>

Temporal precision refers to the ability of a coding system to accurately represent time-sensitive information and capture

Fig. 17 Neuromorphic devices the information-processing strategies influences.