# Nanoscale Horizons

# COMMUNICATION

View Article Online

Cite this: DOI: 10.1039/d5nh00256q

Received 18th April 2025, Accepted 29th July 2025

DOI: 10.1039/d5nh00256g

rsc.li/nanoscale-horizons

# Dual-mode switching of a bidirectional self-rectifying Ti/HfO<sub>2</sub>/Ti device for bipolar and electronic complementary resistive switching

This study explores the dual-mode switching behavior of bidirectional self-rectifying  $Ti/HfO_2/Ti$  (THT) memristors to address the growing demand for efficient in-memory computing. The device operates in electronic bipolar resistive switching (eBRS) and electronic complementary resistive switching (eCRS) modes with bidirectional self-rectifying properties, differing from conventional unidirectional self-rectifying devices. The device achieves stable dual-mode switching by utilizing electronic trapping/detrapping at oxide layers formed at the top and bottom interfaces, while the  $HfO_2$  layer in the middle serves as a blocking layer. The characteristic bidirectional dual-mode self-rectifying switching offers

Department of Materials Science and Engineering and Inter-University Semiconductor Research Center, Seoul National University, Gwanak-10, Gwanakgu, Seoul 08826, Republic of Korea. E-mail: tagyun@snu.ac.kr, choelsh@snu.ac.kr

**Cheol Seong Hwang**

Cheol Seong Hwang has been a Professor in the Department of Materials Science and Engineering at Seoul National University, Korea, since 1998, and has been a university Distinguished Professor since 2020. His research interests include semiconductor memory materials and devices, as well as neuromorphic computing with memristors. He is the author or coauthor of over 750 peer-reviewed papers, including one selected for Nanoscale

Horizons' 10th anniversary Regional Spotlight Collection: Asia-Pacific. He also served as a Guest Editor with other colleagues for the 'Memristors and Neuromorphic Systems' collection of the journal. He is proud of the long-standing collaboration, which is set to continue.

#### New concepts

In this study, we propose a Ti/HfO2/Ti (THT) memristor to achieve bidirectional self-rectifying (bSR) behavior and in-memory parity generation for error detection within crossbar arrays (CBAs). Unlike conventional self-rectifying devices that allow switching only in a single direction, the THT device forms trap layers at both the top and bottom interfaces by employing Ti electrodes on both sides. This configuration enables bidirectional self-rectifying characteristics and allows electronic complementary resistive switching (eCRS) behavior. The proposed THT memristor maintains the selector-free characteristic of self-rectifying switching while addressing the low retention caused by electronic detrapping using an integrated error-checking system. In addition, when the THT device is implemented in a  $1 \times n$  line cell configuration, the eBRS mode functions as a 1-bit memory cell, while the eCRS mode serves as a 1bit parity cell. This dual-mode operation enables in-memory parity bit generation using the same memristor. We experimentally demonstrate XNOR-based operations utilizing the eCRS mode, verifying its use for error detection. Furthermore, the proposed scheme improves energy efficiency and uniformity compared to filament-based CRS devices, suggesting its scalability for larger arrays using parallel operations.

efficient parity bit generation through in-memory parity generation, minimizing overhead and potential errors during data delivery. When the THT memristors are integrated into a  $1 \times n$  line cell configuration, the eBRS mode device as a 1-bit encoded memory cell and the eCRS mode device as a 1-bit parity cell within the given interconnect line enable the desired in-memory parity generation.

#### Introduction

With the rapid development of artificial intelligence, the memory bottleneck issue, which refers to the critical burden of handling enormous data transfer between the memory and the processor, has become increasingly problematic. In response, alternative computing architectures, such as near-memory and in-memory computing, have emerged, benefiting from shorter or eliminated data paths between memory and computing

units. Resistive switching random-access memory (RRAM) has attracted significant attention for these applications due to its nonvolatile memory functionality, low power consumption, fast switching speed, and high scalability due to the simple two-terminal structure and stackable design. <sup>1-3</sup> However, the passive nature of the memory introduces sneak-current issues in a cross-bar array (CBA) structure, thereby undermining the reliability of circuit operation due to interference from adjacent cells, which limits large-scale integration and adversely affects logic operations.4 Furthermore, the risk of data corruption is higher due to more limited endurance than the complementary metal-oxide-semiconductor (CMOS) transistor.5,6

Various solutions have been proposed to address sneakcurrent issues. For instance, embedding selector devices (e.g., diodes, transistors, and threshold switches) into RRAM has been proposed.<sup>7,8</sup> However, the additional selectors induce higher operation voltages, increased variation, and integration complexity. Alternatively, self-rectifying RRAM that utilizes band alignment using one (i.e., top) electrode with a higher work function than the other (i.e., bottom) electrode can resolve sneak-current issues without using selectors.<sup>4</sup> The switching mechanism of reported self-rectifying RRAM typically relies on switching between electronic trapping/detrapping within the trap-rich layer. This approach offers higher endurance than the conductive filament formation/rupture mechanism, but lower retention at high temperatures and slower operation speeds.<sup>9</sup> Consequently, adopting an error-checking system to account for data degradation is crucial.

Recent works have demonstrated the detection and correction of various errors using XOR operations with parity bits in RRAM. 10-14 A single RRAM with complementary resistive switching (CRS) behavior can implement XOR operations within a single cycle, achieving the smallest chip area and high switching speed. 15 Nevertheless, no work has reported bidirectional self-rectifying (bSR) memristors with CRS behavior to simultaneously solve the sneak current and data reliability issues.

In this study, a low-power and high-reliability Ti/HfO2/Ti (THT) device is reported that exhibits electronic complementary resistive switching (eCRS) with bSR behavior. Ti is generally used as an active electrode due to its strong affinity for oxygen, allowing it to react with oxygen ions in the resistive switching (RS) layer.  $^{16,17}$  In particular, the interfacial  $TiO_x/HfO_x$  structure, formed through oxygen scavenging by Ti from HfO2, contributes significantly to the switching behavior by providing a defect-rich environment and acting as a reservoir for oxygen vacancies. Previous studies demonstrated that engineering the Ti/HfO2 interface to form TiOx can improve the RRAM switching characteristics. 18,19 In most RRAM devices, an active electrode is paired with an inert electrode to control oxygen vacancies in the RS layer and adjust the barrier height at the interface. However, this work used Ti thin films for both electrodes to form two distinct vacancy-rich RS layers, enabling the eCRS mode with bSR behavior. Structural analyses based on transmission electron microscopy (TEM), X-ray photoelectron spectroscopy (XPS), and electrical analyses through currentvoltage (I-V) measurements were conducted to understand the underlying origin of the bSR behavior. While many studies have reported electronic bipolar resistive switching (eBRS) based on an electron trapping/detrapping mechanism, this work introduces eCRS with bSR behavior, which can be utilized for inmemory parity generation in a CBA. Using the eCRS with bSR behavior, where the SET operation occurs in both the positive and negative bias regions, two distinctive low-resistance states (LRS) can be achieved in a single directional bias sweep. Consequently, eCRS behavior with bSR was demonstrated by setting the initial state to a LRS, followed by RESET (switching from a LRS to a high-resistance state (HRS)), and subsequent SET (switching from a HRS to another LRS). A single memory cell string with three THT devices was fabricated to demonstrate the 1-bit parity generation. Furthermore, the extension of the demonstrated parity generation to larger array sizes is proposed, along with its potential application in Hamming code-based error correction. Lastly, eCRS with bSR was compared with conventional CRS devices, demonstrating improved power efficiency and operation.

# Results and discussion

Structural and electrical analysis of the Ti/TiO<sub>2-x1</sub>/HfO<sub>v</sub>/  $TiO_{2-x2}/Ti$  structure

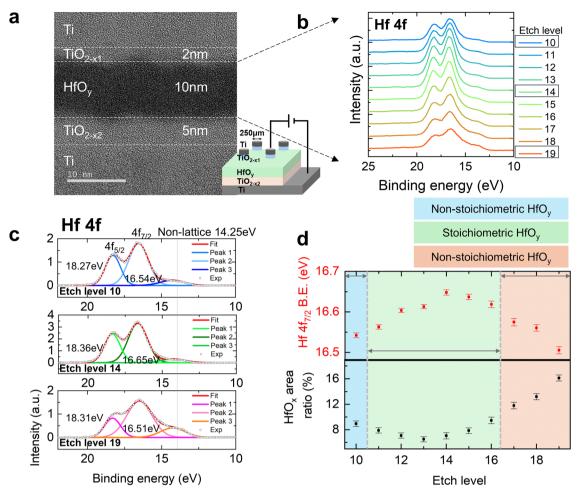

The THT memristor was examined through structural and electrical analysis. First, the crystal structure, suboxide formation, and chemical composition were analyzed using TEM and XPS. Fig. 1(a) shows a cross-section TEM image of the THT memristor, where an easily distinguishable layer structure with metallic Ti at the top and bottom, amorphous 10-nm-thick  $HfO_2$  in the middle, and amorphous  $TiO_{2-x1}$  and  $TiO_{2-x2}$  $(x_1, x_2 < 2)$  at the upper and lower Ti/HfO<sub>2</sub> interfaces could be recognized. The thickness of the upper  $TiO_{2-x_1}$  layer ( $\sim 2$  nm) appears thinner than the lower  $TiO_{2-x2}$  layer ( $\sim 5$  nm). Fig. S1 shows the chemical composition mapping results for Hf and Ti, obtained using energy-dispersive X-ray spectroscopy (EDS), indicating the well-defined 10-nm-thick  $HfO_2$ , thinner  $TiO_{2-x1}$  and thicker  $TiO_{2-x2}$ , consistent with the TEM image. The difference in the suboxides is related to the film growth process. The lower  $TiO_{2-x2}$  layer is formed in two steps. First, the Ti bottom electrode surface is exposed to air, forming a native oxide. It is then further oxidized by active oxygen atoms during the plasma-enhanced atomic layer deposition (PEALD) of HfO<sub>2</sub> film at a substrate temperature of 200 °C, with O<sub>2</sub> plasma as the oxygen source. <sup>20,21</sup> In contrast, the upper  $TiO_{2-x_1}$  layer is formed when the Ti top electrode is deposited by electron-beam evaporation, where Ti interacts with the underlying HfO2 layer and absorbs oxygen ions from the top portion of HfO2 at room temperature, resulting in fewer Ti-O interactions compared to the lower layer of  $TiO_{2-x2}$ .

XPS analysis was subsequently used to confirm the influence of the formation of  $TiO_{2-x1}$  and  $TiO_{2-x2}$  on the  $HfO_2$  layer. Fig. 1(b) shows the XPS depth profile results from the Hf 4f peak for the 10-nm-thick HfO2 layer. The Hf 4f peaks could be

Published on 30 2025. Downloaded on 27/08/25 20:15:22

Nanoscale Horizons Communication

Fig. 1 (a) A cross-sectional TEM image of the  $Ti/TiO_{2-x1}/HfO_v/TiO_{2-x2}/Ti$  structure. (b) XPS spectra of the Hf 4f region for a depth profile of the  $HfO_v$ layer. (c) Deconvolution of the Hf 4f peaks at etching levels of 10, 14, and 19. (d) Binding energy (upper panel) and HfO<sub>x</sub> area ratio (lower panel) shift analysis.

deconvoluted into a Hf 4f<sub>5/2</sub> peak, 4f<sub>7/2</sub> peak, and non-lattice  $HfO_x$  (x < 2) peak, with the binding energy of the non-lattice peak fixed at 14.25 eV. Fig. 1(c) shows the deconvoluted spectra from etch levels of 10 (upper HfO<sub>2</sub>), 14 (middle HfO<sub>2</sub>), and 19 (lower HfO<sub>2</sub>). The upper panel in Fig. 1(d) shows the clear shifting tendency of the binding energy of the Hf  $4f_{7/2}$  peak, which increases from 16.54 eV to 16.65 eV at depths of about 1 nm to 5 nm (etch level from 10 to 14), then decreases from 16.65 eV to 16.51 eV at depths of about 5 nm to 10 nm (etch level from 14 to 19). Based on the binding energy of the Hf  $4f_{7/2}$ peak of 16.7 eV for stoichiometric HfO2, 22 the shifts in the Hf 4f<sub>7/2</sub> binding energy suggest that the HfO<sub>2</sub> layer in the THT memristor has a stoichiometric composition in the middle. In contrast, the composition is nonstoichiometric (oxygen deficient) at the top and bottom interfaces. The lower panel of Fig. 1(d) shows the non-lattice  $HfO_x$  (x < 2) peak area ratio variation, which is consistent with the shifts in Hf  $4f_{7/2}$ . For the upper  $TiO_{2-x_1}/HfO_2$  interface, the area ratio of non-lattice  $HfO_x$ was 9%, which then decreased to 6% in the middle and then increased to 16% for the lower HfO<sub>2</sub>/TiO<sub>2-x2</sub> interface. Fig. S2 shows the XPS depth profiles of the O 1s and Ti 2p peaks, where

both the binding energy shift and non-lattice oxygen (or oxygen ions near oxygen vacancies (Vo)) area ratio follow the same trend observed in Hf 4f analysis, confirming Ti oxidation at both interfaces of the 10-nm-thick HfO2 layer and supporting the identification of the  $TiO_{2-x1}$  and  $TiO_{2-x2}$  interfacial layers. The XPS results confirmed that the 10-nm-thick HfO<sub>2</sub> layer contained a high concentration of V<sub>O</sub> formed at both interfaces compared to the relatively stoichiometric composition in the middle, resulting in a HfO<sub>v</sub> ( $y \le 2$ ) layer composition. Therefore, it can be concluded that the fabricated sample coincides with a  $Ti/TiO_{2-x1}/HfO_{y}/TiO_{2-x2}/Ti$  structure. It was reported that electronic switching requires a trap-rich layer (TL) to capture and release the carriers through electron trapping and detrapping mechanisms. 23 Therefore, TL1—comprising TiO<sub>2-x1</sub> and the adjacent upper portion of HfO<sub>ν</sub>—and TL2 consisting of the lower portion of  $HfO_{\nu}$  and  $TiO_{2-x2}$ —as confirmed by TEM and XPS analyses, are both expected to contribute to resistive switching behaviour in the THT memristor. The structural difference between the upper and lower interfaces, considered a key factor in asymmetric switching behavior, will be discussed below.

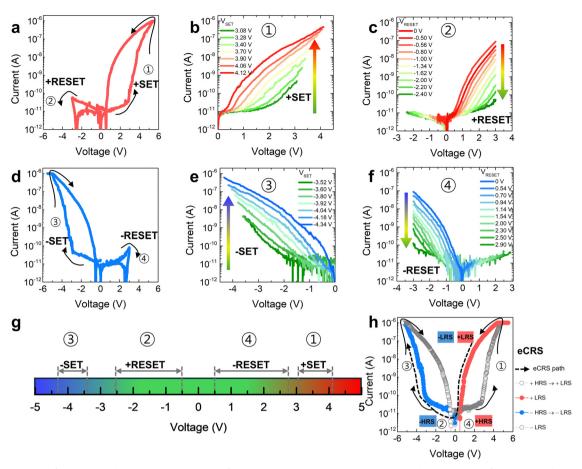

Fig. 2 (a) Positive eBRS operation of the THT device with a +SET voltage of 5 V, a compliance current of 1 μA and a +RESET voltage of –3 V. (b) Gradual SET switching from +HRS to +LRS with different set sweep voltages (3.08 V to 4.12 V). (c) Rectifying RESET switching from +LRS to +HRS with different reset sweep voltages from -0.50 V to -2.40 V, confirmed by a 3.0 V single sweep after each reset sweep. (d) Negative eBRS operation of the THT device. (e) Gradual -SET switching from -HRS to -LRS with different set sweep voltages (-3.52 V to -4.34 V). (f) Rectifying -RESET switching from -LRS to -HRS with different reset sweep voltages (from 0.54 V to 2.90 V) confirmed by a -3.0 V single sweep after each reset sweep. (g) A schematic diagram showing the THT device operation voltages with positive eBRS and negative eBRS. (h) eCRS with bSR operation obtained by the consecutive operation of positive eBRS and negative eBRS: switching from +HRS to +LRS, then resetting to -HRS, and back to -LRS.

Fig. 2 shows the two self-rectifying eBRS switchings of a pristine dot-type THT memristor with a top-electrode diameter of 250 µm. Fig. 2(a) shows a positive eBRS, having two transitions, with +SET (+HRS  $\rightarrow$  +LRS) in the positive bias region and +RESET (+LRS  $\rightarrow$  +HRS) in the negative bias region. Fig. 2(b) and (c) show the gradual SET and RESET operations with an increase in maximum sweep voltages from 3.08 V to 4.12 V and from -0.5 V to -2.4 V, respectively. The sign of the RESET operation is defined based on the polarity of the corresponding SET operation. For clarity, the HRS in the positive bias region is denoted as +HRS, while the HRS in the negative bias region is referred to as -HRS. Fig. 2(d) shows a negative eBRS, having two transitions, with -SET ( $-HRS \rightarrow -LRS$ ) and -RESET $(-LRS \rightarrow -HRS)$  operations. Similar to positive eBRS, Fig. 2(e) and (f) show the gradual –SET and –RESET operations from -3.52 V to -4.34 V and from 0.54 V to 2.90 V, respectively.

Fig. 2(g) summarizes the voltage ranges for the two eBRS switchings, where the two eBRS switchings can be combined for eCRS, as there is no overlapping of the voltage regions. Fig. S3 shows the dependence of the non-overlapping behavior on

HfO<sub>2</sub> thickness. THT devices with 4-nm- and 7-nm-thick HfO<sub>2</sub> layers exhibit overlapping voltage regions and unstable switching, while the 10-nm-thick HfO<sub>2</sub> device provides well-separated windows suitable for stable eCRS operation. Fig. 2(h) shows eCRS with bSR operation, where the THT memristor transitions from +LRS to -HRS and from -HRS to -LRS. The two resistive switchings (RSs) are possible as the THT device has naturally formed anti-serial RS layers of  $TiO_{2-x1}$  and  $TiO_{2-x2}$ . In other words, CRS operation is also possible in eBRS operations as the RS in two anti-serial BRS devices is equivalent to CRS operation.<sup>24</sup> Thus, the proposed THT device can perform eBRS and eCRS operations, which are defined as dual-mode switching.

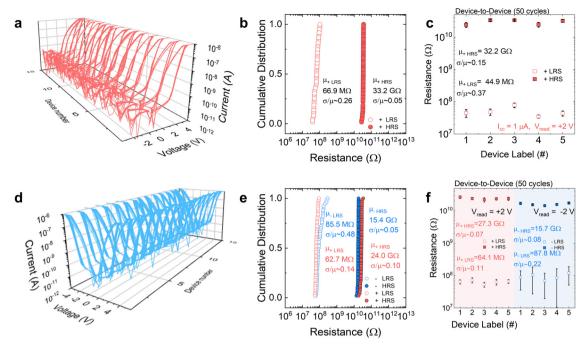

Fig. 3 shows the uniformity of the dual-mode switching in dot-type THT memristors with a diameter of 250 μm. Fig. 3(a) shows the positive eBRS curves acquired from 15 devices, each subjected to 10 cycles under a compliance current of 1 μA, confirming the high switching uniformity. Fig. 3(b) shows the cumulative probabilities of cycle-to-cycle variation in the resistance values of positive eBRS over 50 cycles of DC I-V sweeps at Nanoscale Horizons Communication

Fig. 3 (a) DC I-V switching cycles of positive eBRS for 15 devices, each measured over 10 cycles. (b) Cycle-to-cycle variation of positive eBRS over 50 cycles. (c) Device-to-device variation of positive eBRS for 5 devices over 50 cycles. (d) DC I-V switching cycles of eCRS for 15 devices, each measured over 10 cycles. (e) Cycle-to-cycle variation of eCRS over 50 cycles. (f) Device-to-device variation of eCRS for 5 devices over 50 cycles

a reading voltage of 2 V. In this work, the read margin is defined as the difference between the voltages at which the HRS and LRS reach 0.1 nA, which were ~3 V and 0.5 V, respectively.25 Therefore, the read voltage must be selected between these two voltage values. A read voltage of 2 V resulted in the lowest resistance value variations, while maintaining a sufficiently high on/off current ratio ( $\sim 500$ ). Therefore, 2 V was selected as the read voltage. The coefficients of variation (CV), which are defined as the standard deviation divided by the mean for positive eBRS, were 0.26 for +LRS and 0.05 for +HRS. Fig. 3(c) shows the median values of  $R_{+LRS}$  and  $R_{+HRS}$  acquired from five devices over 50 DC cycles to verify the device-to-device characteristics. The CVs for the +LRS and +HRS resistances were measured as 0.37 and 0.15, respectively. Likewise, Fig. 3(d) shows the eCRS curves from 15 different devices, each subjected to 10 cycles under a compliance current of 1  $\mu A$  for both polarities, showing the bSR properties. Fig. 3(e) shows the cumulative probabilities of cycle-to-cycle variation for eCRS over 50 cycles, obtained at a read voltage of  $\pm 2$  V. The evaluations included +LRS, +HRS, -LRS, and -HRS, and the corresponding CVs were 0.14 for +LRS, 0.10 for +HRS, 0.48 for -LRS, and 0.05 for -HRS. The observed difference in CV values between +LRS and -LRS is attributed to the Pre-SET process. Fig. S4 shows that positive eBRS operates in a forming-free fashion due to the higher defect density at the HfO<sub>v</sub>/TiO<sub>2-x2</sub> interface, whereas negative eBRS requires a Pre-SET process to induce switching at the opposite interface ( $TiO_{2-x_1}/HfO_{\nu}$ ), indicating that the active switching layer shifts depending on the bias polarity. Fig. 3(f) shows the median values of  $R_{+LRS}$ ,  $R_{+\mathrm{HRS}}$ ,  $R_{-\mathrm{LRS}}$ , and  $R_{-\mathrm{HRS}}$  of eCRS at a read voltage of  $\pm 2$  V,

acquired from device-to-device assessment over 50 cycles for five devices. The CVs were measured as 0.11 for +LRS and 0.07 for +HRS in the positive region, and 0.22 for -LRS and 0.08 for -HRS in the negative region. These results demonstrate the high uniformity and reliability of dual-mode switching in the THT memristor.

#### Mechanism of the THT memristor eCRS operation

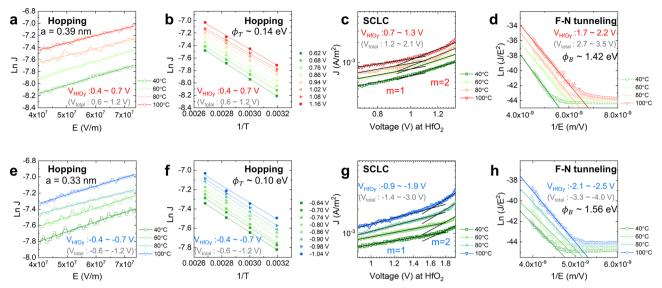

The mechanism of eCRS with bSR behavior in the THT memristor is further investigated by measuring the I-V curves of dottype devices with a diameter of 250 µm at temperatures from 313 K to 373 K (40–100 °C). These curves were analyzed according to various conduction mechanisms, including Schottky emission, hopping conduction, Fowler-Nordheim (F-N) tunneling, Poole-Frenkel (P-F) emission, ohmic conduction, direct tunneling, and space-charge-limited conduction (SCLC). The electric field for fitting was calculated by dividing the voltage across 2-nm  $TiO_{2-x1}$ , 10-nm  $HfO_{\nu}$ , and 5-nm  $TiO_{2-x2}$ , using a dielectric constant of 25 for amorphous  $HfO_{\nu}$ and 30 for the mixed amorphous and anatase phase in  $TiO_{2-x1}$ and  $TiO_{2-x2}$ . The phases of the layers were confirmed using TEM and XRD, with detailed and additional capacitance-frequency curve results shown in Fig. S5. 28,29 In the low voltage range of the positive region (LVR, 0.6 V to 1.2 V), electron charge injection from the Ti bottom electrode to TiO2-x2 proceeded smoothly due to the quasi-ohmic contact at the  $TiO_{2-x^2}/Ti$  interface. In contrast, charge injection from  $TiO_{2-x^2}$ to HfO<sub>v</sub> was hindered due to the high energy barrier. 30,31 Therefore, the electric field of  $HfO_{\nu}$  was used to fit the I-Vcurves at each temperature. The linear relationship seen in the

Fig. 4 (a) Hopping conduction in the HfO<sub>V</sub> layer (0.6 V to 1.2 V). (b) Arrhenius plots for the HfO<sub>V</sub> layer. (c) Double logarithmic I-V curves of the THT memristor in the positive region, showing ohmic (m = 1) and space-charge-limited conduction (m = 2) behavior (1.2 V to 2.1 V). (d) F-N tunneling in the  $HfO_v$  layer (2.7 V to 3.5 V). (e) Hopping conduction in the  $HfO_v$  layer (-0.6 V to -1.2 V). (f) Arrhenius plots for the  $HfO_v$  layer. (g) Double logarithmic I-Vcurves of the THT memristor in the negative region (-1.4 V to -3.0 V). (h) F-N tunneling in the HfO<sub>v</sub> layer (-3.3 V to -4.0 V).

ln I versus E plot at each temperature, as shown in Fig. 4(a), suggests that current conduction in the positive LVR is governed by hopping conduction, as described by eqn (1):

$$J = qan\nu \exp\left[\frac{qaE}{kT} - \frac{E_{\rm a}}{kT}\right] \tag{1}$$

where  $a, n, \nu, E_a$ , and k are the mean hopping distance, electron concentration at the conduction band, frequency of thermal vibrations of the trap site, activation energy, and Boltzmann constant, respectively.32

The hopping distance of 0.39 nm was calculated from the slopes of best-fit linear plots. Fig. 4(b) shows the ln *I versus* 1/*T* plots at different voltages. Following the hopping mechanism, a zero-field trap energy level ( $\phi_{\rm T}$ ) of 0.14 eV was extracted from the slopes of the best-linear-fit plots and their extrapolation to zero voltage. The low current level of +HRS observed in the I-V curve indicates that only a few excited electrons could transport through hopping in this region. In the intermediate voltage range (IVR, 1.2 V to 2.1 V), the voltage drop across the HfO<sub>v</sub> layer was used for analysis. Fig. 4(c) shows the double logarithmic I-V curves, where the conduction behavior is consistent with SCLC. In these regions, slope values of 1 and 2 were observed, corresponding to ohmic conduction and SCLC, respectively.<sup>33,34</sup> In the high voltage range of the positive region (HVR, 2.7 V to 3.5 V), the electric field of HfO<sub>v</sub> was again adopted, considering that while some excited electrons conduct through hopping conduction, the majority of carrier transport is limited by the insulating properties of the HfO<sub>v</sub> layer. Fig. 4(d) shows the  $ln(J/E^2)$  versus 1/E plot, which exhibits a linear relationship, indicating that conduction in HfO<sub>v</sub> in the HVR is governed by F-N tunneling, as described by eqn (2):

$$J = \frac{q^3 E^2}{8\pi h q \phi_{\rm B}} \exp\left[\frac{-8\pi \left(2q m_{\rm T}^*\right)^{1/2}}{3hE} \phi_{\rm B}^{3/2}\right] \tag{2}$$

where  $m_{\rm T}^*$  is the tunneling effective mass in the dielectric layer, h is the Planck constant, and  $\phi_{\rm B}$  is the barrier height. The F-N tunneling barrier height  $(\phi_B)$  extracted from the slope in the HVR was 1.42 eV, and the tunneling effective mass was given as 0.17  $m_0$ , which was taken from the literature.<sup>35</sup>

The current transport properties in the negative bias region were similarly analyzed using hopping conduction in the low voltage range of the negative region (-0.6 V to -1.2 V), SCLC in the intermediate voltage range (-1.4 V to -3.0 V) and F-N tunneling in the highly negative bias region (-3.3 V to -4.0 V). Fig. 4(e) and (f) show the fitting results for the LVR, confirming that hopping conduction dominates the conduction in HfO<sub>1</sub>, similar to the conduction in the LVR of the positive region. The similarly extracted hopping distance and  $\phi_{\rm T}$  values were  $\sim$  0.33 nm and 0.10 eV, respectively. Fig. 4(g) shows the double logarithmic I-V curves, where the conduction behavior is consistent with SCLC. In these regions, slope values of 1 and 2 were again observed, corresponding to ohmic conduction and SCLC, respectively. Fig. 4(h) shows the  $ln(I/E^2)$  versus 1/E plot. The  $\phi_B$ value for the F-N tunneling mechanism extracted from the slope in the HVR was 1.56 eV, similar to the value in the positive bias region. Therefore, these findings indicate that the trap-rich layer of TL1 or TL2 is filled with electrons in the LVR, depending on the polarity, with a few electrons crossing the middle HfO<sub>v</sub> through hopping. In the HVR, the electrons accumulated in TL1 or TL2 can be transported through the middle HfO<sub>v</sub> by F-N tunneling, switching +HRS to +LRS or -HRS to -LRS.

Nanoscale Horizons

а 1. Positive LVG: Hopping 2. Positive HVR: F-N tunneling 3. +LRS at zero bias  $\chi_{HfO_y}$  =2.14 eV  $\chi_{TiO_{2-x2}}$  = 4.0 eV  $\phi_B \sim 1.42 \text{ eV}$  $\phi_T \sim 0.14 \text{ eV}$ Ti Ti (BE) (BE) Ti Ti Ti (BE) (TE) ဋိ HfO. TiO (TE) (BE) 2nm 10nm 5nm TL1, TL 2: Trap-rich layer 4. Negative LVR: +LRS RESET 5. Negative LVR: Hopping 6. Negative HVR: F-N tunneling 7. -LRS at zero bias  $\phi_R \sim 1.56 \text{ eV}$ ~ 0.10 eV HfO<sub>v</sub> HfO<sub>v</sub> HfO, Τi Ti (TE) ₽ (BE) HfO. (BE) (BE)

Fig. 5 (a) A schematic band diagram of the THT memristor under zero bias conditions. (b) Schematic band diagrams showing the +SET (steps 1 to 3), +RESET (step 4), and -SET (steps 5 to 7) mechanisms based on charge trapping/detrapping.

Additional analysis, including the overall *I–V* curve and poor fitting based on Schottky and P–F emission, is given in Fig. S6.

A switching model for eCRS in the THT memristor was established based on the structural and electrical test results. Fig. 5(a) shows an energy band diagram of the THT memristor. The work function  $(\Phi)$  of the Ti electrode is assumed to be 4.33 eV, and the electron affinity ( $\chi$ ) values of TiO<sub>2-x1</sub>, HfO<sub> $\nu$ </sub>, and  $TiO_{2-x2}$  are taken from the reference values (4.0 eV for  $TiO_{2-x1}$ , 2.14 eV for HfO<sub>v</sub>, and 4.0 eV for  $TiO_{2-x2}$ ). <sup>36,37</sup> Step 1 in Fig. 5(b) shows the positive LVR of the THT device. When a positive bias is applied to the Ti top electrode, electrons rapidly fill TL2—comprising  $TiO_{2-x2}$  and the lower  $HfO_y$  layer—owing to the quasi-ohmic contact between  $TiO_{2-x2}$  and the bottom Tielectrode. However, the movement of electrons to the top electrode is hindered by an energy barrier between HfO<sub>v</sub> and  $TiO_{2-x2}$ , and only a few excited electrons can flow to the top electrode via hopping conduction. Step 2 shows F-N tunneling in the positive HVR, where electrons in TL2 tunnel through the thin potential barrier of HfO<sub>v</sub>. After tunneling through the HfO<sub>v</sub> layer, the electrons readily move through  $TiO_{2-x_1}$  and reach the Ti top electrode due to the electron affinity difference between  $HfO_y$  and  $TiO_{2-x1}$ . Therefore,  $HfO_y$  acts as a blocking layer in response to low electric fields and a tunneling path under high electric fields. Step 3 shows the +LRS at zero bias, where electrons remain trapped in the TL2 trap sites even after the voltage is removed. In this state, the traps in TL2 are filled, decreasing the energy barrier at the  $HfO_{\nu}$  and  $TiO_{2-x2}$  interface and allowing efficient electron transport when a positive bias is subsequently applied. Fig. S7 shows the endurance of eCRS over 10<sup>3</sup> cycles and the retention of +LRS for over 30 000 s at room temperature, with gradual decay. Such stable retention in

electronic switching devices can be attributed to the absence of an internal field, which is induced by the identical work functions of the electrodes; this can hardly be achieved when two electrodes with different work functions (e.g., Pt and Ti (or TiN)) are adopted. 31,38 Step 4 shows the de-trapping of electrons from TL2 to the Ti bottom electrode under a negative bias at the Ti top electrode. In step 5, electrons are rapidly injected from the Ti top electrode to TL1, consisting of  $TiO_{2-x1}$  and upper HfO<sub>v</sub>, due to Ti/TiO<sub>2-x1</sub> quasi-ohmic contact. Conduction is dominated by hopping, as a few excited electrons move through  $HfO_y$  while the energy barrier at the  $HfO_y$  and  $TiO_{2-x1}$  interface restricts others. Step 6 shows that at a sufficiently high negative bias, HfO<sub>v</sub> becomes thin enough for the electrons from TL1 to transit through F-N tunneling and reach the Ti bottom electrode, switching to -LRS. Similarly, step 7 shows that under zero-bias conditions, electrons remain trapped at the TL1 trap sites, indicating –LRS. From step 1 to step 7, HfO<sub>v</sub> serves as a blocking and switching layer. As a blocking layer, the middle part of HfO, prevents electrons injected at low voltage from moving to the opposite electrode, enabling rectifying behavior. As a switching layer,  $HfO_{\nu}$  at both interfaces, along with  $TiO_{2-x1}$ and  $TiO_{2-x2}$ , provides trap sites. Therefore, the dual-mode switching of the THT memristor can be understood from the structure, where two serially connected TL1 and TL2 layers are formed at both interfaces, separated by the middle part of the HfO, layer, trapping and detrapping electrons depending on the polarity.

Ti (BE)

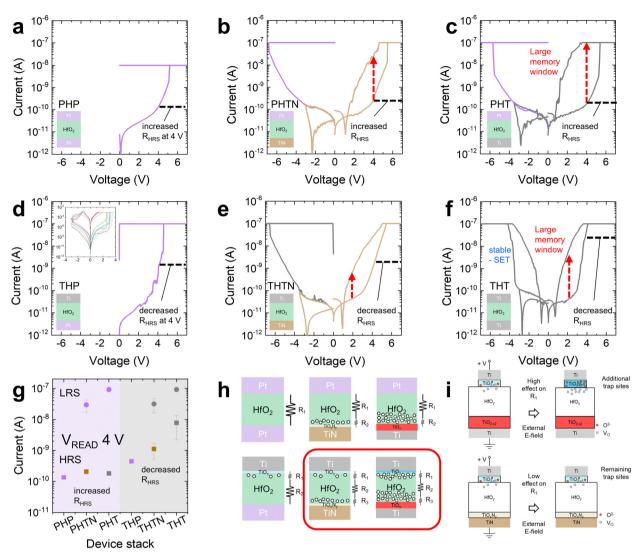

The I-V characteristics of MIM stacks with a 10-nm-thick  $HfO_2$  layer and electrodes with different work functions and oxygen reactivities (Pt, TiN, and Ti) were examined to verify the effects of electrodes. Fig. 6(a)–(c) show the I-V characteristics of

Fig. 6 Resistive switching I-V curves of (a) Pt/10-nm-thick HfO<sub>2</sub>/Pt, (b) Pt/10-nm-thick HfO<sub>2</sub>/TiN, (c) Pt/10-nm-thick HfO<sub>2</sub>/Ti, (d) Ti/10-nm-thick HfO<sub>2</sub>/Pt, (e) Ti/10-nm-thick HfO<sub>2</sub>/TiN, and (f) Ti/10-nm-thick HfO<sub>2</sub>/Ti devices. (g) LRS/HRS current distributions for different stacked devices. (h) Schematic diagrams of devices with different electrodes containing an HfO<sub>2</sub> layer and corresponding interface oxide layers; each layer is represented as a series resistance component ( $R_1$  to  $R_3$ ). (i) The formation of additional trap sites depending on differences in the external electric field distribution at the top interface ( $R_3$ ), in the HfO<sub>2</sub> bulk layer ( $R_2$ ), and at the bottom interface ( $R_3$ ) for THTN and THT.

Pt/HfO<sub>2</sub>/Pt (PHP), Pt/HfO<sub>2</sub>/TiN (PHTN), and Pt/HfO<sub>2</sub>/Ti (PHT). The inert top Pt electrode is invariant in these configurations, while the bottom electrode is varied. None of the three devices exhibited stable -SET behavior. The PHP device exhibited a breakdown at a compliance current of 10 nA. This failure is attributed to the Schottky barrier between HfO2 and Pt, as well as the low oxygen vacancy density at the interface due to the low reactivity of Pt. However, when the bottom electrode was changed to TiN or Ti, self-rectifying behavior was observed due to their relatively low work functions ( $\Phi_{\text{TiN}}$  = 4.5 eV;  $\Phi_{\text{Ti}}$  = 4.3 eV) and high oxygen reactivity compared to Pt ( $\Phi_{\mathrm{Pt}}$  = 5.3 eV). <sup>39,40</sup> In particular, the PHT device exhibited an increased switching memory window compared to PHTN, which is attributed to a more V<sub>O</sub>-rich interface at the Ti interface than at the TiN interface. Fig. 6(d)–(f) show devices where the Pt top electrode was replaced with a Ti top electrode. The configurations include Ti/HfO<sub>2</sub>/Pt (THP), Ti/HfO<sub>2</sub>/TiN (THTN), and Ti/HfO<sub>2</sub>/Ti (THT). Stable eCRS with bSR behavior was observed only in the THT configuration. The breakdown of the THP device implies that +SET behavior is associated with the bottom interface. The THTN and THT devices exhibited switching windows comparable to PHTN and PHT but with decreased  $R_{HRS}$  values due to Ti's low work function and high oxygen affinity. However, THTN did not exhibit SET behavior in the negative bias region, indicating that the -SET behavior is not solely governed by the top interface. Fig. 6(g) shows the current distribution for each stack acquired from six devices over 10 I-V cycles at a read voltage of 4 V. RHRS decreased when the top electrode was changed from Pt to Ti, while  $R_{LRS}$  was barely affected. This finding suggests that while the entire RS layer influences the HRS state, the bottom layer, where electron injection occurs, plays a more significant role in determining  $R_{LRS}$ . This finding

Nanoscale Horizons Communication

is consistent with the observation that the LRS current increased when the bottom electrode was changed from TiN (PHTN and THTN) to Ti (PHT and THT), considering the higher trap-site density in the bottom layer. Fig. 6(h) shows a schematic representation where each layer in a stack composed of the HfO<sub>2</sub> layer and interface layers is treated as a single resistance component connected in series, explaining the differences in switching behavior depending on the top/bottom electrode. The PHP device has no Vo-rich interface on either side, resulting in the highest R<sub>HRS</sub>. In contrast, HfO<sub>2</sub> with TiN or Ti shows V<sub>O</sub>-rich interfaces, with the Ti interface having a higher V<sub>O</sub> concentration than the TiN interface. Based on the electrode materials, the relative resistance in the HRS state can be deduced as following the order:  $R_{PHP} > R_{PHTN} > R_{THP} >$  $R_{\mathrm{PHT}} > R_{\mathrm{THTN}} > R_{\mathrm{THT}}$ . This relationship matches the median value of HRS current measured at 4 V in Fig. 6(g), except for the PHT and THP devices. The lower HRS current in PHT compared to THP can be attributed to breakdown events. As expected, the HRS current at 2 V is lower in THP than in PHT. Consequently, the series resistance, composed of the HfO2 bulk layer and the interface layers, is associated with the switching characteristics of each device. Compared to other configurations, the stable negative SET behavior observed in THT originates from the electric field distribution determined by the composition of the series resistance. Both THTN and THT exhibit the lowest overall resistance among all configurations, and they consist of a top

interface  $(R_1)$ , the HfO<sub>2</sub> bulk layer  $(R_2)$ , and a bottom interface  $(R_3)$ . In THTN, the bottom interface has a relatively low  $V_O$ concentration, leading to most of the electric field being distributed across  $R_2$  and  $R_3$ . In contrast, in THT, the bottom interface with a high Vo concentration decreases R3, which allows the electric field to also be applied to  $R_1$ . This results in the highest electric field existing at the top interface in THT, promoting additional reactions between Ti and HfO2, generating more Vo, and enabling stable negative SET behavior, as shown in Fig. 6(i). Overall, the suppressed negative eBRS behavior observed in both Pt and TiN devices suggests that the formation of the top interfacial TiO<sub>x</sub> layer is more likely driven by chemical interactions rather than deposition-induced effects.

# Implementation of an XNOR logic gate and in-memory parity bit generation

XOR/XNOR gates are building blocks for various applications, such as encryption, arithmetic operations, and error handling. It was reported that the CRS can implement these functionalities in a sequential logic array; therefore, the eCRS described above can also be used for the same applications. <sup>14</sup> However, as discussed here, eCRS can offer additional merit for error correction by generating an in-memory parity bit.

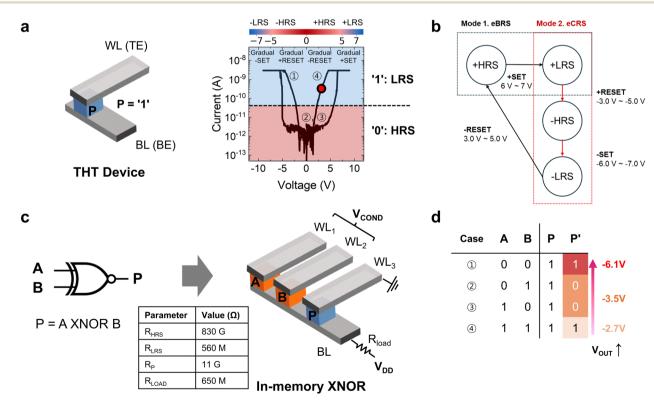

Three THT memristors are fabricated with a common bit line (BL) connected to a load resistor for demonstration.

Fig. 7 An in-memory XNOR gate composed of three THT memristors connected in parallel with a common BL connected to a load resistor. (a) Electrical characteristics of the crosspoint THT memristor. (b) A state transition diagram for the THT memristor representing the required applied bias for eBRS and eCRS. (c) Implementation of the XNOR gate in  $1 \times 3$  memristors. The WLs of the input and output memristors are connected to  $V_{\text{COND}}$  and GND, respectively. (d) The truth table of the XNOR gate. As the number of '1's in the input memristors decreases, the higher the voltage drop across the output

An XNOR logic gate can be implemented by representing the logical states '1' and '0' using the  $\pm$ LRS and  $\pm$ HRS of a memristor, respectively. Fig. 7(a) shows a single THT memristor initialized to +LRS. The bias conditions for eCRS and eBRS of the crosspoint THT memristor are summarized in the state transition diagram shown in Fig. 7(b). Depending on the magnitude of the applied negative bias, eCRS occurs from +LRS to -HRS or -LRS. Fig. 7(c) illustrates an in-memory XNOR gate based on two-input memristors, A and B. This operation is achieved by applying a conditional voltage ( $V_{\rm COND}$ ) to the word lines (WLs) of A and B, GND to the WL of the output memristor P, and a driving voltage ( $V_{\rm DD}$ ) to the BL through the load resistance ( $R_{\rm load}$ ). As the number of '1's in the input cells increases, the applied voltage across the P memristor decreases due to the voltage divider effect, as described by eqn (3) and (4):

$$V_{\text{OUT,P}} = \frac{R_{\text{P}}R_{\text{eq}}}{R^*}V_{\text{DD}} + \frac{R_{\text{load}}R_{\text{P}}}{R^*}V_{\text{COND}}$$

(3)

$$R^* = R_{eq}R_{load} + R_{load}R_{P} + R_{eq}R_{P}$$

(4)

where  $R_P$ ,  $R_{eq}$ , and  $R^*$  are the resistance of the P memristor, the equivalent resistance, and the proportional resistance, respectively. Fig. 7(d) shows the truth table of the XNOR gate, where P and P' represent the initial and final states of the P memristor, respectively. When both A and B are '1' (case 4), the

P memristor remains in a +LRS state as the lowest  $V_{\rm OUT,P}$  is applied, as described in eqn (3). Cases 2 and 3 have the same number of '1's and a higher voltage drop than case 4, so the P memristor undergoes +RESET at  $\sim$  -3.5 V, resulting in -HRS. Case 1 has the highest  $V_{\rm OUT,P}$ , resulting in the -LRS state. The load resistor and the resistance of the P memristor are set to 650 M $\Omega$  and 11 G $\Omega$ , respectively, to prevent resistance changes in the input memristors. Fig. S8 explains the input stability.

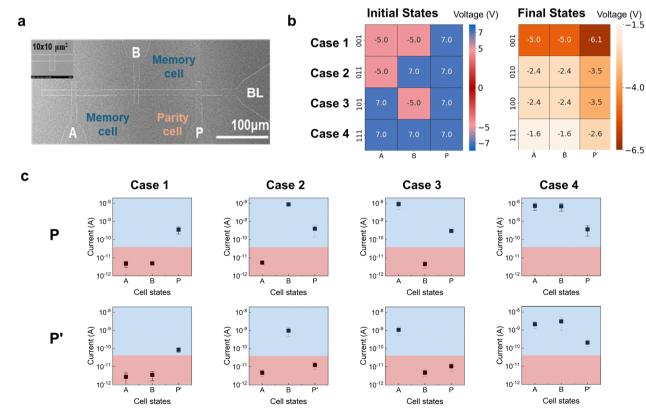

Fig. 8(a) shows an SEM image of the  $1 \times 3$  arrangement of THT memristors, each with a switching area of  $10 \times 10 \, \mu \text{m}^2$ , used for the experimental demonstration of the XNOR logic operation. The optimal bias conditions for the conditional switching of the P memristor are selected based on the resistance states of the THT memristors, as described by eqn (3) and (4).  $V_{\rm DD}$  and  $V_{\rm COND}$  are set to -6.5 V and -1 V, respectively. Fig. 8(b) shows heatmaps representing the voltage drop across each memristor for each input case's initial and final states. Fig. 8(c) shows 15 cycles of XNOR operation with an average CV of 0.42. Logical '1' and '0' were determined based on whether the read current was  $>5 \times 10^{-11}$  A or  $<5 \times 10^{-11}$  A. A read voltage of 4 V was applied to the BL when the common node voltage of the bias controller exceeded -6.1 V and to the WL when it was lower to preserve the output state during the sensing step after the XNOR operation. Although the sensing operation is required after each logic cycle when a single XNOR

Fig. 8 Experimental demonstration of an XNOR logic gate. (a) A top-view SEM image of the  $1 \times 3$  THT memristor consisting of two input cells and an output cell. (b) The voltage drop across each memristor in the initial and final states for each XNOR logic gate input case. (c) The results from 15 cycles of the XNOR gate.

Nanoscale Horizons Communication

operation is performed, the cost is negligible when the readout is conducted only after multiple logic operations are completed, such as in Hamming code applications.

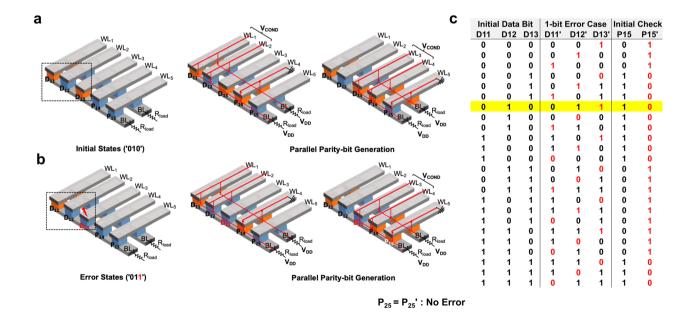

Accordingly, given that error detection and correction using the Hamming code rely on XOR or XNOR logic gates, a parallel in-memory error handling method for three data bits per BL is proposed using the two-input XNOR logic gate. Fig. 9 shows the parallel error detection method for three-input data bits in  $2 \times 5$  memristors. When the initial data is stored in the memory array, the first parity bit is generated and stored in the P<sub>15</sub> cell using the two XNOR logic gates. Fig. 9(a) shows a  $2 \times 5$  array of memristors for handling three data bits (D<sub>11</sub>,  $D_{12}$ ,  $D_{13}$ : '010') in  $BL_1$  and  $(D_{21}, D_{22}, D_{23}$ : '011') in  $BL_2$ . The parity bit for the first and second bits is generated and stored in the 4th positions ( $P_{14}$  and  $P_{24}$ ) by applying  $V_{COND}$  to  $WL_1$  and  $WL_2$ , GND to  $WL_4$ , and  $V_{DD}$  to  $BL_1$  and  $BL_2$ . Then, the threeinput parity bits are generated using the XNOR logic operation and stored in the 5th positions (P15 and P25). The two XNOR logic gates are equivalent to the three-input XNOR gate described in eqn (5) and (6):

$$P_{14} = \overline{D_{11} \oplus D_{12}} \tag{5}$$

$$P_{15} = \overline{D_{11} \oplus D_{12} \oplus D_{13}} = \overline{P_{14} \oplus D_{13}}$$

(6)

Once a single-bit error occurs in the data, error detection can be performed by regenerating the parity bit. Fig. 9(b) shows an example of the error case where the D<sub>13</sub> cell is flipped from '0' to '1' in BL<sub>1</sub> while the data bit in BL<sub>2</sub> remains unchanged. The error is detected when the regenerated parity bit,  $P'_{15}$ , differs from the previous parity bit, P<sub>15</sub>. Fig. 9(c) summarizes the error detection process for all single-bit error cases. The proposed

in-memory parity generation can be performed in parallel and extended to larger array sizes. Additionally, error detection and correction can be carried out using the Hamming code, as discussed in Fig. S9. Furthermore, the proposed THT memristor can be operated in eBRS or eCRS mode in the same array structure, depending on the initial state. As BRS and CRS operations in memristors can perform all 16 Boolean logic functions using logic cascading, 15,41 the proposed XNOR logic based on a THT memristor can be utilized in arithmetic operations to minimize costs.

#### Comparison of memristive CRS

The general mechanism for conventional CRS is based on the formation of an hourglass-shaped conductive filament (the SET operation) with the rupture of the conductive filament at the thinnest point due to the Joule heating effect. 42 Consequently, the high energy consumption and variation in CRS operation due to heat effects are inevitable, resulting in the memristor's low endurance. In contrast, the proposed THT memristor showed improved stability and power efficiency, with low fabrication cost, when performing CRS operation compared to other devices. Table 1 compares CRS operation in terms of ON/OFF ratio, retention, endurance, power, multilevel capabilities, variability, and cost. The high ON/OFF ratio is related to immunity to variation and multilevel performance. The proposed THT device has a high ON/OFF ratio due to the low HRS current from its self-rectifying characteristics. As the switching mechanism is related to electronic switching that does not involve the Joule heating effect, CRS can be operated with higher endurance than filamentary switching, while maintaining the lowest power consumption. In addition, the THT

Fig. 9 Parallel error detection for three input data bits in 2 × 5 memristors. The XNOR logic gates can be operated in parallel along the BL. (a) Parity-bit generation using two XNOR logic gates (b) The 1-bit error detection process when the BL1 data is flipped from '010' to '011'. (c) The parity bits for all possible 1-bit error cases for the three data bits.

Table 1 A comparison of various CRS device structures and their electrical characteristics

| Ref.      | Device structure                                                                         | On/off ratio | Retention (s)   | Endurance | Power (W cm <sup>-2</sup> ) | Multilevel | Mechanism            | Variability | Cost |

|-----------|------------------------------------------------------------------------------------------|--------------|-----------------|-----------|-----------------------------|------------|----------------------|-------------|------|

| 43        | Au/a-C/a-C:Cu/Au                                                                         | 10           | _               | $10^{4}$  | 7.5                         | No         | Filamentary          | 1.5         | High |

| 44        | ITO/GO/Au NPs/Al <sub>2</sub> O <sub>3</sub> /Al                                         | 10           | $4 \times 10^3$ | 150       | 0.03                        | No         | Filamentary          | 0.3         | High |

| 45        | TiN/HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> /TiO <sub>x</sub> /IrO <sub>x</sub> | $10^{2}$     | $10^{4}$        | $10^{3}$  | _                           | Yes        | Filamentary          | 1.6         | Low  |

| 46        | Ag/r-TiO <sub>2</sub> /FTO                                                               | 10           | $10^{4}$        | $10^{2}$  | _                           | No         | Filamentary          | 0.7         | High |

| 47        | Pt/TiO <sub>x</sub> /TiO <sub>2</sub> /TiO <sub>x</sub> /Pt                              | < 10         | $10^{6}$        | $10^{5}$  | 700                         | No         | Filamentary          | 0.3         | High |

| 48        | Au/SrFeO <sub>x</sub> /SrRuO <sub>3</sub>                                                | 50           | $10^{3}$        | $10^{2}$  | 400                         | Yes        | Filamentary          | 0.8         | High |

| This work | Ti/HfO <sub>2</sub> /Ti                                                                  | $10^{3}$     | $3 \times 10^4$ | $10^{3}$  | 0.006                       | Yes        | Electronic switching | 0.3         | Low  |

device exhibited a low variability of 0.3, which is given by the following equation:

$$\frac{\max(I_{\text{on}}) - \min(I_{\text{on}})}{\operatorname{median}(I_{\text{on}})} \tag{7}$$

where  $I_{\rm on}$  is the current level of the LRS. In this work, the native oxidation of Ti electrodes reduces the fabrication costs without using noble metals or multiple layers. Therefore, the proposed THT memristor has the potential to be used in CRS applications with low power consumption and variability. Utilizing the multilevel characteristic can expand CRS operation from a 1-bit parity bit to multi-bit parity bit generation to process more data per operation. 13 Although this requires a sensing scheme with additional peripheral circuits, it can increase data reliability in in-memory computing.

# Conclusions

In this work, a  $\text{Ti/TiO}_{2-x1}/\text{HfO}_{\nu}/\text{TiO}_{2-x2}/\text{Ti}$  memristor is proposed that exhibits dual-mode switching. The dual-mode switching mechanism is presented based on the anti-serial connection of TL1 and TL2, which act as RS layers, whereas the middle part of HfO<sub>v</sub> acts as a blocking layer. The active Ti electrodes play a crucial role in forming the  $TiO_{2-x1}$  and  $TiO_{2-x2}$  layers and introducing nonstoichiometric interfaces with adjacent HfO<sub>v</sub>, which reversibly trap or detrap electrons depending on the polarity. The proposed memristor shows advantages over conventional CRS devices by utilizing eBRS for the memory cell and eCRS for the parity cell during in-memory parity generation. In addition, trap-based eCRS outperforms reported CRS devices based on the filament mechanism in terms of low power consumption and uniformity. Consequently, the dual-mode switching of the proposed device can be utilized further for applications that require XOR operations, such as error correction codes and in-memory Hamming codes.

# **Methods**

#### Device fabrication and structural analysis

Dot-type: the THT memristor was fabricated in dot-type with a 125  $\mu m \times$  125  $\mu m \times \pi$  area. Using an electron-beam evaporator (SORONA, SRN-200), a 50-nm-thick Ti bottom electrode was deposited on a SiO<sub>2</sub>/Si substrate. A 10-nm-thick HfO<sub>2</sub> switching layer was deposited via plasma-enhanced atomic layer deposition (CN-1, Atomic Premium plus 200) using tetrakis(ethylmethylamino)-hafnium and O2 plasma as the Hf precursor and oxygen source, respectively, with an O2 plasma power of 100 W at a substrate temperature of 200 °C. The PEALD sequence was as follows: a 0.5-s Hf-precursor pulse; a 15-s Ar purge; a 7-s O<sub>2</sub> plasma pulse; and a 15-s Ar purge. Then, a 50-nm-thick Ti top electrode was deposited using the e-beam evaporator, followed by lift-off.

1 × 3 THT memristor: a 50-nm-thick Ti layer was deposited on a SiO<sub>2</sub>/Si substrate using an electron-beam evaporator (SORONA, SRN-200). Photolithography was performed using a maskless lithography system (NanoSystem Solutions, Inc., DL-1000 HP). A Ti common BL with a line width of 10 μm was formed by dry etching using an ICP etcher (Oxford, Plasma Pro System 100 Cobra). A 10-nm-thick HfO2 switching layer was deposited under conditions identical to those used for the dot-type cell. Three Ti WLs with a line width of 10 μm were patterned by photolithography, followed by 50-nm-thick Ti layer deposition via electron-beam evaporation and subsequent lift-off. The pad-open process used an ICP etcher (Oxford, Plasma Pro system 100 Cobra) with Cl2 and Ar plasma.

The X-ray photoelectron spectroscopy (XPS) data were acquired with Axis Supra (Kratos, UK) equipment using a monochromatic Al Ka source. The depth profiling was performed in situ via Ar<sup>+</sup> ion etching with an acceleration voltage of 5 kV in the XPS chamber. The binding energies were corrected relative to the C 1s signal at 284.5 eV. Transmission electron microscopy (TEM, JEOL, JEM-ARM200F) was used for structure analysis.

#### Characterization

The electrical properties were measured using a semiconductor parameter analyzer (Hewlett-Packard 4155A and 4155B). A direct current (DC) voltage bias was applied to the top Ti electrode while the bottom Ti electrode was grounded. All electrical measurements were conducted using a LabVIEWbased interface.

# Author contributions

Hyun Young Kim designed and conducted the experiments and wrote the manuscript. Taegyun Park designed logic application. Néstor Ghenzi developed a LabVIEW-based measurement program for device characterization. Hyung Jun Park and Dong Hoon Shin contributed to data analysis and provided insightful advice. Dong Yun Kim, Tae Won Park, and Jea Min Cho assisted with data interpretation. Taegyun Park and Cheol Seong Hwang supervised the overall research and manuscript preparation.

Nanoscale Horizons Communication

# Conflicts of interest

There are no conflicts to declare.

# Data availability

Raw data are available from the corresponding author upon reasonable request.

All the data that support this study are included in this article and SI. See DOI: https://doi.org/10.1039/d5nh00256g

# Acknowledgements

This work was supported by the National Research Foundation of Korea (grant no. 2020R1A3B2079882).

# References

- D. Silver, J. Schrittwieser, K. Simonyan, I. Antonoglou, A. Huang, A. Guez, T. Hubert, L. Baker, M. Lai, A. Bolton, Y. T. Chen, T. Lillicrap, F. Hui, L. Sifre, G. van den Driessche, T. Graepel and D. Hassabis, *Nature*, 2017, 550, 354–359.

- 2 J. W. Jeon, B. Park, Y. H. Jang, S. H. Lee, S. Jeon, J. Han, S. K. Ryoo, K. D. Kim, S. K. Shim, S. Cheong, W. Choi, G. Jeon, S. Kim, C. Yoo, J. K. Han and C. S. Hwang, ACS Appl. Mater. Interfaces, 2024, 16, 15032–15042.

- 3 G. Kim, V. Kornijcuk, D. Kim, I. Kim, C. S. Hwang and D. S. Jeong, *Micromachines*, 2019, **10**, 219.

- 4 J. Y. Seok, S. J. Song, J. H. Yoon, K. J. Yoon, T. H. Park, D. E. Kwon, H. Lim, G. H. Kim, D. S. Jeong and C. S. Hwang, *Adv. Funct. Mater.*, 2014, 24, 5316–5339.

- 5 K. Huang, P. H. Siegel and A. A. Jiang, 2020 International Symposium on Information Theory (ISIT), IEEE, Los Angeles, CA, USA, 2020, pp. 2694–2699.

- 6 D. Niu, Y. Xiao and Y. Xie, 2012 17th Asia and South Pacific Design Automation Conference (ASP-DAC), IEEE, Sydney, NSW, Australia, 2012, pp. 79–84.

- 7 L. Shi, G. Zheng, B. Tian, B. Dkhil and C. Duan, *Nanoscale Adv.*, 2020, 2, 1811–1827.

- 8 R. Waser and M. Aono, Nat. Mater., 2007, 6, 833-840.

- 9 S. Choi, T. Moon, G. Wang and J. J. Yang, *Nano Convergence*, 2023, **10**, 58.

- 10 N. Xu, T. G. Park, H. J. Kim, X. Shao, K. J. Yoon, T. H. Park, L. Fang, K. M. Kim and C. S. Hwang, *Adv. Intell. Syst.*, 2020, 2, 190082.

- 11 T. Park, Y. R. Kim, J. Kim, J. Lee and C. S. Hwang, *Adv. Intell. Syst.*, 2022, **4**, 2100267.

- 12 T. Park, Y. R. Kim, D. H. Shin, B. J. Lee and C. S. Hwang, *Adv. Intell. Syst.*, 2023, 5, 2200341.

- 13 K. J. Yoon, J. W. Han and W. Bae, *Adv. Electron. Mater.*, 2020, **6**, 2000672.

- 14 N. Xu, T. Park, K. J. Yoon and C. S. Hwang, *Phys. Status Solidi RRL*, 2021, **15**, 2100208.

- 15 S. Gao, F. Zeng, M. Wang, G. Wang, C. Song and F. Pan, Sci. Rep., 2015, 5, 15467.

- 16 M. Sowinska, T. Bertaud, D. Walczyk, S. Thiess, M. A. Schuber, M. Lukosius, W. Drube, Ch Walczyk and T. Schroeder, Appl. Phys. Lett., 2012, 100, 233509.

- 17 P. Calka, M. Sowinska, T. Bertaud, D. Walczyk, J. Dabrowski, P. Zaumseil, C. Walczyk, A. Gloskovskii, X. Cartioxa, J. Sune and T. Schroeder, ACS Appl. Mater. Interfaces, 2014, 6, 5056–5060.

- 18 Y. Kim, Y. J. Kwon, J. Kim, C. H. An, T. Park, D. E. Kwon, H. C. Woo, H. J. Kim, J. H. Yoon and C. S. Hwang, Adv. Electron. Mater., 2019, 5, 1800806.

- B. Ku, Y. Abbas, S. Kim, A. S. Sokolov, Y.-R. Jeon and C. Choi, *J. Alloys Compd.*, 2019, 797, 277–283.

- 20 D. Walczyk, T. Bertaud, M. Sowinska, M. Lukosius, M. A. Schubert, A. Fox, D. Wolansky, A. Scheit, M. Fraschke, G. Schoof, C. Wolf, R. Kraemer, B. Tillack, R. Korolevych, V. Stikanov, C. Wenger, T. Schroeder and C. Walczyk, 2012 International Semiconductor Conference Dresden-Grenoble (ISCDG), IEEE, Grenoble, France, 2012, pp. 143–146.

- 21 V. A. Matveev, N. K. Pleshanov, A. P. Bulkin and V. G. Syromyatnikov, *J. Phys.: Conf. Ser.*, 2012, **340**, 012086.

- 22 W. Zhang, J. Z. Kong, Z. Y. Cao, A. D. Li, L. G. Wang, L. Zhu, X. Li, Y. Q. Cao and D. Wu, *Nanoscale Res. Lett.*, 2017, 12, 393.

- 23 K. M. Kim, J. M. Zhang, C. Graves, J. J. Yang, B. J. Choi, C. S. Hwang, Z. Y. Li and R. S. Williams, *Nano Lett.*, 2016, 16, 6724–6732.

- 24 E. Linn, R. Rosezin, C. Kügeler and R. Waser, *Nat. Mater.*, 2010, **9**, 403–406.

- 25 T. W. Park, J. Moon, D. H. Shin, H. J. Kim, S. S. Kim, J. M. Cho, H. Park, K. S. Woo, D. Y. Kim, S. Cheong, H. Song, J. H. Shin, S. H. Lee, N. Ghenzi and C. S. Hwang, ACS Appl. Mater. Interfaces, 2024, 16, 65046–65057.

- 26 D. Acharyya, A. Hazra and P. Bhattacharyya, Microelectron. Reliab., 2014, 54, 541–560.

- 27 M. S. Islam, S. Sadman, A. S. M. J. Islam and J. Park, AIP Adv., 2020, 10, 035202.

- 28 Q. Cheng, W. Ahmad, G. Liu and K. Wang, 2011 11th International Conference on Nanotechnology, IEEE, Portland, OR, USA, 2011, pp. 1598–1601.

- 29 V. Dang, H. Parala, J. H. Kim, K. Xu, N. B. Srinivasan, E. Edengeiser, M. Havenith, A. D. Wieck, T. de los Arcos, R. A. Fischer and A. Devi, *Phys. Status Solidi A*, 2014, 211, 416–424.

- 30 J. H. Yoon, K. M. Kim, S. J. Song, J. Y. Seok, K. J. Yoon, D. E. Kwon, T. H. Park, Y. J. Kwon, X. Shao and C. S. Hwang, *Adv. Mater.*, 2015, 27, 3811–3816.

- 31 G. Kim, S. Son, H. Song, J. B. Jeon, J. Y. Lee, W. H. Cheong, S. Choi and K. M. Kim, *Adv. Sci.*, 2023, **10**, 2205654.

- 32 D. E. Kwon, Y. Kim, H. J. Kim, Y. J. Kwon, K. S. Woo, J. H. Yoon and C. S. Hwang, *J. Mater. Chem. C*, 2020, **8**, 1755–1761.

- 33 K. M. Kim, B. J. Choi, Y. C. Shin, S. Chio and C. S. Hwang, *Appl. Phys. Lett.*, 2007, **91**, 012907.

- 34 K. M. Kim, B. J. Choi, D. S. Jeong, C. S. Hwang and S. Han, Appl. Phys. Lett., 2006, 89, 162912.

- 35 Y. C. Yeo, T. J. King and C. M. Hu, *Appl. Phys. Lett.*, 2002, **81**, 2091–2093.

- 36 Y. Q. Liu, J. Zhang, H. H. Wu, W. Cui, R. B. Wang, K. Ding, S. T. Lee and B. Q. Sun, *Nano Energy*, 2017, 34, 257–263.

- Communication

- 37 L. Wu, H. X. Liu, J. F. Lin and S. L. Wang, IEEE Trans. Electron Devices, 2021, 68, 1622-1626.

- 38 K. S. Woo, Y. Wang, Y. Kim, J. Kim, W. Kim and C. S. Hwang, Adv. Electron. Mater., 2020, 6, 1901117.

- 39 T. Jeong, I. W. Yeu, K. H. Ye, S. Yoon, D. Kim, C. S. Hwang and J.-H. Chio, Nanoscale, 2024, 16, 6949-6960.

- 40 T. Park, S. S. Kim, B. J. Lee, T. W. Park, H. J. Kim and C. S. Hwang, Nanoscale, 2023, 15, 6387-6395.

- 41 K. M. Kim and R. S. Williams, IEEE. Trans. Circuits Syst. I: Regul. Pap., 2019, 66, 4348-4355.

- 42 S. Ambrogio, S. Balatti, D. C. Gilmer and D. Ielmini, IEEE Trans. Electron Devices, 2014, 61, 2378-2386.

- 43 Q. L. Tian, X. N. Zhao, Y. Lin, Z. Q. Wang, Y. Tao, H. Y. Xu and Y. C. Liu, Appl. Phys. Lett., 2022, 121, 183502.

- 44 G. Khurana, N. Kumar, M. C. Hhowalla, J. F. Scott and R. S. Katiyar, Sci. Rep., 2019, 9, 15103.

- 45 W. Banerjee, X. M. Zhang, Q. Luo, H. B. Lv, Q. Liu, S. B. Long and M. Liu, Adv. Electron. Mater., 2018, 4, 1700561.

- 46 Y. Abbas, R. B. Ambade, S. B. Ambade, T. H. Han and C. Choi, Nanoscale, 2019, 11, 13815-13823.

- 47 S. Srivastava, J. P. Thomas, X. Y. Guan and K. T. Leung, ACS Appl. Mater. Interfaces, 2021, 13, 43022-43029.

- 48 V. R. Nallagatla, J. Kim, K. Lee, S. C. Chae, C. S. Hwang and C. U. Jung, ACS Appl. Mater. Interfaces, 2020, 12, 41740-41748.