# Journal of Materials Chemistry C

Cite this: J. Mater. Chem. C, 2025, 13, 4861

Received 12th November 2024, Accepted 3rd February 2025

DOI: 10.1039/d4tc04792c

rsc.li/materials-c

### 1. Introduction

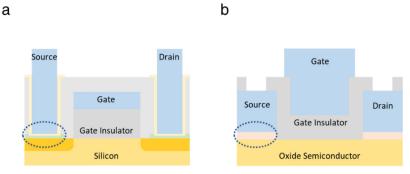

Since the Hosono group's discovery of amorphous indium gallium zinc oxide (a-IGZO) in 2004, amorphous oxide semiconductors (AOSs) have garnered significant attention as channel materials in thin-film transistors (TFTs).<sup>1</sup> In 2013, LG Display pioneered the mass production of active-matrix organic light-emitting diode (AMOLED) televisions by using an IGZObased backplane on 8th-generation glass substrates, setting a new industry standard for large-sized displays.<sup>2,3</sup> The success of IGZO electronics is largely attributed to its reasonable electron mobility, extremely low off-current, excellent large-area uniformity, compatibility with low-temperature processing, and reliable electrical stability.<sup>4-6</sup> As the semiconductor industry grapples with the physical limitations of further miniaturization, which is critical for improving performance, power efficiency, area scaling, and cost-effectiveness (often referred to as PPAC), AOSs have emerged as potential alternative channel materials. In particular,

## Advancements and hurdles in contact engineering for miniaturized sub-micrometer oxide semiconductor devices

With conventional silicon-based devices approaching their physical scaling limits, alternative channel materials, such as transition metal dichalcogenides and oxide semiconductors (OSs), have emerged as promising candidates for extending Moore's law and advancing performance, power efficiency, area scaling, and cost-effectiveness. Among these, OSs stand out as particularly promising, having already been established as the industry standard for high-end active-matrix organic light-emitting diodes due to their moderate mobility, extremely low off-current, steep subthreshold swing, excellent uniformity, and compatibility with low-temperature fabrication processes. However, to enable the deployment of OSs in more demanding applications, such as 3D dynamic random-access memory and other advanced electronic systems, further improvements are necessary, particularly in terms of enhancing on-current and hydrogen stability and reducing contact resistance ( $R_c$ ). In this work, we review strategies to optimize electrical contact properties to improve the device performance of OSs and examine the underlying mechanism of  $R_c$  from a device physics perspective.

oxide semiconductors (OSs) have attracted considerable attention as channel materials for next-generation vertical channel transistors (VCTs), 2T0C and 3D dynamic random-access memory (DRAM) due to their aforementioned unique properties.<sup>7–10</sup> Their wide bandgap  $(E_{\rm G})$  enables promising solutions to the scaling and leakage challenges encountered in DRAM devices.<sup>11,12</sup> From a processing perspective, the atomic layer deposition (ALD) of the OS channel layer offers excellent conformality on complex nanoscale structures, presenting a compelling alternative to the conventional sputtering deposition method commonly used in display devices. This growing interest in AOSs is evidenced by the rising number of research papers on oxide semiconductor (OS) devices that are presented at major semiconductor conferences, such as the IEEE International Electron Device Meeting (IEDM) and the Symposium on VLSI Technology and Circuits, increasing from just 2 papers in 2016 to 40 in 2023.8,13,14

Scaling AOS-based devices poses several challenges, including short channel effects (SCEs) such as drain-induced barrier lowering, hot carrier effects, high-temperature process compatibility, threshold voltage ( $V_{TH}$ ) control, hydrogen-related reliability, and contract resistance ( $R_C$ ). Notably, as the channel length decreases, the influence of  $R_C$  and channel shortening at the metal-semiconductor (M–S) interface becomes increasingly pronounced, emerging as a critical barrier to device performance.  $R_C$  has long been a critical issue in the semiconductor industry because it limits further miniaturization and degrades the performance of nanoscale devices.<sup>15–18</sup> While substantial efforts have successfully reduced  $R_C$  in Si-based devices,

View Article Online

ROYAL SOCIETY

OF CHEMISTR

View Journal | View Issue

<sup>&</sup>lt;sup>a</sup> Department of Display Science and Engineering, Hanyang University, Seoul 04763, Republic of Korea. E-mail: jkjeong1@hanyang.ac.kr

<sup>&</sup>lt;sup>b</sup> Department of Electronic Engineering, Hanyang University, Seoul 04763 Republic of Korea

<sup>&</sup>lt;sup>c</sup> Department of Nanoscale Semiconductor Engineering, Hanyang University, Seoul 04763, Republic of Korea

<sup>&</sup>lt;sup>d</sup> Semiconductor Research and Development Center, Samsung Electronics, Hwaseong, Republic of Korea

<sup>†</sup> J. H. Jeong and J. E. Oh contributed to this work equally.

#### Review

AOSs, which have predominantly been utilized in the display industry, have faced less pressure to optimize electrical contact properties due to their comparatively less stringent scaling requirement, attributed to the larger contact hole sizes ( $\geq 10^{-8}$  cm<sup>2</sup>) relative to those (approximately  $10^{-12}$  cm<sup>2</sup>) in the semiconductor industry.<sup>19</sup> Consequently, the  $R_{\rm C}$  in AOS TFTs remains approximately four orders of magnitude higher than in Si-based metal oxide semiconductor field-effect transistors. However, as advancements in highresolution technology and DRAM drive the need for further scaling and enhancing of device performance, reducing  $R_{\rm C}$  in AOSs is becoming an increasingly critical factor.<sup>20,21</sup> While this review primarily focuses on reducing  $R_{\rm C}$  by optimizing ohmic contacts, the development of Schottky barrier (SB) TFTs, which operate in the deep subthreshold regime, has also been studied for enabling lowpower operation in wearable devices and sensor circuitries.<sup>22,23</sup>

Although numerous comprehensive review articles on AOSs exist, the majority have predominantly focused on optimizing high performance and stability.<sup>2,5,11,24–27</sup> In this work, we shift the emphasis towards understanding the origin of  $R_{\rm C}$  at the M–S interface and provide a classification of the latest methods for reducing  $R_{\rm C}$  in AOS TFTs. Additionally, we compare the material properties and the enhancement strategies of AOSs with those of Si-based devices. In Section 2, we discuss the charge carrier injection mechanisms at the M–S junction and the methodologies employed to extract electrical contact properties. Section 3 covers recent advancements in reducing  $R_{\rm C}$  in OS TFTs, broadly categorizing the approaches into band alignment and carrier density strategies, with a detailed view of leading studies on carrier density optimization. Finally, we propose potential strategies to further decrease  $R_{\rm C}$  in future AOS-based devices.

### 2. Metal-semiconductor junction

#### 2.1 Junction classification: formation of a Schottky barrier

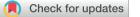

M–S junctions typically exhibit an energy mismatch at the interface, leading to the formation of a Schottky barrier as a result of the difference in Fermi energy ( $E_{\rm F}$ ) between the metal and the semiconductor. In an ideal case in which surface interactions are negligible, the SB height ( $\Phi_{\rm B}$ ) is determined solely by the metal work function ( $\Phi_{\rm M}$ ) and the electron affinity of the semiconductor ( $\chi$ ), with  $\Phi_{\rm B}$  expressed as  $\Phi_{\rm B} = \Phi_{\rm M} - \chi$ .<sup>28,29</sup> Based on the relationship between the metal and semiconductor work functions, M–S junctions can be classified as either ohmic contacts (when  $\Phi_{\rm M} < \Phi_{\rm S}$ ) or Schottky contacts (when  $\Phi_{\rm M} > \Phi_{\rm S}$ ).

In practice, however, modifying  $\Phi_{\rm B}$  by using different metals is challenging. Experimental studies indicate that for most common semiconductors, the  $\Phi_{\rm B}$  at the M–S interface is relatively independent of the metal's work function, a phenomenon known as Fermi-level pinning (FLP). FLP at the charge neutral level (CNL) arises from several factors, including native point defects, interface trap states ( $D_{\rm it}$ ), and metal-induced gap states (MIGS).<sup>30–33</sup> Among these, MIGS are the most significant contributor to FLP, originating from the penetration of the metal's electron wave function into the semiconductor and forming tailing states within the semiconductor's  $E_{\rm G}$ .<sup>34,35</sup> Furthermore, the extent of FLP is influenced by the  $E_{\rm G}$ , with semiconductors that have a narrower  $E_{\rm G}$  exhibiting stronger FLP due to the slower decay of the penetrated wave function.<sup>36</sup>

This behavior is quantitatively described by the pinning factor (S), defined as  $S = d\Phi_B/d\Phi_M$ . When S = 1, known as the Schottky-Mott limit, the  $\Phi_{\rm B}$  is free of FLP and depends solely on the  $\Phi_{M}$ , reflecting an ideal M–S junction. In contrast, when S = 0,  $\Phi_{\rm B}$  becomes independent of  $\Phi_{\rm M}$ , with the  $E_{\rm F}$  fully pinned at a fixed energy level, which is referred to as the CNL and is defined as the Bardeen limit (Fig. 1(c)). In reality, most semiconductors exhibit behavior between these two extremes, with smaller S values indicating stronger pinning. Studies have shown a correlation between S and electronegativity difference  $(\Delta X)$ , where ionic materials tend to exhibit S values near 1, while covalent materials are positioned closer to S = 0 (Fig. 1(d)).<sup>37</sup> This discrepancy arises because ionic materials have minimal surface energy changes, while covalent materials experience significant surface energy perturbation due to dangling bonds, resulting in stronger FLP and lower S values. It is noted that Schottky contacts can be employed selectively based on the specific device applications. Promising Schottky contact between oxide channel (e.g., ZnO, IGZO) and metals (e.g., Ag, Pt, Pd) can be achieved through low-temperature processing, making them suitable for use as a gate stack in MESFET.<sup>21,22,38-40</sup> However, their application in DRAM access transistors, which require a high thermal budget, remains challenging due to significant leakage currents and adverse interface deterioration.

#### 2.2 Charge injection mechanism

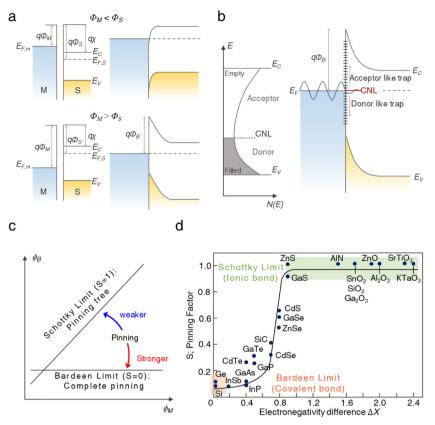

The effective  $\Phi_{\rm B}$  at the M–S interface is a key determinant of current flow, with charge injection influenced by factors such as doping density  $(N_e)$ , temperature, and applied voltage. The  $N_{\rm e}$  directly affects the barrier width ( $x_{\rm d}$ ), which is described by the equation  $x_d = (2k_s\varepsilon_0\Phi_M/qN_e)^{-1/2}$ .  $N_e$  plays a crucial role in determining the current transport mechanism, which can be classified into thermionic emission (TE), thermionic-field emission (TFE), and field emission (FE) (Fig. 2(a)).<sup>41</sup> In lightly doped semiconductors, current predominantly flows via TE, where carriers are thermally excited and overcome the SB due to the wide  $x_{\rm d}$ . As  $x_{\rm d}$  increases, the barrier width narrows, and tunneling begins to play a role in the conduction mechanism. In a semiconductor with an intermediate  $N_{\rm e}$ , thermally excited carriers partially tunnel through the SB, a process known as TFE. When  $x_{\rm d}$  becomes sufficiently narrow due to high doping levels, carrier injection occurs through direct tunneling, forming an ohmic contact, a process referred to as FE, though this is rarely observed. The distinction between these charge injection mechanisms is governed by the comparison of thermal energy of  $k_{\rm B}T$  to the characteristic energy  $E_{00}$ , defined by the equation  $E_{00} = (N_e/\epsilon_s m^*)^{1/2} qh/4\pi$ . According to conventional demarcation points, current transport is dominated by TE when  $E_{00} \le 0.5kT$ , by TFE when  $0.5kT < E_{00} < 5kT$ , and by FE when  $5kT \leq E_{00}$  (Fig. 2(b)).

#### 2.3 Extraction method: the gated transmission line method

The  $R_{\rm C}$  in AOS TFTs is closely associated with the voltage required for charge transport across M–S interfaces at both

Fig. 1 (a) Energy band diagram illustrating Schottky and Ohmic contact in an ideal case. (b) Energy band diagram showing the effect of Fermi-level pinning (FLP) due to metal-induced gap states (MIGS, right), with a schematic of the charge neutral level as the branch point of the MIGS (left). (c) Schematic  $\Phi_B - \Phi_M$  plot indicating the degree of FLP at the metal-semiconductor interface. (d) Collected data showing the dependence of the pinning factor (S) on the electronegativity difference.

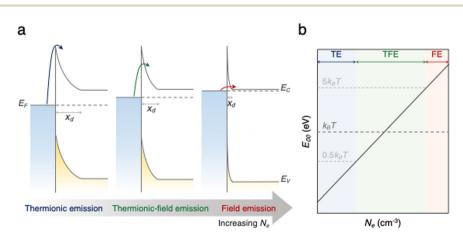

the source-channel and channel-drain junctions. The applied voltage  $(V_{app})$  is distributed between the contact and channel regions, as expressed by the equation  $V_{app} = 2\Delta V_{SD} + \Delta V_{Ch} = I_D(2R_C + R_{ch})$  (Fig. 3(a)). Here,  $\Delta V_{SD}$  represents the voltage drop at the source and drain (S/D) and the channel interface, which primarily comes from the  $R_C$  that results from the energy barrier impeding carrier injection at the M–S junction. Given

the significant impact  $R_{\rm C}$  has on the electrical properties of AOS-based devices, accurate measurement of  $R_{\rm C}$  is essential for evaluating contact enhancement strategies (Section 3).

Both  $R_{ch}$  and  $R_{C}$  exhibit gate bias ( $V_{G}$ ) dependency due to the shift in the Fermi level within the semiconductor and the gate-field-induced reduction of the barrier height and width at the M–S interface (Fig. 3(b)). To accurately characterize  $R_{C}$ , the gated

**Fig. 2** (a) Schematic representation of the carrier transport at the metal–semiconductor interface as doping concentration increases. (b)  $E_{00}$  as a function of doping density, illustrating the three charge injection modes: thermionic emission (TE) when  $E_{00} \le 0.5kT$ , thermionic-field emission (TFE) when  $0.5kT < E_{00} < 5kT$ , and field emission (FE) when  $5kT \le E_{00}$ .

**Fig. 3** (a) Schematic representation of a device illustrating the resistor network  $R_T = R_{ch} + 2R_{c}$ , along with a voltage profile indicating the voltage drop across the drain-channel-source region. (b) Energy band diagram showing the barrier decreasing as  $V_G$  increases, with a plot demonstrating the  $V_G$  dependence of  $R_C$  for high  $V_G$  and low  $\Phi_B$ . (c), (d) Schematic graphs for a transmission line method (TLM) of  $R_T$  as a function of L.

transmission line method (g-TLM), also known as the gated transfer length model, is commonly employed. This method analyzes current-voltage (*I–V*) characteristics at different gate voltages ( $V_{\rm G} \gg V_{\rm T}$ ) in the linear region ( $V_{\rm D} \rightarrow 0$ ) using a set of devices with varying channel lengths (*L*), resulting in a family of TLM curves. The *I–V* characteristics in the linear region are described by the equation:<sup>28</sup>

$$I_{\rm D} = \mu_{\rm FE} C_{\rm OX} \frac{W}{L_{\rm eff}} \left( V_{\rm G} - V_{\rm T} - \frac{1}{2} V_{\rm D} \right) V_{\rm D}$$

(1)

where  $L_{\text{eff}}$  is the effective channel length, defined as  $L_{\text{eff}} = L - 2\Delta L$ , with *L* being the mask channel length and  $\Delta L$  accounting for process bias and lateral dopant diffusion. Thus,  $R_{\text{ch}}$  can be expressed as:<sup>42</sup>

$$R_{\rm ch} = \frac{V_{\rm D}}{I_{\rm D}} = \frac{L - 2\Delta L}{W\mu_{\rm FE}C_{\rm OX}\left(V_{\rm G} - V_{\rm T} - \frac{1}{2}V_{\rm D}\right)}$$

(2)

Taking  $R_{\rm C}$  into account, the total device resistance  $(R_{\rm T})$  is given by:

$$R_{\rm T} = R_{\rm ch} + 2R_{\rm c} = \frac{L - 2\Delta L}{W\mu_{\rm FE}C_{\rm OX}\left(V_{\rm G} - V_{\rm T} - \frac{1}{2}V_{\rm D}\right)} + 2R_{\rm c} \quad (3)$$

Because  $R_c$  remains constant while  $R_{ch}$  varies linearly with L, plotting  $R_T$  against L at a fixed  $V_G$  yields a straight line. If no intersection occurs (Fig. 3(c)),  $\Delta L = 0$  and  $R_C$  become dependent on  $V_{GS}$  due to its correlation with carrier density. Here  $R_C$  and  $R_{\rm sh}$ , where  $R_{\rm ch} = R_{\rm sh}L/W$ , can be extracted as a function of  $V_{\rm G}$ . Alternatively, if an intersection occurs,  $\Delta L \neq 0$ , the convergence point indicates  $2\Delta L$  and  $2R_{\rm C}$ , in accordance with eqn (3). The value of  $\Delta L$  generally arises from the diffusion of oxygen vacancies (V<sub>O</sub>), which is more pronounced in the OSs with a higher concentration of V<sub>O</sub>.<sup>43</sup> This diffusion leads to a reduction in SB width, thereby facilitating carrier injection and rendering electron injection independent of  $V_{\rm G}$ .

### Improvement method

When silicon is directly interfaced with metals, a Schottky junction forms due to Fermi level pinning, which arises from MIGS and the thermal instability caused by metal–silicon interdiffusion.<sup>44</sup> To overcome this issue, a silicide coupling layer is often introduced at the interface, creating an ohmic contact that reduces  $R_{\rm C}$  while enhancing both the thermal and structural stability of the junction (Fig. 4(a)). Extensive research on improving the electrical contact properties of Si-based devices has focused on the use of different silicides, such as TiSi<sub>2</sub>, NiSi, and CoSi<sub>2</sub>, to optimize these properties.<sup>45-49</sup>

In indium-based OSs, such as a-IGZO, IZTO, and IGO, recent research efforts have focused on reducing the effective  $\Phi_{\rm B}$  at the metal–OS interfaces. The indium-based channels generally have relatively high work functions, typically exceeding 4 eV.<sup>50-52</sup>

Fig. 4 Schematic illustrations of (a) silicon and (b) OS transistors. A number of different silicides are used to decrease the contact resistance in silicon transistors. In OS transistors, several methods are used, such as formation of a conduction region or insertion of an interlayer between the OS and the source or drain.

Despite efforts to pair these semiconductors with metals with similarly high  $\Phi_M$ , achieving a low  $\Phi_B$  remains a significant challenge. To overcome this, two primary approaches have been explored: (1) the formation of an n<sup>+</sup>-doped conduction region at the M–S interface, and (2) the insertion of interlayers (ILs) to modify the interface (Fig. 4(b)). The anticipated advantages and limitations of these methods are outlined in Table 1, with their corresponding electrical properties detailed in Table 2. A comprehensive discussion of both strategies is provided in the following section.

#### 3.1. Conductive region formation

**3.1.1. Metal-induced methods.** The use of metals with a high reducing power as S/D electrodes has been extensively studied as a means to create an  $n^+$ -doped region at the M-S

interface. When such a metal (*e.g.*, Al, Ti, W) is inserted between the indium-based channel and the S/D electrodes, their strong reductive nature allows them to extract oxygen from the channel, owing to the relatively weak In–O bonds in the OS. This process generates  $V_O$  and free carriers, forming an  $n^+$  conduction layer that reduces both the  $\Phi_B$  and  $R_C$ .

*Al-induced method.* In a study by Yang *et al.*, self-aligned topgate a-IGZO TFTs were fabricated, focusing on the Al-induced doping effect to create conductive S/D regions.<sup>65</sup> Postdeposition annealing (PDA) at 200 °C after Al deposition significantly increased V<sub>O</sub> at the Al/a-IGZO interface. X-ray photoelectron spectroscopy (XPS) of the O1s spectra revealed an increase in V<sub>O</sub> from 27% to 58% after the 200 °C PDA. Additionally, a shift in the In 3d XPS peaks indicated the

|                             | Approach             | Pros.                                   | Cons.                                                    |

|-----------------------------|----------------------|-----------------------------------------|----------------------------------------------------------|

| Conductive region formation | Metal-induced        | No additional processing required       | Formation of unwanted MO <sub>x</sub> interfacial layers |

|                             | Doping               | Broadly investigated                    | Deterioration of the OS surface                          |

|                             | Doping               | broadly investigated                    | Temporal instability<br>Limited process margin           |

| Interlayer insertion        | OS engineering       | No additional processing required       | Alteration of overall electrical properties              |

|                             | n <sup>+</sup> layer | Without deterioration of the OS surface | Requires additional processing steps                     |

|                             | DB layer             | Prevents intermixing at the interface   | Limitation in further improvement                        |

| Table 2 | Summary | v of advancements i | in improvina electric | al contact properties | in OS TETs re | enorted to date |

|---------|---------|---------------------|-----------------------|-----------------------|---------------|-----------------|

|         | Jummun  |                     |                       | at contact properties |               |                 |

| Approach             | OS        | Deposition<br>method | <i>W/L</i> (µm) | $R_{\rm c}W(\Omega~{\rm cm})$ | $ ho_{ m C} \left( \Omega \ { m cm}^2  ight)$ | $({ m cm}^{\mu_{ m FE}}~{ m V}^{-1}~{ m s}^{-1})$ | Ref. |

|----------------------|-----------|----------------------|-----------------|-------------------------------|-----------------------------------------------|---------------------------------------------------|------|

| Metal-induced        | IGZO      | SPT                  | 16/8            | _                             | $5.2	imes10^{-4}$                             | 16.1                                              | 53   |

|                      | IGZO      | SPT                  | 2.4/0.8         | 2.7                           | _                                             | 8.5                                               | 54   |

| Doping               | IGZO      | SPT                  | 3/5             | 10.2                          | _                                             | 17.2                                              | 55   |

| 1 0                  | IGZO      | SPT                  | _               | _                             | $1.3	imes10^{-6}$                             | _                                                 | 56   |

|                      | ZnO       | ALD                  | 15/2            | 0.3                           | _                                             | 39.2                                              | 57   |

|                      | IGZTO     | SPT                  | 10/10           | 11.3                          | _                                             | 27.2                                              | 58   |

| OS engineering       | $In_2O_3$ | ALD                  | /0.04           | 0.002                         | $1.3	imes10^{-9}$                             | _                                                 | 59   |

| 0 0                  | IGZO      | ALD                  | 24/24           | 1.8                           | _                                             | 36.9                                              | 60   |

| n <sup>+</sup> layer | IGZO      | SPT                  | 300/500         | 510.0                         | _                                             | 12.0                                              | 61   |

|                      | IGZO      | ALD                  | 60/30           | 0.1                           | $4.2	imes10^{-7}$                             | 45.3                                              | 62   |

| DB layer             | IGZO      | SPT                  | 625/95          | 18.0                          | _                                             | 11.5                                              | 63   |

|                      | IGZO      | SPT                  | 1000/150        | 104.5                         | —                                             | 14.8                                              | 64   |

*W*/*L*: width and length of the channel;  $\rho_{\rm C}$ : specific contact resistivity.

#### Review

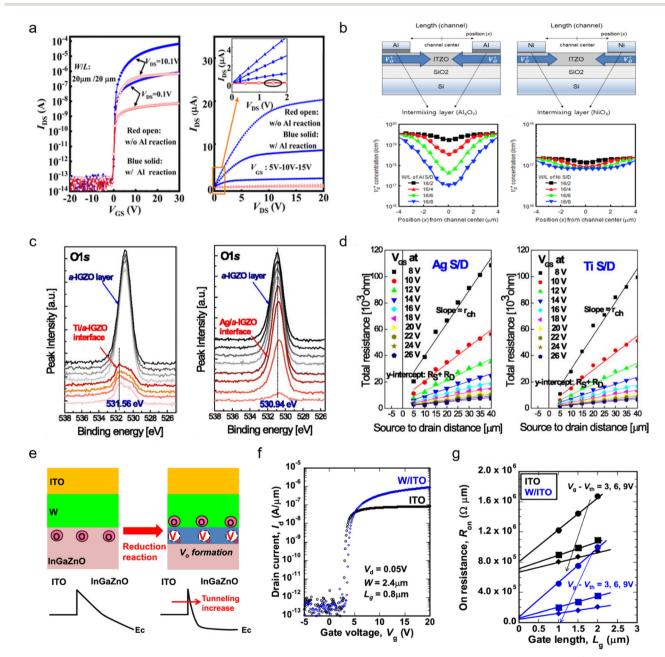

reduction of In according to the reaction:  $2\text{Al} + \text{In}_2\text{O}_3 \rightarrow \text{Al}_2\text{O}_3 + 2\text{In}$  (Gibbs free energy ( $\Delta G$ ) = -752.6 kJ mol<sup>-1</sup>). The resulting *I–V* characteristics of the Al-treated TFTs showed enhanced drain current in the on-state region, without current crowding at low  $V_{\rm D}$ , indicating good ohmic contact with a low  $R_{\rm C}W$  of 10  $\Omega$  cm, while the untreated TFTs exhibited significantly suppressed drain current (Fig. 5(a)).

However, the strong reducing power of Al can lead to excessive conductivity in the channel region, potentially degrading the transfer characteristics.<sup>66</sup> Park *et al.* suggested

that Ni electrodes would be more suitable S/D electrodes for high-density applications, where precise contact properties are crucial.<sup>53</sup> Thermally deposited Ni and Al electrodes were compared in terms of contact performance (Fig. 5(b) images shown top). Technology computer-aid design simulations showed that the Ni electrodes exhibited superior electrical properties compared to the Al electrodes, which was attributed to two factors: (1) a reduced generation and diffusion of V<sup>+</sup><sub>O</sub>, which acts as a shallow donor, and (2) a lower metal intermixing at the M–S junctions in Ni-based devices (Fig. 5(b) images shown below).

**Fig. 5** (a) The *I*–*V* characteristics with and without an AI reaction. (b) Schematic illustration comparing the diffusion extent of  $V_D^+$  when using AI and Ni electrodes (top images), along with a simulation of  $V_D^+$  concentration in the ITZO layer (bottom images). (c) O1s XPS analysis from Ti/a-IGZO and Ag/ a-IGZO interfaces from the TFT devices. (d)  $R_T$  plotted with respect to a-IGZO TFT channel length for different  $V_G$  with Ag and Ti electrodes. (e) Schematic illustration of the interfacial reaction between W and IGZO. (f)  $I_D - V_G$  characteristics of IGZO TFTs using ITO and W/ITO. (g) On resistance of IGZO TFTs using ITO and W/ITO.

Ti-induced method. Ti, known for its strong reducing power, can generate V<sub>O</sub> and form TiO<sub>2</sub> at the interface with indiumbased channels.<sup>67</sup> In a study by Choi et al., using Ti as S/D electrodes in a-IGZO TFTs significantly lowered the resistance compared to Ag S/D electrodes.<sup>68</sup> Analysis with XPS revealed the formation of a  $TiO_r$  layer and  $V_O$  at the Ti/a-IGZO interface, facilitated by the lower formation enthalpy of TiO<sub>x</sub> compared to that of  $In_2O_3$ ,  $Ga_2O_3$ , and ZnO (Fig. 5(c)). In contrast, no  $V_0$ generation was observed at the Ag/a-IGZO interface, resulting in higher  $R_{\rm C}$ . Consequently, the specific contact resistivity ( $\rho_{\rm C}$ ) of the Ti electrode was approximately one-third that of the Ag electrodes (Fig. 5(d)). However, the use of Ti electrodes can lead to  $V_{\Omega}^{+}$  formation and metal diffusion after thermal treatment, potentially reducing the effective channel length. This limits Ti's suitability for applications requiring aggressive scaling. Thus, Ti is often used in its metal-nitride form or combined with other materials.<sup>69</sup>

*W-induced method.* To mitigate the effective channel length shortening caused by  $V_O$  and metal diffusion during high temperature annealing, Kataoka *et al.* explored the use of indium tin oxide (ITO), which exhibits lower reactivity with IGZO.<sup>54</sup> However, the use of ITO alone resulted in a lower oncurrent compared to Ti electrodes due to a higher  $R_C$ . To address this, a 2 nm thick W layer was introduced to form a W/ITO electrode. XPS depth profile analysis revealed W–O bonds at the W/IGZO interface, indicating the formation of WO<sub>3</sub>, which was absent in the W/ITO interface. Additionally, Ga 2p spectra indicated a reduction reaction between W and IGZO, leading to V<sub>O</sub> formation and thinning of the depletion layer, thereby increasing the tunneling current (Fig. 5(e) and (f)). The  $R_{\rm C}W$  values of the ITO and W/ITO were measured to be 1.8 × 10<sup>5</sup> and 2.7 × 10<sup>4</sup>  $\Omega$  µm, respectively, with the W/ITO electrode exhibiting the lowest  $R_{\rm C}$  (Fig. 5(g)). Other studies have also investigated the use of metals with strong reducing power to form an n<sup>+</sup> region at the OS interface while minimizing channel shortening.<sup>70,71</sup>

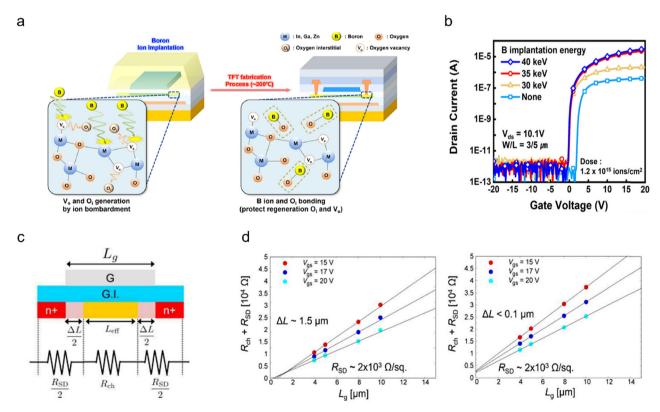

**3.1.2. Doping.** Another effective strategy for enhancing the contact properties of OS TFTs involves inducing an  $n^+$  region through doping techniques applied between the channel and S/D. This can be achieved with ion implantation or plasma treatment.

Ion implantation. Several studies have explored the formation of n<sup>+</sup> regions using B ion implantation.<sup>72,73</sup> Kang *et al.* investigated the effect of varying implantation energy during B<sup>+</sup> ion implantation on the  $R_{\rm C}$  of self-aligned coplanar a-IGZO TFTs (Fig. 6(a)).<sup>55</sup> B acts as an n-type dopant in metal oxide TFTs and is also well known for its stability at high temperature, due to the strong B–O bond. Ion implantation was performed at 30, 35, and 40 keV to compare the effects of implantation energy on device characteristics (Fig. 6(b)). With increasing implantation energy, device mobility improved and the  $R_{\rm c}W$  decreased. However, the lateral spread ( $\Delta L$ ) of the

**Fig. 6** (a) Schematic illustration of the reaction of B ions implanted in the IGZO surface. (b) The I-V characteristics at different B implantation energies. (c) Illustration of S/D series resistance  $R_{ch} + R_{SD}$  at the gate edges in TFTs. (d) Measurements of the S/D series resistances in Ne<sup>+</sup> (left) or B<sup>+</sup> (right) implanted TFTs as a function of gate length ( $L_g$ ) for  $V_G$  of 15, 17, and 20 V.

implanted ions increased, likely due to enhanced B ion diffusion at higher energies. The  $\Delta G$  of B<sub>2</sub>O<sub>3</sub> (-1,192.9 kJ mol<sup>-1</sup>) was significantly lower than that of In<sub>2</sub>O<sub>3</sub> (-830.7 kJ mol<sup>-1</sup>), Ga<sub>2</sub>O<sub>3</sub> (-998.3 kJ mol<sup>-1</sup>), and ZnO (-348.1 kJ mol<sup>-1</sup>), which facilitated the formation of stable B-O bonds. This stability, in conjunction with oxygen interstitials, led to the creation of V<sub>O</sub> sites during ion bombardment, ultimately increasing the carrier concentration ( $n_e$ ).

Moreover, Ui *et al.* compared the effects of Ne<sup>+</sup> and B<sup>+</sup> ion implantation in a-IGZO TFTs.<sup>74</sup> Although Ne<sup>+</sup> ions are larger, they exhibited greater diffusion within a-IGZO during annealing, resulting in a smaller  $\Delta L$  for B<sup>+</sup> implantation (Fig. 6(c) and (d)). This behavior was attributed to the stronger B–O bonding, which restricted diffusion. These findings underscore the importance of considering ion size, bonding energy, and implantation energy when optimizing ion implantation for contact region doping. Other ions, such as F and N, have also been investigated for similar doping applications.<sup>75–77</sup>

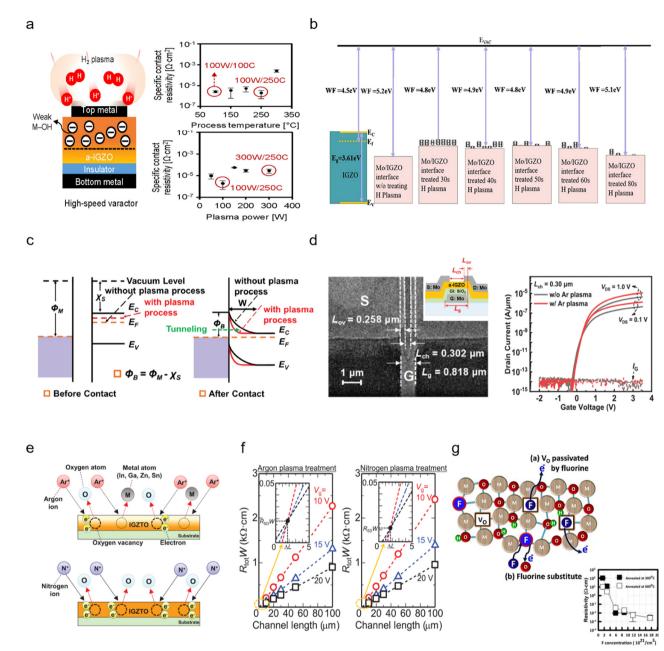

Plasma treatment. Plasma treatment, particularly using H and Ar plasma, has been extensively studied as an effective method for lowering the  $R_{\rm C}$  in OS TFTs.<sup>78–84</sup> In an investigation by Park et al., H plasma treatment with a variety of conditions was analyzed using TLM extraction to assess its impact on  $R_{\rm C}$ (Fig. 7(a)).<sup>56</sup> The findings indicated that H treatment reduces the potential barrier width by increasing  $n_{\rm e}$ , although weak M-OH bonds are partially diffused during the process. It was observed that  $R_{\rm C}$  varied with plasma power and temperature, as shown in Fig. 8(b). The study emphasized that optimizing plasma power and process temperature is critical. Higher RF power introduces excessive H into a-IGZO, forming unstable bonds that lead to device instability. Proper thermal processing can mitigate this instability. Ahmad et al. investigated the relationship between  $\rho_{\rm C}$ , hydrogen doping, and diffusion at the channel-S/D interface, noting changes in work function with increasing hydrogen plasma treatment time (Fig. 7(b)).<sup>85</sup> However, the high diffusivity and reactivity of H imposed limitations on process temperature and conditions.<sup>86</sup> Consequently, alternative approaches focused on inert gases, such as Ar and Ne, for plasma treatments.

In the work by Lu *et al.*, Ar plasma treatment was shown to affect contact properties, with prolonged treatment time promoting V<sub>O</sub> formation, thereby reducing the barrier width, enhancing tunneling, and subsequently decreasing  $R_{\rm C}$ (Fig. 7(c)).<sup>57</sup> This impact was significant in short-channel devices. For example, Zhang *et al.* demonstrated effective  $R_{\rm C}$ reduction in a 302 nm self-aligned bottom-gate a-IGZO TFT, and attributed the improvement to increased V<sub>O</sub> and carrier density (Fig. 7(d)).<sup>87</sup> The improved *I–V* transfer characteristics showed enhanced on-current and notable reliability, indicating that Ar plasma treatment is a promising technique for nanoscale AOS technologies, including micro-displays, flexible integrated circuits, and advanced optoelectronic applications.

Due to the relatively large mass of Ar ions, which can etch OS films, treatment with a nitrogen (N) plasma has also been investigated as a lower impact alternative.<sup>58</sup> The N plasma

treatment has resulted in reduced  $R_{\rm C}W$  and  $\Delta L$  compared to an Ar plasma, which could be attributed to N's smaller ion mass and reduced collateral effects (Fig. 7(e) and (f)). Additionally, F plasma treatment has been explored as a technique to reduce  $R_{\rm C}$ .<sup>88,89</sup> F ions, due to their similar ion radius to O, effectively passivate V<sub>O</sub> sites (Fig. 7(g)). The robust metal–F bonds exhibit higher bond energy than metal–O bonds, maintaining enhanced stability even after annealing at 600 °C. Furthermore, the influence of a mixture of gases, such as CF<sub>4</sub> + O<sub>2</sub> or Ar + O<sub>2</sub>, on  $R_{\rm C}$  has also been investigated, providing additional feasibility for the use of plasma treatments to optimize device performance.<sup>90–92</sup>

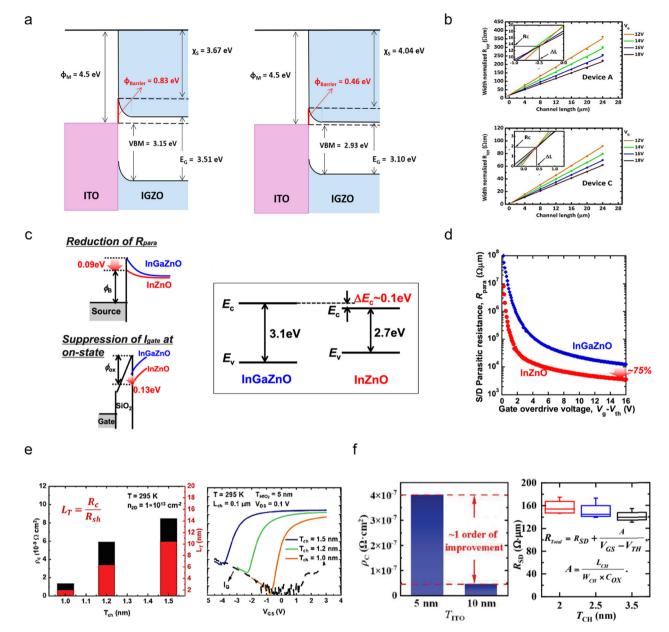

**3.1.3.** Oxide semiconductor engineering. The electrical characteristics of AOS, including carrier density and  $E_{\rm G}$ , which directly influences electrical contact properties, are notably dependent on the relative composition ratio of metal cations and oxygen. Several studies have examined the impact of varying cation composition ratios in OS TFTs to optimize performance and reduce  $R_{\rm C}$ .<sup>93,94</sup> Lee *et al.* have demonstrated a strong correlation between In content and contact resistant, showing that increased In ratios result in a reduced  $E_{\rm G}$ , higher electron affinity, and elevated work function. These factors contribute to a >40% reduction in the barrier height between the channel and S/D electrodes.<sup>95</sup> Consequently,  $R_{\rm C}W$  significantly decreases from 13.5 to 1.8  $\Omega$  cm (Fig. 8(a) and (b)).

In a complementary study, Saito *et al.* found that IZO exhibited superior mobility and lower  $R_{\rm C}$  than IGZO TFTs.<sup>59</sup> A measurement of  $\Phi_{\rm B}$  based on a TE model indicated an  $\Phi_{\rm B}$  of 0.46 eV for IGZO and 0.37 eV for IZO, highlighting a lower barrier in IZO. Moreover, Fowler–Nordheim tunneling current models revealed a 0.13 eV larger band offset at the IZO/SiO<sub>2</sub> interface compared to IGZO, consistent with the  $\Phi_{\rm B}$  difference (Fig. 8(c)). These findings underscored the critical role of metal composition in modulating  $\Phi_{\rm B}$  and  $R_{\rm C}$ , with IZO TFTs showing approximately 75% lower S/D resistance compared to IGZO TFTs (Fig. 8(d)).

Channel thickness also influences carrier density, which in turn affects  $R_{\rm C}$ . Niu *et al.* have observed that increasing carrier density in In<sub>2</sub>O<sub>3</sub> results in  $\rho_{\rm C}$  (Fig. 8(e)), and have proposed an optimal channel thickness for achieving target carrier density essential for next-generation, high-performance ultra-scaled back end of the line electronics.<sup>60</sup> However, while higher carrier density can decrease  $R_{\rm C}$ , it may shift the material's behavior toward metallicity, necessitating careful optimization to balance a low  $R_{\rm C}$  with semiconducting properties (Fig. 8(f)).<sup>96</sup>

As channel dimensions scale downward, thermal electron injection over the SB can lead to a significant increase in  $R_{\rm C}$ . Recent research has therefore focused on optimizing channel thickness to modulate carrier density and exploring structural modifications to improve contact properties, with the ultimate goal of developing TFTs that combine high on-current and stable  $V_{\rm T}$ .<sup>97,98</sup>

#### 3.2. Interlayer insertion

**3.2.1.**  $\mathbf{n}^+$  layer. Doping techniques have been widely studied to improve contact properties (refer to Section 3.1). However, the OS interface near the S/D electrodes remains

**Fig. 7** (a) Schematic illustration of hydrogen plasma treatment on TFTs (left) and  $\rho_C$  as a function of process temperature and plasma power. (b) The schematic energy diagram of the work function at the Mo/IGZO interface. (c) The energy band diagrams of a Ti electrode and an OS layer, before (left) and after (right) contact. The effective potential barrier width is reduced with an Ar plasma process. (d) Top-down and cross-section SEM images of TFT (left) and the transfer characteristics of TFTs with and without Ar plasma treatment. (e) The illustration of the different mechanisms of Ar<sup>+</sup> and N<sup>+</sup> plasma treatments. (f) Width-normalized  $R_T$  as a function *L* for TFTs fabricated with Ar (left) and N (right) plasma treatment. (g) Model of F doping showing V<sub>O</sub> passivated by F or F substitution for O. When F concentration increases, resistivity decreases.

vulnerable to degradation, leading to an increase in interface defects that can offset the advantages of higher carrier concentration ( $n_e$ ). To address this challenge, the insertion of an n<sup>+</sup> layer, with a higher  $n_e$  than the OS channel, has been explored as an effective approach to reduce the barrier width while minimizing interface damage.<sup>61,62,99-103</sup>

*Homogeneous layer.* The  $n_e$  in sputter-derived OS layers can be modulated by controlling the oxygen partial pressure ( $P_{O_2}$ ),

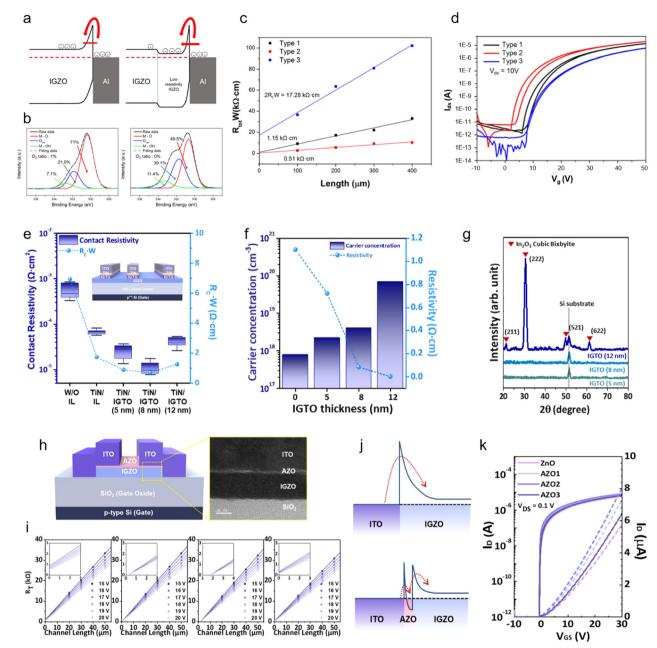

power, and cation composition during the deposition process. Kim *et al.* investigated the modulation of the contact barrier in a-IGZO TFTs by varying the  $P_{O_2}$  in a homogenous IL, as shown in Fig. 9(a).<sup>61</sup> The deposition ratio of  $O_2/(O_2 + Ar)$  was adjusted to 1% (type 1), 0% (type 2), and 20% (type 3) for the sputtered a-IGZO IL, using the same target as the channel layer. The type 2 device exhibited an improved  $\mu_{FE}$  of 12.03 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a negative  $V_T$  shift of -4.1 V, and a 2.3-fold reduction in  $R_CW$  compared to the type 1 device, which had a  $\mu_{FE}$  of 9.95 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a  $V_T$  of

#### Review

**Fig. 8** (a) Schematic of the energy band diagram for contact structures of ITO and IGZO with low In concentration (left) and high In concentration (right). (b) Linear fit obtained from the TLM analysis for low In concentration (device A) and high In concentration (device B). (c) Schematic of the band diagram of IGZO and IZO. (d) Comparison of S/D  $R_{\rm C}$  between IZO FETs and IGZO FETs. (e) Channel thickness dependence of  $\rho_{\rm C}$  and current transfer length (left), and transfer characteristics for different channel thicknesses (right). (f)  $\rho_{\rm C}$  with channel thicknesses ( $T_{\rm ITO}$ ) of 5 and 10 nm (left) and  $R_{\rm SD}$  for different  $T_{\rm ITO}$  (right).

5.8 V, and an  $R_{\rm C}W$  of 575  $\Omega$  cm (Fig. 9(c) and (d)). The increase in  $P_{\rm O2}$  from 0% to 1% and 20% resulted in a significant reduction in V<sub>o</sub> from 39.1% to 21.9% and 12.6%, respectively, driven by the reaction  $1/2O_2 + V_{\rm O}^{2+} + 2e^- \rightarrow O_{\rm O}$  (Fig. 9(b)). Consequently, the higher  $n_{\rm e}$  observed in the type 2 IGZO IL can be attributed to the presence of intrinsic V<sub>O</sub> defects, which act as donors and effectively form a highly doped layer, thereby enhancing ohmic contact properties.

Heterogeneous layer. Many studies have focused on identifying the optimal conditions for IL to achieve superior electrical contact properties. Recently, Jeong *et al.* proposed a multi-stack IL structure composed of an oxygen-scavenging TiN layer and an n<sup>+</sup> IGTO layer, highlighting the thickness dependence of the IGTO layer ( $t_{\rm IGTO}$ ) on the  $R_{\rm C}$  of a-IGZO devices.<sup>103</sup> IGZO TFTs with a TiN/IGTO (3/8 nm) IL had the lowest  $R_{\rm C}W$  of 0.7  $\Omega$  cm, which was significantly lower than the control device, which had an  $R_{\rm C}W$  of 6.9  $\Omega$  cm. The observed performance degradation when  $t_{\rm IGTO} > 8$  nm, as shown in Fig. 6(e), was attributed to changes in crystallinity. Despite the high  $n_{\rm e}$  in 12 nm thick IGTO (Fig. 9(f)), crystallization-induced deterioration at the M–S interface caused an increase in  $R_{\rm C}W$  to 1.3  $\Omega$  cm.

**Fig. 9** (a) Energy band alignment of the contact region for a-IGZO TFTs without an interlayer (IL) and with a low resistivity IL. (b) O 1s XPS spectra of IGZO thin films with oxygen ratios of 0% and 1% during deposition. (c)  $R_TW$  as a function of *L* for three device types: type 1 without an IL; type 2 with an n<sup>+</sup>-IGZO IL; type 3 with an n<sup>-</sup>-IGZO IL. (d) Transfer characteristics of the three a-IGZO TFT types. (e) Contact scheme-dependent  $\rho_C$  and  $R_CW$  in a-IGZO TFTs with different ILs. (f) Hall effect measurements of the IGTO/IGZO thin-film stacks with IGTO thickness ( $t_{IGTO}$ ) values of 0, 5, 8, and 12 nm. (g) GIXRD pattern of the IGTO thin films with varying  $t_{IGTO}$ . (h) Device schematic of the proposed a-IGZO TFT structure with a cross-sectional HRTEM image. (i)  $R_T-L$  plots as a function of  $V_G$  in a-IGZO TLM devices with different ILs. (j) Schematic energy band diagrams at the contact region. (k) Transfer characteristics at  $V_D$  of 0.1 V with different ILs.

Additionally, Jeong *et al.* reported on an ALD-based ultrathin IL method (Fig. 9(h)).<sup>62</sup> The optimized doping ratio of an Al-doped ZnO IL was achieved by adjusting the number of Al<sub>2</sub>O<sub>3</sub> injection cycles during the ALD process, resulting in the lowest  $R_{\rm C}W$  of 0.13  $\Omega$  cm at an Al<sub>2</sub>O<sub>3</sub>:ZnO ratio of 2:8 (Fig. 9(i)). This substantial improvement was corroborated by a schematic energy band diagram, based on UPS and ellipsometry analysis, which indicated a reduction in  $\Phi_{\rm B}$  due to the IL's high  $n_{\rm e}$ . This

enhanced electrical contact contributed to an increase in  $\mu_{\text{FE}}$  from 38.8 to 45.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, as shown in Fig. 9(k).

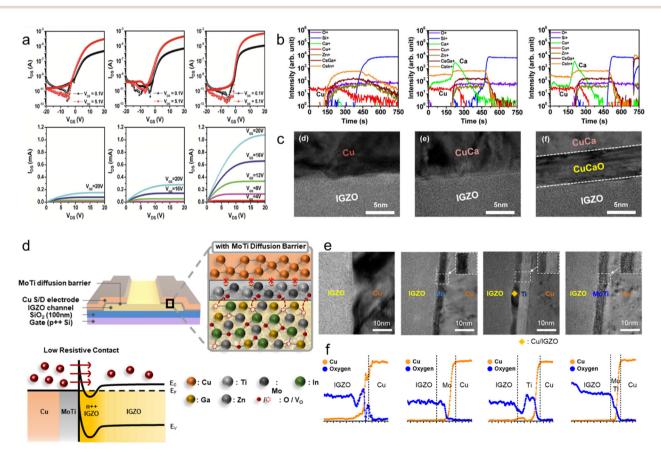

**3.2.2. Diffusion barrier layer.** Inserting a diffusion barrier (DB) layer is another effective method to enhance the contact properties of OS devices, because it prevents adverse metal atom interdiffusion into the OS channel during the thermal annealing, which can otherwise lead to instability and device performance degradation.<sup>63,64,104</sup> The choice of DB material

depends on factors such as reactivity, adhesion, anti-diffusion properties, and low  $R_{\rm C}$ . For example, Jeong et al. used a 5 nm thick Ca-doped CuO (CuCaO<sub>x</sub>) DB IL positioned between a Ca-doped Cu (CuCa) electrode and an a-IGZO channel.<sup>104</sup> This configuration exhibited significant improvements in electrical properties, with a  $\mu_{\rm FE}$  of 20.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, an SS of 0.4 V decade<sup>-1</sup>, and a  $R_{\rm C}W$  of 25.8  $\Omega$  cm, in contrast to the control device with Cu S/D electrodes, which had corresponding values of 3.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, 1.51 V decade<sup>-1</sup>, and 175  $\Omega$  cm (Fig. 10(a)). This enhancement was attributed to the effective suppression of Cu diffusion toward the channel layer by the CuCaO<sub>r</sub> IL and the formation of an extremely smooth interface (Fig. 10(b) and (c)). An in-depth study on MoTi DB was also conducted to determine why the Cu/MoTi stack exhibited superior performance compared to individual materials such as Mo or Ti alone.<sup>64</sup> The MoTi alloy leveraged the advantageous properties of both elements: Mo provided an excellent DB against Cu migration, while Ti acted as an oxygen scavenger, facilitating the formation of low-ohmic contacts (Fig. 10(d)-(f)). The device incorporating a 5 nm thick MoTi IL exhibited superior electrical characteristics, including a significantly lower R<sub>C</sub>, compared to devices without an IL or those using individual Mo and Ti ILs. The synergistic effect of Mo and Ti was crucial in achieving this improvement.

### 4. Suggestion

As the semiconductor industry progresses toward higher integration for PPAC, reducing device dimensions has become essential. This has spurred interest in short-channel and 3D structures such as VCTs, gate-all-around (GAA), and channel-all around (CAA) designs. However, research aimed at minimizing  $\Delta L$  to mitigate SCEs while suppressing performance degradation caused by  $R_{\rm C}$  remains relatively limited. To enable the application of OS in 3D architectures, further investigations into R<sub>C</sub> reduction strategies and geometrical effects on R<sub>C</sub> are imperative. Contact geometry plays a pivotal role in influencing local current density through variations in the electric field. While electric field concentration near edge contact can enhance charge transport and reduce  $R_{C_1}$  it can also cause localized temperature rises along the current paths, resulting in increased  $R_{\rm C}$ .<sup>105,106</sup> Therefore, optimizing contact geometry to manage field concentration is essential for improving device performance. In this context, studies have explored strategies to mitigate current crowding effects on R<sub>C</sub> by modulating contract area and channel edge design. For instance, in transition-metal dichalcogenides (TMDs), minimized contact areas are often employed, whereas OSs have been investigated with an emphasis on increasing contact areas.107-111 Specifically, integrating OS into DRAM architectures

**Fig. 10** (a) Transfer and output characteristics of a-IGZO TFTs with different S/D electrodes: Cu, CuCa, and CuCa/CuCaO<sub>x</sub>. (b) Elemental depth profiling results for the a-IGZO devices with different S/D electrodes. (c) Cross-sectional TEM images of the channel and electrode stacks. (d) Concept of the synergistic effect in Cu/MoTi/IGZO stacks, combining diffusion blocking against Cu migration and forming a good n<sup>+</sup> layer. (e) Cross-sectional TEM images of Cu/IGZO, Cu/Mo/IGZO, Cu/Ti/IGZO, and Cu/MoTi/IGZO stacks. (f) Elemental depth profiles from EDS analysis of Cu and O for different stacks.

with nanometer-scale contact holes ( $\sim 1 \times 10^{-12} \text{ cm}^2$ ) requires achieving a specific contact resistivity ( $\rho_{\rm C} = R_{\rm C} \cdot A_{\rm C}$ ) below  $10^{-6} \ \Omega \ {\rm cm}^2$  to avoid performance degradation and ensure reliable device operation. Meeting this target necessitates further research into scaling-friendly contact engineering approaches tailored to ultra-scaled and 3D device architectures.

## 5. Conclusion

OSs are emerging as promising candidates for next-generation channel materials, with the potential to address the scaling limitations inherent in conventional silicon-based devices. This review focuses on key strategies for reducing  $R_{\rm C}$  in OS-based TFTs, which remains a critical challenge for further miniaturization and performance enhancement. While various methods such as conductive region formation and interlayer insertion have been explored to reduce  $R_{\rm C}$  in OS TFTs, the majority of studies have focused on devices with relatively long channel length (>1  $\mu$ m). The effectiveness of these strategies for submicrometer or even sub-100-nanometer channel lengths is highly dependent on the fabrication process, structure, and thermal budget. This remains an open question and warrants further investigation. In particular, the formation of an n<sup>+</sup> conduction region and interlayer insertion have demonstrated effectiveness in lowering the effective potential barrier between metal and semiconductor and enhancing carrier injection. As OS technologies advance into more sophisticated applications, such as DRAM, reducing  $R_{\rm C}$  will be vital to meet the performance demands of future semiconductor devices. Continued innovation in contact engineering will be vital for unlocking the full potential of OSs in high-performance, scalable electronics, paving the way for their integration into future device architectures.

## Data availability

The datasets used and/or analyzed during the current study are available from the corresponding author on reasonable request.

## Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

This work was supported by the National Research Foundation (NRF) grant funded by the Korean government (NRF-2022M3H4A6A01035636, and 2022M3H4A1A04068923) and Samsung Electronics Co., Ltd (IO240814-10715-01, and IO201210-08034-01).

## References

1 K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano and H. Hosono, *Nature*, 2004, **432**, 488–492.

- 2 T. Kim, C. H. Choi, J. S. Hur, D. Ha, B. J. Kuh, Y. Kim, M. H. Cho, S. Kim and J. K. Jeong, *Adv. Mater.*, 2023, **35**, 2204663.

- 3 J. F. Wager, Inf. Disp., 2016, 32, 16-21.

- 4 T. Kamiya and H. Hosono, NPG Asia Mater., 2010, 2, 15–22.

- 5 H. Hosono, Nat. Electron, 2018, 1, 428.

- 6 B. He, G. He, L. Zhu, J. Cui, E. Fortunato and R. Martins, *Adv. Funct. Mater.*, 2024, **34**, 2310264.

- 7 J. E. Yang, Y. Jang, N. R. Han, H. J. Sung, J. K. Kim, Y. Cha, K. H. Lee, K. Jung, M. Jung, W. Lee, M. H. Cho and S. Kim, 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI, Technology and Circuits), 2024, pp. 1–2, DOI: 10.1109/VLSITechnologyandCir46783.2024.10631550.

- 8 D. Ha, W. Lee, M. H. Cho, M. Terai, S. W. Yoo, H. Kim, Y. Lee, S. Uhm, M. Ryum, C. Sung, Y. Song, K. Lee, S. W. Park, K. S. Lee, Y. S. Tak, E. Hwang, J. Chea, C. Im, S. Byeon, M. Hong, K. Sim, W. J. Jung, H. Ryu, M. J. Hong, S. Park, J. Park, Y. Choi, S. Lee, G. Woo, J. Lee, D. S. Kim, B. J. Kuhm, Y. G. Shin and J. Song, 2023 International Electron Devices Meeting (IEDM), IEEE, 2023, pp. 1–4.

- 9 A. Belmonte, H. Oh, N. Rassoul, G. L. Donadio, J. Mitard, H. Dekkers, R. Delhougne, S. Subhechha, A. Chasin, M. J. van Setten, L. Kljucar, M. Mao, H. Puliyalil, M. Pak, L. Teugels, D. Tsvetanova, K. Banerjee, L. Souriau, Z. Tokei, L. Goux and G. S. Kar, 2020 IEEE International Electron Devices Meeting (IEDM), 2020, p. 28.

- 10 S. Ryu, M. Kang and S. Kim, *Adv. Mater. Technol.*, 2024, 9, 2302209.

- 11 A. R. Choi, D. H. Lim, S. Y. Shin, H. J. Kang, D. Kim, J. Y. Kim, Y. Ahn, S. W. Ryu and I. K. Oh, *Chem. Mater.*, 2024, **36**, 2194–2219.

- 12 J. S. Hur, S. Lee, J. Moon, H. G. Jung, J. Jeon, S. H. Yoon, J. H. Park and J. K. Jeong, *Nanoscale Horiz.*, 2024, 9, 934–945.

- 13 J. C. Chiu, E. Sarkar, Y. M. Liu, Y. C. Chen, Y. C. Fan and C. W. Liu, 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI, Technology and Circuits), 2023, pp. 1–2.

- 14 Q. Li, W. Zhao, Q. Hu, C. Gu, S. Zhu, H. Liu, R. Huang and Y. Wu, 2023 International Electron Devices Meeting (IEDM), 2023, pp. 1–4.

- 15 S. Jeon, K. H. Lee, S. H. Lee, S. I. Cho, C. S. Hwang, J. B. Ko and S. H. K. Park, *J. Mater. Chem. C*, 2023, **11**, 14177–14186.

- 16 J. Raja, K. Jang, C. P. T. Nhuyen, N. Balaji, S. Chatterjee and J. Yi, *IEEE Electron Device Lett.*, 2014, 35, 756–758.

- J. Lee, S. Byeon, S. Kim, S. W. Yoo, W. Lee, S. Hong, M. H. Cho, S. J. Kim, D. Ha and D. S. Kim, *IEEE Electron Device Lett.*, 2024, 45, 1655–1668.

- 18 P. Barquinha, A. M. Vilà, G. Gonçalves, L. Pereira, R. Martins, J. R. Morante and E. Fortunato, *IEEE Trans. Electron Devices*, 2008, 55, 954–960.

- 19 H. Tang, A. Dayeh, S. T. Picraux, J. Y. Huang, and K. N. Tu, Nano Lett., 2012, 12, 3979–3985.

- 20 H. Tang, H. Dekkers, N. Rassoul, S. Sutar, S. Subhechha, V. Afanas'ev, J. Van Houdt, R. Delhougne, G. S. Kar and A. Belmonte, *IEEE Trans. Electron Devices*, 2024, 71, 567–573.

- 21 Z. Wu, J. Niu, C. Lu, Z. Bai, K. Chen, Z. Wu, W. Lu, M. Liu, F. Liao, D. Geng, N. Lu, G. Yang and L. Li, *IEEE Electron Device Lett.*, 2024, **45**, 408-411.

- 22 S. Lee and A. Nathan, Science, 2016, 354, 302-304.

- 23 A. Barua, K. D. Leedy and R. Jha, *Solid State Electron. Lett.*, 2020, 2, 59–66.

- 24 M. H. Cho, M. J. Kim, H. Seul, P. S. Yun, J. U. Bae, K. S. Park and J. K. Jeong, *J. Inf. Disp.*, 2019, 20, 73–80.

- 25 E. Fortunato, P. Barquinha and R. Martins, *Adv. Mater.*, 2012, 24, 2945–5986.

- 26 A. Olziersky, P. Barquinha, A. Vilà, C. Magaña,

E. Fortunato, J. R. Morante and R. Martins, *Mater. Chem. Phys.*, 2011, 131, 512–518.

- 27 P. Barquinha, L. Pereira, G. Gonçalves, R. Martins and E. Fortunato, *Electrochem. Solid-State Lett.*, 2008, 11, 248–251.

- 28 B. G. Streetman and S. Banerjee, *Solid State Electronic Devices*, 2000, vol. 4.

- 29 S. M. Sze, Y. Li and K. K. Ng, *Physics of semiconductor devices*, John wiley & sons, 2021.

- 30 L. J. Brillson, Y. Dong, F. Tuomisto, B. G. Svensson, A. Y. Kuznetsov, D. Doutt, H. L. Mosbacker, G. Cantwell, J. Zhang, J. J. Song, Z. Q. Fang and D. C. Look, *J. Vac. Sci. Technol.*, *B*, 2012, **30**, 050801.

- S. Yogev, R. Matsubara, M. Nakamura, U. Zschieschang,

H. Klauk and Y. Rosenwaks, *Phys. Rev. Lett.*, 2013, 110, 036803.

- 32 L. J. Brillson, J. Vac. Sci. Technol., A, 2007, 25, 943-949.

- 33 J. Robertson, J. Vac. Sci. Technol., A, 2013, 31, 050821.

- 34 J. Tersoff, Phys. Rev. Lett., 1984, 52, 465.

- 35 J. Robertson and L. Lin, *Microelectron. Eng.*, 2011, 88, 373–376.

- 36 T. Nishimura, K. Kita and A. Toriumi, *Appl. Phys. Lett.*, 2007, **91**, 123123.

- 37 S. Kurtin, T. C. McGill and C. A. Mead, *Phys. Rev. Lett.*, 1969, 22, 1433.

- 38 M. Lorenz, A. Lajn, H. Frenzel, M. Grundmann, P. Barquinha, R. Martins and E. Fortunato, *Appl. Phys. Lett.*, 2010, 97, 243506.

- 39 H. Frenzel, A. Lajn, M. Brandt, H. V. Wenckstern, G. Biehne, H. Hochmuth, M. Lorenz and M. Grundmann, *Appl. Phys. Lett.*, 2008, **92**, 192108.

- 40 H. Frenzel, A. Lajn, H. V. Wenckstern, G. Biehne, H. Hochmuth and M. Grundmann, *Thin Solid Films*, 2009, **518**, 1119–1123.

- 41 D. K. Schroder, Semiconductor Material and Device Characterization, John Wiley & Sons, 2015, 978-0-471-73906-7.

- 42 J. G. J. Chern, P. Chang, R. F. Motta and N. Godinho, *IEEE Electron Device Lett.*, 1980, 1, 170–173.

- 43 N. On, B. K. Kim, S. Lee, E. H. Kim, J. H. Lim and J. K. Jeong, *IEEE Trans. Electron Devices*, 2020, **67**, 5544–5551.

- 44 L. Lin, Y. Guo and J. Robertson, Appl. Phys. Lett., 2012, 101, 052110.

- 45 M. S. Kim, S. H. Hwang, S. H. Kim, J. H. Kim, E. Park, K. H. Han and H. Y. Yu, *IEEE Electron Device Lett.*, 2023, 44, 1040–1043.

- 46 H. Jeon, B. Jung, Y. D. Kim, W. Yang and R. J. Nemanich, J. Appl. Phys., 2000, 88, 2467–2471.

- 47 A. Newman, A. Campos, D. Pujol, P. Fornara, M. Gregoire and D. Mangelinck, *Mater. Sci. Semicond. Process.*, 2023, 162, 107488.

- 48 W. Tang, S. T. Picraux, J. Y. Huang, A. M. Gusak, K.-N. Tu and S. A. Dayeh, *Nano Lett.*, 2013, **13**, 2748–2753.

- 49 X. Chen, F. Du, C. Wang, H. Xu, Y. Zhang, F. Hou, X. Yang, Y. Wu, C. Tsai, Z. Chen, Y. Guo, Z. Liu and X. Wu, *IEEE Trans. Electron Devices*, 2021, 68, 1378–1381.

- 50 M. H. Cho, C. H. Choi, M. J. Kim, J. S. Hur, T. Kim and J. K. Jeong, ACS Appl. Mater. Interfaces, 2023, 15, 19137–19151.

- 51 H. J. Yang, H. J. Seul, M. J. Kim, Y. Kim, H. C. Cho, M. H. Cho, Y. H. Song, H. Yang and J. K. Jeong, ACS Appl. Mater. Interfaces, 2020, 12, 52937–52951.

- 52 H. J. Seul, J. H. Cho, J. S. Hur, M. H. Cho, M. H. Cho, M. T. Ryu and J. K. Jeong, *J. Alloys Compd.*, 2022, 903, 163876.

- 53 J. Park, M. Shin and J. Yi, *Mater. Sci. Semicond. Process.*, 2020, **120**, 105253.

- 54 J. Kataoka, N. Saito, T. Ueda, T. Tezuka, T. Sawabe and K. Ikeda, *Jpn. J. Appl. Phys.*, 2019, **58**, SBBJ03.

- 55 S. H. Kang, I. S. Lee, K. Kwak, K. T. Min, N. B. Choi, H. W. Hwang, H. C. Choi and H. J. Kim, ACS Appl. Electron. Mater., 2022, 4, 2372–2379.

- 56 H. Park, J. Yun, S. Park, I. Ahn, G. Shin, S. Seong, H. J. Song and Y. Chung, ACS Appl. Electron. Mater., 2022, 4, 1769–1775.

- 57 J. Lu, W. Wang, J. Liang, J. Lan, L. Lin, F. Zhou, K. Chen, G. Zhang, M. Shen and Y. Li, *IEEE Electron Device Lett.*, 2022, 43, 890–893.

- 58 H. Tsuji, T. Takei, M. Ochi, M. Miyakawa, K. Nishiyama, Y. Nakajima and M. Nakata, *IEEE J. Electron Devices Soc.*, 2022, **10**, 229–234.

- 59 C. Niu, Z. Lin, V. Askarpour, Z. Zhang, P. Tan, M. Si, Z. Shang, Y. Zhang, H. Wang, M. S. Lundstrom, J. Maassen and P. D. Ye, *IEEE Trans. Electron Devices*, 2024, 71, 3403–3410.

- 60 D. H. Lee, Y. H. Kwon, N. J. Seong, K. J. Choi, G. Kim and S. M. Yoon, ACS Appl. Electron. Mater., 2022, 4, 6215–6228.

- 61 T. Kim, Y. Kim, J. Ahn and E. K. Kim, ACS Appl. Electron. Mater., 2023, 5, 3772–3779.

- 62 J. H. Jeong, S. H. Yoon, S. H. Lee, B. J. Kuh, T. Kim and J. K. Jeong, *IEEE Electron Device Lett.*, 2024, 45, 849–852.

- 63 S. Hu, K. Lu, H. Ning, Z. Fang, X. Liu and W. Xie, *IEEE Electron Device Lett.*, 2018, 39, 504–507.

- 64 J. L. Kim, C. K. Lee, M. J. Kim, S. H. Lee and J. K. Jeong, *Thin Solid Films*, 2021, 731, 138759.

- 65 H. Yang, X. Zhou, H. Fu, B. Chang, Y. Min, H. Peng, L. Lu and S. Zhang, ACS Appl. Mater. Interfaces, 2021, 13, 11442–11448.

- 66 T. Mudgal, N. Walsh, R. G. Manley and K. D. Hirschman, ECS Trans., 2014, 61, 405–417.

- 67 H. Ji, A. Y. Hwang, C. K. Lee, P. S. Yun, J. U. Bae, K.-S. Park and J. K. Jeong, *IEEE Trans. Electron Devices*, 2015, 62, 1195–1199.

- 68 K.-H. Choi and H.-K. Kim, Appl. Phys. Lett., 2013, 102, 052103.

- 69 J. Lee, S. Byeon, S. Kim, S. W. Yoo, W. Lee, S. Hong, M. Hee Cho, S. Jin Kim, D. Ha and D. Sin Kim, *IEEE Electron Device Lett.*, 2024, **45**, 1665–1668.

- 70 Y. B. Li and T. P. Chen, *ECS J. Solid State Sci. Technol.*, 2023, 12, 095003.

- 71 D. Luo, H. Xu, M. Zhao, M. Li, M. Xu, J. Zou, H. Tao, L. Wang and J. Peng, ACS Appl. Mater. Interfaces, 2015, 7, 3633–3640.

- 72 R. R. Chowdhury, M. S. Kabir, R. G. Manley and K. D. Hirschman, *ECS Trans.*, 2019, **92**, 135–142.

- 73 M. S. Kabir, R. R. Chowdhury, R. G. Manley and K. D. Hirschman, *ECS Trans.*, 2020, **98**, 81–88.

- 74 T. Ui, K. Yasuta, Y. Yamane and J. Tatemichi, *ECS Trans.*, 2022, **109**, 67–78.

- 75 L. X. Qian, W. M. Tang and P. T. Lai, ECS Solid State Lett., 2014, 3, 87–90.

- 76 B. H. Lee, D. Y. Lee, J. Y. Lee, S. Park, S. Kim and S. Y. Lee, *Solid-State Electron.*, 2019, **158**, 59–63.

- 77 S. H. Moon, Y. H. Kwon, N. J. Seong, K. J. Choi and S. M. Yoon, *IEEE Electron Device Lett.*, 2023, 44, 1128–1131.

- 78 Y. Magari, H. Makino and M. Furuta, ECS J. Solid State Sci. Technol., 2017, 6, Q101–Q107.

- 79 B. Du Ahn, H. S. Shin, H. J. Kim, J. S. Park and J. K. Jeong, *Appl. Phys. Lett.*, 2008, 93, 203506.

- 80 X. D. Huang, J. Q. Song and P. T. Lai, *IEEE Electron Device Lett.*, 2016, 37, 1574–1577.

- 81 J. S. Park, J. K. Jeong, Y. G. Mo, H. D. Kim and S. I. Kim, *Appl. Phys. Lett.*, 2007, **90**, 262106.

- 82 S. H. Yang, J. Y. Kim, M. J. Park, K. H. Choi, J. S. Kwak, H. K. Kim and J. M. Lee, *Surf. Coat. Technol.*, 2012, 206, 5067–5071.

- 83 J. H. Kang, E. Namkyu Cho, C. Eun Kim, M. J. Lee, S. Jeong Lee, J. M. Myoung and I. Yun, *Appl. Phys. Lett.*, 2013, 102, 222103.

- 84 J. K. Lee, S. An and S. Y. Lee, *IEEE Electron Device Lett.*, 2023, 44, 1845–1848.

- 85 D. Ahmad, J. Xu, J. Luo, N. Zhou, J. Gao and Y. Lu, *Appl. Surf. Sci.*, 2024, 672, 160891.

- 86 H. Jeong, B. Lee, Y. Lee, J. Lee, M. Yang, I. Kang, M. Mativenga and J. Jang, *Appl. Phys. Lett.*, 2014, **104**, 022115.

- 87 Y. Zhang, J. Li, Y. Zhang, H. Yang, Y. Guan, M. Chan, L. Lu and S. Zhang, *IEEE Electron Device Lett.*, 2023, 44, 1300–1303.

- 88 J. G. Um and J. Jang, Appl. Phys. Lett., 2018, 112, 162104.

- 89 J. K. Um, S. Lee, S. Jin, M. Mativenga, S. Y. Oh, C. H. Lee and J. Jang, *IEEE Trans. Electron Devices*, 2015, 62, 2212–2218.

- 90 H. Jang, S. J. Lee, Y. Porte and J. M. Myoung, Semicond. Sci. Technol., 2018, 33, 035011.

- 91 S. Knobelspies, A. Takabayashi, A. Daus, G. Cantarella, N. Münzenrieder and G. Tröster, *Solid-State Electron.*, 2018, 150, 23–27.

- 92 W. S. Liu, C. H. Hsu, Y. Jiang, Y. C. Lai and H. C. Kuo, Semicond. Sci. Technol., 2021, 36, 045007.

- 93 J. W. Kim, T. J. Jung and S. M. Yoon, J. Alloys Compd., 2019, 771, 658–663.

- 94 S. H. Bae, H. J. Ryoo, J. H. Yang, Y. H. Kim, C. S. Hwang and S. M. Yoon, *IEEE Trans. Electron Devices*, 2021, 68, 6159–6165.

- 95 N. Saito, T. Sawabe, J. Kataoka, T. Ueda, T. Tezuka and K. Ikeda, *Jpn. J. Appl. Phys.*, 2019, **58**, SBBJ07.

- 96 Y. Kang, K. Han, Y. Chen and X. Gong, 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). IEEE, 2023, 1–2.

- 97 S. H. Noh, H. E. Kim, J. H. Yang, Y. H. Kim, Y. H. Kwon, N. J. Seong, C. S. Hwang, K. J. Choi and S. M. Yoon, *IEEE Trans. Electron Devices*, 2022, **69**, 5542–5548.

- 98 J. Zhang, Z. Lin, Z. Zhang, K. Xu, H. Dou, B. Yang, A. Charnas, D. Zheng, X. Zhang, H. Wang and P. D. Ye, *IEEE Trans. Electron Devices*, 2023, **70**, 6651–6657.

- 99 C. Hung, S. Wang, C. Lin, C. Wu, Y. Chen, P. Liu, Y. Tu and T. Lin, *Jpn. J. Appl. Phys.*, 2016, 55, 06GG05.

- 100 M. Liu, H. Kim, X. Wang, H. W. Song, K. No and S. Lee, *ACS Appl. Electron. Mater.*, 2021, **3**, 2703–2711.

- 101 S. Choi, IEEE Electron Device Lett., 2020, 42, 168–171.

- 102 Q. Li, C. Gu, S. Zhu, Q. Hu, W. Zhao and X. Li, IEDM, 2022, 2–7.

- 103 J. H. Jeong, S. W. Seo, D. Kim, S. H. Yoon, S. H. Lee, B. J. Kuh, T. Kim and J. K. Jeong, *Sci. Rep.*, 2024, 14, 10953.

- 104 C. K. Lee, D. Y. In, D. J. Oh, S. H. Lee, J. W. Lee and J. K. Jeong, *IEEE Trans. Electron Devices*, 2018, 65, 1383–1390.

- 105 V. P. Madangarli, G. Gradinaru, G. Korony, T. S. Sudarshan, G. M. Loubriel, F. J. Zutavern and P. E. Patterson, Sandia National Labs, 1994, https://www.osti.gov/servlets/purl/ 10163562.

- 106 V. P. Madangarli, G. Korony, G. Gradinaru and T. S. Sudarshan, IEEE Trans. Electron Devices, 1996, 43, 793–799.

- 107 J. T. Smith, A. D. Franklin, D. B. Farmer and C. D. Dimitrako-poulos, ACS Nano, 2013, 7, 3661–3667.

- 108 H. Y. Park, W. S. Jung, D. H. Kang, J. Jeon, G. Yoo, Y. Park, J. Lee, Y. H. Jang, J. Lee, S. Park, H. Y. Yu, B. Shin, S. Lee and J. H. Park, *Adv. Mater.*, 2015, 28, 864–870.

- 109 V. Passi, A. Gahoi, E. G. Marin, T. Cusati, A. Fortunelli,

G. Iannaccone, G. Fiori and M. C. Lemme, *Adv. Mater. Interfaces*, 2019, 6, 1801285.

- 110 W. Park, S. F. Shaikh, J. W. Min, S. K. Lee, B. H. Lee and M. M. Hussain, *Nanotechnology*, 2018, **29**, 325202.

- 111 J. S. Kim, M. K. Joo, M. X. Piao, S. E. Ahn, Y. H. Choi, J. Na, M. Shin, M. J. Han, H. K. Jang and G. T. Kim, *Thin Solid Films*, 2014, **558**, 279–282.