# Nanoscale

Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

High uniformity and improved nonlinearity by embedding nanocrystal

in selector-less RRAM

Writam Banerjee\*, Nianduan Lu, Ling Li, Pengxiao Sun, Qi Liu, Hangbing Lv,

Shibing Long, and Ming Liu

**Abstract**

Sneak path problem is one of the major hindrances for the application of high density

3D crossbar resistive random access memory (RRAM). For the selector-less RRAM

devices, nonlinear (NL) current-voltage (I-V) characteristics is an alternative approach

to minimize the sneak paths. In this work we have demonstrated metallic IrO<sub>x</sub>

**RRAM** nanocrystal  $(IrO_x-NC)$ based selector-less crossbar devices

IrO<sub>x</sub>/AlO<sub>x</sub>/IrO<sub>x</sub>-NC/AlO<sub>x</sub>/W structure with very reliable hysteresis resistive switching

(RS) of > 10,000 cycles, stable multiple levels, high temperature (HT) data retention.

Moreover, an improvement in the NL behavior has been reported as compared to a pure

high-κ AlO<sub>x</sub> RRAM. The origin of the NL nature has been discussed using hopping

model and Luittenger's 1D metal theory. The nonlinearity can be further improved by

structure engineering and will improve the sensing margin of the devices, which is

rewarding for crossbar array integration.

**Keywords:** resistive switching, nanocrystal, nonlinearity, variable range hopping,

Luttinger's model

Laboratory of Nano-Fabrication and Novel Devices Integrated Technology, Institute of Microelectronics,

Chinese Academy of Sciences, Beijing 100029, China.

E-mail: writam.banerjee@gmail.com/writam.banerjee@ime.ac.cn

Tel: 86-10-82995582; Fax: 86-10-82995583

1

# Introduction

The continuous advancement in dimensional miniaturization with amplified performance of non-volatile memories (NVM), adds the impulsive force to widening of the horizon with introducing new applications. Due to fundamental scaling limit with process complexity of mainstream NVM devices, distinct and individual alternative approaches with exciting architectures are being explored. RRAM is a simple metal-insulator-metal (MIM) based emerging NVM in which an electrical resistance (R) will be periodically altered within a high resistance state (HRS) and a low resistance state (LRS). Available memory window is defined by the ratio of two R states i.e  $\xi$  = HRS/LRS at a fixed read voltage (V<sub>READ</sub>). RRAM holds a great potential as emerging candidate because of its simple design, high speed operation, magnificent scalability and good control over economic consumption. Binary oxide, 4 transition metal oxides, 5 chalcogenides<sup>6</sup> and organic compounds<sup>7</sup> are being investigated for the active body of the resistive switches. In RRAM, switching stability is one of the major commodities. To improve the stability in RS, several methods including nanocrystals (NC) such as ruthenium (Ru), gold (Au), copper (Cu), platinum (Pt), i iridium oxide (IrO<sub>x</sub>) and et al have been reported. Recently, to compete with 3D V-NAND technology, the small 4F<sup>2</sup> feature size of RRAM devices are utilizing successfully for high density crossbar 3D architecture in horizontal<sup>13</sup> or in vertical direction.<sup>14</sup> The gradation of density can be controlled by n-layers of crossbar array with a minimum feature size of 4F<sup>2</sup>/n. Sneak current paths are the general problem in crossbar RRAM devices. 15 Since, the crossbar design connects each word line (WL) and bit line (BL) in the perpendicular direction, the read operation can significantly be affected by the parasitic sneak path currents. <sup>16</sup> The sneak path problem can be solved by introducing a selector device such as diode, <sup>17</sup> threshold switches <sup>18</sup> with RRAM cell. But unfortunately the one selector and one RRAM device (1S-1R) configuration can increase process complexity. A simple RRAM cell with NL nature can solve this problem. <sup>19</sup> NL behaviour in I-V hysteresis can effectively reduce the undesired current flow through a series-parallel configuration of crossbar array. Therefore, NL is a much needed parameter to come into possession of a better high density crossbar RRAM array operation. Several ways have been proposed to improve NL nature, such as active layer thickness engineering, <sup>20</sup> hetero-structure design, <sup>21-23</sup> but indeed, improvement of NL by NC with very stable RS phenomena not has been reported yet.

Hence, this paper will present a simple IrO<sub>x</sub>-NC based crossbar RRAM device with more stable hysteresis switching cycles of > 10,000, more reliable multi levels (retentivity >10<sup>5</sup> sec for each state) and more NL nature, which is useful for crossbar array application. A pure high-κ AlO<sub>x</sub> based crossbar RRAM devices has also been fabricated for comparison. To understand the RS phenomena, the I-V curves were fitted to several mechanisms and fortunately the crossbar RRAM received a specified treatment in terms of variable range hopping (VRH) conduction. Interestingly, the temperature dependent I-V relations are in well agreement with Luttinger's model<sup>24</sup> of 1D metal and overlapping together to follow a single master curve, which can develop the realization of the dominant conduction mechanism by tunnelling through defects. It has been shown that nanotubes,<sup>25</sup> nanowires<sup>26</sup> and also nanofibers<sup>27</sup> obtained NL charge

transport behaviour in terms of Luttinger's theory. This time we investigate this model for the metal nanocrystal (MNC) based crossbar RRAM devices. The achievements of this study may be the opening of the upcoming new possibilities of realizing high performing RS phenomena, depending on which modern electronics can visualize the goal of very high density 3D crossbar array.

# Experimental

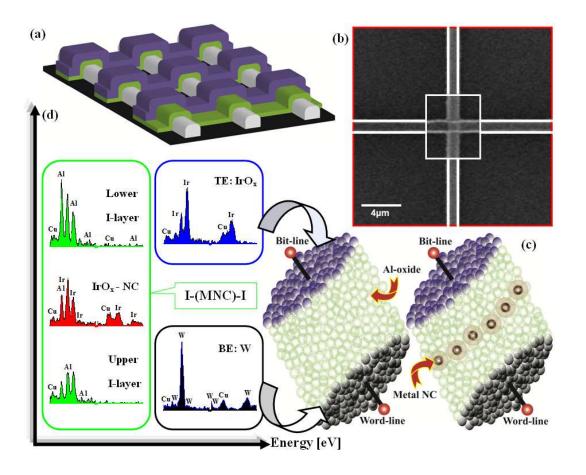

A simple MIM stack was fabricated to design crossbar RRAM devices. As an I-layer, high-κ materials are playing a major role to form the main body of the RS. Since 1962, in the very early stage of the NVM technology, RS phenomena was first introduced by T. W. Hickmott, based on the Si-oxide and other high-κ oxide materials.<sup>28</sup> A favourable reception to the high-κ materials as switching layer has been offered by the advanced RRAM technology in a regular manner. RS phenomena are found in many high- $\kappa$  materials such as  $AlO_x$ ,  $^{12,29,30}$   $TiO_x$ ,  $^{21}$   $TaO_x$ ,  $^{22}$   $HfO_x$ ,  $^{31}$  and so on. In the latest addition of International Technological Roadmap for Semiconductors (ITRS)<sup>1</sup> have taken into account the MNC in the I-layer to form a MI-(MNC)-IM structure for the emerging research memory device. The high work function (WF) metal has been used to form MNC in I-layer. Inert metals were selected to form both of the BL and WL for all of those fabricated crossbar RRAM devices. RS based on highly conducting metallic filament formed by cation movement can be avoided by using inert metal lines, which can control the RS mechanism by anion migration i.e the movement of oxygen ions towards the anode or in reverse way oxygen vacancies (V<sub>0</sub>) towards the cathode.<sup>3</sup> Before fabrication the Si/SiO<sub>2</sub> was chosen as the substrate. To fabricate the crossbar RS devices, at first tungsten (W) with a thickness of  $\sim 80$  nm was deposited by sputtering process on the full wafer. During deposition a pure metallic W target was used with a power of 150 W under Ar environment. Photolithographic and wet etching processes were used to design the W as WL with bottom pad. After patterning the bottom lines, another optical lithographic step was introduced to pattern the RS oxide and BL layers. Then, a 5 nm thick AlO<sub>x</sub> as lower I-layer and 2 nm as Upper I-layer was sputtered from a pure Al<sub>2</sub>O<sub>3</sub> target with a power of 80 W under Ar and oxygen gas mixture. To form the I-(MNC)-I structure, 1 nm thick IrO<sub>x</sub> layer was deposited in between the lower and upper I-layers. The formation of as-deposited NCs depends on many factors, such as, 1) the nature of the material, 2) adhesion to the deposited surface, 3) surface energy of the deposited film with respect to the substrate and 4) very importantly on the as-deposited film thickness. The formation of the as-deposited IrO<sub>x</sub>-NC<sup>12</sup> and the effect of thickness and annealing temperature<sup>32</sup> already have been reported. The IrO<sub>x</sub> layer was deposited from a pure Ir target with the power of 50 W in the Ar and oxygen environment. Finally, on top 80 nm thick IrO<sub>x</sub> as BL was sequentially deposited by sputtering process abide by lift-off. The main difference between S1 and S2 RRAM is the IrO<sub>x</sub>-NC layer. A simple illustration of cross-bar devices is shown in Fig. 1a.

The scanning electron microscopic (SEM) analysis of the RRAM device was done by using Zeiss-Supra 55. RRAM devices were electrical characterized by using Keithley-4200SCS the semiconductor characterization system.

### Results and discussion

The SEM image of the fabricated  $IrO_x$ -NC RRAM with a cross point of 1.5  $\mu$ m × 1.5  $\mu$ m is shown in **Fig. 1b**. Two different RRAM structures, one is with  $IrO_x$ -NC in MI-(MNC)-IM (S1) form and the other without  $IrO_x$ -NC in MIM (S2) form are illustrated in **Fig. 1c**. The different layers of the MI-(MNC)-IM structure were confirmed by the energy dispersive X-ray spectroscopy (EDS) analysis as shown in **Fig. 1d**. The formation of the tiny 1 nm  $IrO_x$ -NC within the  $AlO_x$  layer for the via-type RRAM devices has been reported elsewhere 12. This kind of structure engineering can play an important role to improve the much required properties of the crossbar RRAM devices for larger array integration.

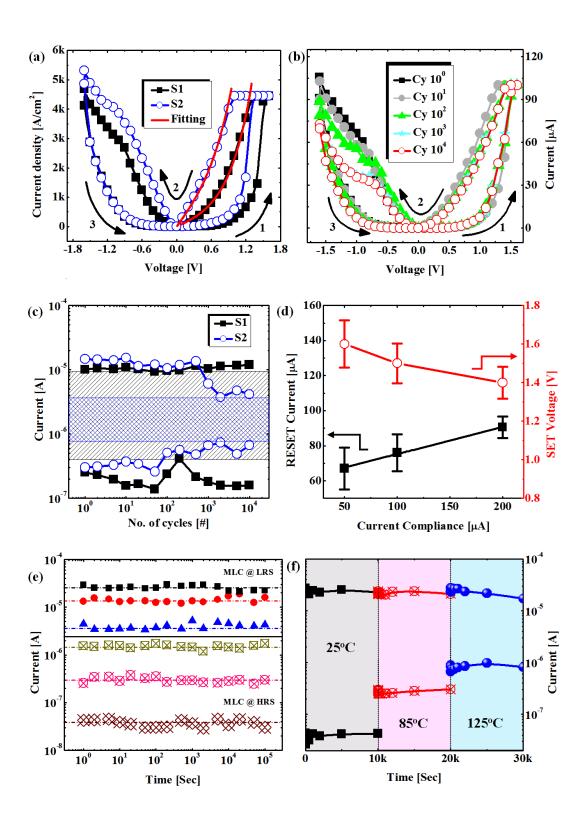

Fig. 2a shows a bipolar touch in current density-voltage (J-V) hysteresis characteristics of S1 and S2 crossbar RRAM devices. On applying an external stimulation with either a positive forward bias or a negative reverse bias the junction point of BL and WL can be turned-on depending on the virgin state of the I-layer. The initial resistance state for S1 and S2 devices were holding a HRS, thus a positive bias was applied to the BL to make the transition from HRS to LRS, called SET process. A negative voltage can make the transition from LRS to HRS, known as RESET process. Continuous arrows are indicating the RS direction. A similar manner of acting under the specified circumstances with >10,000 RS cycles at the same SET and RESET voltages can be observed for the S1 devices as shown in Fig. 2b. Applied current compliance (I<sub>CC</sub>) level was maintained at 100 μA throughout the continuous RS operations. As inert type high WF metal lines are employed in the BL and WL, anions like oxygen

vacancies (V<sub>o</sub>) will take place to control the electric current flow through the circuit. The BL will act as the cathode and WL will act as anode in this case. To complete the circuit, BL was raised to higher voltage level by applying a positive voltage and WL was grounded. The electron flow from BL to WL will be enhanced by increasing the voltage at BL ( $V_{BI}$ ). An abrupt transition of R state from 100 k $\Omega$  to 10 k $\Omega$  will take place with the  $V_{BL}$  above +1 V. In this situation, the  $V_o$  anions will be distributed in the whole range of the active layer and will make a connection between the WL and BL. Another transition from LRS to HRS i.e. the RESET transition will take place at -1.5 V. The resistance will increase gradually as the number of V<sub>o</sub> anions will decrease with the voltages. Because of the electric field enhancement, the filament formation will be guided by the MNC and as a result the higher switching stability has been achieved by S1 structure [Fig. 2c] with a nice I<sub>RESET</sub> scaling trend [Fig. 2d]. During the hysteresis switching measurements the SET and RESET voltages were fixed at +2 V and -1.5 V with the SET  $I_{CC}$  of 100  $\mu$ A. For the worse case the S1 and S2 devices are showing the resistance ratio of >20 and >5, respectively. Although the I<sub>RESET</sub> scaling was maintaining its nature at a low I<sub>CC</sub> of 10 µA, V<sub>SET</sub> was not showing the trend at the lower I<sub>CC</sub>. For a typical device the V<sub>SET</sub> and I<sub>RESET</sub> scaling trend is shown in Fig. S1 of supporting information. Highly stable multi levels of data storage capability are achieved for S1 devices at both of the high and low conducting states [Fig. 2e]. Fig. 2f shows that the fabricated S1 crossbar RRAM devices are capable to retain data at HT also. During the retention test SET and RESET were maintained at +2 V and -1.5 V, respectively, with a pulse of 500 µs. The I<sub>CC</sub> level (200 µA) was the same during the retention measurements at 25°C, 85°C and 125°C. Good nonvolatile characteristics can be achieved with  $\xi$  of >20 at 125°C.

The voltage dependent resistance changes are achieved by both of the S1 and S2 devices. But in this voltage dependent resistance network system, the voltage dependency in LRS of S1 devices is more prominent than that of the S2 devices [Fig. 2a]. A fair comparison within the same frame of the I-V characteristics indicates a parabolic type NL nature of the S1 devices.

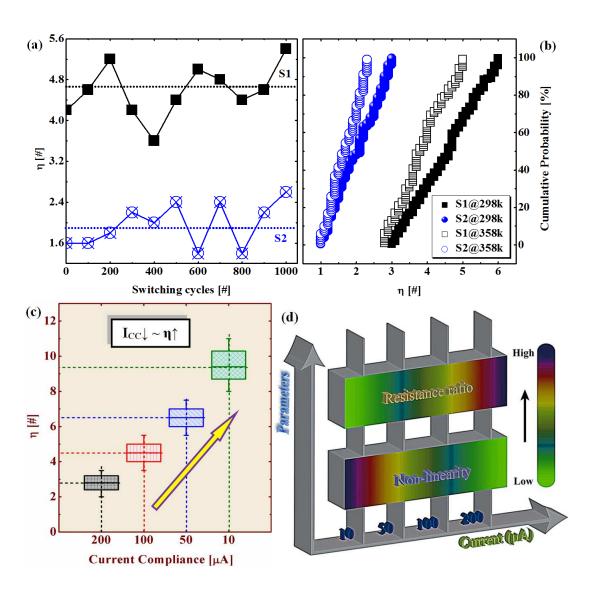

The NL factor  $(\eta)$  is defined as the ratio of current at the SET voltage  $(V_{SET})$  to the current at half of the  $V_{SET}$ . At the same operating conditions the higher  $\eta$  can be executed by S1 devices as shown in Fig. 3a. For the S1 devices the current at half of V<sub>SET</sub> is lower i.e higher R value is achieved as compare to the S2 devices. This voltage dependent resistance property can improve the sensing margin of the crossbar devices by making more resistive sneak paths. In a common crossbar, the selected device (SD) needs higher voltage than the half selected devices (HSD) or the unselected devices (USD). Hence, higher η value can easily introduce a higher resistive effect in HSD or USD. A simple illustration of the relation between  $\eta$  and crossbar array is shown in Fig. **S2** of the supporting information. To confirm the n characteristics, over 200 devices were measured for each type of the fabricated crossbar RRAM devices, are summarized in Fig. 3b. The cumulitive probability of the S1 and S2 devices at room temperature (RT) and HT can be obtained with different coefficient of variations ( $\phi$ ), where  $\phi$  is defined by the ratio of standard deviation ( $\sigma$ ) to mean ( $\mu$ ) value. Lower  $\phi$  can be observed for the S1 devices at RT and HT measurements. For S1 and S2 devices the

variation of  $\eta$  with different  $\phi$  values are listed in **Table S1** of the supporting information. One can achieve higher η for S1 devices at the RT as well as at the HT. When the writing process of the crossbar array RRAM devices is in progress, the higher η of the S1 devices are able to improve the voltage delivery through the SD. A study on voltage distribution scheme along the WL for linear and NL devices has shown the necessity of higher n<sup>16</sup> to create more resistive leakage paths, resulting a lesser degradation of the operating voltage have been achieved by the NL devices as compare to the linear one. Indeed higher η is one of the basic requirements to achieve one highly dense 3D crossbar RRAM array. Moreover, η can be further improved by reducing the current flow through the circuit. Distinguished NL values are achieved with maintaining an increasing trend in the company of decreasing  $I_{CC}$  as shown in Fig. 3c. S1 devices are showing almost linear nature with very less  $\eta$  at a high  $I_{CC}$  of 200  $\mu$ A. At  $I_{CC}$  of 100  $\mu$ A and 50  $\mu A$  the  $\eta$  values are accordingly ~ 4.5 and ~ 6.5. Similar  $\eta$  have been reported for the TiO<sub>2</sub> based 1T1R devices.<sup>20</sup> For S1 devices, highest  $\eta$  of > 10 can be observed with an  $I_{CC}$  of 10  $\mu$ A. NL value of > 10 have been reported for the other devices such as TaO<sub>x</sub>/TiO<sub>x</sub> based oxide hetero structure RRAM<sup>22</sup> and transition metal oxide (TMO) based RRAM. <sup>19</sup> One very clear  $\xi$  and  $\eta$  scaling trend can be observed from Fig. 3d. In brief, the lower the I<sub>CC</sub>, the lower the resistance ratio and the higher the nonlinearity.

In what follows, we want to discuss the physical origin of the switching mechanism for LRS. Actually, different conduction mechanisms have been suggested including SCLC, Fowler-Nordeim (FN) tunneling or Pool Frenckel (PF) emission. However, here we suggest that VRH is responsible for the conduction process and the  $V_{\rm o}$  dominates the

switching mechanism of the fabricated RRAM devices. According to hopping theory,<sup>33</sup> the I-V curves of RRAM device can be formulated as the **Equation 1**.

$$J \sim 2eR'N_tk_BT\gamma_oexp(\theta'_{nn})\sinh\left(\frac{eR'F}{k_BT}\right)$$

(1)

The current density is denoted by J where e is electron charge, R' is the average hopping distance,  $N_t$  is the density of localized states in volume and energy ground t,  $k_B$  is the Boltzman constant, T is the temperature,  $\gamma_0$  is the attempt frequency,  $\theta'_{nn}$  is the average nearest hopping range. If, for a given T the carrier will be hoping to a site within a sphere of radius r(T). Then, the average hopping distance can be written as **Equation 2**.

$$R' \sim \left(\frac{3}{16\pi N_t \phi k_B T}\right)^{\frac{1}{2}} \tag{2}$$

where,  $\varphi$  is the inverse localization length ( $\varphi^{-1} = 0.1$  nm and 0.12 nm for  $AlO_x$  and  $IrO_x$ , respectively). The I-V curves are superposed perfectly with this hopping theory as shown in **Fig. 2a**. Therefore, it is expected that hopping process is the dominating factor of the current conduction through the formation of the  $V_0$  anion filament.

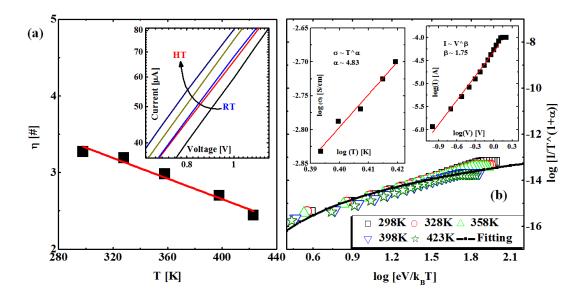

NL behaviour is a strong dependant of T. The T dependent LRS I-V characteristics are plotted in the inset of **Fig. 4a**. With increasing of T the LRS current increases which is clearly an indication of the non-metallic filament formation through the anion migration for the fabricated RRAM devices.<sup>34</sup> For 1D system, the average nearest hopping  $\theta'_{nn}$  is inversely related to the operating T as shown in **Equation 3**.

$$\theta'_{\rm nn} = \left(\frac{T_{\rm o}}{T}\right)^{\frac{1}{2}} \tag{3}$$

Therefore,  $\theta'_{nn}$  decreases with increasing T, which is related to  $\eta$  of the devices with different T. If one can plot the graph  $\eta(T)$  vs T [Fig. 4a], a clear decreasing trend of  $\eta$

can be observed with increasing of T. As the hopping distance is continuously decreasing with increasing T, hence  $\eta$  becomes weaker at higher T. The conductivity ( $\sigma$ ) of the devices is strongly depends on T. Indeed, as  $\sigma$  increases with T, resulting a lower R and lower  $\eta$  at HT. More remarkably,  $\sigma$  related to T with a simple power-law equation. In agreement with Luttinger's model of 1D metal,  $\sigma \sim T^{\alpha}$  at lower  $V_{BL}$  can be well fitted in our case. The universal scaling character in T dependent I-V curves is the major prediction of the Luttinger's model. When  $I/T^{(1+\alpha)}$  is plotted against  $eV_{BL}/k_BT$ , then all of those different T dependent I-V curves will be conjugated together and will generate a single I as written in **Equation 4**.<sup>24</sup>

$$I = I_o T^{(1+\alpha)} \cdot \sinh\left(\frac{\gamma e V_{BL}}{k_B T}\right) \cdot \left| \Gamma\left[\frac{(\beta+1)}{2} + \frac{i\gamma e V_{BL}}{\pi k_B T}\right] \right|^2$$

(4)

where  $I_0$  and  $\gamma$  are the constants,  $\Gamma$  is the gamma function and  $\beta$  is related to I and V at low T i.e  $I \sim V^{\beta}$ . With  $\alpha \sim 4.83$  and  $\beta \sim 1.75$  [inset of **Fig. 4b**], the Luttinger's model is fitted perfectly with our experimental results. A comparison of  $\alpha$  and  $\beta$  values for this work and the other reported works are shown in **Table S2** of supporting information. All of those different T dependent I-V characteristics will show good power-law behaviour and will collapse quite nicely onto a universal curve over the entire bias range excepting the higher bias region where the device reaches the  $I_{CC}$  value, as shown in **Fig. 4b**. As the  $V_0$  anions are playing a major role to control the switching mechanism, therefore we assume the whole filament as a 1D quantum many-body system. The charges will forward through devices by tunnelling through the 1D quantum defects created by the formation of  $V_0$  anions. This is the generation of the idea about the hopping through defects and the origin of NL characteristics of the

fabricated crossbar RRAM devices. Further improvement in the structure design is necessary to achieve very high  $\eta$  for real high density crossbar array integration.

# Conclusions

The structure engineering based on I-MNC-I concept for selector-less crossbar RRAM has been reported in this study. The design will allow a high stability in hysteresis switching endurance of >10,000 cycles, well controlled SET and RESET operations, multiple levels in HRS as well as in LRS, HT data retention with improved nonlinearity in the LRS. The higher the η, the higher the writing power efficiency, as maximum current will flow through SD and can be achieved with lower I<sub>CC</sub> and lower T. We believe that, this new approach offers the flexibility to engineer nonlinearity which can meet the urgent requirements of the future crossbar RRAM memory technology. But more analysis on device structure design is necessary to achieve high density memory application with good resistance ratio, high nonlinearity even at HT, reliable switching cycles and good retention at low current.

# Acknowledgements

This work is founded by the China Postdoctoral Science Foundation under grant No. 2014M561083 and the Ministry of Science and Technology of China under grant Nos. 2014AA032901, 2013CBA01604, 2011AA010402, 2011CB707600, 2011AA010401, 2013CBA01604, 2014AA032900 and National Natural Science Foundation of China under grant Nos. 61322408, 61334007, 61376112, 61221004, 61274091, 61106119, 61106082, and 61006011.

### References

- 1 Industrial Technology Roadmap for Semiconductors, http://www.itrs.net/, 2013.

- 2 A. Sawa, *Mater Today.*, 2008, **11**, 28.

- 3 R. Waser, M. Aono, *Nat. Mater.*, 2007, **6**, 833-840.

- I. G. Baek, M. S. Lee, S. Seo, M. J. Lee, D. H. Seo, D.-S. Suh, J. C. Park, S. O. Park, H. S. Kim, I. K. Yoo, U-In. Chung, and J. T. Moon, *Tech. Dig. Int. Electron Devices Meet.*, 2004, 587-590.

- 5 M.-J. Lee, S. Han, S. H. Jeon, B. H. Park, B. S. Kang, S.-E. Ahn, K. H. Kim, C. B. Lee, C. J. Kim, I.-K. Yoo, D. H. Seo, X.-S. Li, J.-B. Park, J.-H. Lee, and Y. Park, *Nano Lett.*, 2009, 9, 1476-1481.

- 6 M. N. Kozicki, M. Yun, L. Hilt, and A. Singh, *Pennington NJ USA:*Electrochemical Society., 1999, **99**, 298-309.

- 7 J. C. Scott, and L. D. Bozano, *Adv. Mater.*, 2007, **19**, 1452–1463.

- 8 J. H. Yoon, K. M. Kim, M. H. Lee, S. K. Kim, G. H. Kim, S. J. Song, J. Y. Seok, and C. S. Hwang, *Appl. Phys. Lett.*, 2010, 97, 232904.

- 9 W. Guan, S. Long, R. Jia, and M. Liu, *Appl. Phys. Lett.*, 2007, **91**, 062111.

- 10 Q. Liu, S. Long, W. Wang, S. Tanachutiwat, Y. Li, Q. Wang, M. Zhang, Z. Huo, J. Chen, and M. Liu, *IEEE Electron Device Lett.*, 2010, **31**, 1299-1301.

- 11 M. J. Yun, H.-D. Kim, S. M. Hong, J. H. Park, D. S. Jeon, and T. G. Kim, *J. Appl. Phys.*, 2014, **115**, 094305.

- W. Banerjee, S. Maikap, C. S. Lai, Y. Y. Chen, T. C. Tien, H. Y. Lee, W. S. Chen, F. T. Chen, M. J. Kao, M. J. Tsai, and J. R. Yang, *Nanoscale Res. Lett.*, 2012, 7, 194.

- 13 Q. Xia, J. J. Yang, W. Wu, X. Li, and R. S. Williams, *Nano Lett.*, 2010, 10, 2909-2914.

- 14 S.-G. Park, M. K. Yang, H. Ju, D.-J. Seong, J. M. Lee, E. Kim, S. Jung, L. Zhang, Y. C. Shin, I.-G. Baek, J. Choi, H.-K. Kang, and C. Chung, *Tech. Dig. Int. Electron Devices Meet.*, 2012, 501-504.

- 15 J. Liang, and H.-S. P. Wong, *IEEE Trans. Electron Devices.*, 2010, 57, 2531-2538.

- 16 An. Chen, *IEEE Trans. Electron Device.*, 2013, **60**, 1318-1326.

- 17 Y. Li, H. Lv, Q. Liu, S. Long, M. Wang, H. Xie, K. Zhang, Z. Huo, and M. Liu, Nanoscale, 2013, 5, 4785-4789.

- S. Kim, Y.-B. Kim, K. M. Kim, S.-J. Kim, S. R. Lee, M. Chang, E. Cho, M.-J. Lee, D. Lee, C. J. Kim, U.-I. Chung, and I.-K. Yoo, *Symposium on VLSI Tech. Dig.*, 2013, 240.

- 19 S. Lee, D. Lee, J. Woo, E. Cha, J. Song, J. Park, and H. Hwang, *Tech. Dig. Int. Electron Devices Meet.*, 2013, 272-275.

- 20 F. Lentz, B. Roesgen, V. Rana, D. J. Wouters, and R. Waser, *IEEE Electron Device Lett.*, 2013, **34**, 996-998.

- J. J. Yang, M.-X. Zhang, M. D. Pickett, F. Miao, J. P. Strachan, W.-D. Li, W. Yi, D. A. A. Ohlberg, B. J. Choi, W. Wu, J. H. Nickel, G. M. Ribeiro, and R. S. Williams, *Appl. Phys. Lett.*, 2012, 100, 113501.

- 22 Y. Yang, S. H. Choi, and W. Lu, *Nano Lett.*, 2013, **13**, 2908–2915.

- 23 Y.-S. Chen, H.-Y. Lee, P.-S. Chen, W.-S. Chen, K.-H. Tsai, P.-Y. Gu, T.-Y. Wu,

- C.-H. Tsai, S. Z. Rahaman, Y.-D. Lin, F. Chen, M.-J. Tsai, and T.-K. Ku, *IEEE Electron Device Lett.*, 2014, **35**, 202-204.

- 24 J. D. Yuen, R. Menon, N. E. Coates, E. B. Namdas, S. Cho, S. T. Hannahs, D. Moses, and A. J. Heeger, *Nat. Mater.*, 2009, 8, 572-575.

- Z. Yao, H. W. C. Postma, L. Balents, and C. Dekker, *Nature.*, 1999, 402,

273-276.

- 26 L. Venkataraman, Y. S. Hong, and P. Kim, *Phys. Rev. Lett.*, 2006, **96**, 076601.

- 27 A. N. Aleshin, H. J. Lee, Y. W. Park, and K. Akagi, *Phys. Rev. Lett.*, 2004, 93, 196601.

- 28 T. W. Hickmott, J. Appl. Phys. 1962, **154**, 2669–2682.

- 29 W. Banerjee, S. Z. Rahaman, and S. Maikap, *Jap. J. Appl. Phys.*, 2012, 51, 04DD10.

- 30 Y. Wu, S. Yu, H. -S. P. Wong, Y.-S. Chen, H.-Y. Lee, S.-M. Wang, P.-Y. Gu, F. Chen, M.-J. Tsai, *IEEE International Memory Workshop*, 2012.

- 31 S. Yu, H.-Y. Chen, B. Gao, J. Kang, and H.-S. P. Wong, *ACS Nano.*, 2013, 7, 2320-2325.

- 32 W. Banerjee, S. Maikap, T.-C. Tien, W.-C. Li, and J.-R. Yang, *J. Appl. Phys.*, 2011, **110**, 074309.

- 33 V. L. Nguyena, and D.-T. Dang, *Physica B.*, 2003, **334**, 88-97.

- 34 H. Sun, Q. Liu, S. Long, H. Lv, W. Banerjee and M. Liu, J. Appl. Phys., 2014, 116, 154509.

- 35 F. D. M. Haldane, J. Phys. C: Solid State Phys., 1981, 14, 2585-2609.

36 L. Li, N. Lu, and M. Liu, J. Appl. Phys., 2014, 116, 164504.

**Fig. 1** The crossbar RRAM structures. (a) Schematic illustration of a crossbar array. (b) Scanning electron microscopy (SEM) image of a 1.5 μm × 1.5 μm cross point. (c) The schematic of the junction point of MI-(MNC)-IM device (S1) and MIM device (S2). (d) The layer by layer elemental analysis of the S1 crossbar RRAM devices has been confirmed by the energy dispersive X-ray analysis. A clear evidence of MNC is found in between the insulating layers.

Fig. 2 Memory performance of the fabricated RRAM devices. (a) Typical bipolar J-V hysteresis switching for the S1 and S2 devices with  $I_{CC}$  of 100  $\mu A$ . VRH process is

fitted well with the LRS of the devices. The input parameters are:  $N_t$ =  $4\times10^9$  m<sup>-1</sup> and  $\gamma_0$  =  $1\times10^{13}$  s<sup>-1</sup>. (b) Very stable continuous RS of >10,000 cycles are achieved for S1 RRAM, because of the formation of stable filament. (c) MNC within the structure are playing a vital role to control the stability of the filament. Therefore, the superior stability is obtained for S1 RRAM instead of S2. (d)  $I_{RESET}$  and  $V_{SET}$  depends on  $I_{CC}$  upto a certain limit. For very low  $I_{CC}$  the trend was not matching perfectly. (e) Various levels can be achieved for the lower conducting state as well as for the higher conducting state. Reliability of each state has been tested over 27 hours. (f) High non-volatility can be observed even at  $125^{\circ}C$ .

**Fig. 3** Nonlinear behavior of the crossbar RRAM devices. (a) The variation of  $\eta$  over switching cycles for S1 and S2 devices. (b) The cumulative probability distribution of  $\eta$  at RT and HT with a same  $I_{CC}$  of 100 μA. Higher  $\eta$  will introduce more resistive sneak paths for the S1 devices which is very useful for crossbar array application. (c) The  $\eta$  will change as a function of  $I_{CC}$ . (d) The  $\eta$  and  $\xi$  dependence on  $I_{CC}$ . For higher  $I_{CC}$ , device will show linear nature with higher  $\xi$  and for lower  $I_{CC}$ , device will show nonlinear nature with lower  $\xi$ .

**Fig. 4** (a) Temperature dependent NL behavior. The I-V shows the semiconducting nature of the filament (inset). (b) Luttinger's model of 1D metal fitted well with RRAM devices. The fitting parameters  $\alpha$  and  $\beta$  will depends on T and V at lower voltage and lower temperature, respectively (inset). The input parameters are:  $I_0 = 5 \times 10^{-8}$  Amp, T = 298 K and  $\gamma = 2$ .