# Nanoscale

Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

Cite this: DOI: 10.1039/c0xx00000x

www.rsc.org/xxxxxx

## COMMUNICATION

## Low voltage and high ON/OFF ratio field-effect transistors based on CVD MoS<sub>2</sub> and ultra high-k PZT gate dielectric

Changjian Zhou, ab Xinsheng Wang, Salahuddin Raju, Ziyuan Lin, Daniel Villaroman, Baoling Huang, Helen Lai-Wa Chan, Mansun Chan, and Yang Chai

Received (in XXX, XXX) Xth XXXXXXXXX 20XX, Accepted Xth XXXXXXXX 20XX 10 DOI: 10.1039/b000000x

MoS<sub>2</sub> and other atomic-level thick layered materials have been shown with high potential for outperforming Si transistor at the scaling limit. In this work, we demonstrate a MoS<sub>2</sub> transistor with low voltage and high ON/OFF ratio. A 15 record small equivalent oxide thickness of ~ 1.1 nm has been obtained by using ultra high-k Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> gate dielectric. The low threshold voltage (< 0.5 V) is comparable to that of the liquid/gel gated MoS2 transistor. The small subthreshold swing of 85.9 mV/dec, high on/off ratio of  $\sim 10^8$ 20 and negligible hysteresis ensure a high performance MoS<sub>2</sub> transistor operated at 1V. The extracted field-effect mobility of 1-10 cm<sup>2</sup>/V·s suggests a high crystalline quality of CVDgrown MoS<sub>2</sub> flakes. The combination between twodimensional layered semiconductor and ultra high-k 25 dielectric may enable the development of low-power electronics application.

The advent of various two-dimensional layered materials, including graphene<sup>1</sup> and transition-metal dichalcogenides (TMD), <sup>2</sup> paves the way to miniaturize semiconductor devices down to a 30 truly atomic scale. As a typical member in the TMD family, MoS<sub>2</sub> has been demonstrated for its applications in transistors, photodetecors<sup>5</sup> and integrated circuits (ICs).<sup>6</sup> Unlike the gapless graphene, single-layer MoS<sub>2</sub> has an ultrathin-thickness around 0.7 nm and a direct bandgap of 1.9 eV and lacks of dangling bonds. 35 These characteristics make it quite resistant to short-channel effect and outperform the Si transistor at the scaling limit.<sup>7,8</sup>

As the feature size of IC technology scales downwardly and the density of transistors increases dramatically, the power 40 consumption of the IC continues to go up and becomes the most difficult challenge. Therefore, it is of significant importance to reduce the power consumption without comprising the device performance in other respects. First, the operation voltage V<sub>D</sub> has to be reduced to decrease the dynamic switching power. Second, 45 the off-state leakage current is required to be decreased to minimize the standby power. 9 Ultra high-k dielectrics have to be introduced to realize an equivalent oxide thickness (EOT) of less than 1 nm. However, they still retain a certain off-state leakage

current. 10 Third, it requires a small sub-threshold swing (SS) to 50 turn on the transistor with a low voltage. Fourth, the transistor should exhibit negligible hysteresis for digital computing. Up to now, some efforts have been devoted to this end by using different gate high-k dielectrics such as HfO<sub>2</sub>, 4, 6 Al<sub>2</sub>O<sub>3</sub>, 11 and ion liquid /gel gate. 12, 13 For the high-k dielectrics which are formed 55 by atomic layer deposition (ALD) technique, the absence of dangling bonds makes it very challenging to deposit uniform ultra-thin dielectrics directly on the MoS2 layer. Surface treatment or buffer layer is usually required before the ALD process,  $^{14\text{-}16}$  which degrades the quality of MoS $_2$  and limits the 60 achievable minimum dielectric thickness. Theoretical simulation suggests that a low voltage of 0.5 V could be applied to MoS<sub>2</sub> transistor with ~ 0.5 nm EOT.8 Until now, it has not been demonstrated experimentally vet. The ion liquid/gel gated MoS<sub>2</sub> transistors demonstrate good performance at a low voltage, but 65 this technique is not suitable for small feature size devices and it is also incompatible with standard CMOS processing technology. In this study, we demonstrate field-effect transistors based on CVD synthesized MoS<sub>2</sub> atomic layer and ultra high-k Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> (PZT) gate dielectrics. A low operation voltage  $_{70}$  of less than 1 V and a high ON/OFF ratio of  $\sim 10^8$  have been achieved with the ultra high-k PZT dielectric of 100 nm thickness (~ 1.1 nm EOT).

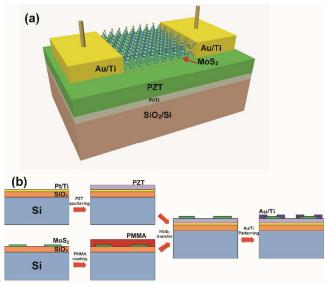

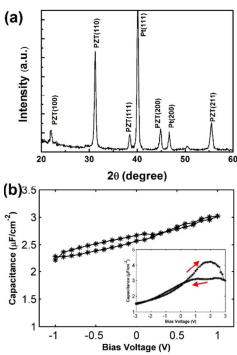

Fig. 1(a) shows the three-dimensional schematic of the PZT 75 gated MoS<sub>2</sub> transistor and Fig. 1(b) illustrates the process flow for fabricating the proposed MoS<sub>2</sub> transistor. For PZT preparation, we started with a 300 nm SiO<sub>2</sub>/ Si wafer, on which a layer of Pt/Ti (100 nm/10 nm) was sputtered as the bottom gate material and also the seed layer for PZT deposition. Then a layer of ~100 80 nm PZT film was prepared by radio frequency sputtering method using a ceramic target. As-prepared PZT was then annealed at 650 °C in N<sub>2</sub>/O<sub>2</sub>=1:1 atmosphere for 1 min by rapid thermal annealing. Fig. 2(a) shows the XRD patterns of the annealed PZT thin film. The film clearly exhibits polycrystalline perovskite 85 structures, with its typical crystal orientation annotated in Fig. 2 (a). Mechanically exfoliated single-layer or few-layer MoS<sub>2</sub> flakes have very limited sizes for practical applications, although

<sup>&</sup>lt;sup>a</sup> Department of Applied Physics, The Hong Kong Polytechnic University, Kowloon, Hong Kong

b Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Kowloon, Hong Kong

c Department of Mechanical and Aerospace Engineering, The Hong Kong University of Science and Technology, Kowloon, Hong Kong

they usually exhibit better crystal quality. Recently, CVD has been largely explored to synthesize large-area, layer-controlled crystalline MoS<sub>2</sub> flakes, <sup>17-24</sup> making MoS<sub>2</sub> a promising semiconducting channel material for the field-effect transistors to s extend CMOS to the end of the roadmap. In this work, singlelayer MoS<sub>2</sub> was grown by direct vapor phase reaction method using a setup similar to that reported in Ref 21. The synthesized MoS<sub>2</sub> flakes were transferred onto PZT substrate by conventional PMMA-mediated method. The source/drain electrodes were 10 patterned onto the final substrate using conventional photolithography followed by Au/Ti (100 nm/ 10 nm) evaporation and lift-off processes. Fig. S1 shows one typical device after the electrode formation.

Fig. 1 (a) Schematic structure of the PZT gated MoS<sub>2</sub> transistor (not to scale); (b) Process flow for fabricating the proposed MoS<sub>2</sub> transistors.

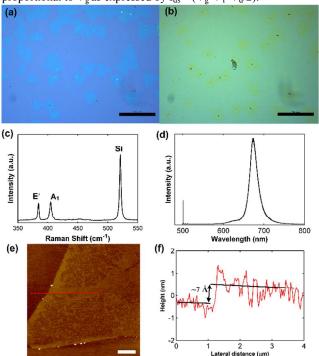

Fig. 3(a) and Fig. 3(b) show typical optical images of the 20 transferred MoS<sub>2</sub> flakes on the SiO<sub>2</sub> and PZT substrate, respectively. The triangular shape of the MoS<sub>2</sub> flakes can be clearly identified in Fig. 3 (a), while it is not so apparent in Fig. 3(b) due to the poor optical contrast of the PZT substrate. The typical size of the MoS<sub>2</sub> flakes is  $\sim 20 \mu m$ , measured as the side 25 length of the triangular (See also Fig. S1). It is shown that these triangular flakes could merge into a single flake or even a continuous film if the growth time is long enough, as also reported in Ref. 21. Raman spectrum of the MoS<sub>2</sub> flake is presented in Fig. 3(c). There are two active Raman modes, with 30 their peak frequencies located at 384.7 cm<sup>-1</sup> and 404.6 cm<sup>-1</sup>, respectively. The E' mode results from the in-plane vibration of the two S atoms with respect to the Mo atom and the A<sub>1</sub> mode results from the out-of-plane vibration of the two S atoms in opposite directions. The difference between the two peak 35 frequencies is used as a convenient indicator to determine the layers of the MoS<sub>2</sub> sample. <sup>25, 26</sup> In this work, the peak difference is usually less than 20 cm $^{-1}$ , suggesting that the synthesized MoS $_2$  flakes are monolayers. $^{20,\ 25}$  The full width at half maximum (FWHM) of the peak is ~ 3 cm<sup>-1</sup>, which is comparable with the 40 mechanical exfoliated monolayer MoS2, indicating a high crystalline quality of the synthesized sample.<sup>20</sup> The photoluminescence (PL) spectra show two peaks at ~625 nm

(1.98 eV) and 673 nm (1.84 eV), corresponding to the B1 and A1 direct excitonic transition, respectively. The prominent intensity 45 of A1 peak is attributed to the gap transition at the K point of the Brillouin zone in monolayer MoS<sub>2</sub>. <sup>27</sup> The thickness of the MoS<sub>2</sub> flake is about 7 Å as measured by atomic force microscopy (Fig. 3(e) and (f)), also confirming its single-layer characteristic.

Fig. 2 (a) X-ray diffraction spectrum of the annealed PZT thin film. (b) Capacitance-voltage characteristic of the PZT thin film. Inset shows the measurement results under a larger sweeping voltage (3V) and the arrows indicate the sweeping directions.

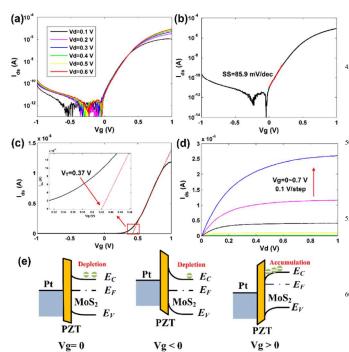

With the relatively large area of transferred MoS<sub>2</sub> flakes, it is quite convenient to fabricate multiple devices without resorting to the costly electron beam lithography. In this work, we have successfully fabricated MoS<sub>2</sub> transistors with channel lengths 60 ranging from 1.5 μm to 4 μm. The current-voltage characteristics were measured by B1500 system under vacuum ambient (pressure lower than 10<sup>-6</sup> Torr) using a Lakeshore TTPX cryogenic probe station. Fig. 4(a) presents the transfer characteristic of a transistor with 1.5 µm channel length and 65 nominal 20 µm channel width. The device shows clearly switching characteristics in the scanned gate voltage range of -1 V to 1V under various drain-source voltages (V<sub>d</sub>). The low voltage characteristic is attributed to the small EOT (~ 1 nm).

Fig. 4(b) illustrates the transfer characteristic of the transistor under V<sub>d</sub>=0.6 V. The inverse slope of the red straight line in Fig. 4(b) represents the SS of the device. A small SS of 85.9 mV/dec is obtained, which is comparable to recently reported top-gate or dual-gate MoS<sub>2</sub> transistors<sup>4, 11</sup> based on ALD high-k dielectrics <sub>75</sub> and mechanically exfoliated MoS<sub>2</sub> flakes. It is shown in Fig. 4(b) that the OFF-state current near V<sub>g</sub>=0 V is less than 10<sup>-13</sup> A and the on current is  $\sim 10^{-5}$  A. Thus a high ON/OFF ratio of  $\sim 10^{8}$  is achieved, which is also comparable to the best results reported for mechanically exfoliated devices. We have used the extrapolation so in the linear region method to extract the threshold voltage  $(V_T)^{28}$

In the linear region, the channel current I<sub>ds</sub> is in linear proportional to  $V_g$  as expressed by  $I_{ds} \propto (V_g - V_T - V_d/2)$ .

Fig. 3 Optical image of the transferred MoS<sub>2</sub> flakes onto (a) SiO<sub>2</sub>/Si 5 substrate and (b) PZT substrate; Scale bars 50 μm for (a) and (b). (c) Typical Raman spectrum of the synthesized MoS<sub>2</sub> flake. E' and A<sub>1</sub> denote the in-plane and out-of-plane vibration modes of the sulfur atoms. (d) Photoluminescence spectrum of the MoS<sub>2</sub> flake. The laser wavelength for Raman and PL measurement is 488 nm. (e) Atomic force microscope 10 image of a MoS<sub>2</sub> flake on the SiO<sub>2</sub> substrate, scale bar 1μm. (f) Crosssection plot of the MoS<sub>2</sub> flake along the red dashed line in (e).

By finding the V<sub>g</sub> axis intercept of the linear extrapolation of the  $I_{ds}$ - $V_g$  curve at the maximum slope point, and the value of  $V_T$  $_{\mbox{\scriptsize 15}}$  is calculated by subtracting  $V_{\mbox{\scriptsize d}}/2$  from the intercept value. For this device, the V<sub>T</sub> is about 0.37 V, as indicated in Fig. 4 (c). It is noticed that the slope (transconductance) starts decrease toward saturation at a low drain bias of 0.1 V, as shown in Fig. 4(c). While this saturation phenomena are not observed when the drain 20 bias is slightly larger, the velocity saturation effect could be excluded as a contribution. Considering the relatively large asobtained contact resistances at the source/drain terminals and the well-studied crowding effect in kinds of thin film transistors, it is most likely that the slope saturation is due to the low bias current 25 crowding effect Fig. 4 (d) shows the output characteristics of the device. The drain-source current I<sub>ds</sub> exhibits clearly saturation behavior at a low drain voltage, suggesting the good control of the carrier transport by the gate voltage. It is noteworthy that the present device is a normally-off n-channel transistor. As a 30 switching device, normally-off behavior is desirable for lowpower electronics. However, this behavior was not observed for many reported MoS<sub>2</sub> transistors. 4, 6, 11, 18, 21 In the present study, the Pt gate has a higher work function  $(\Phi_m)$  than Ti, Cr and Al which were used as the adhesive layer in direct contact with the 35 gate dielectrics. We explain the observed normally-off behavior in terms of energy band diagrams. The single-layer MoS2 has a bandgap of 1.84 eV, as suggested by the PL measurement, and the work function ( $\Phi_{MoS2}$ ) is assumed as ~ 4.9 eV and the electron

affinity is 4 eV.29 Assuming the bulk value of the work function 40 for the bottom gate ( $\Phi_m$ =5.6 eV), the band diagram at equilibrium suggests the carrier depletion at zero gate bias, as shown in Fig. 4(e). Thus the device is maintained at OFF state at zero gate bias and negative gate bias. When the applied positive gate voltage increases, the MoS<sub>2</sub> band diagram will evolves from the depletion 45 region to the accumulation region and the device is biased at ON state. Similarly, it is reported that a bilayer MoS<sub>2</sub> transistor could be changed from depletion mode to enhance mode by replacing the Al gate with Pd gate. 6

The field-effect mobility is derived using the expression  $\mu$ =  $[\Delta I_{ds}/\Delta V_g] \times [L/(WC_iV_d)]$ , where L and W are the channel length and width, respectively, and  $C_i$  is the capacitance per area. We made a test structure of metal-PZT-metal capacitor to measure  $C_i$ . Unlike commonly used dielectrics such as SiO<sub>2</sub> or HfO<sub>2</sub>, the PZT 55 dielectric shows clearly voltage-dependent capacitances, as shown in Fig. 2(b). The relative dielectric constant of the PZT dielectric is calculated to be in the range of 250-350, with the maximum value obtained under the largest positive voltage bias. The mobility of the MoS<sub>2</sub> transistor is around 1.39-1.88 cm<sup>2</sup>/V·s, 60 estimated using the maximum and minimum capacitance, respectively. Using the same method, we have calculated the mobility for multiple devices on the same substrate. Fig. S2-S4 present the transfer characteristics with different channel dimensions, in which a high mobility of 10.01 is achieved for a 65 device with 2 µm channel length (Fig. S2). Generally, the mobility is in the range of 1-10 cm<sup>2</sup>/V·s and the threshold voltage is about 0.2-0.4 V. These results suggest the high quality of the CVD MoS<sub>2</sub> flakes and the applicability of the proposed PZT dielectric MoS<sub>2</sub> transistors for low voltage electronics. 70 Considering the device working at 1 V bias, a dielectric constant of  $\sim$ 350 is obtained and the EOT is  $\sim$  1.1 nm. This EOT is the smallest value among the MoS2 transistors in the existing literatures. This level of low voltage operation has only been reported in ion liquid/gel gated MoS<sub>2</sub> transistors.

It is well known that the interdiffusion between silicon and PZT constrains the reliability of PZT ferroelectric transistor. The interdiffusion happens because the PZT is deposited on the Si substrate and the Pb diffuses into the silicon at a high temperature which is used for crystallization of the PZT. In this study, the 80 MoS<sub>2</sub> flakes were transferred onto the polycrystalline PZT film and no high-temperature processes were used after the transfer process. This is in distinct to the interface of the traditional structure consisting of PZT and bulk semiconductor material. The interface trap density could be evaluated using the equation: The 85 interface trap density could be evaluated using the equation:

$$D_{it} = \frac{c_i}{a^2} \left( \frac{q \cdot SS}{KT \ln 10} - 1 \right) \tag{1}$$

$D_{it} = \frac{c_i}{q^2} \left( \frac{q \cdot SS}{KT \ln 10} - 1 \right)$  (1) Using the measured data of  $C_i$  (2.2 ~ 3  $\mu$ F/cm<sup>2</sup>) and SS (85.9 mV/dec), the trap density at room temperature (T=300 K) is estimated as  $6.3 \sim 8.6 \times 10^{12} / \text{cm}^2 \cdot \text{eV}$ . The interface traps 90 between atomic-level-thick semiconductor and substrate is a common problem for the 2D based electronics. These interface traps are possibly resulted from the transfer process of 2D layered materials or the atomic-level roughness of the substrate. To further improve the interface, researchers have developed new 95 transfer process like dry-transfer process to avoid the potential chemical contamination during the PMMA-mitigated transfer

process

Fig. 4 Electrical characteristics of the PZT gated MoS2 transistors with 5 1.5 μm channel length and 20 μm nominal channel width. (a) Transfer characteristics of the MoS<sub>2</sub> transistors with various V<sub>d</sub> ranging from 0.1 V to 0.6 V. (b) Extraction of the subthreshold swing (SS) from the transfer characteristics at V<sub>d</sub>=0.6 V, the SS is about 85.9 mV/dec for this device. (c) Extrapolation method to obtain the threshold voltage, which is 0.37 V. (d) 10 Output characteristics of the MoS2 transistor. The device shows good saturation properties. (e) Energy-band diagrams for the Pt/PZT/MoS<sub>2</sub> structures under different bias.

It is known that PZT thin film has been widely studied for the 15 applications, including ferroelectric memory, 30 micromechanical systems<sup>31</sup> and high-density integrated capacitors.<sup>32</sup> The ferroelectric hysteresis of the PZT thin film with ~ 100 nm thickness appears when a large sweeping voltage (3 V) is used (See inset of Fig 2(b)), indicating the relatively large coercive 20 field of the PZT film. It is well known that the coercive field of ferroelectric thin film with 100 nm thickness is much larger than that in micrometer range. 30 If we consider the inactive layer near the electrode interface, this value could be even larger. For the present PZT thin film, the coercive field is larger than  $10^7 \text{ V/m}$ . 25 Also, it shows asymmetric gating effect which is mainly due to the difference of the top electrode (Au/Ti) and bottom electrode (Pt/Ti) in terms of material and also thermal processing, because the bottom electrode endured a high temperature process when the PZT was annealed. While sweeping with a large voltage can 30 induce the ferroelectric memory effect, the gate current is relatively larger especially when the gate is biased at a large positive voltage. With a smaller sweeping range, PZT can be regarded as a dielectric material with a limited hysteresis and an ultra-high dielectric constant. In this study, we conducted the gate 35 voltage sweep within 1 V, thus both the leakage current and the capacitance hysteresis has been reduced.

Fig. 5(a) shows the hysteresis behavior of the transfer characteristics. For normally operational PZT gated MoS<sub>2</sub> 40 transistors, the hysteresis is  $\sim 0.01$  V, which is only 1% of the sweeping range. The performance is very remarkable considering the usually reported large hysteresis in MoS<sub>2</sub> transistors even with dielectric encapsulation process.<sup>33</sup> Since the measurement is conducted in vacuum, we can exclude the effect due to the 45 absorption of the oxygen/water molecules. There are two origins of the hysteresis. First, the defects of the MoS<sub>2</sub> formed during the growth or the transfer process can give rise to a large hysteresis. We fabricated and measured the MoS<sub>2</sub> transistor using the 300 nm SiO<sub>2</sub> as the gate dielectric. The device also shows very small 50 hysteresis (See Fig. S5, S6). This suggests that the MoS<sub>2</sub> itself has very limited defects density. Second, as a typical oxide ferroelectric material, the polycrystalline PZT is usually oxygen deficient.<sup>30</sup> In the regions near the interface, there are more oxygen deficiencies than in the bulk. Oxygen vacancies act as 55 electron traps when the MoS<sub>2</sub> is biased at a positive voltage, thus induces the clockwise hysteresis of the transfer curves. Furthermore, we have characterized the device under a low temperature of 150 K. The MoS<sub>2</sub> transistor shows hysteresis-free transfer characteristics, as indicated in Fig. 5(b). The resultant 60 hysteresis-free behavior suggests that highly mobile oxygen vacancies don't come into play at a low temperature and the density of the surface traps is very small at room temperature.

65 Fig. 5 Hysteresis characteristics of the MoS<sub>2</sub> transistors measured at (a) 300 K and (b) 150 K. The dashed lines show the backward sweeping results and the inset shows the magnified figure of the right part indicated by the red arrow.

In summary, we presented the MoS<sub>2</sub> transistors with a low  $_{70}$  voltage of 1 V and a high on/off ratio of  $\sim 10^8$  by combing the ultra high-k PZT dielectric and CVD MoS<sub>2</sub> flakes. The features of the low threshold voltage (< 0.5 V), small SS (85.9 mV/dec), and the normally-off characteristic suggest the high potential of the proposed device for low power digital circuit applications. The 75 small hysteresis indicates the high quality of the CVD synthesized MoS<sub>2</sub> flakes and the clean interface between the  $MoS_2$  and PZT. The record small EOT obtained with  $\sim 100$  nm PZT could be scaled down for even smaller voltage operation,

24.

75 25.

26

28.

85 29.

32.

33.

either by decreasing the PZT thickness or increasing the dielectric constant with the optimization of the PZT deposition process.

#### Acknowledgements

We acknowledge financial support from the Hong Kong 5 Research Grant Council (grant number: PolyU 252001/14E), the Hong Kong Polytechnic University (grant numbers: 1-ZVCG, G-UC72) and AOE under Grant AOE/P-04/08-1.

#### References

- F. Schwierz, Nature nanotechnology, 2010, 5, 487-496.

- 10 2. Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman and M. S. Strano, Nature nanotechnology, 2012, 7, 699-712.

- A. C. Ferrari, F. Bonaccorso, V. Falko, K. S. Novoselov, S. 3. Roche, P. Bøggild, S. Borini, F. Koppens, V. Palermo, N. Pugno, J. A. Garrido, R. Sordan, A. Bianco, L. Ballerini, M. Prato, E. Lidorikis, J. Kivioja, C. Marinelli, T. Ryhänen, A. 15 Morpurgo, J. N. Coleman, V. Nicolosi, L. Colombo, A. Fert, M.

- Garcia-Hernandez, A. Bachtold, G. F. Schneider, F. Guinea, C. Dekker, M. Barbone, C. Galiotis, A. Grigorenko, G. Konstantatos, A. Kis, M. Katsnelson, C. W. J. Beenakker, L. Vandersypen, A. Loiseau, V. Morandi, D. Neumaier, E. Treossi, 20

- V. Pellegrini, M. Polini, A. Tredicucci, G. M. Williams, B. H. Hong, J. H. Ahn, J. M. Kim, H. Zirath, B. J. van Wees, H. van der Zant, L. Occhipinti, A. Di Matteo, I. A. Kinloch, T. Seyller, E. Quesnel, X. Feng, K. Teo, N. Rupesinghe, P. Hakonen, S. R. T. Neil, Q. Tannock, T. Löfwander and J. Kinaret, Nanoscale, 2014, DOI: 10.1039/c4nr01600a.

- 4. B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti and A. Kis, Nature nanotechnology, 2011, 6, 147-150.

- 5. O. Lopez-Sanchez, D. Lembke, M. Kayci, A. Radenovic and A. Kis, Nature nanotechnology, 2013, 8, 497-501.

- 6. H. Wang, L. Yu, Y. H. Lee, Y. Shi, A. Hsu, M. L. Chin, L. J. Li, M. Dubey, J. Kong and T. Palacios, Nano letters, 2012, 12, 4674-4680.

- 7. K. F. Mak, C. Lee, J. Hone, J. Shan and T. F. Heinz, Physical Review Letters, 2010, 105.

- 8. Y. Yoon, K. Ganapathi and S. Salahuddin, Nano letters, 2011, 11, 3768-3773.

- 9. C. H. Cheng and A. Chin, IEEE Electron Device Letters, 2014, 35, 274-276.

- 40 10. The International Technology Roadmap for Semiconductors, http://www.itrs.net/Links/2013ITRS/2013Chapters/2013ERM Summary.pdf.

- H. Liu and P. D. Ye, IEEE Electron Device Letters, 2012, 33, 11. 546-548

- 45 12. Y. Zhang, J. Ye, Y. Matsuhashi and Y. Iwasa, Nano letters, 2012, 12, 1136-1140.

- J. Pu, Y. Yomogida, K. K. Liu, L. J. Li, Y. Iwasa and T. 13. Takenobu, Nano letters, 2012, 12, 4013-4017.

- 14. S. Son, S. Yu, M. Choi, D. Kim and C. Choi, Applied Physics Letters, 2015, 106, 021601.

- X. Zou, J. Wang, C. H. Chiu, Y. Wu, X. Xiao, C. Jiang, W. W. 15. Wu, L. Mai, T. Chen, J. Li, J. C. Ho and L. Liao, Advanced

- materials, 2014, 26, 6255-6261. L. Cheng, X. Qin, A. T. Lucero, A. Azcatl, J. Huang, R. M. 16. Wallace, K. Cho and J. Kim, ACS applied materials &

- interfaces, 2014, 6, 11834-11838. Y. H. Lee, X. Q. Zhang, W. Zhang, M. T. Chang, C. T. Lin, K. 17. D. Chang, Y. C. Yu, J. T. Wang, C. S. Chang, L. J. Li and T. W. Lin, Advanced materials, 2012, 24, 2320-2325.

- 60 18. X. Wang, H. Feng, Y. Wu and L. Jiao, Journal of the American Chemical Society, 2013, 135, 5304-5307.

- 19. Y. Zhan, Z. Liu, S. Najmaei, P. M. Ajayan and J. Lou, Small, 2012, 8, 966-971.

- 20. Y. Yu, C. Li, Y. Liu, L. Su, Y. Zhang and L. Cao, Scientific reports, 2013, 3, 1866.

- A. M. van der Zande, P. Y. Huang, D. A. Chenet, T. C. 21. Berkelbach, Y. You, G. H. Lee, T. F. Heinz, D. R. Reichman, D.

- A. Muller and J. C. Hone, Nature materials, 2013, 12, 554-561. 22. Z. Jin, S. Shin, H. Kwon do, S. J. Han and Y. S. Min, Nanoscale, 2014, 6, 14453-14458.

- 23. L. K. Tan, B. Liu, J. H. Teng, S. Guo, H. Y. Low and K. P. Loh, Nanoscale, 2014, 6, 10584-10588.

- Y. Shi, H. Li and L. J. Li, Chemical Society reviews, 2014, DOI: 10.1039/c4cs00256c.

- C. Lee, H. Yan, L. E. Brus, T. F. Heinz, J. Hone and S. Ryu, ACS nano, 2010, 4, 2695-2700.

- H. Li, Q. Zhang, C. C. R. Yap, B. K. Tay, T. H. T. Edwin, A. Olivier and D. Baillargeat, Advanced Functional Materials, 2012, 22, 1385-1390.

- 80 27. A. Splendiani, L. Sun, Y. Zhang, T. Li, J. Kim, C. Y. Chim, G. Galli and F. Wang, Nano letters, 2010, 10, 1271-1275.

- A. Ortiz-Conde, F. J. García Sánchez, J. J. Liou, A. Cerdeira, M. Estrada and Y. Yue, Microelectronics Reliability, 2002, 42, 583-596.

- S. Das, H. Y. Chen, A. V. Penumatcha and J. Appenzeller, Nano letters, 2013, 13, 100-105.

- 30. M. Dawber, K. M. Rabe and J. F. Scott, Reviews of Modern Physics, 2005, 77, 1083-1130.

- C. R. Bowen, H. A. Kim, P. M. Weaver and S. Dunn, Energy 31. & Environmental Science, 2014, 7, 25.

- A. Roest, R. Mauczok, K. Reimann, L. van Leuken-Peters and M. Klee, IEEE transactions on ultrasonics, ferroelectrics, and frequency control, 2009, 56, 425-428.

- D. J. Late, B. Liu, H. S. Matte, V. P. Dravid and C. N. Rao, ACS nano, 2012, 6, 5635-5641.