# Journal of Materials Chemistry C

Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

www.rsc.org/materialsC

### Journal Name

#### ARTICLE

## Flash memory based on solution processed hafnium dioxide charge trapping layer

Jiaqing Zhuang,<sup>a</sup> Su-Ting Han,<sup>a</sup> Ye Zhou,<sup>a</sup> and V. A. L. Roy <sup>\*ab</sup>

Received 00th January 2014, Accepted 00th January 2014

Cite this: DOI: 10.1039/x0xx00000x

DOI: 10.1039/x0xx00000x

www.rsc.org/

Hafnium dioxide (HfO<sub>2</sub>) film prepared by sol-gel technique has been used as a charge trapping layer in organic flash memory. The thickness, crystallinity and morphology of HfO<sub>2</sub> fabricated by various conditions were investigated. X-ray diffraction (XRD) patterns indicated the formation of monoclinic HfO<sub>2</sub> crystals with increasing annealing temperature. Atomic force microscope (AFM) images showed relatively smooth films of HfO<sub>2</sub> growth. The annealing temperature dependent effects on the memory window as well as data retention properties have been discussed. A large memory window and long data retention time have been achieved for the pentacene based flash memory. The results demonstrate that solution proceed HfO<sub>2</sub> film could be a promising candidate as charge trapping layer in printable flash memory.

#### 1. Introduction

Recently, flash memories have attracted great attention as they have considerable share in the non-volatile semiconductor memory market.<sup>1-7</sup> Flash memory is an electronic device used for data storage with non-volatile property which can be electrically programmed and erased. Tremendous efforts have been focused on the development of flash memory for portable electronic devices, smart television, radio frequency identification (RFID) tags and so on.<sup>8-21</sup> Flash memory is the leading product in the market of non-volatile semiconductor memory with more strict requirements as the microelectronic technology advances where the data storage and density requirements increase dramatically. Traditional flash memory based on the concept of floating gate has the drawback that unexpected conduction between the floating gate and channel may occur and all the charges may be drained off as the floating gate is a conductor.

To solve these problems, flash memory was proposed by using insulating materials as the charge trapping elements.<sup>22-25</sup> Recently, various dielectric materials with high dielectric constant have been employed as charge trapping materials to improve the operating speed and get better charge retention ability. For examples, TiO<sub>2</sub>, <sup>26, 27</sup> Si<sub>3</sub>N<sub>4</sub>, <sup>23, 24, 28, 29</sup> and HfO<sub>2</sub> <sup>22-25, 30, 31</sup> have been studied in previous reports. In addition, numerous methods have been developed to prepare these insulator films. Among them, HfO<sub>2</sub> has been widely used as it has a higher charge trapping density and can be prepared by various techniques such as chemical vapor deposition (CVD),<sup>24, 25</sup> physical vapor deposition (PVD),<sup>32</sup> and atomic layer deposition (ALD).<sup>22, 23, 33</sup> Although the HfO<sub>2</sub> can be deposited using alternative methods such as ALD, CVD, or PVD, the

complicated instruments and procedures restrain their practical application. Further, the solution processed  $HfO_2$  shows great potential in large area production, which can be printed through roll-to-roll process. To reduce the cost on the fabrication procedure, solution process method has been proposed to fabricate the  $HfO_2$  film.<sup>30, 34</sup> For the first time, we demonstrate an organic flash memory based on solution processed  $HfO_2$ . Therefore, it is necessary to investigate the charge trapping property of solution processed  $HfO_2$  and the influences on the memory effect.

Here, we report a novel organic flash memory based on solgel processed  $HfO_2$ . Memory devices were fabricated with solgel processed  $HfO_2$  as floating gate and their respective memory properties were analyzed. In addition, the effects of annealing temperature and thickness of  $HfO_2$  film on the memory properties have been studied. Pentacene was used as the organic semiconductor due to its high mobility and stable electrical performance.<sup>34-38</sup> The thickness of  $HfO_2$  film decreases with increasing spin-coating speed or annealing temperature. We systematically studied the program/erase behavior for the fabricated devices. A memory window of 41.10 V was obtained with the data retention time of more than  $10^5$  s. These results indicate that the solution processed  $HfO_2$ could be an excellent candidate for printable memory devices.

#### 2. Experimental

#### 2.1. Materials

Hafnium (IV) chloride (HfCl<sub>4</sub>, 98%) and pentacene (sublimated grade) were purchased from Aldrich. All chemicals and solvents were used without further purification. The highly

doped Si wafer with 300 nm  $SiO_2$  was cleaned using standard for further use. method and then transferred into the glove box filled with  $N_2$

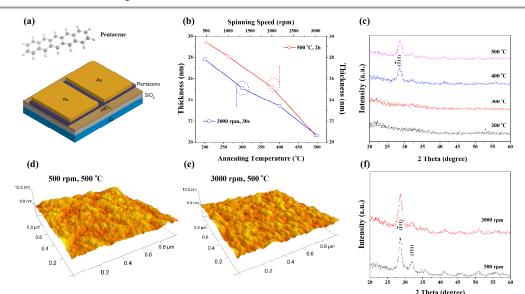

**Fig. 1** (a) Schematic of the HfO<sub>2</sub> based flash memory device architecture, structures of pentacene and HfO<sub>2</sub> in this study; (b) Theta (degree) thickness of HfO<sub>2</sub> films prepared at various spinning speed or annealing temperature; (c) XRD patterns of HfO<sub>2</sub> films spin-coated at 3000 rpm for 30 s and annealed at 200, 300, 400 and 500 °C for 2 h; AFM images of HfO<sub>2</sub> film spin-coated at the speed of (d) 500 rpm and (e) 3000 rpm for 30 s and annealed at 500 °C for 2 h. (f) XRD patterns of HfO<sub>2</sub> films spin-coated at the speed of 500 rpm and (c) 3000 rpm for 30 s and annealed at 500 °C for 2 h.

#### 2.2. Preparation of HfO<sub>2</sub> precursor

The starting materials, HfCl<sub>4</sub>, C<sub>2</sub>H<sub>5</sub>OH, HNO<sub>3</sub> and H<sub>2</sub>O were weighed according to the stoichiometric ratio of HfCl<sub>4</sub>:C<sub>2</sub>H<sub>5</sub>OH:HNO<sub>3</sub>:H<sub>2</sub>O = 1:410:5:5. The solution of HfO<sub>2</sub> precursor was prepared by mixing the HfCl<sub>4</sub> and C<sub>2</sub>H<sub>5</sub>OH under nitrogen atmosphere and followed by mixing with distilled water and HNO<sub>3</sub>. Then, to promote the hydrolysis and polymerization of the HfO<sub>x</sub> sol-gel, the solution was filtered using a 0.2 µm PTFE filter and heated at 50 °C for 3 h.<sup>34</sup>

The HfO<sub>2</sub> film was prepared by spin-coating the HfO<sub>2</sub> solgel. To study the thickness dependent effects, the HfO<sub>2</sub> film on the cleaned substrate was obtained by spin-coating at different speed from 500 to 3000 rpm for 30 s, and followed by annealing at 500 °C for 2 h. Another set of HfO<sub>2</sub> films were prepared to investigate the temperature dependent effects using the same spinning speed of 3000 rpm for 30 s but different annealing temperature from 200 °C to 500 °C.

#### 2.3. Device fabrication

The device architecture in this study is given in Fig. 1a. Top contact geometry was used in our memory devices. In a typical fabrication process, the  $HfO_2$  was prepared by spin-coating its precursor on the cleaned heavily-doped p-type Si with a 300 nm native SiO<sub>2</sub> layer. For our device and silicon-oxide-nitride-oxide-silicon (SONOS) type memories, the  $HfO_2$  and  $Si_3N_4$  are used as charge trapping layers respectively. The  $HfO_2$  functionalized as both tunneling and charge storage layer in this study while the SONOS have separated layers with SiO<sub>2</sub> and  $Si_3N_4$  as the tunneling and charge storage layers respectively. For the consideration of simplicity, the device structure is

shown in Fig 1a. The p-type Si acts as the control gate while SiO<sub>2</sub> layer serves as the blocking dielectric layer. A 40 nm pentacene, an organic compound with five fused benzene rings as shown on the top left of Fig 1a, was thermally deposited as a p-type semiconducting layer at a rate of 0.1-0.2 Å's<sup>-1</sup>. Gold electrodes were then thermally evaporated through a shadow mask at a rate of 0.1 Å's<sup>-1</sup>, with a channel length of 30  $\mu$ m and width of 1000  $\mu$ m. Gold was chosen as the source and drain contacts due to its high work function which is beneficial for hole injection and transportation.<sup>35</sup>

#### 2.4. Characterization

The thickness of HfO<sub>2</sub> films were characterized by the ellipsometer (Rudolph Research Auto/EL). Grazing incidence X-ray diffraction (GIXRD) patterns of the deposited films were recorded using a Philips X'Pert X-ray diffractometer using Cu K $\alpha$  radiation ( $\lambda = 1.5406$  Å). The film morphology was investigated by atomic force microscope (AFM, Veeco Multimode V) through tapping mode. The electrical characterization of the memory devices has been measured by a Keithley 2612 source meter in a glove box filled with N<sub>2</sub> at room temperature.

#### 3. Results and discussion

In this work, the thickness, phase information as well as morphology of the  $HfO_2$  charge trapping layer were studied in detail as these properties have significant effects on the device performance.

To investigate the effects of crystallinity and thickness of  $HfO_2$  charge trapping layer on the performance of memory device, structure shown in Fig. 1a, two set of  $HfO_2$  films were

Journal Name

ARTICLE

prepared via spin-coating at various speed and then annealed at various temperatures. Fig. 1b presents the variation of thickness of HfO<sub>2</sub> films obtained at different conditions. Set 1 (blue line) indicates films prepared at a same spinning speed of 3000 rpm with different annealing temperature from 200 to 500 °C, and set 2 (red line) indicates films prepared at an annealing temperature of 500 °C with different spinning speed from 500 to 3000 rpm, respectively. For set 1, the thickness of HfO<sub>2</sub> films decreases from around 28 to 21 nm as the temperature reduces. Further, for set 2, the thickness of HfO<sub>2</sub> films decreases from around 29 to 21 nm. These results show that more crystals are formed with well intact crystalline grains at higher annealing temperature for set 1. Meanwhile, larger centrifugal and air shear force led to the formation of thinner precursor layers at faster speed for set 2.

Fig. 1c shows the XRD pattern of  $HfO_2$  films of set 1 with preparation conditions shown in section 2.2. As can be seen from the figure, no obvious diffraction peaks can be found for

the films prepared at 200 or 300 °C as the temperature is too low to form crystalline HfO<sub>2</sub>. As shown in Fig. 1e and Fig. 1f, two typical diffraction peaks around 28.2° ( $\overline{111}$ ) and 31.6° (111) ascribed to monoclinic phase<sup>39, 40</sup> could be found when the temperature increases up to 400 °C. The structure of monoclinic HfO<sub>2</sub> is given on the top right of Fig. 1a. There is no significant enhancement in the peak density and well agreement with the results reported by Wang *et al.*<sup>39</sup>. Therefore, the maximum temperature was fixed at 500 °C in this study.

We further examined the morphology of the spin-coated HfO<sub>2</sub> films. Fig. 1d and Fig. 1e present the AFM images of HfO<sub>2</sub> films spin-coated at speed of 500 rpm and 3000 rpm followed by annealing at 500 °C. The scanned area is 1  $\mu$ m × 1  $\mu$ m. From Fig. 1d and Fig. 1e, no obvious defects and no remarkable differences could be found. Further, the root mean square (rms) is found to be 0.559 nm and 0.620 nm for the films shown in Fig. 1d and Fig. 1e, respectively.

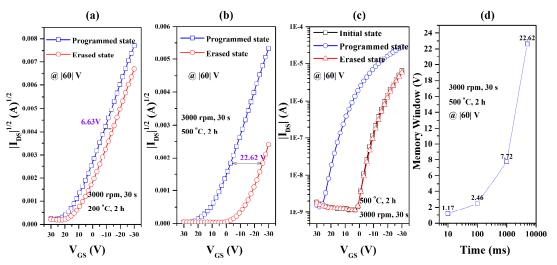

**Fig. 2** Transfer characteristic of memory devices with  $HfO_2$  spin-coated at 3000 rpm and annealed at (a) 200 °C and (b) (c) 500 °C, the program and erase voltage are +60 V and -60 V for 5 s, and (d) the relationship of program/erase time and the memory window of the device with  $HfO_2$  spin-coated at 3000 rpm and annealed at 500 °C.

We first investigated the effect of annealing temperature on HfO<sub>2</sub> film for memory devices. The memory transistors with HfO2 annealed at 200 °C and 500 °C were fabricated and transfer characteristics of these two memory devices are shown in Fig. 2a and Fig. 2b. The programming and erasing bias pulses were set at +60 V/-60 V for 5 s. A significant shift of the threshold voltage (V<sub>T</sub>), which is determined from the intercept of the plot of  $|I_{DS}|^{1/2}$  versus the gate-source voltage (V<sub>GS</sub>), can be observed after applying the positive gate pulse. The memory window,  $\Delta V_T$ , is defined as the change of  $V_T$  in program/erase operations. As shown in Fig. 2a and Fig. 2b, a larger memory window of 22.62 V is obtained for device with HfO<sub>2</sub> prepared at higher temperature. Furthermore, as shown in Fig. 2c, it is found that the transfer curve shifts towards negative voltage direction when a positive voltage is applied on the gate electrode, which proves that HfO2 act as trapping element of electrons. Saturation mobility is determined from the slope of transfer characteristics  $|I_{DS}|^{1/2}$  versus  $V_{GS}$  at drain-source voltage  $(V_{DS}) = -30$  V by using the equation,  $I_{DS} = (WC_{OX}/2L)\mu(V_{GS} - V_T)^2$ . For the memory device at initial state, the transistor has a carrier mobility ( $\mu$ ) of ~1.02 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, a threshold voltage ( $V_T$ ) of 12.11 V and an ON/OFF current ratio of over ~10<sup>3</sup>, as shown in Fig 2c.

In addition, we tested the effect of spinning speed on the memory window of devices fabricated via spinning speed ranging from 500, 1000, 2000, to 3000 rpm. The values of memory window were determined to be 5.29 V, 8.18 V, 11.15 V and 22.62 V as shown in Fig. S1, which proves that thinner HfO<sub>2</sub> film traps charges efficiently in comparison with thicker films. The results revealed that the thickness of HfO<sub>2</sub>, which was confirmed in Fig. 1b, has to be optimized to obtain superior memory characteristics. We proposed that the electric field is larger for thinner HfO<sub>2</sub> layer so that the electrons are easily injected in or pulled out during programming or erasing

Page 4 of 6

operation. Therefore, thinner HfO<sub>2</sub> film obtained through either increasing the spinning speed or annealing temperature would lead to the enhancement of its charge trapping ability.

The relationship between memory window and operation time for the devices based on  $HfO_2$  which was spin-coated at 3000 rpm and annealed at 500 °C was demonstrated in Fig. 2d. The memory window shifts from 1.17 V, 2.46 V, 7.72 V to 22.62 V as the programming/erasing time increases. The results show that the current memory device can be operated within a

short time effectively and larger memory window can be achieved by extending the duration. In comparison with previous reports, utilizing  $HfO_2$  nanoparticles as charge trapping layer, the devices found to operate faster.<sup>31</sup> Besides, the device based on  $HfO_2$  with lower annealing temperature (100 °C) has been demonstrated in Fig. S2. Furthermore, we fabricated a low temperature solution processed  $HfO_2$  layer on a thin  $Al_2O_3$  blocking dielectric layer and the operating voltage are reduced to +5/-5 V, as presented in Fig. S3.

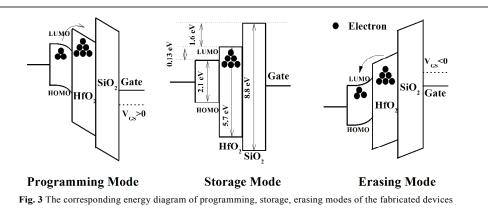

Fig. 3 shows the schematic energy diagram for the device in programming, storage as well as the erasing modes.<sup>35</sup> According to the shift direction of the transfer curves, the  $HfO_2$  acts as an electron trapping element from the lowest unoccupied molecular orbitals (LUMO) of pentacene during programming operation when a positive voltage is applied to

the gate. After programming, the electrons will be kept in the trapping sites of  $HfO_2$  and flow back to the LUMO if a negative voltage is applied to the gate. In addition, it worth noting that  $HfO_2$  acts as a tunneling dielectric layer as well as charge trapping element enhancing the program efficiency without an additional tunneling layer.

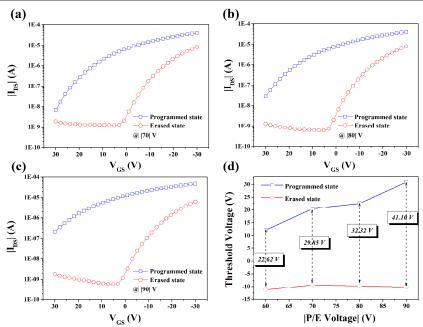

Fig. 4 I-V characteristics of devices based on HfO<sub>2</sub> layer (spin-coated at 3000 rpm for 30s and annealed at 500 °C for 2 h) under program/erase voltage at |70| V, |80| V, |90| V for 5 s, respectively.

Journal Name

As explained in the previous discussion, the device with  $HfO_2$  prepared at 3000 rpm and 500 °C achieved the largest memory window. We also tested the devices using various gate bias voltages from |60| to |90| V with increments of |10| V. The respective transfer curves are presented in Fig. 2c, Fig. 4a, Fig. 4b and Fig. 4c. The memory window is found to be 22.62, 29.85, 32.32 and 41.10 V with increasing program and erase voltage as shown in Fig. 4d, which is due to the increment of electrons extracted from the pentacene at larger electric field. Besides, the ON/OFF current ratio at zero gate voltage is found to be 1.15 × 10<sup>3</sup>, 2.02 × 10<sup>3</sup>, 2.23 × 10<sup>3</sup>, and 6.56 × 10<sup>3</sup> for various gate bias voltages. These results indicate that our memory device work at the non-destructive mode perfectly at zero gate voltage for reading operation.

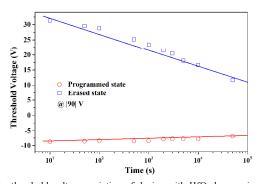

In order to investigate the data retention property of the memory device, the threshold voltage of a typical device with  $HfO_2$  layer (spinning speed of 3000 rpm and annealed at 500 °C) as a function of time was measured and the result is depicted in Fig. 5. The programmed/erased states were obtained at an applied bias of ±90 V for 5s. As illustrated in Fig. 5, both the programmed and erased states degraded slowly with time. Overall, the memory window of this device is well maintained for more than  $10^5$  s. The memory window after  $10^5$  s is around 44.5 % of its initial state, which is comparable with the reported results of device using Si<sub>3</sub>N<sub>4</sub> or HfO<sub>2</sub> layer.<sup>23, 31, 41</sup> Furthermore, the detailed retention and operation voltage of our devices compared with the other reported values are given in Table S1 and Table S2.

#### 4. Conclusions

In summary,  $HfO_2$  charge trapping layer has been fabricated using sol-gel and spin-coating method. We systematically studied the memory effects with respect to various fabrication conditions. The memory window becomes larger with higher  $HfO_2$  annealing temperature or faster spinning speed, which mainly results from high crystallinity and thin film thickness. Moreover, after  $10^5$  s, the memory devices retained 44.5 % of stored charges compared to its initial state. These results indicate that solution proceed  $HfO_2$  is a promising candidate as a charge trapping layer in flash memory.

#### Acknowledgement

This work was financially supported by Shenzhen Municipality project no. JCYJ20120618115445056 and City University of Hong Kong project no. 7002853.

#### Notes and references

<sup>a</sup> Department of Physics and Materials Science, City University of Hong Kong, Hong Kong SAR; E-mail: <u>val.roy@cityu.edu.hk</u>

<sup>b</sup> Shenzhen Research Institute, City University of Hong Kong, High-Tech Zone, Nanshan District, Shenzhen, 518057, China.

<sup>†</sup> Electronic Supplementary Information (ESI) available: [details of any supplementary information available should be included here. See DOI: 10.1039/b000000x/

- S. M. Kim, E. B. Song, S. Lee, J. Zhu, D. H. Seo, M. Mecklenburg, S. Seo and K. L. Wang, *ACS Nano*, 2012, 6, 7879-7884.

- H. C. Chang, C. L. Liu and W. C. Chen, ACS Appl. Mater. Interfaces, 2013, 5, 13180-13187.

- H.-C. Chang, C.-L. Liu and W.-C. Chen, *Adv. Funct. Mater.*, 2013, 23, 4960-4968.

- C. W. Tseng, D. C. Huang and Y. T. Tao, ACS Appl. Mater. Interfaces, 2013, 5, 9528-9536.

- 5. Y. Zhou, S. T. Han, P. Sonar and V. A. L. Roy, Sci. Rep., 2013, 3, 2319.

- S. T. Han, Y. Zhou, C. Wang, L. He, W. Zhang and V. A. Roy, *Adv. Mater.*, 2013, 25, 872-877.

- T. Sekitani, T. Yokota, U. Zschieschang, H. Klauk, S. Bauer, K. Takeuchi, M. Takamiya, T. Sakurai and T. Someya, *Science*, 2009, 326, 1516-1519.

- Q. Wei, Y. Lin, E. R. Anderson, A. L. Briseno, S. P. Gido and J. J. Watkins, *ACS Nano*, 2012, 6, 1188-1194.

- J. S. Lee, J. Cho, C. Lee, I. Kim, J. Park, Y. M. Kim, H. Shin, J. Lee and F. Caruso, *Nature Nanotechnol.*, 2007, 2, 790-795.

- C.-M. Chen, C.-M. Liu, M.-C. Tsai, H.-C. Chen and K.-H. Wei, *J Mater Chem C*, 2013, 1, 2328.

- K.-J. Baeg, D. Khim, D.-Y. Kim, S.-W. Jung, J. B. Koo and Y.-Y. Noh, Jap. J. Appl. Phys., 2010, 49, 05EB01.

- A. Chung, J. Deen, J. S. Lee and M. Meyyappan, *Nanotechnol.*, 2010, 21, 412001.

- P. Heremans, G. H. Gelinck, R. Müller, K.-J. Baeg, D.-Y. Kim and Y.-Y. Noh, *Chem. Mater.*, 2010, 23, 341-358.

- S.-J. Kim, Y.-S. Park, S.-H. Lyu and J.-S. Lee, *Appl. Phys. Lett.*, 2010, 96, 033302.

- C.-W. Tseng and Y.-T. Tao, ACS Appl. Mater. Interfaces, 2010, 2, 3231-3240.

- C.-L. Liu, T. Kurosawa, A.-D. Yu, T. Higashihara, M. Ueda and W.-C. Chen, J. Phys. Chem. C, 2011, 115, 5930-5939.

- K. J. Baeg, D. Khim, J. Kim, B. D. Yang, M. Kang, S. W. Jung, I. K. You, D. Y. Kim and Y. Y. Noh, *Adv. Funct. Mater.*, 2012, 22, 2915-2926.

- D. S. Chung, I. Kang, S. K. Kwon and Y. H. Kim, *RSC Adv.*, 2013, 3, 13156-13162.

- W. L. Leong, N. Mathews, B. Tan, S. Vaidyanathan, F. Dotz and S. Mhaisalkar, *J. Mater. Chem. C*, 2011, 21, 8971-8974.

- L. Larcher and A. Padovani, *Microelectron. Reliab.*, 2010, 50, 1251-1258.

- 21. S. J. Kim and J. S. Lee, Nano Lett, 2010, 10, 2884-2890.

- 22. H.-W. You and W.-J. Cho, Appl. Phys. Lett., 2010, 96, 093506.

- H. W. You, S. M. Oh and W. J. Cho, *Thin Solid Films*, 2010, 518, 6460-6464.

- 24. Z. H. Ye, K. S. Chang-Liao, T. C. Liu, T. K. Wang, P. J. Tzeng, C. H. Lin and M. J. Tsai, *Microelectron. Eng.*, 2009, 86, 1863-1865.

- Y. N. Tan, W. K. Chim, B. J. Cho and W. K. Choi, *IEEE Electron Dev. Lett.*, 2004, 51, 1143-1147.

- 26. Y. H. Peng, F. Liu, X. Y. Liu, G. Du and J. F. Kang, *Jap. J. Appl. Phys.*, 2013, 52.

- 27. M. K. Bera and C. K. Maiti, *Semiconductor Science and Tech.*, 2007, 22, 774-783.

- S. J. Chang, M. Bawedin, W. Xiong, S. C. Jeon, J. H. Lee and S. Cristoloveanu, *Microelectron. Eng.*, 2011, 88, 1203-1206.

- N. Nikolaou, P. Dimitrakis, P. Normand, V. Ioannou-Sougleridis, K. Giannakopoulos, K. Mergia, K. Kukli, J. Niinisto, M. Ritala and M. Leskela, *Solid-State Electronics*, 2012, 68, 38-47.

- H. C. You, T. H. Hsu, F. H. Ko, J. W. Huang, W. L. Yang and T. F. Lei, *IEEE Electron Dev. Lett.*, 2006, 27, 653-655.

- J. Molina, R. Ortega, W. Calleja, P. Rosales, C. Zuniga and A. Torres, *Mater. Sci. Eng. B-Adv.*, 2012, 177, 1501-1508.

- I. Ok, H. Kim, M. Zhang, F. Zhu, S. Park, J. Yum, H. Zhao, D. Garcia, P. Majhi, N. Goel, W. Tsai, C. K. Gaspe, M. B. Santos and J. C. Lee, *Appl. Phys. Lett.*, 2008, 92, 202903.

- J. Buckley, B. De Salvo, G. Ghibaudo, M. Gely, J. F. Damlencourt, F. Martin, G. Nicotra and S. Deleonibus, *Solid-State Electron.*, 2005, 49, 1833-1840.

- O. Acton, G. Ting, H. Ma, J. W. Ka, H. L. Yip, N. M. Tucker and A. K. Y. Jen, *Adv. Mater.*, 2008, 20, 3697.

- S. T. Han, Y. Zhou, Z. X. Xu, L. B. Huang, X. B. Yang and V. A. L. Roy, *Adv. Mater.* 2012, 24, 3556-3561.

- 36. C. Pramanik and G. P. Miller, Molecules, 2012, 17, 4625-4633.

- C.-W. Tseng, Y.-L. Chen and Y.-T. Tao, Org. Electron., 2012, 13, 1436-1442.

- K.-J. Baeg, Y.-Y. Noh, J. Ghim, B. Lim and D.-Y. Kim, *Adv. Funct. Mater.*, 2008, 18, 3678-3685.

- Z. J. Wang, T. Kumagai, H. Kokawa, M. Ichiki and R. Maeda, J. *Electroceram.*, 2007, 21, 499-502.

- C. V. Ramana, K. K. Bharathi, A. Garcia and A. L. Campbell, *The J. Phys. Chem. C*, 2012, 116, 9955-9960.

- S. Maikap, H. Y. Lee, T. Y. Wang, P. J. Tzeng, C. C. Wang, L. S. Lee, K. C. Liu, J. R. Yang and M. J. Tsai, *Semicond. Sci. Technol.*, 2007, 22, 884-889.