# Nanoscale

Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

## Nanoscale

### **RSCPublishing**

#### **ARTICLE**

# Multiprotocol-induced plasticity in artificial synapses

Cite this: DOI: 10.1039/xoxxooooox

Received ooth January 2012, Accepted ooth January 2012

DOI: 10.1039/x0xx00000x

www.rsc.org/

Vladimir Kornijcuk, <sup>ab</sup> Omid Kavehei, <sup>c</sup> Hyungkwang Lim, <sup>ad</sup> Jun Yeong Seok, <sup>ad</sup> Seong Keun Kim, <sup>a</sup> Inho Kim, <sup>a</sup> Wook-Seong Lee, <sup>a</sup> Byung Joon Choi, <sup>b</sup> and Doo Seok Jeong\*<sup>a</sup>

We suggest a 'universal' electrical circuit for realization of an artificial synapse that exhibits long-term plasticity induced by different protocols. The long-term plasticity of the artificial synapse is basically attributed to the nonvolatile resistance change of the bipolar resistive switch in the circuit. The synaptic behaviours realized by the circuit is termed 'universal' insomuch as i) the shape of the action potential is not required to vary so as to implement different plasticity-induction behaviours, activity-dependent plasticity (ADP) and spike-timing-dependent plasticity (STDP), ii) the behaviours satisfy several essential features of biological chemical synapse including firing-rate and spike-timing encoding and unidirectional synaptic transmission, and iii) both excitatory and inhibitory synapses can be realized using the same circuit but the different diode polarity in the circuit. The feasibility of the suggested circuit as an artificial synapse is demonstrated by conducting circuit calculations and the calculation results are introduced in comparison with biological chemical synapses.

#### Introduction

Mammalian brains have distinctive features in comparison with digital computers. First, they are typical examples of analogue data processors, enabling the limited number of data process units, i.e. neurons, to deal with a much larger amount of information than digital systems.<sup>1, 2</sup> Second, they process information by means of a large population of neurons (population representation) rather than individual neurons.<sup>2-4</sup> Therefore, as the information encoding and decoding is realized in a statistical manner, erroneous computation occurring in a number of individual neurons have little impact on the overall performance of the population including them, in other words, a fine example of error-tolerant-computing. Third, mammalian brains are able to learn and adapt themselves, which is one of the most distinctive features differentiating them from digital computers. Given these interesting three basic features, there have been attempts to achieve some brain-like on-chip functionalities by means of solid-state devices. Such efforts are referred to as neuromorphic engineering.<sup>5</sup>

The mammalian brain is understood as a complex network of neurons that are connected via synapses; in mammalian brains, on average, there are thousands of synapses (local memory) for each neuron, which makes them a bottleneck of any hardware implementation. Synapses are understood to play significant roles in the aforementioned features of the brain, i.e. population representation<sup>6, 7</sup>, memory, and adaptation (learning)<sup>8</sup>. There are two types of synapses: electrical synapse (also known as

gap-junction) and chemical synapse. 1 The latter is regarded to be mainly involved in learning and memory in the happocampus<sup>8</sup>, while recent study suggests that electrical synapses play a key role in fear learning and memory<sup>9</sup>. Chemical synapses are plastic and involved in learning and memory. In other words, plasticity of their synaptic efficacy defines the connectivity between two associated neurons. Chemical synapses undergo such plastic change upon external electrical stimulation of their associated neurons. It should be noted that the synaptic transmission through a chemical synapse is unidirectional insomuch as the transmission takes place by means of neurotransmitters (chemical messengers) that are released from the 'presynaptic neuron' and arrive at receptors on the 'postsynaptic neuron'. Several plasticity-induction protocols are known, such as activity-dependent plasticity (ADP) and spike-timing-dependent plasticity (STDP), in which a chemical synapse encodes firing rate (activity) information conveyed by the presynaptic neuron and the spike-timing information. On the contrary, electrical synapses are bidirectional, since the transition through their narrow gapjunctions (ca. 3 nm) occurs in an electric manner, which resembles an electric resistor. Chemical synapses have been the main point of focus in neuromorphic engineering. Therefore, in this study, the term 'synapse' denotes a 'chemical synapse' unless otherwise stated.

To date, several candidates for artificial synapses have been proposed, which are based on functional materials such as ferroelectrics<sup>10, 11</sup>, phase-change materials<sup>12, 13</sup>, ferromagnetic

Nanoscale Page 2 of 10

ARTICLE Journal Name

materials<sup>14</sup>, and nanoionic resistive switching materials<sup>15-22</sup> or complementary metal-oxide-semiconductor conventional technologies<sup>23-27</sup>. Recently, a number of neuromorphic circuits based on nanoionic resistive switching materials have been proposed.<sup>28-31</sup> This class of neuromorphic circuits can be classified in a rather general category of "memristive devices and circuis". 32, 33 In general, most of the nanoionic candidates are two-terminal capacitor-shaped devices, thus pre and postsynaptic terminals can be mapped to the device's two electrodes. A popular approach to implementation of synaptic plasticity induction in such a capacitor-shaped synapse is to vary action potential (AP)'s shape that is suitable for each plasticity induction protocol. 11, 12, 14, 20 This approach appears to be suitable for neuromorphic circuits based on synaptic plasticity induced by a particular single protocol. However, regarding the general use of artificial synapses, which is not protocol-specified, such a method perhaps lacks 'universal' feature of artificial synapses in a broader term as a fundamental neuromorphic system building-block. Another potential problem of this approach is the difficulty in generating such shape of APs using artificial neurons. Therefore, the universality of artificial synapses appears to be of significant importance in enabling various induction-protocols to be realized by employing fixed shape of APs, e.g. square-shaped, which can be easily generated by artificial neurons. Besides, several other aspects of artificial synapses should be considered to satisfy general features of biological synapses. These aspects include unidirectional synaptic transmission and excitatory and inhibitory behaviours. These aspects seem to be barely implemented in two-terminal artificial synapses, in particular, those based on bipolar resistive switches (BRSs). The difficulty mostly lies in such that passive stand-alone BRSs cannot avoid bidirectional transmission and realize negative resistance, required for inhibitory synaptic behaviour.

This paper suggests an artificial synaptic circuit based on a BRS. Circuit calculations were conducted under different stimulation conditions in a time domain so as to identify the successful encoding of presynaptic spikes', i.e. APs', firing rate and timing of pre and postsynaptic spikes. Both pre and postsynaptic spikes were set the same square-shaped voltage pulse of constant height and width. A cation-based Pt/GeSe<sub>x</sub>/Ag system was regarded as the BRS in the circuit; its behavioural parameters, acquired from the switching measurements, were used in the calculations. The results show good agreement with the mentioned features of biological synapses. The proposed circuit appears to pave the way for realization of hardwarebased artificial neural networks (ANNs) as well as computersimulation-based, i.e. in silico, ANNs. This simple circuit may be employed in in silico ANNs as an artificial synapse exhibiting multi-protocol-inducing plasticity fulfilling the given characteristics of biological synapses. In addition, our synaptic circuit perhaps promises a progress in building interfaces with biological neurons for a detailed investigation of biological neural behaviour and a further development of brain-machine interfaces.

#### **Experimental**

#### Bipolar switch fabrication

A cation-based Pt(bottom electrode)/GeSe<sub>x</sub>/Ag(top electrode) BRS was formed in crossbar structure of  $10\times10~\mu\text{m}^2$  area. The thicknesses of the Pt, GeSe<sub>x</sub>, and Ag layers are 100, 50, and 100 nm, respectively. The Pt bottom electrode (BE) was sputtered onto an oxidized Si wafer with a Ti adhesion layer on top and patterned by using a standard photolithography technique. Thereafter, the GeSe<sub>x</sub> solid electrolyte layer was sputtered onto the patterned bottom electrode. Finally, the Ag top electrode (TE) was e-beam-evaporated onto the GeSe<sub>x</sub> layer and patterned by using a photolithography technique.

#### Bipolar switching measurements

Quasi-static current-voltage (*I-V*) characteristics of the BRS were measured by using a Keithley 236 Source Measure Unit. The response of the switch to consecutive voltage pulses was identified using a Tektronix AFG3101 function generator and a Tektronix TDS5104 oscilloscope. The TE was subject to an applied voltage while the BE was grounded.

#### Circuit calculation

The calculations in this work were performed by using an LTspice circuit simulator. A BRS code was carefully chosen among a number of memristor models, providing the best fitting results. Basically, the model proposed by Biolek *et al.*<sup>34</sup> provides an optimal fit to the experimental results. However, threshold voltages for switching were employed in our circuit calculation. The N-channel metal-oxide-semiconductor field-effect-transistor (n-MOSFET) in this work was simulated by using the sub-0.13 micron BSIM 4 model.<sup>35</sup> All remaining elements were taken directly from the list proposed by the simulator software.

#### **Synaptic calculation**

#### Bipolar switching behaviour of a Pt/GeSe<sub>x</sub>/Ag switch

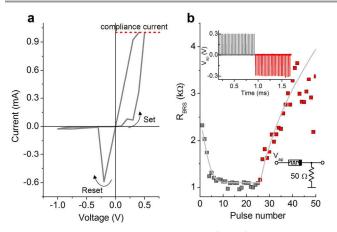

A BRS of Pt(bottom electrode)/GeSe<sub>x</sub>/Ag(top electrode) was regarded to be used in the synaptic circuit; the following synaptic calculations were conducted based on its behavioural parameters. A representative I-V curve of the BRS is shown in Figure 1a. Employing Ag electrode in cation-based memory has an advantage of low threshold voltage compared with, for instance, Cu electrode.<sup>36</sup> The BRS exhibits threshold voltages for resistance decrease  $(V_{set})$  and increase  $(V_{reset})$  of approximately 0.2 and -0.2, respectively. The presence of thresholds defines a voltage-window ( $V_{\text{reset}} - V_{\text{set}}$ ), and thus only voltage staying out of the window allows a nonvolatile change in resistance. In Figure 1a, linear I-V behaviour which is zero-crossing is also seen, so that resistance can be regarded constant within the subthreshold voltage-window. These characteristics are of importance in choosing a proper SPICE model of the BRS.

Page 3 of 10 Nanoscale

Journal Name ARTICLE

An attempt to further identify the switching behaviour of the BRS was made by observing BRS' responses to consecutive square voltage pulses whose width and height were 1µs and 0.3 V, respectively. As shown in Figure 1b, nonvolatile changes in resistance in both directions were realized by applying the voltage pulse train plotted in the inset. Both increase and decrease in resistance are rather gradual, therefore, the BRS is able to represent various resistance states. Electrical characteristics of the BRS are shown in detail in Supplementary Information.

Figure 1. (a) Quasi-static I-V behaviour of the Pt/GeSe<sub>x</sub>/Ag BRS. A compliance current of 1 mA was applied. (b) Change of R<sub>BRS</sub> upon a voltage train applied to the BRS in the configuration shown in the lower inset. The applied voltage train ( $V_{op}$ ) is plotted in the upper inset, where the voltage pulse width and height are 1  $\mu$ s and 0.3 V, respectively. The grey line denotes a curve fitting the data.

Table 1. Parameters used for the calculations

| Parameter                                             | Value                                                        |

|-------------------------------------------------------|--------------------------------------------------------------|

| $R_{\rm BRS}$ in the full ON state $(R_{\rm ON})$     | 1.4 kΩ                                                       |

| $R_{\rm BRS}$ in the full OFF state ( $R_{\rm OFF}$ ) | 7.5 kΩ                                                       |

| Cation mobility $(\mu_v)$ positive V                  | $1.5 \times 10^{-8} \text{ m}^2 \text{s}^{-1} \text{V}^{-1}$ |

| negative V                                            | $2.8 \times 10^{-9} \text{ m}^2\text{s}^{-1}\text{V}^{-1}$   |

| Switching layer thickness (D)                         | 50 nm                                                        |

| Window function parameter (p) positive V              | 1                                                            |

| negative V                                            | 0.7                                                          |

| $V_{ m reset}$                                        | -0.2 V                                                       |

| $V_{ m set}$                                          | 0.2 V                                                        |

| Threshold function parameter (s)                      | $10^{-3} \text{ V}$                                          |

| MOSFET channel length/width                           | 150/500 nm                                                   |

| MOSFET $V_{\mathrm{th}}$                              | 0.2 V                                                        |

| MOSFET channel resistance                             | 17.1 kΩ ( $V_{ds}$ =1.5 V and $V_{g}$ =1)                    |

|                                                       |                                                              |

Implementing the above-mentioned switching behaviours using a SPICE model allows much easier and simpler calculations of the aimed circuit. The remarkable characteristics of the BRS are such as i) presence of thresholds, ii) linear *I-V* behaviour, and iii) non-linear resistance change upon consecutive voltage pulses. Given these features, the model proposed by Biolek *et al.*<sup>34</sup> together with the threshold function most likely provides the best fitting result; the differential equation of the state variable *w* is given by

$$\frac{dw}{dt} = \frac{\mu_{\nu} R_{ON}}{D^2} \cdot I(t) \cdot f_w(w) \cdot f_{th}(V), \tag{1}$$

where w and  $\mu_v$  nominally denote the length of Ag-filaments within the initially insulating electrolyte layer of thickness D and the mobility of the Ag ions confined within w.  $R_{\rm ON}$  denotes the resistance of the BRS in the extreme case when w=D, i.e. the lowest resistance of the BRS.  $f_w$  indicates the window function implementing nonlinear migration of the nominal Ag-filament/electrolyte boundary across the thickness D. In this work, a new window function, which provided the best fitting, was introduced and is given by

$$f_w(w) = \left(\frac{\cos(\pi w) + 1}{2}\right)^p, p > 0,$$

(2)

where p is a window function parameter. The aforementioned threshold voltages for nonvolatile switching are implemented in Eq.(1) by introducing the threshold function  $f_{th}$  given by

$$f_{th}(V) = e^{-(V_{TH} - |V|)/s}, V_{TH} \in \{V_{set}, V_{reset}\},$$

(3)

where s is a parameter determining the slope of the threshold function in the vicinity of  $V_{\text{TH}}$ . The smaller s, the steeper a change in  $f_{th}$  with respect to |V| in the vicinity of  $V_{\text{TH}}$ .

Note that this SPICE model is highly empirical, which describes the bipolar switching kinetics of the Ag-based BRS under limited conditions such as pulse height and width up to 0.6 V and 5  $\mu$ s, respectively (see Supplementary Information). Thus, this model including the parameters is unlikely useful unless the BRS is subject to the given range of input. In particular, the switching voltages ( $V_{\rm reset}$  and  $V_{\rm set}$ ) are strongly dependent on the duration, i.e. pulse width.<sup>37, 38</sup> A generic model of cation-based switching, considering the source and sink of cations, i.e. redox reactions, describes switching kinetics in extremely wide time and voltage domains.<sup>37, 38</sup> Such a model can cover all approximations, e.g. the SPICE model in the present study, localized in the domains.

Using this SPICE model with the parameters listed in Table 1, the change of  $R_{\rm BRS}$  upon the voltage pulse train, shown in Figure 1b, was successfully fitted (grey line in Figure 1b). Note that different  $\mu_{\nu}$  and p values for different electric field directions, i.e. asymmetric migration-rate constants, were used in this fitting. These parameters form the basis for the following circuit calculations. The parameters in use were extracted from statistical analysis on the BRS' responses to different inputs (pulse width:  $0.5-1.5~\mu s$  and height: 0.3-0.6~V).

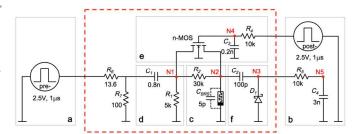

**Figure 2.** Electrical circuit for the artificial synapse (red dashed line) and a circuit for synaptic plasticity evaluation.

Nanoscale Page 4 of 10

ARTICLE Journal Name

#### Circuit configuration

The circuit used for the multiprotocol-induced plasticity implementation is shown in Figure 2. Pre and postsynaptic spike-firing was simulated by invoking two voltage pulse generators, which are shown in Figures 2a and b, respectively. The width and the amplitude of each spike were set 1 µs and 2.5 V, respectively. Note that spike shapes were not varied throughout the whole study; instead, inter-spike interval (ISI) and pre and postsynaptic spike-timing were varying timedomain parameters. The RC integrator in Figure 1b was employed to evaluate the change of postsynaptic membrane potential upon the synaptic efficacy; the integrator corresponds to the membrane of the postsynaptic neuron. In this work, synaptic plasticity will mainly be described in terms of postsynaptic potential (PSP), so that potentiation and depression were defined by relative changes in PSP, i.e.  $\Delta PSP$ , upon plasticity induction trials. This circuit was aimed to encode presynaptic activity (firing rate) and the timing of pre and postsynaptic spikes for both excitatory and inhibitory synapse cases. The subcircuits in Figures 2c, d, e, and f play key roles in synaptic plasticity induction.

The essential features of long-term plasticity of the biological synapse, long-term potentiation (LTP) and long-term depression (LTD), were realized by using the BRS, which is placed in Figure 2c. As discussed earlier, both polarities are required to alter the resistance in different directions, i.e. the resistance increases and decreases under negative and positive voltage, respectively. In the circuit shown in Figure 2, a change in  $R_{\rm BRS}$  leads to a change in voltage drop across the BRS, and consequently a change in PSP evolution in due course. For instance, an increase in  $R_{\rm BRS}$  results in potentiation, since the resistance increase elevates the voltage at node N2, which consequently elevates the PSP, i.e. causes potentiation. A decrease in  $R_{BRS}$  results in a change in the opposite direction, so that depression is achieved. It is therefore apparent that the role of a BRS in an artificial electronic synapse depends on the circuit configuration. For instance, in a typical single BRSbased electronic synapse, where pre and postsynaptic spikes are incident on the two terminals of the BRS, potentiation and depression are realized by a decrease and an increase in the resistance, respectively. 15, 16, 20 Note that  $C_{BRS}$  denotes the capacitance of the BRS due to the use of the solid electrolyte which is dielectric.

The subcircuit in Figure 2d plays an important role in realization of ADP. Employing charging and discharging of capacitor  $C_1$  enables the polarity of a voltage, applied to the BRS, i.e.  $V_{\rm N2}$ , to be altered without changing the polarity of the presynaptic spikes. In addition, the contribution of each charging and discharging effect to the change of  $R_{\rm BRS}$  varies upon charging and discharging time-windows. Thus, changing the ISI, while using identical spike widths, realizes a change in their relative contributions, which implies ADP. The MOSFET shown in Figure 2e, 'crops' a part of the RC output signal at node N1 and transmits it to the BRS; cropping is controlled by the gate to which postsynaptic connection is applied. Therefore,

a voltage assigned to the BRS, i.e.  $V_{\rm N2}$ , depends on the pre and postsynaptic spike-timing, hence, implementing STDP. The subcircuit in Figure 2f determines either excitatory or inhibitory synaptic behaviour depending on the polarity of diodes  $D_1$ . Under the current configuration, the subcircuit in Figure 2f implements an excitatory synapse and an inhibitory configuration can be realized by simply flipping the polarity of the diode. The diode is employed to introduce an asymmetric  $V_{\rm N3}$  profile when charging and discharging capacitor  $C_2$ , which in turn leads to asymmetry in  $V_{\rm N5}$ , i.e. PSP. This asymmetry is attributed to the asymmetric current-voltage relationship of the diode. Unless otherwise stated, the calculations in the following sections are conducted on excitatory synapse. The detail of plasticity induction of the given circuit is addressed in following subsections.

The circuit parameters listed in Table 1 realize the synaptic plasticity in an activity domain below 500 kHz. However, depending on the purpose of the artificial synapse, the activity-window can be optimized by changing the circuit parameters, in particular, resistance and capacitor values.

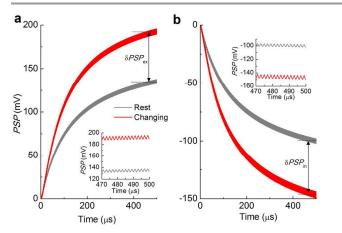

**Figure 3.** PSP evolution for the 'rest' and 'changing' synaptic efficacy cases, calculated on (a) excitatory and (b) inhibitory synapses. For both cases, presynaptic activity was set 500 kHz to realize HFS-induced LTP.  $\delta PSP$  denotes a difference in PSP between the 'rest' and 'changing' efficacy runs at a given time. The number of voltage pulses for the time period (0 – 500 μs) is 250. The PSP evolution in the time range 470 – 500 μs is zoomed in in the insets.

#### **PSP** evaluation

As mentioned earlier, the membrane model of a postsynaptic neuron was implemented by means of the RC integrator shown in Figure 2b. The PSP was a measure of the electrostatic potential difference across capacitor  $C_4$ . A change in synaptic efficacy upon plasticity induction was evaluated by calculating a difference in PSP between 'changing' and 'rest' efficacy cases at a certain time after stimulation;  $\Delta PSP=(PSP_c-PSP_0)/PSP_0\times100$ , where  $PSP_c$  and  $PSP_0$  denote PSPs for the changing and the rest efficacy cases, respectively. For instance, an LTP-caused deviation of PSP evolution from the rest efficacy case is plotted in Figure 3. The LTP was achieved by applying a high frequency stimulus (HFS), 500 kHz, to the presynaptic terminal in Figure 2a.  $\Delta PSP$  was evaluated at 500  $\mu$ s. On the contrary, LTD rather decreases PSP evolution from

Journal Name ARTICLE

**Nanoscale**

the rest case, showing negative  $\Delta PSP$ . In case of LTP,  $R_{BRS}$  increases, leading to elevation of  $V_{N2}$ . This in turn elevates  $V_{N5}$  denoting the PSP. During LTD,  $R_{BRS}$  change proceeds in the opposite direction, so that  $V_{N2}$  decreases, and so does  $V_{N5}$ , compared to the rest efficacy case. Note that the PSP varies upon the capacitance of the integrator, which is of the postsynaptic neuron; the choice of the capacitance is a matter of artificial neuron rather than synapse. For all calculations in this study  $C_4$  was set 3 nF. Note that the read-out time is measured from the initiation of pulse application and the read-out time for each synaptic behaviour is specified since PSP evaluation depends on read-out time. One can identify a change in synaptic efficacy after a training period; however it gives almost the same percentage change as long as the BRS is of non-volatile resistance change.

#### Results

Page 5 of 10

#### Activity-dependent plasticity

The charging and discharging of capacitor  $C_1$  in Figure 2d varies upon the ISI of the presynaptic spike-train. In particular, when it comes to ISI values that are close to the characteristic RC time-constant of the circuit (ca. 3.2  $\mu$ s), the discharging as well as the subsequent charging is significantly affected by the ISI. Subsequently, the output voltage from the RC circuit depends on the ISI, i.e. presynaptic activity. Utilizing these charging and discharging effects enables the BRS to undergo resistance change in both directions, i.e. up and down, while the polarity of incident spikes is maintained positive.

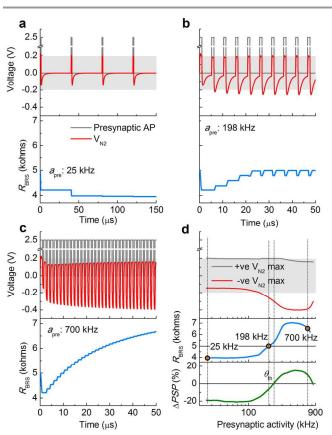

The PSP of the circuit was evaluated by applying presynaptic spike-trains of different ISI values, 39, 4.05, and 4.29 µs, corresponding to 25, 198, and 700 kHz in activity, respectively, while no postsynaptic spikes were applied. Figure 4 shows the calculated transient profile of  $V_{\rm N2}$ , i.e. a voltage across the BRS, and the corresponding change of  $R_{BRS}$  for the three different activities. The shaded regions in the figure denote a subthreshold voltage range (-0.2 to 0.2 V) for the change of  $R_{\rm BRS}$ ; voltage within the range does not lead to resistance change. Capacitor  $C_1$  is fully discharged during the ISI period when the ISI largely exceeds the RC time-constant (see the upper panel of Figure 4a). In this case, the maximum amplitudes of both negative and positive output voltage barely change upon spike number. Upon an incident single AP, induced  $V_{\rm N2}$  during charging and discharging is asymmetric; the negative maximum of  $V_{\rm N2}$  is much larger than the positive one as can be seen in Figure 4a. Despite this asymmetry, the contribution of the negative maximum to  $R_{BRS}$  change is not dominant over that of the positive one because of the asymmetry of  $\mu_{\nu}$ , i.e. higher under positive voltage than negative one. Therefore, at each incident, only a slight decrease in  $R_{RBS}$  is seen, leading to LTD (see Figure 4a bottom panel).

Figure 4. Transient  $V_{\rm N2}$  profile and the corresponding  $R_{\rm BRS}$  under a presynaptic AP train at activities ( $a_{\rm pre}$ ) of (a) 25, (b) 198, and (c) 700 kHz. In all cases, the initial resistance was set to 5 kΩ. The grey zone indicates the subthreshold voltage region, i.e.  $V_{\rm reset} < V < V_{\rm set}$ , for the change of  $R_{\rm BRS}$ . (d) The positive and negative  $V_{\rm N2}$  maxima with respect to presynaptic activity. The corresponding  $R_{\rm BRS}$  and  $\Delta PSP$  are also plotted. The threshold activity  $\theta_{th}$  (ca. 198 kHz) for LTP is designated using a dashed line. The PSP was read at 50 μs for all three cases.

In contrast, when the ISI decreases and it becomes close to or even shorter than the RC time-constant, full discharge is prevented, pushing the transient voltage towards negative values (see upper panels in Figures 4b and c). This eventually lets the negative voltage peaks largely exceed  $V_{\text{reset}}$ , while the positive peaks decrease, resulting in a stepwise increase in  $R_{\rm BRS}$ as shown in Figures 4b and c. The positive and negative voltage peaks in the steady state, the corresponding  $R_{BRS}$ , and the  $\Delta PSP$ value read at 50 µs are plotted in an activity domain in Figure 4d. These results identify that the presynaptic activity information is successfully encoded in the synaptic circuit, exhibiting a threshold activity  $\theta_{th}$  for LTP induction (ca. 198 kHz) as shown in Figure 4d. Activities below the threshold induce LTD rather than LTP. These features are well consistent with ADP in biological synapses. In addition, the calculated ADP behaviour avoids unlimited growth of synaptic efficacy. In fact, limited growth of synaptic efficacy is seen in biological synapses.<sup>39, 40</sup> This limited growth in Figure 4d is understood in terms of switching kinetics of the BRS. The higher the presynaptic activity is, the narrower the negative effective voltage at node N2 is. Thus, switching time sufficient to cause a large change in  $R_{\rm BRS}$  is barely given to the BRS at high Nanoscale Page 6 of 10

ARTICLE Journal Name

activities despite the high negative voltage peaks. Given this trade-off between the voltage peak height and the voltage application time, a  $R_{\rm BRS}$  increase rate tends to decrease at high activities slightly.

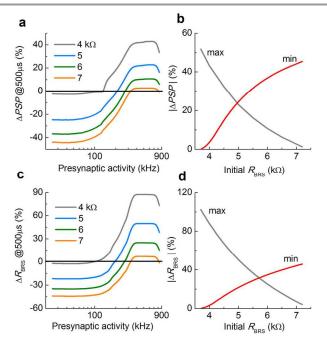

Figure 5. ADP behaviour and the corresponding  $\Delta R_{BRS}$  of the artificial synapse were calculated with different initial  $R_{BRS}$  values, i.e. different initial synaptic efficacies, and plotted in (a) and (c), respectively. The maximum of positive  $\Delta PSP$  due to LTP and the minimum of negative one due to LTD are plotted in (b). The corresponding maximum and minimum of  $\Delta R_{BRS}$  are shown in (d). All  $\Delta PSP$  and  $\Delta R_{BRS}$  values were taken at 500 μs.

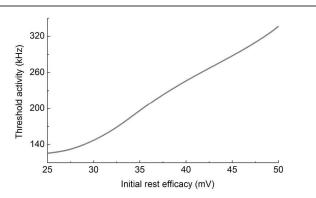

Figure 6. Dependence of threshold activity for LTP in ADP on initial synaptic efficacy. The PSP was evaluated at  $500~\mu s$ .

The history-depending BRS allows its various initial resistance states on each induction trial, implying that the artificial synapse is history-dependent. The ADP behaviour was calculated for different initial  $R_{\rm BRS}$  (4 – 7 k $\Omega$ ) and is plotted in Figure 5a. High initial resistances mean high initial synaptic efficacies that can be achieved by previous LTP induction. As shown in Figure 5b, the positive  $\Delta PSP$  at high activities tends to continuously decrease with the initial resistance while the negative  $\Delta PSP$  exhibits the opposite behaviour. The continuous decrease in the positive  $\Delta PSP$  indicates the fact that the limited

synaptic efficacy, i.e. saturation, is achievable by repeating LTP induction trials. The corresponding change of  $R_{\rm BRS}$  at the various initial  $R_{\rm BRS}$  in an activity domain is shown in Figure 5c. Note that the PSP was read at 500  $\mu s$  so as to observe more obvious ADP behaviour.

Regardless of the initial resistance, a threshold activity  $\theta_{th}$  for the transition between LTD and LTP is noticed in Figure 5a. Such thresholds have been well known in biological synapses, working as criteria for either LTD or LTP in an activity domain. There have been several empirical models accounting for the activity-dependent plasticity of chemical synapses by taking into account such thresholds, e.g. the Bienenstock-Cooper-Munro (BCM) rule<sup>41</sup> and the Oja rule<sup>42</sup>. Notably, in our artificial synapse, the threshold activity increase with the initial synaptic efficacy, i.e. higher activities are required to induce LTP as the initial efficacy increases. The relationship is seen in Figure 6, where initial efficacy was described as a 'rest' PSP value evaluated at 500  $\mu$ s. This implies that the threshold is given by a function of synaptic efficacy.

#### Spike-timing-dependent plasticity

The n-MOSFET in Figure 2e crops the RC circuit's output voltage at node N1 upon arrival of a postsynaptic spike at the gate terminal (turning on the channel when  $V_{\rm N4} > V_{\rm th}$ =0.2 V) and transmits the cropped voltage to node N2. However, capacitor  $C_3$  and resistor  $R_4$  in Figure 2e delay transmission of the postsynaptic spike to node N4, and thus the consequent elevation of  $V_{\rm N4}$ . Therefore, a time lag between the postsynaptic spike firing and the channel's turn-on occurs.

Upon arrival of the postsynaptic spike at the MOSFET and the channel's turn-on in due course,  $V_{\rm N2}$  increases insomuch as the channel works as a bypass between nodes N1 and N2. The relative timing of the pre and the postsynaptic spikes therefore determines relative contributions of positive and negative voltage inputs to  $R_{BRS}$  change. These aspects of the circuit realize general features of STDP in biological synapses, such as encoding the timing of pre and postsynaptic spikes and LTPinduction at even lower presynaptic activities than the ADP threshold  $\theta_{th}$ . A3-45 The STDP behaviour of the circuit at a particular interval between a pre and a postsynaptic spike  $\Delta t$ was evaluated by applying a train of several pairs of pre and postsynaptic spikes with certain time interval. By varying the spike interval on each trial, the entire STDP characteristics of the circuit were evaluated. The frequency of the voltage-pair train was set 50 kHz for all calculations, which is sufficiently low to differentiate the STDP implementation from the LTP induction by HFS in ADP. Note that  $\Delta t$  is taken positive when the presynaptic spike is ahead of the postsynaptic. The arrival and termination times of a presynaptic (postsynaptic) spike are denoted by  $t_{\text{pre1}}$  ( $t_{\text{post1}}$ ) and  $t_{\text{pre2}}$  ( $t_{\text{post2}}$ ), respectively, so that  $\Delta t$ =  $t_{\text{post1}}-t_{\text{pre1}}$ .

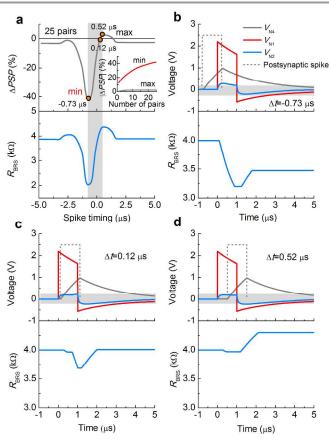

Calculation results for  $\Delta PSP$  and  $R_{BRS}$  are shown in Figures 7a. The number of spike-pairs on each trial, i.e. in each voltage train, was 25, which corresponds to 500  $\mu$ s in time. As shown in the inset of Figure 7a, the change of the PSP upon the spike-timing is proportional to the number of pairs. The calculated

**Nanoscale Journal Name ARTICLE**

STDP characteristics are in agreement with those of biological synapses; positive  $\Delta t$ , i.e. a presynaptic spike ahead of a postsynaptic, leads to LTP and negative  $\Delta t$  to LTD. Timewindows for the LTD and the LTP are approximately 3 and 1.5 μs, respectively. There is a transition zone of approximately 1.4 μs width between the LTD- and LTP-windows, which is depicted using a grey zone. The centre of the zone is placed at around  $\Delta t = 0$ .

Page 7 of 10

To highlight the STDP features,  $V_{\rm N2}$  and the corresponding  $R_{\rm BRS}$  change were evaluated in a time domain at three representative  $\Delta t$  points, -0.73, 0.12, and 0.52  $\mu$ s, at which i) the maximum LTD, ii) a negligible change in the PSP, and iii) the maximum LTP are shown, respectively. Their profiles are plotted in Figures 7b, c, and d, respectively. Note that, due to capacitor  $C_3$  and resistor  $R_4$  in Figure 2e, the take-off and the peak of  $V_{\rm N4}$  indicate the arrival and the termination of the postsynaptic spike, respectively.

Figure 7. (a) Upper panel: Calculated STDP behaviour of the artificial synapse. The STDP was evaluated after 25 pairs of pre and postsynaptic spikes at 50 kHz. corresponding to a read-out time of 500  $\mu s$ . The larger the number of pairs, the higher  $|\Delta PSP|$ , as shown in the inset of the figure. Lower panel: The corresponding RBRS change with respect to timing of pre and postsynaptic spikes. Indicated using the cycles are the three timing values (-0.73, 0.12, and 0.52  $\mu$ s) when the LTD maximum, negligible plasticity in total, and the LTP maximum occur respectively. The profiles of  $V_{\rm N1},~V_{\rm N2},~{\rm and}~V_{\rm N4}$  in a time domain are evaluated for the three timing values: (b) -0.73, (c) 0.12, and (d) 0.52 μs. For each case, RBRS in the given timing range is also plotted in the lower panel of each figure [(b), (c), and (d)]. The initial resistance was set to  $4 \text{ k}\Omega$ .

- i)  $\Delta t$ =-0.73 µs:  $t_{post1} < t_{pre1} < t_{post2} < t_{pre2}$ . The postsynaptic spike arrives 0.73 µs ahead of the presynaptic spike, leading to the profile of  $V_{\rm N2}$ , shown in Figure 7b. Given that the channel of the n-MOSFET works as a bypass upon arrival of the postsynaptic spike, which turns on the channel, the resistance in total between nodes N1 and N2 decreases, and thus  $V_{\rm N2}$  becomes higher than that in the absence of the postsynaptic spike (compare Figures 4a and 7b). In the time-window,  $0 \le t \le 1$  µs,  $V_{N2}$  exceeds  $V_{set}$ , leading to a decrease in  $R_{BRS}$  as shown in the lower panel of Figure 7b. Upon the termination of the presynaptic spike the negative maximum of  $V_{\rm N2}$  is reached, which is higher than that shown in case of ADP (see Figure 4a). This transient negative  $V_{\rm N2}$  leads to an increase in  $R_{RBS}$  in due course. Given the asymmetry of  $\mu_{\nu}$ , the contribution of the positive  $V_{\rm N2}$  to the  $R_{\rm BRS}$  change is larger than the negative voltage. This effect is shown in the lower panel of Figure 7b. Thus, the overall change of  $R_{\rm BRS}$  is negative, implying LTD.

- $\Delta t$ =0.12 µs:  $t_{\text{pre1}} < t_{\text{post1}} < t_{\text{pre2}} < t_{\text{post2}}$ . In this case, the presynaptic spike arrival ( $t_{post1}$ ) is 0.12 µs ahead of the postsynaptic, which means the postsynaptic spike arrives while the presynaptic spike is present. The profile of  $V_{\rm N2}$ and the consequent  $R_{\rm BRS}$  change are shown in Figure 7c. Upon arrival of the postsynaptic spike the voltage increases and crosses  $V_{\text{set}}$ , leading to a negative change in  $R_{\text{BRS}}$ . This negative change is maintained until the presynaptic spike terminates  $(t_{post1} \le t \le t_{pre2})$ . In the time range  $t_{pre2} < t \le t_{post2}$ , the absence of the presynaptic spike triggers the discharging of capacitor  $C_1$ . However, the presence of the bypass, due to the postsynaptic spike, maintains the higher  $|V_{N2}|$  ( $V_{N2} < 0$ ), which exceeds  $V_{\text{reset}}$ . Thus, a positive change in  $R_{\text{BRS}}$  is achieved during this time period. As can be seen in the lower panel of Figure 7c, the positive and negative voltage contributions to the change of  $R_{BRS}$  are almost identical, resulting in the negligible change in  $R_{BRS}$ .

- iii)  $\Delta t$ =0.52 µs:  $t_{pre1} < t_{post1} < t_{pre2} < t_{post2}$ . Since the termination of the postsynaptic spike is behind that of the presynaptic spike, the effect of the bypass on an increase in  $V_{\rm N2}$  and the consequent decrease in  $R_{\rm BRS}$  are not large. For the same reason,  $|V_{\rm N2}|$  ( $V_{\rm N2}$ <0) is elevated in  $t_{\rm pre2}$ <t< $t_{\rm post2}$ , resulting in a relatively large contribution of the negative voltage to  $R_{\rm BRS}$  change. The change of  $R_{\rm BRS}$  in total is therefore positive, which implies LTP.

In case of large interval between the pre and postsynaptic spikes, i.e. when  $\Delta t$  goes out of the LTD- / LTP-window, no change in  $R_{BRS}$  arises from the STDP protocol, since spikes separated by such large interval do not change  $|V_{\rm N2}|$  largely enough to differentiate it from case of low frequency stimulus (LFS) in the ADP. In Figure 7, a small offset of the  $\Delta PSP$  is seen outside the time-windows. This offset arises from the LFSinduced LTD at 50 kHz, which is consistent with the ADP behaviour shown in Figure 5a. This observation implies the crosstalk between the two different induction protocols. It is found that the STDP cannot be achieved in a high frequency range insomuch as no LTD in the STDP is observable. This Nanoscale Page 8 of 10

ARTICLE Journal Name

behaviour is well consistent with biological synaptic behaviour, which will be addressed in Discussion section.

Capacitor  $C_3$  and resistor  $R_4$  mostly determine the overlap between  $V_{\rm N1}$  and  $V_{\rm N4}$ , arising from the pre and the postsynaptic spike, respectively, in the time domain. Thus, the STDP behaviour, such as the centre of the transition zone bet

ween the LTD- and LTP-windows and the widths of the windows, can be designed by changing  $C_3$  and  $R_4$ .

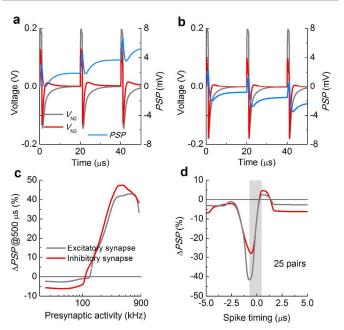

**Figure 8.**  $V_{\rm N2}$ ,  $V_{\rm N3}$ , and the consequent PSP profiles are plotted for (a) excitatory and (b) inhibitory synapses. In both cases, the calculations were conducted at a presynaptic activity of 50 kHz. The calculated (a) ADP and (b) STDP behaviours in both excitatory and inhibitory synapses are plotted. The  $\Delta$ PSP in (c) was read at 500  $\mu$ s at each presynaptic activity and that in (d) after 25 pairs of pre and postsynaptic spikes, corresponding to a read-out time of 500  $\mu$ s.

#### Synaptic excitation and inhibition

Diode  $D_1$  in the subcircuit in Figure 2f results in different RC time-constants depending on the polarity of  $V_{\rm N3}$  and the diode configuration. In addition, the polarity of diode  $D_1$  strongly affects  $V_{\rm N3}$  while charging and discharging capacitor  $C_2$ . While charging, a reverse bias voltage is applied to diode  $D_1$ , so that the resistance of diode  $D_1$  is high. Thus,  $V_{\rm N3}$  becomes positively high, which in turn increases the PSP, i.e.  $V_{\rm N5}$ . However, discharging capacitor  $C_2$  confronts a different condition; while discharging capacitor  $C_2$ , i.e.  $V_{\rm N3} < 0$ , electrons released from capacitor  $C_2$  see a much lower resistance of diode  $D_1$  as the diode is forward-biased. Consequently, the deviation of  $V_{N3}$ from the ground potential is much less than that in the charging case, meaning the contribution of discharging of capacitor  $C_2$  to the PSP is not as prominent as that of charging. Given this condition, the PSP evolves into a positive value. The evolution of PSP during LFS-induced LTD for excitatory synapse can be seen in Figure 8a. It is seen that the positive PSP evolution arises from the charging process rather than discharging process.

When it comes to inhibitory synapse, the evolution of the PSP should proceed towards negative values. This can be achieved by the contribution of discharging of capacitor  $C_2$  to the PSP evolution, which is dominant over that of charging. Flipping the polarity of diode  $D_1$  ensures a lower but still positive  $V_{\rm N3}$  value than the case of the diode polarity shown in Figure 2. That is, during charging of capacitor  $C_2$ , diode  $D_1$  is subject to a forward bias voltage, so that the resistance of diode  $D_1$  is low, leading to small  $V_{\rm N3}$  compared with the excitatory synapse case. However, during discharging, diode  $D_1$  is subject to a reverse bias voltage, so that electrons released from capacitor  $C_2$  confront high resistance through diode  $D_1$ . Thus,  $V_{\rm N3}$  shifts towards higher negative values. As a matter of fact, the negative maxima of  $V_{\rm N3}$  for excitatory and inhibitory cases are approximately -0.131 and -0.172 V, respectively. This mismatch between the contributions of charging and discharging of capacitor  $C_2$  leads to evolution of negative PSP, i.e. inhibitory synaptic behaviour. Indeed, as shown in Figure 8b (LFS-induced LTD case), the negative PSP evolution arises from the discharging process unlike the positive PSP evolution case (excitatory synaptic behaviour). The ADP and STDP calculations were performed on the inhibitory synapse and the results are plotted in Figures 8c and d. Note that  $C_2$  for the inhibitory synapse was 70 pF since the lower capacitance than that for the excitatory synapse gives a better correspondence with the excitatory synapse case. It is seen that both ADP and STDP behaviours are successfully implemented in the inhibitory synapse.

#### Unidirectional synaptic transmission

As illustrated in Figure 2, application of postsynaptic spikes to the circuit turns on the channel of the n-MOSFET. However, without presynaptic spikes, turning on the channel barely leads to the change of  $V_{\rm N2}$ , so that plasticity cannot solely be induced by the arrival of the postsynaptic spikes. This implies the fact that the synaptic transmission is unidirectional, i.e. from the presynaptic neuron to the post synaptic one. As stated earlier, the unidirectional synaptic transmission is a key feature of biological synapses, which defines pre and postsynaptic neurons. This unidirectionality cannot be achieved in two-terminal capacitor-type synapses employing memristive devices, given that bidirectional current flow is unquestionably required for long-term plasticity, i.e. LTD and LTP, in such artificial synapses.

#### **Discussion**

The STDP behaviour in our artificial synapse is activated at only low presynaptic activity. High presynaptic activity allows the ADP behaviour to be dominant over the STDP, so that only LTP is seen. The extinction of the STDP, i.e. LTD to be specific, at high presynaptic activity is understood in terms of the relative contributions of the charging and discharging effects to the voltage across the BRS, i.e.  $V_{\rm N2}$ . The positive

Page 9 of 10 Nanoscale

Journal Name ARTICLE

maximum of  $V_{\rm N2}$  shifts towards the negative side with respect to presynaptic activity as shown in Figure 4d. Thus, the lack of the positive voltage contribution to the change of  $R_{\rm BRS}$  prevents the LTD in the STDP despite the  $V_{\rm N2}$  elevation upon arrival of postsynaptic spikes at the n-MOSFET. In addition, as shown in Figure 7, the STDP behaviour at low presynaptic activity and timing out of the time-windows exhibits LTD. This LTD basically arises from the low presynaptic activity, 50 kHz, which triggers LTD in the ADP. Given these examples, the crosstalk between the protocols is estimated. Indeed, such crosstalk has been found in biological synapses, implying the good agreement of our artificial synapse with biological one.  $^{46}$

Several complex effects on plasticity induction, e.g. complex spike-train, such as triplet and quadruplet spike-train, effects on STDP<sup>47</sup> underpin a further research to be implemented. There may be much more effects that are required to be implemented in artificial synapses. Considering effects that play important roles in given applications of artificial synapses, the suggested circuit needs to be modified in the future. In addition, the detailed synaptic behaviours of the circuit can be fine-tuned by adjusting the components in the circuit. In particular, several components in the circuit as well as the height and width of an AP should be carefully chosen by taking into account the detailed resistive switching behaviour of the BRS. Further, artificial neurons should be of concern in optimizing the circuit components since the shape of the AP produced by the artificial neurons.

Regarding integration of this synaptic circuit, scalability is of significant concern. In comparison with the state-of-the-art CMOS synapses<sup>25, 26</sup>, a less number of circuit components, particularly transistor, in a unit synapse is beneficial in terms of fabrication cost. However, the obstacle to scalability is the requirement of such large capacitance ( $C_1$ : 0.8 nF) mainly for the ADP realization compared with the CMOS synapses<sup>25</sup>. Nonetheless, it should be emphasized that the focus of our synaptic circuit is on its functionality capable of multiprotocolinduced plasticity, and thus it cannot be directly compared with the CMOS synapses that implement particular protocols separately. A possible solution to such a large area of a unit synapse is probably use of high-k dielectrics or/and threedimensional capacitors, which enable a large increase in capacitance per unit area of a wafer. 48 Regarding power consumption, the synaptic circuit consumes approximately 1 mW/spike, and thus 1 nJ/spike. The ADP induction, shown in Figure 5, costs a minimum of 13 nJ (at 25 kHz, 12 spikes) and a maximum of 275 nJ (at 900 kHz, 450 spikes). Certainly, the energy consumption is larger than several CMOS synapses, e.g. recently reported CMOS synapse implementing STDP, which consumes 0.37 pJ/spike.<sup>27</sup> Thus, a further optimization of the circuit is required for minimization of synapse area as well as energy consumption, which is indeed beyond the scope of this work. Thus, we leave the question open for the moment.

The behaviour of the BRS as the key component of the proposed synaptic circuit has a significant impact on synaptic plasticity of the circuit in detail. That is, different BRS (memristor) models result in differences in detailed synaptic

behaviour. Therefore, a proper BRS model should be chosen by taking into account the experimental switching behaviour of the BRS under consideration. Other types of BRSs than the Pt/GeSe<sub>x</sub>/Ag switch can be utilized in the synaptic circuit with optimal values of the circuit components. Accordingly, the BRS model is required to be replaced by that reflecting the reality of the BRS in use. Since the first suggestion of a BRS model by Strukov et al.<sup>49</sup> in 2008, the original model has been largely modified for the fidelity to the reality of BRSs.<sup>34, 50-52</sup> Recent review papers on BRS models well sort available models and their characteristics.<sup>53, 54</sup>

#### **Conclusions**

We suggested an electrical circuit able to encode presynaptic activity and timing of pre and postsynaptic spikes. The circuit also satisfies general features of biological synapses such as excitatory and inhibitory synaptic behaviours unidirectional, i.e. pre → postsynaptic neuron, synaptic transmission. The calculation results let us know the feasibility of the circuit as an artificial synapse, regarding the successful implementation of ADP and STDP behaviours. Of course, synaptic functionalities required to be implemented in artificial synapses depend on the purposes of the systems including the synapses, so that only particular functionalities rather than general ones are necessary to be realized. 21, 28, 30, 31 However, for the moment, it is of significant importance to achieve artificial synapses implementing general aspects of biological synapses, which can be versatile. Thus, they can be used in various neuromorphic systems for diverse purposes.

#### **Acknowledgements**

D.S.J. acknowledges a Korea Institute of Science and Technology grant (grant no. 2Z04030). O.K. appreciates the support of an Australian Research Council (ARC) Discovery Project grant (no. DP140103448) from the University of Melbourne.

#### Notes and references

- <sup>a</sup> Electronic Materials Research Centre, Korea Institute of Science and Technology, 136-791 Seoul, Republic of Korea. \*E-mail: <a href="mailto:dsjeong@kist.re.kr">dsjeong@kist.re.kr</a>; Fax: +82 2 9585509; Tel: +82 2 9585490

- <sup>b</sup> Department of Materials Science and Engineering, Seoul National University of Science and Technology, 139-743 Seoul, Republic of Korea.

- <sup>c</sup> School of Electrical and Computer Engineering, Royal Melbourne Institute of Technology, VIC 2001, Australia.

- <sup>d</sup> Department of Materials Science and Engineering and Inter-university Semiconductor Research Centre, Seoul National University, 151-744 Seoul, Republic of Korea.

Electronic Supplementary Information (ESI) available: See DOI: 10.1039/b000000x/

ARTICLE Journal Name

- D. S. Jeong, I. Kim, M. Ziegler and H. Kohlstedt, RSC Adv., 2013, 3, 3169-3183.

- A. Pouget, P. Dayan and R. Zemel, Nat. Rev. Neurosci., 2000, 1, 125-132

- W. J. Ma, J. M. Beck, P. E. Latham and A. Pouget, *Nat. Neurosci.*, 2006, 9, 1432-1438.

- B. B. Averbeck, P. E. Latham and A. Pouget, Nat. Rev. Neurosci., 2006, 7, 358-366.

- 5. C. Mead, Proc. IEEE, 1990, 78, 1629-1636.

- S. Deneve, P. E. Latham and A. Pouget, *Nat. Neurosci.*, 1999, 2, 740-745

- S. Deneve, P. E. Latham and A. Pouget, *Nat. Neurosci.*, 2001, 4, 826-831.

- 8. R. C. Malenka and R. A. Nicoll, Science, 1999, 285, 1870-1874.

- S. Bissiere, M. Zelikowsky, R. Ponnusamy, N. S. Jacobs, H. T. Blair and M. S. Fanselow, *Science*, 2011, 331, 87-91.

- 10. H. Ishiwara, Jpn. J. Appl. Phys., 1993, 32, 442.

- Y. Nishitani, Y. Kaneko, M. Ueda, T. Morie and E. Fujii, *J. Appl. Phys.*, 2012, 111, 124108.

- D. Kuzum, R. G. D. Jeyasingh, B. Lee and H. S. P. Wong, *Nano Lett.*, 2011, 12, 2179-2186.

- M. Suri, O. Bichler, D. Querlioz, B. Traore, O. Cueto, L. Perniola, V. Sousa, D. Vuillaume, C. Gamrat and B. DeSalvo, *J. Appl. Phys.*, 2012, 112, 054904-054910.

- P. Krzysteczko, J. Münchenberger, M. Schäfers, G. Reiss and A. Thomas, Adv. Mater., 2012, 24, 762-766.

- H. Lim, I. Kim, J.-S. Kim, C. S. Hwang and D. S. Jeong, Nanotechnol., 2013, 24, 384005.

- S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder and W. Lu, *Nano Lett.*, 2010, 10, 1297-1301.

- 17. T. Chang, S.-H. Jo and W. Lu, ACS Nano, 2011, 5, 7669-7676.

- T. Ohno, T. Hasegawa, T. Tsuruoka, K. Terabe, J. K. Gimzewski and M. Aono, *Nature Mater.*, 2011, 10, 591-595.

- M. Ziegler, R. Soni, T. Patelczyk, M. Ignatov, T. Bartsch, P. Meuffels and H. Kohlstedt, Adv. Funct. Mater., 2012, 22, 2744-2749.

- Y. Li, Y. Zhong, J. Zhang, L. Xu, Q. Wang, H. Sun, H. Tong, X. Cheng and X. Miao, Sci. Rep., 2014, 4, 4906.

- S. Yu, B. Gao, Z. Fang, H. Yu, J. Kang and H. S. P. Wong, Adv. Mater., 2013, 25, 1774-1779.

- 22. A. Subramaniam, K. D. Cantley, G. Bersuker, D. Gilmer and E. M. Vogel, *IEEE Trans. Nanotechnol.*, 2013, **12**, 450-459.

- 23. G. Indiveri, E. Chicca and R. Douglas, *IEEE Trans. Neural Netw.*, 2006, **17**, 211-221.

- M. Ziegler, M. Oberlander, D. Schroeder, W. H. Krautschneider and H. Kohlstedt, *Appl. Phys. Lett.*, 2012, 101, 263504.

- M. R. Azghadi, N. Iannella, S. F. Al-Sarawi, G. Indiveri and D. Abbott, *Proc. IEEE*, 2014, 102, 717-737.

- 26. G. Indiveri, B. Linares-Barranco, T. J. Hamilton, A. van Schaik, R. Etienne-Cummings, T. Delbruck, S.-C. Liu, P. Dudek, P. Häfliger, S. Renaud, J. Schemmel, G. Cauwenberghs, J. Arthur, K. Hynna, F. Folowosele, S. Saighi, T. Serrano-Gotarredona, J. Wijekoon, Y. Wang and K. Boahen, Front. Neurosci., 2011, 5, 1-23.

- J. M. Cruz-Albrecht, M. W. Yung and N. Srinivasa, *IEEE Trans. Biomed. Circuits Syst.*, 2012, 6, 246-256.

- S. Gaba, P. Sheridan, J. Zhou, S. Choi and W. Lu, *Nanoscale*, 2013, 5, 5872-5878.

- O. Kavehei, E. Linn, L. Nielen, S. Tappertzhofen, E. Skafidas, I. Valov and R. Waser, *Nanoscale*, 2013, 5, 5119-5128.

- 30. G. S. Snider, Nanotechnol., 2007, 18, 365202.

- 31. G. S. Snider, Nanotechnol., 2011, 22, 015201.

- 32. Y. V. Pershin and M. Di Ventra, Phys. Rev. E, 2013, 88, 013305.

- 33. Y. V. Pershin and M. Di Ventra, Phys. Rev. E, 2011, 84, 046703.

- Z. Biolek, D. Biolek and V. Biolkova, *Radioengineering*, 2009, 18, 210-214.

- B. J. Sheu, D. L. Scharfetter, P. K. Ko and M.-C. Jeng, *IEEE J. Solid-State Circuits*, 1987, 22, 558-566.

- W. Lu, D. S. Jeong, M. N. Kozicki and R. Waser, MRS Bull., 2012, 37, 124-130.

- S. Menzel, U. Böttger and R. Waser, J. Appl. Phys., 2012, 111, 014501.

- S. Menzel, S. Tappertzhofen, R. Waser and I. Valov, *Phys. Chem. Chem. Phys.*, 2013, 15, 6945-6952.

- E. I. Moser, K. A. Krobert, M.-B. Moser and R. G. M. Morris, Science, 1998, 281, 2038-2042.

- E. I. Moser and M.-B. Moser, *Neurosci. Biobehav. Rev.*, 1999, 23, 661-672.

- E. Bienenstock, L. Cooper and P. Munro, J. Neurosci., 1982, 2, 32-48.

- 42. E. Oja, J. Math. Biol., 1982, 15, 267-273.

- 43. G.-q. Bi and M.-m. Poo, J. Neurosci., 1998, 18, 10464-10472.

- 44. Daniel E. Feldman, Neuron, 75, 556-571.

- 45. Y. Dan and M.-M. Poo, Physiol. Rev., 2006, 86, 1033-1048.

- P. J. Sjöström, G. G. Turrigiano and S. B. Nelson, *Neuron*, 2001, 32, 1149-1164.

- 47. R. C. Froemke and Y. Dan, Nature, 2002, 416, 433-438.

- S. K. Kim, S. W. Lee, J. H. Han, B. Lee, S. Han and C. S. Hwang, *Adv. Funct. Mater.*, 2010, 20, 2989-3003.

- D. B. Strukov, G. S. Snider, D. R. Stewart and R. S. Williams, Nature, 2008, 453, 80.

- T. Chang, S.-H. Jo, K.-H. Kim, P. Sheridan, S. Gaba and W. Lu, *Appl. Phys. A*, 2011, **102**, 857-863.

- K. Eshraghian, O. Kavehei, K.-R. Cho, J. M. Chappell, A. Iqbal, S. F. Al-Sarawi and D. Abbott, *Proc. IEEE*, 2012, 100, 1991-2007.

- M. D. Pickett, D. B. Strukov, J. L. Borghetti, J. J. Yang, G. S. Snider,

D. R. Stewart and R. S. Williams, *J. Appl. Phys.*, 2009, 106, 074508.

- E. Linn, A. Siemon, R. Waser and S. Menzel, *IEEE Trans. Circuits Syst. I, Reg. Papers*, 2014, 61, 2402-2410.

- A. Ascoli, F. Corinto, V. Senger and R. Tetzlaff, *IEEE Circuits Syst. Mag.*, 2013, 13, 89-105.