### Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

www.rsc.org/nanoscale

## Direct growth of patterned graphene on SiO<sub>2</sub> substrates without the use of catalysts or lithography<sup>†</sup>

Yong Seung Kim<sup>1,2</sup>, Kisu Joo<sup>3</sup>, Sahng-Kyoon Jerng<sup>1,2</sup>, Jae Hong Lee<sup>1,2</sup>, Euijoon Yoon<sup>4</sup>, Seung-Hyun Chun<sup>1,2,\*</sup>

1 Graphene Research Institute, Sejong University, Seoul 143-747, Korea

2 Department of Physics, Sejong University, Seoul 143-747, Korea

<sup>3</sup> Department of Nano Science and Technology, Graduate School of Convergence Science and Technology, Seoul National University, Suwon 443-270, Korea

<sup>4</sup> Department of Materials Science and Engineering, Seoul National University, Seoul 151-744, Korea

<sup>†</sup>Electronic supplementary information (ESI) is available: effect of growth time, methane flow, and plasma power on synthesized graphene.

\* Author to whom correspondence should be addressed. Electronic mail: <u>schun@sejong.ac.kr</u>.

#### ABSTRACT

We demonstrate one-step fabrication of patterned graphene on SiO<sub>2</sub> substrates through a process free from catalysts, transfer, and lithography. By simply placing a shadow mask during the plasma enhanced chemical vapor deposition (PECVD) of graphene, an arbitrary shape of graphene can be obtained on SiO<sub>2</sub> substrate. The formation of graphene underneath the shadow mask was effectively forbidden by low-temperature, catalyst-free process. The growth conditions were optimized to form polycrystalline graphene on SiO<sub>2</sub> substrates and the crystalline structure was characterized by Raman spectroscopy and transmission electron microscopy (TEM). Patterned graphene on SiO<sub>2</sub> functions as a field-effect device by itself. Our method is compatible with present device processing techniques and should be highly desirable for the proliferation of graphene applications.

KEYWORDS: Graphene, catalyst-free synthesis, PECVD, low temperature, SiO<sub>2</sub>

Graphene is one of the most promising materials for applications in next-generation electronic devices because of its unique properties, such as high carrier mobility, high transmittance and excellent mechanical flexibility.<sup>1</sup> Large-area graphene, synthesized on metal surface by chemical vapor deposition (CVD), has spurred its applications in such devices.<sup>2</sup> However, the use of a metallic catalyst underneath the graphene layer inevitably requires a transfer process,<sup>3-5</sup> which is not compatible with standard processes in the semiconductor industry. Furthermore, multiple process steps, including coating with organic materials for catalyst etching and transfer, photo/e-beam lithography, and wet/dry etching, complicate the application of graphene to electronic devices. These processes are time consuming and, more importantly, cause degradation of graphene due to mechanical damage and chemical contamination which bring unwanted disorders to the devices. To achieve transfer-free synthesis of graphene, there have been attempts to grow graphene films at the interface between Cu<sup>6</sup> or Ni<sup>7, 8</sup> and the underlying dielectrics either by diffusing carbon atoms through the grain boundaries, or by using a selfassembled monolayer of carbon materials squeezed between a catalytic metal and a substrate<sup>9</sup>. However these methods still require catalytic metals that must be etched away. Therefore, it is desirable to pursue alternative fabrication method for graphene devices.

So far, the metal-catalyst-free synthesis of graphene has been tried by thermal CVD (or molecular beam epitaxy) on sapphire,<sup>10-12</sup> quartz,<sup>11, 13</sup> SiO<sub>2</sub>,<sup>13-16</sup> MgO,<sup>17-20</sup> GaN,<sup>21</sup> ZrO<sub>2</sub>,<sup>18</sup> Si<sub>3</sub>N<sub>4</sub>,<sup>22</sup> and HfO<sub>2</sub>,<sup>23</sup> which result in graphitic carbon or nanocrystalline graphene. Recently, relatively high quality graphene films were synthesized by thermal CVD at atmospheric pressure<sup>24-26</sup>, showing the possibility of catalyst-free graphene growth.

However, with these high growth temperatures  $(1100 \sim 1600 \text{ °C})$  it is not possible to utilize the benefits of direct growth, *i.e.*, integration with existing technologies.

In this article, we demonstrate direct formation of patterned graphene on SiO<sub>2</sub> substrates without using catalysts or lithography. A pre-defined metal shadow mask is used as the pattern template in PECVD graphene growth. This process is transfer-free, catalyst-free, lithography-free, all dry, simple to implement, and scalable for batch production. This method also allows us to prepare multiple samples with different shapes in a matter of hours. The patterned graphene was characterized by Raman spectroscopy, TEM, and atomic force microscopy (AFM) to investigate its crystallinity and nanoscale morphology. The results were fed back to modify the growth conditions for improved graphene quality. Hall-bar patterned graphene, fabricated instantly on SiO<sub>2</sub>, is investigated to assess the electrical properties of the graphene sheets with respect to the applied gate voltages and demonstrates the simplicity of our method.

#### II. EXPERIMENTAL PROCEDURES

#### Growth

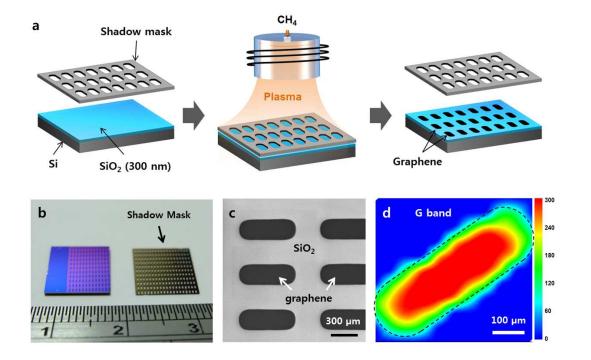

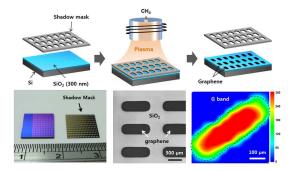

The substrate used in this study is  $SiO_2(300 \text{ nm})/n$ -Si wafer purchased from Dasom RMS. As schematically illustrated in Figure 1a, a shadow mask made of stainless steel is placed on top of the substrate and the growth of graphene is done by flowing mixing gas of methane and hydrogen in a PECVD system. Prior to the graphene growth,  $O_2$  gas was introduced into the chamber at a flow rate of 40 standard cubic centimeters per minute (sccm) and discharged at an RF power of 50 W for 3 minutes to remove any organic materials contaminating the surface. During the graphene growth stage, RF plasma was

generated under a continuous flow of hydrogen (H<sub>2</sub>, 20 sccm) and methane (CH<sub>4</sub>, 2 sccm), while the pressure was kept at 10 mTorr. The resolutions of mass flow controllers are 1 sccm for hydrogen and 0.1 sccm for methane, respectively. The growth temperature was varied from 500 to 900 °C. Subsequently, the sample was cooled down rapidly to room temperature at a cooling rate of 3 °C/s by turning off the heating power.

#### Characterization

Raman spectroscopy (Renishaw, inVia) with an excitation wavelength of 514.5 nm was used to measure the crystallinity of graphene films. Surface morphology of the samples was evaluated by a commercial AFM (PSIA, XEI100). Scanning electron microscope (SEM) images were taken by a Tescan VEGA-3 system. High-resolution transmission electron microscopy (HR-TEM, JEOL JEM-2100F) was used to investigate the microstructure of graphene (operating at 200 kV). Electrical properties were measured by using standard four-probe method.

#### **III. RESULTS AND DISCUSSION**

Patterned few-layer graphene is obtained in one-go process by placing a shadow mask on the substrate during the graphene growth. Optical and SEM images of directly grown graphene on a SiO<sub>2</sub> substrate are presented in Figure 1b and 1c, respectively. Raman map of G band in Figure 1d indicates that the graphene growth is forbidden underneath the masked area. This is the salient feature of direct graphene growth without catalysts. In the typical CVD growth on metals, patterned graphene has been formed in two ways. One is by photo/e-beam lithography after a series of graphene growth, catalyst etching, and transfer processes. The other is by stamped-transfer after the growth on

Nanoscale Accepted Manuscript

lithographically-defined metal pattern.<sup>27</sup> Some variants of transfer-free synthesis<sup>6, 7</sup> still need patterns defined by lithography and the catalyst etching process. In contrast, our method for graphene pattern does not require any chemicals which are detrimental to graphene.

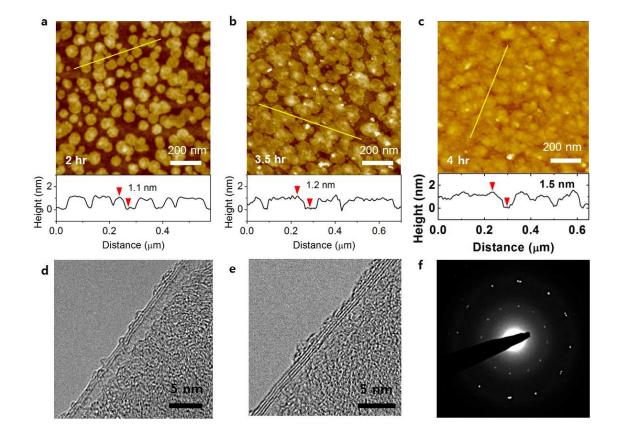

To investigate the growth mechanism in detail, a time-dependent growth study was performed. Figure 2a–c shows AFM images of the as-grown graphene with different growth durations. The line profile of graphene nucleated on the substrate (Figure 2a) illustrates that the step height of the graphene is about ~1.1 nm. Continued growth enlarges the size of graphene grains, and they coalesce into larger ones (Figure 2b). Finally, interconnected graphene networks are formed with thickness of ~1.5 nm (Figure 2c). In Raman spectroscopy, due to increased thickness and interaction between the layers, the ratio of 2D/G peak intensity decreased a bit with longer growth duration (Figure S1).<sup>28</sup> To investigate the microstructures, polycrystalline graphene films are transferred onto a TEM grid by etching the substrate. High-resolution TEM images in Figure 2d–e and selected-area electron diffraction (SAED) pattern in Figure 2f clearly show that layered and hexagonal crystalline structures of graphene films are synthesized on SiO<sub>2</sub> substrates.

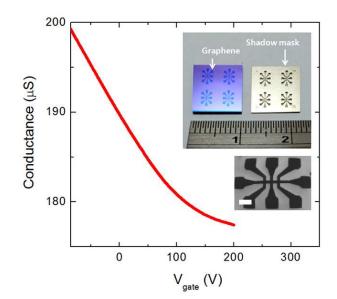

The one-step fabricated graphene pattern on SiO<sub>2</sub> can be immediately used as fieldeffect devices. The upper inset of Figure 3 shows an optical image of Hall-bar patterned graphene on a SiO<sub>2</sub> substrate, prepared by simply placing a shadow mask during the growth. The channel width and the length of Hall-bar structure are well-defined as 100  $\mu$ m and 300  $\mu$ m, respectively (lower inset of Figure 3). The sheet resistance and corresponding optical transmittance of graphene is obtained as 1.4 kΩ/square and ~75 %,

respectively (a double-sided polished sapphire substrate was used as a reference for optical transmittance measurement). Since the graphene is already on SiO<sub>2</sub>/Si, we can tune the electrical characteristics via a gate voltage ( $V_{gate}$ ) applied to the bottom of the substrate. As shown in Figure 3, a change of curvature near  $V_{gate} = 100$  V is noticed, which implies a possible ambipolar behavior of the film. At zero-bias, the hole density and the mobility are obtained as  $1.3 \times 10^{13}$  cm<sup>-2</sup> and 105 cm<sup>2</sup>/Vs, respectively. Although the mobility is still lower than that of graphene grown on a metal catalyst (~4,000 cm<sup>2</sup>/Vs)<sup>29</sup> and on SiO<sub>2</sub> at 1100 °C (470–530 cm<sup>2</sup>/Vs)<sup>25</sup>, the value is much higher than those obtained from chemically reduced graphene oxide films (~1 cm<sup>2</sup>/Vs)<sup>30</sup> and catalyst-free nanocrystalline graphene (1–40 cm<sup>2</sup>/Vs).<sup>12, 14</sup>

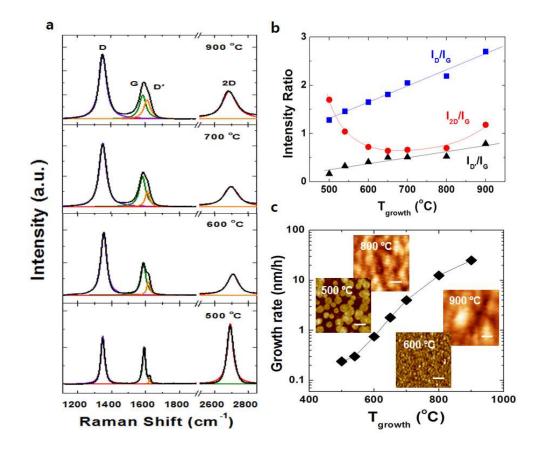

Now that we have shown the merits of direct growth of patterned graphene, it is necessary to improve the graphene quality by optimizing the growth conditions. First, we investigated the temperature dependence of graphene synthesis on SiO<sub>2</sub> substrates. Figure 4a shows Raman spectra of graphene films grown without catalysts at various temperatures ranging from 500 to 900 °C. When the temperature is higher than 600 °C, the growth results in nanographene, which has been typically seen in other studies,<sup>13, 15, 16, 12, 26, 31</sup> as evidenced by the presence of D peak at ~1350 cm<sup>-1</sup>, G at ~1580 cm<sup>-1</sup>, D' at ~1620 cm<sup>-1</sup> and relatively smaller 2D at ~2680 cm<sup>-1</sup>. On the other hand, when the growth temperature is lower than 600 °C, there is a drastic enhancement of 2D peak intensity as the growth temperature decreases (Figure 4a, b). At 500 °C, the intensity of 2D peak is much larger than that of G peak, indicating the transition of nanographene to polycrystalline graphene.<sup>32, 33</sup> The corresponding decrease of D peak intensity at the lower growth

temperature is not consistent with what we have observed in typical CVD graphene grown on metallic catalysts, where the better graphene films are obtained at the higher growth temperatures. We note that the growth rate of graphene depends strongly on the growth temperature (Figure 4c). The fast growth rates at high temperatures may cause the nucleation sites to increase too fast and lead to three-dimensional growth rather than layer-by-layer growth. As a control, we reduced the flow of methane from 2 to 1 sccm at a growth temperature of 600 °C. Surprisingly, in these conditions the Raman spectra show a significant enhancement of 2D peak intensity and a reduction of D peak intensity (Figure S2), implying that the growth rate of graphene could be the critical parameter for determining the quality of synthesized graphene on catalyst-free SiO<sub>2</sub> substrates. Interestingly our growth rate at 500 °C is similar to that of direct thermal CVD growth at  $1100 \,{}^{\circ}\mathrm{C}^{25}$ . Although all the growth parameters are totally different to ours, the results are similar to ours. This observation implies that the growth rate is an important factor for the synthesis of high-quality graphene directly on SiO<sub>2</sub>. The AFM images (insets of Figure 4c) show that the surface of graphene synthesized at 800 and 900 °C are very rough with average roughness about 2.5 and 3.2 nm, respectively. In contrast, relatively flat surface morphologies are observed at the low growth temperature of 500 and 600 °C with average roughness about 0.25 and 0.20 nm, respectively. These observations imply that the growth rate is an important factor for the synthesis of graphene directly on  $SiO_2$ . When the temperature is lower than 500 °C, the growth is so slow that a continuous layer of graphene is not formed within the growth time.

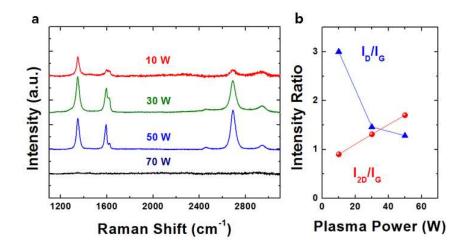

The plasma power is also an important parameter that affects the direct graphene growth. Initially the crystallinity increases with higher plasma powers (Figure 5a, b).

However, when the plasma power is higher than 70 W, no graphene is synthesized. The ICP reactor is known to offer high ionization efficiency compared to DC or RF capacitive discharges.<sup>34</sup> In our system, more than 40% of incoming methane is dissociated into various species, such as  $CH_x$ ,  $C_2H_y$ , H, H<sub>2</sub>, etc., at plasma powers of 50 W (Fig. S3a). The dissociation rate of methane can be tuned by plasma power, affecting the initial stage of graphene growth. High amount of carbon-containing radicals  $(CH_x, C_2H_y)$  increase the growth rate of graphene, but high amount of hydrogen species (H, H<sub>2</sub>) decrease the growth rate by etching the carbon atoms.<sup>35, 36</sup> Fig. S3b–e show AFM images of graphene grains synthesized for 3 hours at 500 °C under different plasma powers. The sizes of the graphene grains are relatively smaller at lower (<10 W) and higher (>70 W) plasma powers, which can be attributed to the reduced supply of carbon-containing radicals and the etching effect of carbon atoms by hydrogen species, respectively. However, the growth becomes faster at optimal plasma powers (30–50 W) due to the increased supply of carbon-containing radicals and the weakened etching effect. These observations show the importance of fine tuning the growth parameters in catalyst-free PECVD and further growth optimization by the control of unexplored growth parameters, such as the partial pressure and flow of hydrocarbon, may lead to smaller defect density and higher crystallinity. Lowering the growth temperature even below 500 °C is another direction so that direct graphene growth on flexible organic substrates is possible.

#### IV. CONCLUSION

In summary, we have demonstrated a transfer-free, catalyst-free, and lithography-free method to define graphene patterns on SiO<sub>2</sub>/Si substrates by simply placing a shadow

mask during the growth. Since the underlying doped Si substrate functions as a back gate, the patterned graphene on  $SiO_2$  can be directly used as field-effect devices. Our results suggest that graphene patterns can be incorporated into desired substrates by a single process. Therefore, in a variety of graphene applications, this method can replace the complex fabrication processes of graphene growth on metal catalysts, catalyst-etching, transfer to the substrate, and lithography. Relatively low mobility of our graphene indicates that further studies are required to improve the crystalline quality of synthesized graphene, which could be achieved by further growth optimization. We believe that our

one-step method shows a promise for broad applications of graphene.

#### ACKNOWLEDGMENTS

This research was supported by the Priority Research Centers Program (2012-0005859), the Basic Science Research Program (2012-0007298, 2012-040278), the Center for Topological Matter in POSTECH (2011-0030786), and the Nanomaterial Technology Development Program (2012M3A7B4049888) through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (MEST). It was also supported by WCU Hybrid Materials Program (R31-2008-000-10075-0) and BK21 Program through National Research Foundation of Korea funded by the Ministry of Education, Science and Technology (MEST). It was also supported by WCU Hybrid Materials Program (R31-2008-000-10075-0) and BK21 Program through National Research Foundation of Korea funded by the Ministry of Education, Science and Technology, and by Technology Innovation Program (10035430) funded by the Ministry of Knowledge Economy.

#### References

- 1. A. K. Geim and K. S. Novoselov, *Nat Mater*, 2007, **6**, 183-191.

- S. Bae, H. Kim, Y. Lee, X. F. Xu, J. S. Park, Y. Zheng, J. Balakrishnan, T. Lei, H. R. Kim, Y. I. Song, Y. J. Kim, K. S. Kim, B. Ozyilmaz, J. H. Ahn, B. H. Hong and S. Iijima, *Nat Nanotechnol*, 2010, 5, 574-578.

- J. W. Suk, A. Kitt, C. W. Magnuson, Y. F. Hao, S. Ahmed, J. H. An, A. K. Swan,

B. B. Goldberg and R. S. Ruoff, *Acs Nano*, 2011, 5, 6916-6924.

- Y.-C. Lin, C.-C. Lu, C.-H. Yeh, C. Jin, K. Suenaga and P.-W. Chiu, *Nano Lett*, 2011, **12**, 414-419.

- X. S. Li, Y. W. Zhu, W. W. Cai, M. Borysiak, B. Y. Han, D. Chen, R. D. Piner, L. Colombo and R. S. Ruoff, *Nano Lett*, 2009, 9, 4359-4363.

- C. Y. Su, A. Y. Lu, C. Y. Wu, Y. T. Li, K. K. Liu, W. J. Zhang, S. Y. Lin, Z. Y. Juang, Y. L. Zhong, F. R. Chen and L. J. Li, *Nano Lett*, 2011, 11, 3612-3616.

- 7. Z. W. Peng, Z. Yan, Z. Z. Sun and J. M. Tour, Acs Nano, 2011, 5, 8241-8247.

- M. Zhou, H. Bi, T. Q. Lin, X. J. Lu, F. Q. Huang and J. H. Lin, *J Mater Chem A*, 2014, 2, 2187-2193.

- H. J. Shin, W. M. Choi, S. M. Yoon, G. H. Han, Y. S. Woo, E. S. Kim, S. J. Chae, X. S. Li, A. Benayad, D. D. Loc, F. Gunes, Y. H. Lee and J. Y. Choi, *Adv Mater*, 2011, 23, 4392-4397.

- 10. Y. Miyasaka, A. Nakamura and J. Temmyo, *Jpn J Appl Phys*, 2011, **50**, 04DH12.

- J. Sun, M. T. Cole, N. Lindvall, K. B. K. Teo and A. Yurgens, *Appl Phys Lett*, 2012, **100**, 022102.

- S. K. Jerng, D. S. Yu, Y. S. Kim, J. Ryou, S. Hong, C. Kim, S. Yoon, D. K.

Efetov, P. Kim and S. H. Chun, *J Phys Chem C*, 2011, **115**, 4491-4494.

- 13. K. B. Kim, C. M. Lee and J. Choi, *J Phys Chem C*, 2011, **115**, 14488-14493.

- J. Sun, N. Lindvall, M. T. Cole, T. Wang, T. J. Booth, P. Boggild, K. B. K. Teo, J. Liu and A. Yurgens, *J Appl Phys*, 2012, **111**, 044103.

- L. C. Zhang, Z. W. Shi, Y. Wang, R. Yang, D. X. Shi and G. Y. Zhang, *Nano Res*, 2011, 4, 315-321.

- H. Medina, Y.-C. Lin, C. Jin, C.-C. Lu, C.-H. Yeh, K.-P. Huang, K. Suenaga, J. Robertson and P.-W. Chiu, *Adv Funct Mater*, 2012, 22, 2123-2128.

- M. H. Rummeli, A. Bachmatiuk, A. Scott, F. Borrnert, J. H. Warner, V. Hoffman,

J. H. Lin, G. Cuniberti and B. Buchner, *Acs Nano*, 2010, 4, 4206-4210.

- A. Scott, A. Dianat, F. Borrnert, A. Bachmatiuk, S. S. Zhang, J. H. Warner, E.

Borowiak-Palen, M. Knupfer, B. Buchner, G. Cuniberti and M. H. Rummeli, *Appl Phys Lett*, 2011, **98**, 073110.

- S. Gaddam, C. Bjelkevig, S. P. Ge, K. Fukutani, P. A. Dowben and J. A. Kelber, J Phys-Condens Mat, 2011, 23, 072204.

- S.-K. Jerng, J. H. Lee, D. S. Yu, Y. S. Kim, J. Ryou, S. Hong, C. Kim, S. Yoon and S.-H. Chun, *J Phys Chem C*, 2012, **116**, 7380-7385.

- J. Sun, M. T. Cole, S. A. Ahmad, O. Backe, T. Ive, M. Loffler, N. Lindvall, E. Olsson, K. B. K. Teo, L. Johan, A. Larsson, A. Yurgens and A. Haglund, *Semiconductor Manufacturing, IEEE Transactions on*, 2012, 25, 494-501.

- J. Sun, N. Lindvall, M. T. Cole, K. B. K. Teo and A. Yurgens, *Appl Phys Lett*, 2011, 98, 252107.

- P. R. Kidambi, B. C. Bayer, R. S. Weatherup, R. Ochs, C. Ducati, D. V. Szabo and S. Hofmann, *Phys Status Solidi-R*, 2011, 5, 341-343.

- M. A. Fanton, J. A. Robinson, C. Puls, Y. Liu, M. J. Hollander, B. E. Weiland, M. LaBella, K. Trumbull, R. Kasarda, C. Howsare, J. Stitt and D. W. Snyder, *Acs Nano*, 2011, 5, 8062-8069.

- J. Y. Chen, Y. G. Wen, Y. L. Guo, B. Wu, L. P. Huang, Y. Z. Xue, D. C. Geng, D. Wang, G. Yu and Y. Q. Liu, *J Am Chem Soc*, 2011, 133, 17548-17551.

- 26. H. Bi, S. R. Sun, F. Q. Huang, X. M. Xie and M. H. Jiang, *J Mater Chem*, 2012, 22, 411-416.

- K. S. Kim, Y. Zhao, H. Jang, S. Y. Lee, J. M. Kim, K. S. Kim, J. H. Ahn, P. Kim, J. Y. Choi and B. H. Hong, *Nature*, 2009, 457, 706-710.

- A. Reina, X. T. Jia, J. Ho, D. Nezich, H. B. Son, V. Bulovic, M. S. Dresselhaus and J. Kong, *Nano Lett*, 2009, 9, 30-35.

- X. S. Li, W. W. Cai, J. H. An, S. Kim, J. Nah, D. X. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo and R. S. Ruoff, *Science*, 2009, **324**, 1312-1314.

- 30. G. Eda, G. Fanchini and M. Chhowalla, *Nat Nanotechnol*, 2008, **3**, 270-274.

- J. H. Hwang, V. B. Shields, C. I. Thomas, S. Shivaraman, D. Hao, M. Y. Kim, A.

R. Woll, G. S. Tompa and M. G. Spencer, *J Cryst Growth*, 2010, **312**, 3219-3224.

- 32. A. C. Ferrari and J. Robertson, *Phys Rev B*, 2000, **61**, 14095-14107.

- 33. A. C. Ferrari, Solid State Commun, 2007, 143, 47-57.

- L. Delzeit, I. McAninch, B. A. Cruden, D. Hash, B. Chen, J. Han and M. Meyyappan, *J Appl Phys*, 2002, 91, 6027-6033.

- I. Vlassiouk, M. Regmi, P. Fulvio, S. Dai, P. Datskos, G. Eres and S. Smirnov, Acs Nano, 2011, 5, 6069-6076.

- 36. Y. S. Kim, J. H. Lee, Y. D. Kim, S.-K. Jerng, K. Joo, E. Kim, J. Jung, E. Yoon, Y. D. Park, S. Seo and S.-H. Chun, *Nanoscale*, 2013, 5, 1221-1226.

**Figure 1.** (a) Schematic diagram of one-step fabrication method to obtain patterned graphene on dielectric substrates without additional transfer or lithography process. (b) Photograph showing the shadow mask and the graphene on  $SiO_2$  after the growth. The mask was made of 150 um-thick stainless steel. (c) SEM image and (d) Raman map of the graphene pattern.

**Figure 2.** AFM height topography and height profile of graphene synthesized for (a) 2, (b) 3.5 and (c) 4 hours at 500 °C under plasma power of 50 W. (d), (e) HRTEM images of graphene edges on a TEM grid. (f) SAED pattern of graphene, showing hexagonal patterns.

**Figure 3.** Back-gate voltage dependence of sheet conductance. At zero-bias, the hole density and the mobility are  $1.3 \times 10^{13}$  cm<sup>-2</sup> and 105 cm<sup>2</sup>/Vs, respectively. Upper inset shows photograph of shadow mask and patterned graphene on SiO<sub>2</sub> after the growth. Lower inset is a SEM image of the Hall-bar patterned graphene on SiO<sub>2</sub> defined by shadow mask. Scale bar = 500 µm.

**Figure 4.** (a) Raman spectra (514 nm laser wavelength), (b) intensity ratios of D, D' and 2D peaks to the G peak of graphene films grown for 2 hours at various temperatures. (c) Temperature dependence of growth rate. Insets shows AFM image of synthesized graphene at various temperature. Scale bar = 100 nm.

**Figure 5.** (a) Raman spectra and (b) intensity ratios of D and 2D peaks to the G peak of graphene films grown at 500 °C for 3 hours with different plasma power.

TOC

Patterned graphene is obtained on SiO<sub>2</sub> substrates without catalyst and lithography by simply placing a shadow mask during the growth process.