Cite this: Mater. Adv., 2026,

7, 1357

## A brief overview of anodic memristors: fundamentals, classification and properties

Elena Atanasova,<sup>a</sup> Andreas Greul,<sup>a</sup> Achim Walter Hassel,<sup>ab</sup> Andrea Zaffora,<sup>ab</sup> Monica Santamaria<sup>cd</sup> and Andrei Ionut Mardare<sup>ab\*</sup>

Memristors have emerged as a promising technology for next-generation memory and neuromorphic computing due to their ability to mimic synaptic behavior and retain previous resistance states, while showing potential as future energy-efficient devices. Various materials have been investigated for resistive switching applications, including valve metals, Hf, Nb, Ta, Ti, etc., which stand out due to their ability to form stable oxide layers with tuneable oxide growth and ability for controlled defect engineering. These properties are crucial for obtaining reliability and scalability in memristive devices. A significant advantage of anodic memristor fabrication in comparison to other methods is the anodization process. It is a simple, cost-effective electrochemical method, which can ensure precise control over the oxide thickness, composition, and intrinsic defect structuring. By adjusting anodization parameters, it is possible to influence oxygen vacancy distribution and interfacial properties, thus enhancing resistive switching capabilities such as formation voltage, switching voltage, endurance, and retention. This review provides a detailed evaluation of memristive devices based on anodic oxides, from their fabrication, resistive switching mechanisms, and defect structuring to applications in memory and neuromorphic computing. Furthermore, a comparison of various valve metals and their alloys is presented, identifying their individual advantages and limitations in memristive performance.

Received 22nd October 2025,

Accepted 4th December 2025

DOI: 10.1039/d5ma01223f

rsc.li/materials-advances

<sup>a</sup> Institute of Chemical Technology of Inorganic Materials (TIM), Johannes Kepler University Linz, Altenberger Str. 69, 4040, Linz, Austria. E-mail: andrei.mardare@jku.at

<sup>b</sup> Danube Private University, Steiner Landstraße 124, 3500 Krems an der Donau, Austria

<sup>c</sup> Engineering Department, University of Palermo, Viale delle Scienze, 90128 Palermo, Italy

<sup>d</sup> National Institute for Lasers, Plasma and Radiation Physics, 077125 Magurele, Romania

Elena Atanasova

*Elena Atanasova is a chemical engineer working in the field of memristive oxide thin films based on valve metals under the supervision of Prof. A. I. Mardare. She obtained her master's degree in chemical technology and is currently pursuing her PhD at the Institute of Chemical Technology of Inorganic Materials at Johannes Kepler University Linz. Her doctoral research focuses on the combinatorial development and electrochemical formation of anodic memristors, with particular emphasis on memristive sensors and their applications in fields such as neuromorphic computing and advanced medical materials.*

Andreas Greul

*Andreas Greul studied chemical engineering at Johannes Kepler University Linz. During his master's thesis at the Institute of Chemical Technology of Inorganic Materials, he investigated the corrosion behaviour of titanium-based medical implants. As a PhD candidate, under the supervision of Prof. Hassel, his research focuses on the electrochemical properties of valve metals and their oxides. Within a European research project, he is involved in the development and testing of advanced medical materials. In his PhD work, he further collaborates with Prof. Mardare's research group on the development and characterization of anodically formed valve-metal-oxide memristive materials.*

## 1. Introduction

Memristors, also known as memory resistors, have become one of the most important advancements in non-volatile memory technologies. Memristors were first predicted in 1971 by Leon Chua, as the missing fourth fundamental passive circuit element, along with resistors, capacitors, and inductors.<sup>1</sup> Memristors can store information based on their resistive states, offering memory and logic in a single device. Their resistance can be regulated by the history of applied voltage or current.<sup>2</sup> This concept remained mostly theoretical until 2008, when Strukov *et al.* at HP Labs reported resistive switching in nanoscale TiO<sub>2</sub> crossbar arrays inspiring modern research on the topic. Since then, over the last two decades, memristor

development has gained significant interest, due to their potential applications in fields such as neuromorphic computing,<sup>3</sup> artificial intelligence,<sup>4</sup> and data storage.<sup>5</sup> Within this broad field, anodic memristors are relatively new devices, whose oxides are grown by electrochemical anodization of a valve metal, rather than by using vacuum techniques, such as sputtering and atomic layer deposition (ALD). One of the first anodic memristors was reported in 2010 by Miller *et al.*, whose devices showed bipolar memristive switching in thin TiO<sub>2</sub>.<sup>6</sup> Building on these studies, many research groups have since explored anodization parameters in order to optimize anodic memristive devices and materials. This is done by varying the oxide thickness, electrolyte composition, applied voltage, time, and temperature to tune switching voltages, ON/OFF ratios,

**Achim Walter Hassel**

Austria. He was a project leader of the Christian Doppler Laboratory for Combinatorial Oxide Chemistry and several EU projects. His research interests are in the field of combinatorial and electrochemical materials science.

*Achim Walter Hassel received his PhD in 1997 from the University of Düsseldorf, Germany. After that, he was an Alexander von Humboldt and JSPS-fellow until 1999 at Hokkaido University (Sapporo, Japan). During 2000–2009, he was the head of the Electrochemistry and Corrosion group at the Max-Planck-Institute for Iron Research and the scientific director of the IMPRS Surmat. Since 2009, he has held a chair in chemistry at Johannes Kepler University Linz,*

**Andrea Zaffora**

*treatments for various applications and on the design of nanostructured electrodes for sustainable hydrogen production through water electrolysis and electroreforming processes.*

*Andrea Zaffora is an assistant professor in the Engineering Department at the University of Palermo. He earned a master's degree in chemical engineering in 2014 and completed a PhD in information and communication technologies in 2018, at the University of Palermo, with a dissertation titled "Electrochemically Prepared High-k Thin Films for Resistive Switching Devices." His current research focuses on electrochemical surface*

**Monica Santamaria**

coordinated European, national, and industry-funded projects. Her awards include the ISE Hans-Jürgen Engell Prize (2006) and a JSPS Research Fellowship (2019). She is the President of the SCI Electrochemistry Division and Treasurer of the International Society of Electrochemistry.

*Monica Santamaria received her PhD in electrochemical engineering from Politecnico di Milano in 2001 after a MSc in chemical engineering at the University of Palermo. Since 2010, she is a full professor of applied electrochemistry at the University of Palermo, leading research on passive films and functional oxides, low-temperature PEM fuel cells, and (photo)electrochemical processes for green hydrogen and value-added chemicals. She has*

**Andrei Ionut Mardare**

*at Johannes Kepler University Linz, Austria. His current research interests include ultra-thin anodic oxides on valve metals and their dynamic processes at the atomic scale.*

*Andrei Ionut Mardare is a physicist working in the field of thin film combinatorial development of inorganic materials. He studied physics at the University of Bucharest, Romania, and conducted his doctoral work at Max-Planck Institute for Iron Research in Düsseldorf, Germany. He received his PhD degree in physics in 2009 from Ruhr University Bochum (RUB) Germany, and then he joined the Institute of Chemical Technology of Inorganic Materials*

endurance, and device-to-device variability. These efforts have jointly proven anodic oxidation as a versatile method for fabrication of memristive devices and provided an alternative route toward simplified fabrication. More recently, combinatorial studies on valve metal alloys have enabled systematic screening of memristive behaviour in the corresponding mixed anodic oxides, allowing for a fast route to map the composition to property relationships and further identify promising material systems.<sup>7</sup>

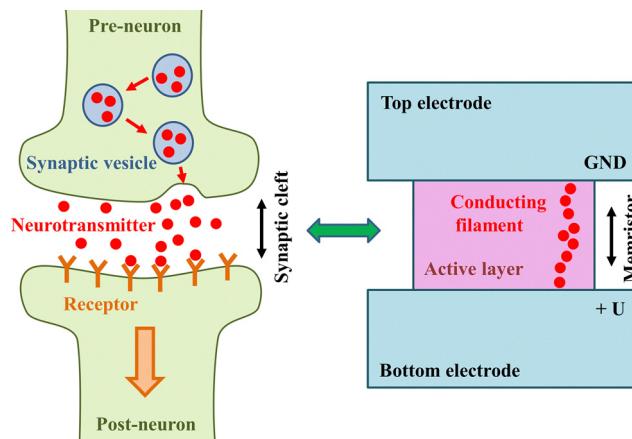

The foundation of memristors lies in the metal-insulator-metal (MIM) structure, which consists of a thin insulating layer of an oxide, active from the memristive point of view, sandwiched between two metal electrodes.<sup>8</sup> This configuration allows the devices to display resistive switching behavior *via* changes in the resistance across the oxide layer by application of an external voltage.<sup>8</sup> The electric field enables oxygen vacancies or metal ions to migrate within the oxide layer, causing localized changes in the material's conductivity. The ion migration is reversible and therefore opens the possibility of switching between a low resistance state (LRS) and a high resistance state (HRS).<sup>9</sup> In binary logic, the HRS represents level "0" or the OFF state, while the LRS describes the "1" or ON state.<sup>2</sup> Several different fabrication pathways for memristive devices are actively being researched. Here, different approaches lead to significantly different switching mechanisms and overall behaviour. Understanding and being able to influence these parameters are the key to improved device performance. Most methods are based on physical or chemical vapor deposition methods, where the metal oxide is deposited directly or through reactive deposition methods. The so-formed layers are then either stacked, as, for example, in bilayer devices, or chemically altered after the fabrication in order to improve their performance.<sup>10,11</sup> Examples for these can be structural changes, like from an amorphous to a crystalline phase or the change of the underlying substrate. Another possibility is the introduction of defects in order to alter the memristor behaviour.<sup>12,13</sup> Amidst these classes of memristors, anodic memristors have drawn attention due to their simple structure, easy fabrication, robustness, and scalability.<sup>14,15</sup>

In the process, thin films of valve metals, such as Hf,<sup>16</sup> Nb,<sup>17–19</sup> Ta,<sup>20,21</sup> and Ti,<sup>22–24</sup> are deposited on a substrate and then anodized to form an oxide layer.<sup>15</sup> The valve metal oxide then acts as an active insulating layer in the MIM structure.<sup>15</sup> The properties of the anodic oxide, such as its thickness, composition, and defect concentration, can be closely controlled *via* the adjustment of process parameters such as applied voltage,<sup>21</sup> anodization time,<sup>17</sup> and electrolyte composition.<sup>16</sup> It additionally allows the precise control of defects such as oxygen vacancies, which play a critical role in the switching mechanism of memristors, therefore allowing fine-tuning of the electrical properties of the devices, such as switching voltage and retention.<sup>25,26</sup> Furthermore, during the anodization, it is possible to incorporate additional dopants, intrinsic defects, and multilayered structures, expanding their range of applications.<sup>19</sup>

In the present work, a concise overview of anodic memristors is given. General concepts detailing the memristive structure and resistive switching characteristics are reviewed and particularities of anodic oxides are emphasised. Filamentary, interfacial and hybrid resistive switching types are described and the relevance of the electrochemical nature of the active anodic oxide film is related to the device performance. The possibility of intrinsic defect engineering provided by the electrochemical route of oxide fabrication is evaluated and its influence on the memristive behaviour in terms of stability, reliability and reproducibility is discussed. A large number of alloys providing functional anodic memristors upon anodization is shown from data available from high throughput combinatorial studies. Finally, an overlook of the main potential application categories such as memories, neuromorphic computing and sensors is provided for understanding the currently underestimated relevance of the electrochemical anodization as a tool for memristive device fabrication.

## 2. Fabrication and operation principles of anodic memristors

### 2.1 Metal-insulator-metal structure for anodic memristors

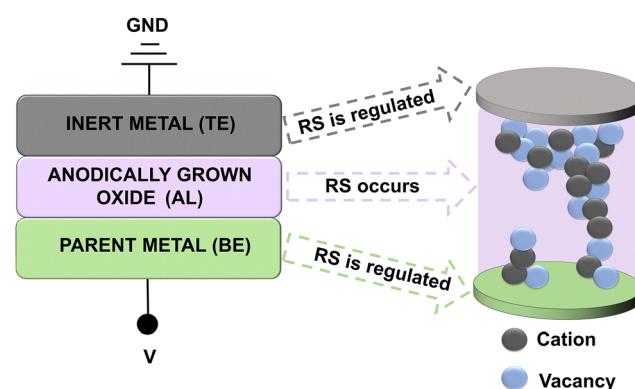

A simple MIM structure is essential for many electronic devices, including resistive random-access memories (ReRAM) and memristors in general. The configuration consists of a thin insulating/dielectric active layer sandwiched between two metallic electrodes, usually referred to as the top electrode (TE) and the bottom electrode (BE) due to their most common vertical stacking. A general representation of the MIM architecture in the case of anodic memristors is shown in Fig. 1.

This structure is relevant for resistive switching devices, since the changes in resistance that occur in the active layer (AL) are responsible for their memory effects. Simple yet effective, the MIM structure is used for fabrication of nanoscale resistive switching devices, as the switching is based on changes in the conductive properties of the active layer.<sup>8</sup> An electrical field is applied between the TE and the BE across the insulator, allowing the device to switch from the ON to OFF resistive state. The MIM architecture allows for scalability and

Fig. 1 General metal–insulator–metal structure (adapted from ref. 9).

high-density memory structures.<sup>27</sup> The correct choice of TE and BE is vital for a functioning memristor.<sup>8</sup> Apart from applying the electric field, the role of the TE is to initiate and control the resistive switching (RS). In general, metals such as Pt, Ag, and Au are typically used as they are chemically stable, resistant to oxidation, and excellent electrical conductors.<sup>28,29</sup> The most common choice for a TE is Pt, due to its inertness and convenient Schottky barrier height when in contact with most anodic oxides. It does not react with the AL during operation, ensuring stable switching behaviour following a large number of switching cycles ( $10^3$ – $10^8$ ). Similar to the TE, the BE must have good electrical conductivity in order to be able to readily transport charges through the insulating/active layer.

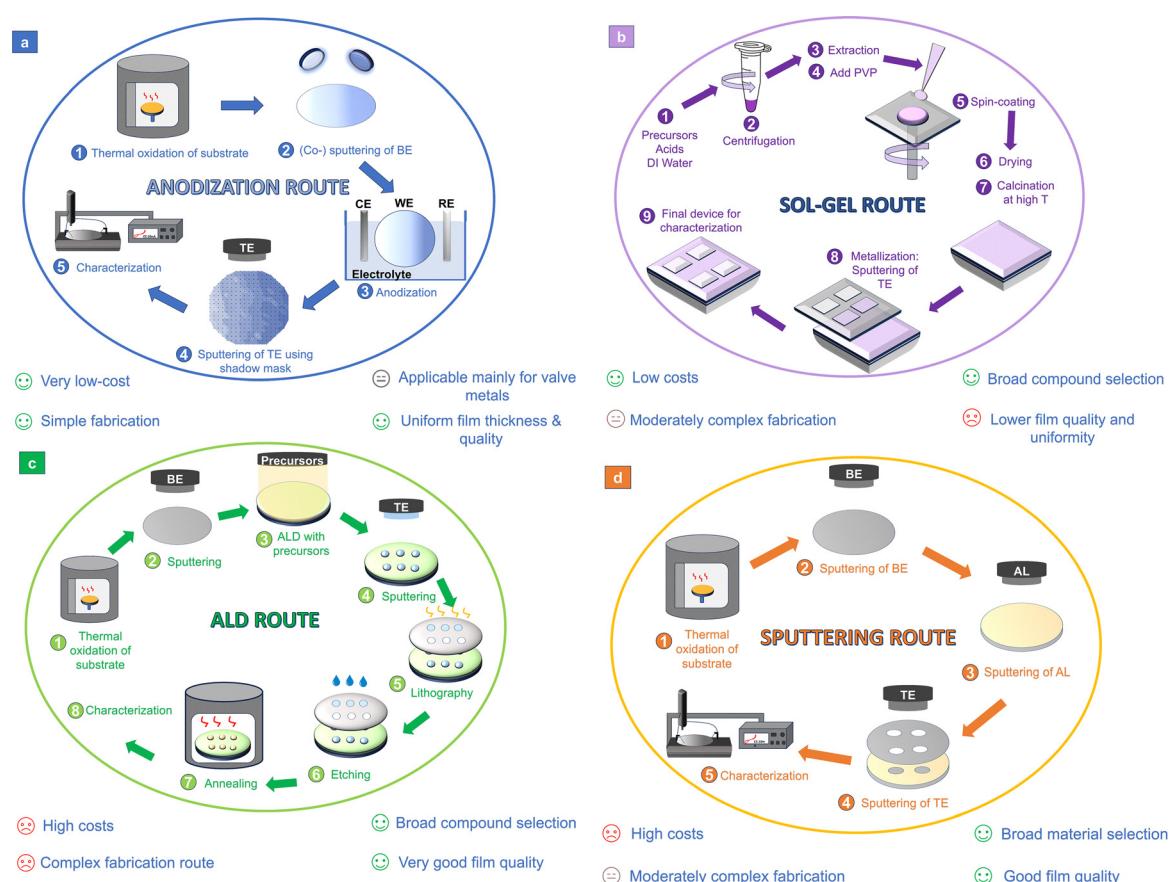

In the case of anodic memristors, common valve metals (Al, Hf, Nb, Ta, Ti, W, and Zr) are used as the BE.<sup>16</sup> These metals are known to form stable oxides through anodization,<sup>30</sup> which are further employed as the active layers of the MIM structures.<sup>23</sup> The good electrical conductivity of valve metals, along with their ability to form oxides capable of maintaining resistive switching while exhibiting outstanding dielectric properties, makes them ideally suited for use as BEs.<sup>30</sup> From the fabrication point of view, an anodic memristor is a MIM structure where the active oxide layer is not deposited using conventional thin film deposition techniques but is rather grown from the BE parent metal/alloy. In Fig. 2(a), the steps involved in

fabrication of anodic memristors (MIM devices) are presented.<sup>31</sup> Following its deposition, the parent metal BE is anodized in an electrochemical cell containing a chosen aqueous electrolyte as the source of  $O^{2-}$  ions necessary for oxidation. Anodization is typically performed with a three-electrode setup, where the parent metal is used as the working electrode (WE), in combination with an inert counter electrode (CE) and a reference electrode (RE). Similar to any other memristive device, a patterning process (shadow masking, lithography, etc.) is involved in obtaining the Pt TEs. To further emphasize the relevance and simplicity of anodization among other routes for fabricating the AL in MIM devices, a comparison with three other commonly used alternatives is shown in Fig. 2 and Table 1. Fig. 2(b) shows the traditional steps used in the sol-gel route. There, a metal-organic or salt precursor solution is deposited, typically by spin-coating or dip-coating, after which it is converted into an oxide film by drying and thermal annealing. The sol-gel approach is also an attractive alternative, as it requires only very simple equipment and inexpensive precursors to cover large or even flexible substrates.<sup>32</sup> However, as summarized in Table 1, sol-gel ALs often suffer from higher roughness, cracking and pinholes. As a result, the final microstructure and stoichiometry are sensitive to solution chemistry and annealing, which can lead to larger device-to-device variability. Fig. 2(c) schematically shows the ALD route for AL

Fig. 2 Typical fabrication steps of the AL by (a) anodization,<sup>31</sup> (b) sol-gel,<sup>32</sup> (c) ALD,<sup>101</sup> and (d) sputtering<sup>102</sup> routes.

Table 1 Comparison of fabrication routes used to obtain the AL in memristive devices

| AL fabrication | AL materials                                                      | Costs                                                                               | Fabrication complexity                                                                        | Time and throughput                                                                                                              | Film quality and uniformity                                                                                                     | Ref.          |

|----------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|

| Anodization    | Limited: mainly applicable for valve metals                       | Very low: electrolyte, potentiostat, electrodes needed                              | Very simple: basic electrochemical knowledge needed                                           | Very fast: oxide growth can occur in tens of $\text{nm s}^{-1}$ and parallel on large areas                                      | High: thickness control <i>via</i> $U$ , $t$ , <sup>39</sup>                                                                    |               |

| Sol-gel        | Wide variety: binary and complex oxides                           | Low: spin-coater, hotplate/furnace, precursors needed                               | Medium: chemically complex, mechanically simple                                               | Medium: deposition is fast, bottleneck is drying and high-T annealing, as well as multiple coatings for thicker films            | Low: can cover large areas; but more prone to thickness variations, cracking/peeling, pin-holes vs vacuum films and anodization | 40–42         |

| Sputtering     | Wide variety: binary and complex oxides, perovskites, <i>etc.</i> | Medium: vacuum system, targets and wafers needed                                    | Medium: vacuum system handling and optimization needed                                        | Fast: deposition rates at $\text{nm min}^{-1}$                                                                                   | Medium: good thickness and composition uniformity on flat wafers; but line-of-sight poor step coverage in deep 3D structures    | 35–38 and 43  |

| ALD            | Wide variety: binary and complex oxides                           | High: very expensive binary and complex oxides; slow cycles increase per-wafer cost | Medium to high: precursor handling, temperature windows, and nucleation layers add complexity | Slow: 0.5–1 $\text{\AA}$ per cycle; hundreds of cycles for 5–10 nm thickness and long process times, especially for high volumes | High: atomic-scale thickness control, excellent conformality in high-aspect-ratio features, very uniform between devices        | 33, 34 and 44 |

fabrication. In this case, the AL is grown by alternating, self-limiting surface reactions, allowing atomic-level thickness control and excellent conformality even in high-aspect-ratio structures. This approach yields very uniform, compositionally well-defined switching layers and is very beneficial for 3D integration and precise vacancy/interface engineering. However, most ALD tools and precursors are expensive, the growth rates are relatively low, and process integration can be more complex.<sup>33,34</sup> For these reasons the overall cost per device is higher than that for the other mentioned routes. Fig. 2(d) depicts the sputtering route, where the insulating oxide is deposited in a vacuum chamber by physical sputtering from a ceramic or metallic target. Magnetron sputtering is commonly used in microfabrication lines, as it offers reasonable throughput and can be combined with standard lithography and etching, making it a very practical choice for CMOS-compatible ReRAMs. On the downside, the step coverage is poorer than that in ALD, as it produces very thin layers. Sub-nanometre thickness control can then become more challenging, and uniformity in complex 3D geometries is limited by the line-of-sight nature of the process when no reactive conditions are provided.<sup>35–38</sup> In contrast, anodization relies on a simple electrochemical oxidation step carried out in a liquid electrolyte, using inexpensive equipment and operating at or near room temperature. It naturally produces well-defined metal/oxide interfaces and can yield highly uniform films over large areas with any degree of complex 3D geometries with minimal process complexity.<sup>39</sup> Overall, the comparison in Fig. 2 and Table 1 underlines that anodization is the simplest and most affordable of the four routes for forming the active insulating layer, while still offering competitive film quality and device performance, especially when compatible valve-metal systems are involved.

## 2.2. Resistive switching characteristics

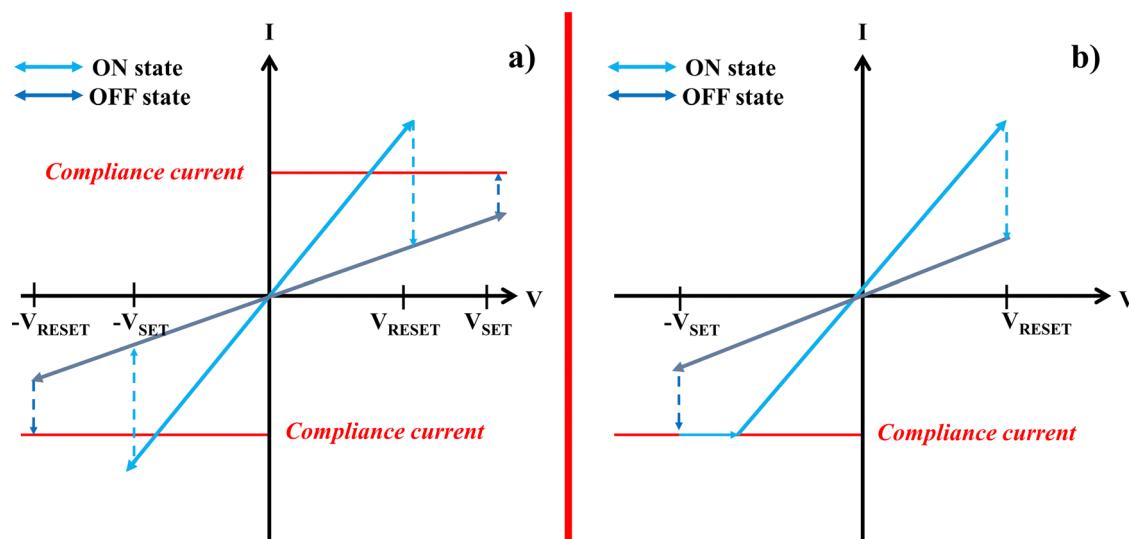

Generally, memristive devices exhibit two main types of switching behavior: either unipolar or bipolar switching between a

HRS and a LRS. In most cases, a forming process is first employed by applying an electric field under certain current limitations for obtaining a stable device before the actual memristive operation. Switching to an ON state (LRS) is known as the SET process. This process requires higher voltages than the RESET process, which returns the device to the OFF state (HRS). In contrast, the RESET process demands a higher current than the SET process. Unipolar switching refers to a switching between the HRS and the LRS, where the polarity of the voltage itself is irrelevant. In this case, only the magnitude is significant for the switching process, which occurs in a single  $I$ – $V$  quadrant. In contrast, bipolar switching is defined by having voltages of opposite polarity for the SET and RESET processes. The current–voltage characteristics of unipolar and bipolar memristors can be seen in Fig. 3(a) and (b), respectively. For both switching modes, the switching is induced by electrical stimulation.<sup>13</sup> Key factors influencing the process are Joule heating and the applied electric field. The former is more common for unipolar devices, while the latter is attributed to bipolar switching devices as they are primarily driven by electric-field-induced redox reactions.<sup>45</sup>

While unipolar and bipolar switching are typically treated as distinct resistive switching mechanisms, certain memristive devices exhibit a hybrid behavior. This phenomenon is known as mixed switching and involves the coexistence or transition between unipolar and bipolar switching characteristics under different operational conditions, as for  $\text{Nb}_2\text{O}_5$ .<sup>18</sup> For instance, the set current compliance (CC) can significantly affect the type of resistive switching. Altering the CC during device operation can cause a transition between unipolar and bipolar switching. At lower CCs, the device may predominantly exhibit bipolar switching, characterized by the polarity-dependent formation and rupture of conductive filaments. Unipolar switching may become dominant at higher CCs, likely due to thermal effects facilitating filament dissolution independent of polarity.<sup>18,46,47</sup>

When the memristor is grown anodically from its parent metal (or alloy), the hybrid switching behaviour may also be

Fig. 3  $I$ – $U$  curve for (a) unipolar and (b) bipolar switching of memristive devices (redrawn from ref. 45).

related to the electrolyte used for anodization. Generally, in any electrochemical anodization process, a finite (usually negligible) amount of electrolyte species may be trapped inside the growing oxide due to the high field-induced ionic movement necessary for the actual formation of new oxide. If most applications of anodic oxides tend to neglect this incorporation, this is not always the case of anodic memristors.<sup>19,21</sup> Common electrolyte species such as those containing C, Na, P, B, *etc.*, may form regions preferentially used for the reversible formation of filaments (for bipolar switching) or regions with enhanced Joule effects (for unipolar switching). An example of hybrid switching is found in  $\text{HfO}_2$ -based anodic memristors, where a balance of oxygen vacancy dynamics and Joule heating determines the mode of operation. Such hybrid devices

allow multi-functional and multi-level switching, enabling applications in reconfigurable circuits and neuromorphic computing.<sup>16</sup>

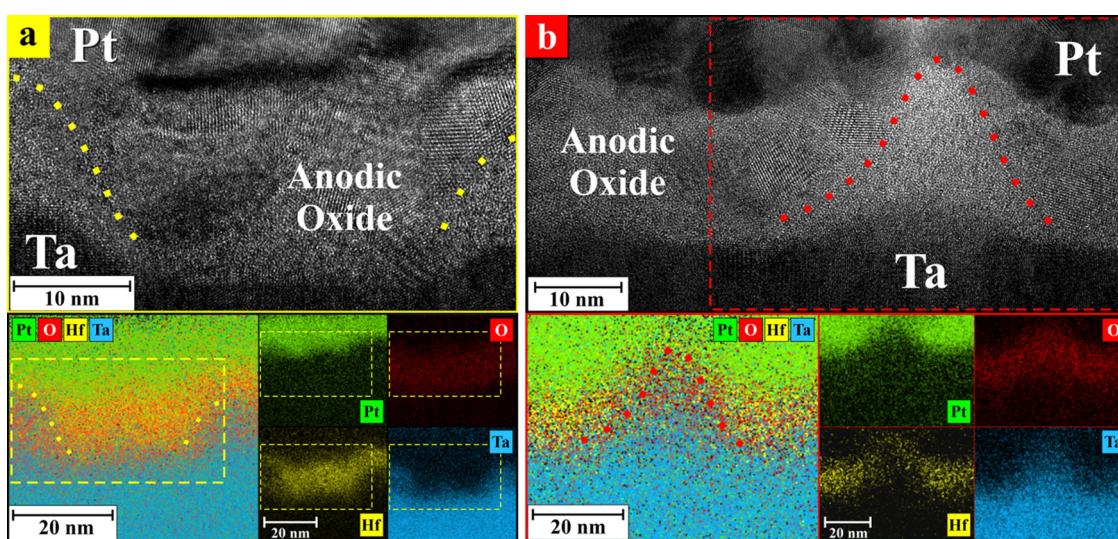

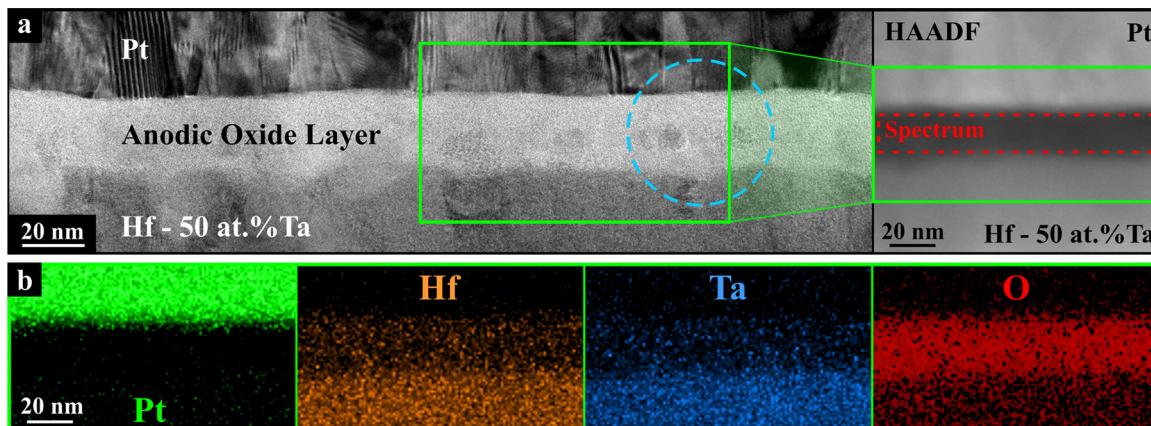

Following the idea of atomic scale modification of a memristive oxide for improved properties, the concept of a composite anodic memristor was recently introduced and refers to active anodic oxides that consist of amorphous/crystalline oxide mixtures and/or a combination of different oxide chemistries. A very good example of anodic composite memristor is found when anodizing  $\text{Hf}/\text{Ta}$  superimposed films. In Fig. 4, such a situation is presented with atomic resolution and an amorphous  $\text{Ta}_2\text{O}_5$  column may be observed as surrounded by crystalline  $\text{HfO}_2$ . The memristive behaviour of such a composite structure obtained exclusively by anodization showed

Fig. 4 Composite  $\text{Hf}/\text{Ta}$  oxides of anodic memristors grown (a) in citrate buffer and (b) in phosphate buffer together with the correspondent elemental energy-dispersive X-ray spectroscopy maps. The approximate position of the amorphous  $\text{Ta}_2\text{O}_5$  nanocolumns surrounded by the polycrystalline  $\text{HfO}_2$  matrix is highlighted with dotted lines.<sup>48</sup>

improved properties when compared to classic memristors, especially in terms of very high HRS/LRS ratios and switching cycles. Moreover, unipolar or bipolar switching was reproducibly demonstrated by the appropriate selection of current limitation.<sup>47,48</sup> In devices with composite or mixed-oxide layers (e.g.,  $\text{HfO}_2/\text{Ta}_2\text{O}_5$ ), regions within the oxide matrix can favour one switching mechanism over the other. The relative contribution of these regions to the overall switching behavior can shift based on external factors, such as the applied voltage or current level.<sup>48</sup>

During the SET process, the memristor transitions from the HRS to the LRS through the application of voltage, which typically causes the formation of conductive filaments in traditional memristors. In valve metal oxide memristors, this can occur due to the movement of oxygen vacancies, which create conductive pathways and increase the material's conductivity. The SET process enables the storage of information by physically altering the device. On the other hand, the RESET process reverses this by transitioning the device from the LRS back to the HRS, effectively erasing the stored information. This happens when an opposite-polarity voltage causes the oxygen vacancies to disperse, increasing the resistance.<sup>49,50</sup>

The HRS and LRS can represent binary data, with the HRS corresponding to “0” showing no formation of filaments and the LRS corresponding to “1”,<sup>2,50</sup> with a conductive filament or a lowered Schottky barrier.<sup>7</sup> A greater difference in resistance between these two states improves the device's data storage capacity and ensures a clearer distinction between the different states. If a memristor can maintain stable resistance states without power, it is classified as non-volatile, whereas volatile memristors lose their stored states without a continuous electric field. In the case of volatile devices, the resistance state returns from the LRS to the HRS once the electrical bias is removed, usually within microseconds to nanoseconds.<sup>51</sup>

Non-volatile memristors can retain both the LRS and the HRS for prolonged periods without applied bias. This stability makes non-volatile devices effective for memory/storage applications, where long-term data retention is needed. This type of switching is typically governed by ion or oxygen vacancy migration which “holds” the state until the next switching is possible. The distinction between volatile and non-volatile devices can be found in neuromorphic computing as well. Volatile memristors still exhibit memory behavior, but they revert to their original state once the electrical stimulus is removed, making them useful for neuromorphic computing, where they mimic synaptic behaviours such as “forgetting”, thus simulating the short-term memory of the human brain. In contrast, non-volatile memristors are ideal for applications requiring stable “memory” over time, simulating the long-term memory of our brain.<sup>52</sup>

In the broader classification of resistive switching devices, volatile and non-volatile behavior represent the two fundamental memory models. Volatile switching, characterized by a spontaneous return to the HRS once the voltage is removed, is often attributed to conduction mechanisms such as charge carrier trapping/de-trapping or reversible ionic movements.<sup>52</sup>

In contrast, non-volatile switching involves the retention of the LRS after voltage removal, mainly due to conductive filament formation. Threshold switching, however, is typically classified as a volatile phenomenon, as the resistance state reverts to the HRS once the applied voltage drops below a critical threshold.<sup>53</sup> This feature separates threshold switching from non-volatile switching, where the LRS is preserved independent of the applied voltage.<sup>53</sup> Thus, volatile memristors can be classified as threshold switching types (digital) and analog switching types.<sup>52</sup> Digital-type devices exhibit abrupt resistance changes with high HRS/LRS ratios and fast switching speeds in the range of nanoseconds, making them suitable for high-speed devices and logic circuits.<sup>52</sup> In contrast, analog-type memristors display gradual conductance changes with lower HRS/LRS ratios, making them more suitable for neuromorphic computing and mimicking of synapsis.<sup>52</sup>

Threshold switching in anodic memristors has been reported not only for mixed anodic oxides<sup>7,46,54</sup> but also for  $\text{Nb}_2\text{O}_5$  and  $\text{TiO}_2$ .<sup>55</sup> In the case of Nb, where both non-volatile and threshold mechanisms are reported based on the O content, the switching behavior is heavily influenced by the oxygen stoichiometry within the  $\text{Nb}_2\text{O}_5$  layer. A higher oxygen vacancy concentration typically promotes filamentary switching, enabling non-volatile memory characteristics. In contrast, a more stoichiometric oxide with fewer oxygen vacancies results in threshold switching. With accurate oxygen vacancy control, devices based on Nb can be designed to be more suitable for either non-volatile memory or neuromorphic applications.<sup>19,54</sup> This duality arises because the oxygen content directly affects the defect density, which governs the formation and dynamics of conductive filaments. Devices with oxygen-deficient oxides provide sufficient active sites for filament formation, allowing stable and permanent resistive states. On the other hand, stoichiometric oxides have limited vacancy pathways, favouring transient, volatile switching. The volatile nature of threshold switching makes it particularly beneficial for applications like neuromorphic computing, where transient behavior can mimic the spiking dynamics of biological neurons.<sup>56</sup>

As already discussed, resistive switching allows the memristors to alter their resistance, thus enabling them to retain and recall information. The mechanism causing the memory effects depends on the device's conductivity, which is modified by the formation of conductive filaments or interfacial effects in the oxide layer of the MIM structure. The former is known as filamentary switching (FS), while the latter is an interfacial switching (IS). In both cases, with the application of voltage, oxygen ions and vacancies experience a promoted migration within the oxide layer. This leads to the formation or breakdown of conductive pathways, allowing the memristor to alter its resistance.<sup>57</sup>

### 2.3. Filamentary resistive switching

The most common mechanism for the RS in memristive devices is FS, which depends on the formation of conductive filaments. They are highly conductive paths inside the oxide layer of the MIM structure. The filaments are composed of

metal ions or oxygen vacancies. They can extend along the entire dielectric layer, connecting the gap between the TE and the BE. This allows the memristor to switch between OFF and ON states. When a conductive filament is formed, the device goes from the OFF to ON state; conversely, when a filament is ruptured, the device goes back into the OFF state. The most common FS mechanisms are the electrochemical metallization mechanism (ECM) and the valence change mechanism (VCM). In the ECM, the conductive paths are formed by electrochemical reduction and metal ion migration, while the VCM depends on oxygen vacancy migration, resulting in local redox reactions. Both mechanisms have a highly localized nature, allowing for low power consumption, as the switching occurs in a small volume of material. Furthermore, FS devices exhibit fast switching, endurance from  $10^6$  to  $10^9$  cycles, and long retention times.<sup>25</sup> This makes the FS devices suitable for non-volatile memory applications. Filament stability and control over the formation/rupture dynamics are critical for both the ECM and the VCM. These challenges will be discussed in the following sections.<sup>49,57</sup>

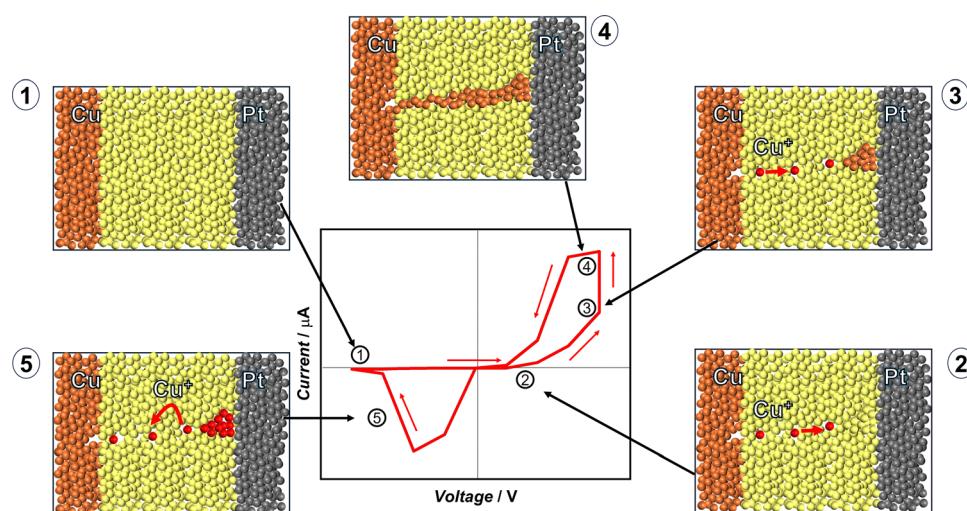

**2.3.1. Electrochemical metallization mechanism.** Memristors based on the ECM rely on forming and dissolving metallic filaments within a solid electrolyte to regulate the transition between the HRS and the LRS. The ECM is associated with cationic devices, having an active electrode, such as Ag and Cu.<sup>58</sup> The switching behavior is driven by redox reactions at the electrodes, making ECM-based memristors suitable for a wide range of memory applications.<sup>57</sup> They are particularly applicable in the context of next-generation memory technologies aiming for high density, fast operation, and low power consumption. In ECM cells, metal cations migrate under an applied electric field towards an inert electrode, such as Pt and W. This begins with the application of a positive bias towards the active electrode, causing the anodic dissolution of the metal at the interface. The metal cations are introduced into the insulating layer, accumulating at the opposite

electrode due to the high electric field present. When reaching the opposite electrode, the metal cations are reduced, forming the conductive metallic filament, which acts as the bridge between both electrodes in the MIM structure.<sup>57</sup> In this way, the device can switch to the ON-state, represented by a low resistance. In Fig. 5, a schematic representation of the atomic level processes occurring during SET and RESET operations of an ECM memristor is presented. During the initial OFF state (Fig. 5(1)), no metallic deposit occurs on the inert electrode, and thus the device has a high resistance. When a positive bias is applied to the active electrode (Fig. 5(2)), the metal atoms begin to dissolve and move through the insulating layer, and the reduction of the metal ions then results in the formation of conductive filaments (Fig. 5(3)). Filament formation is influenced by electrochemical kinetics, ion mobility and the strength of the applied electric field. The insulating layer is critical for the transport of metal cations. Valve metal oxides, such as those used in anodic memristors, are suitable for this, as they have excellent stability, high dielectric strength, and the ability to support controlled ionic transport, which are essential for reliable memristive switching. Furthermore, once the filament connects the two electrodes, the device transitions into an ON state, which has low resistance (Fig. 5(4)). If the voltage polarity is reversed, the filament is then dissolved, returning the device into the initial OFF state (Fig. 5(5)).<sup>59</sup>

Apart from binary switching between the LRS and the HRS, ECM memristors are known for having multilevel switching capabilities.<sup>59</sup> This characteristic allows the devices to exhibit multi-bit data storage, instead of a binary model. By controlling the CC, intermediate resistance states can be programmed. With varying currents during the SET process, the thickness and continuity of the filaments are altered. Thus, ECM-based memristors exhibit outstanding data storage capabilities. Despite the advantages multi-level switching devices possess, filament control is challenging. The initial electroforming needed to create the conductive paths can require high

Fig. 5 Schematic representation of steps of the SET ((1)–(4)) and RESET (5) operations of the electrochemical metallization mechanism (redrawn from ref. 59).

voltages, which can further lead to variability in the device's performance or even breakdown of the film.<sup>27</sup> Furthermore, the retention and endurance in ECM devices may be problematic, as the stability of the metallic filaments over extended periods of time can lead to breakdown due to the constant thermal stress by the Joule effect occurring during the measurements.<sup>59</sup>

The ECM has not yet been fully studied for anodic valve metal oxides. For instance, an ECM-based memristor was demonstrated in devices with a heterojunction structure made of  $\text{SiO}_2/\text{Ta}_2\text{O}_5$ . Here, the conductive filaments are formed and dissolved within the  $\text{Ta}_2\text{O}_5$  layer under an applied electric field. The conductive filaments are composed of metal cations originating from the active electrode, which, in this case, is Ag. The  $\text{SiO}_2$  layer serves as a crucial buffer, regulating the growth direction and confinement of the filaments, ensuring uniform switching behavior. ECM memristors exhibit exceptional electrical performance, at low operating voltages (<0.3 V), while still maintaining high stability and reproducibility. The inclusion of the  $\text{SiO}_2$  layer helps to prevent uncontrolled filament overgrowth and improves the overall switching reliability. This shows that with appropriate design, valve metal oxides, such as  $\text{Ta}_2\text{O}_5$ , can effectively support ECM-based switching, creating energy-efficient memory technologies with enhanced performance characteristics.<sup>60</sup>

Even though at the moment, there are no studies on anodic memristors exhibiting the ECM, the potential is very big. For such anodic memristors, one should consider that the inclusion of an additional metallic ion should be a part of the anodization process itself. The electrochemical community is familiar for a long time with the fact that electrolyte species are always embedded in the growing anodic oxides and exactly this trait will likely be explored. Recent reports have already discussed the presence of electrolyte species inside anodic memristors, positively impacting their stability and resistive switching.<sup>16,19,21,24</sup>

**2.3.2. Valence change mechanism.** The VCM is another possible mechanism driving the resistive switching behavior. Similar to the ECM, it is based on the formation and dissolution of conductive filaments. The filaments are driven by the creation and migration of oxygen vacancies and oxygen ions. Again, similar to the ECM, this process begins with an electro-forming step, where a high electric field is applied to the device, causing a soft breakdown of the dielectric. During electroforming, the  $\text{O}^{2-}$  ions in the oxide layer migrate from their lattice positions toward the anode, leaving behind oxygen vacancies in the lattice. The  $\text{O}^{2-}$  ions could either react with the anode material to form an interfacial oxide layer or be oxidized and discharged as neutral oxygen.<sup>23</sup> The migration of  $\text{O}^{2-}$  ions toward the anode creates a negative charge buildup at the electrode/oxide interface while leaving behind positively charged oxygen vacancies in the oxide layer. This charge redistribution can significantly influence the electrical properties of the material, such as resistance switching in memristors. When enough oxygen vacancies have accumulated, the conductive filaments can form. In this way, the filaments create a connection between the TE and the BE, switching the device from OFF

to ON and allowing current conduction through the device. The filament formation is governed by redox reactions *via* the relocation of oxygen ions under the influence of the electric field. The vacancies allow the formation of the conductive paths, resulting in a SET process in the LRS. Conversely, the RESET process causes the oxygen ions to return to the oxide layer from the anode interface. In this way, a recombination of oxygen ions and vacancies occurs, which then leads to complete or partial filament rupture, returning the device to the HRS. The reversible switching between the two states by formation and rupture of oxygen-based CFs enables the VCM-based memristors to retain and recall resistive states without the need for external power.<sup>9,49</sup>

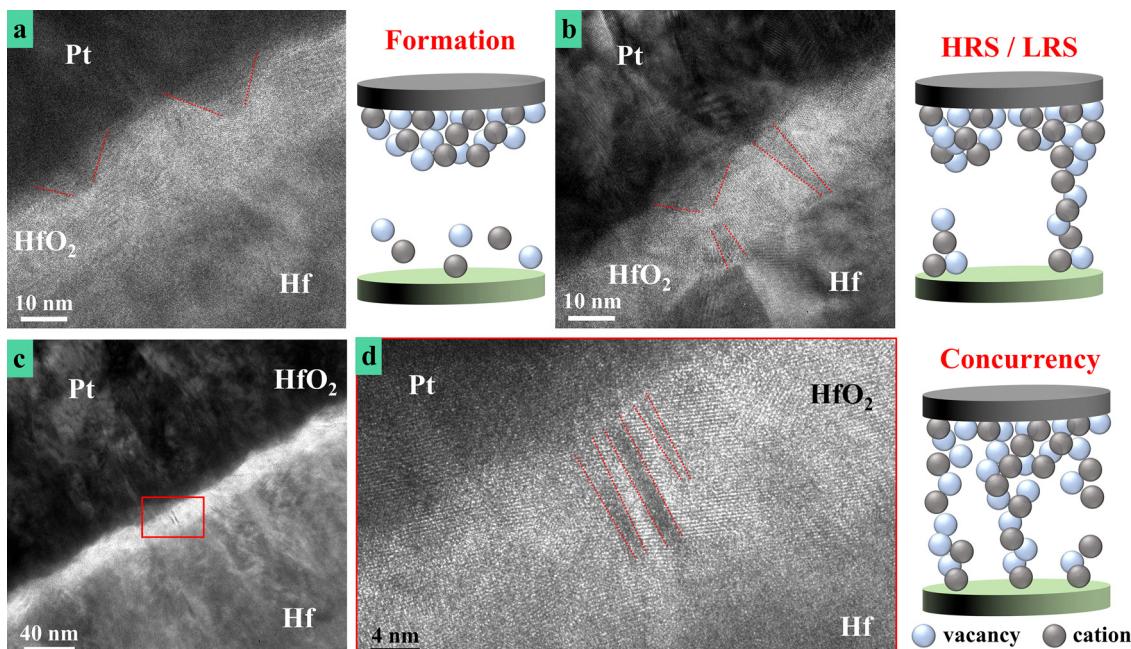

In Fig. 6, a visual representation of the conductive filaments within an anodic  $\text{HfO}_2$  oxide layer is depicted. Their formation is localized, displaying the highly conductive pathways that extend through the oxide layer, connecting the TE and BE. This demonstrates the filamentary nature of the switching mechanism. Oxygen vacancies build up under an electric field to create pathways, enabling the device to transition between resistive states. In addition, concurrency is visible, which refers to the simultaneous existence and interaction of multiple conductive filaments within the oxide layer. This phenomenon can result in multilevel resistance states, where the concurrent activity of multiple filaments allows the device to exhibit intermediate resistance levels. This multilevel behavior is more common for filamentary type switching but has been reported for interfacial memristors as well.<sup>16</sup>

Valve metal anodic memristors are predominantly governed by the VCM due to the intrinsic properties of their oxide layers and the anodization process. The anodic oxidation of valve metals such as Hf, Ta, Nb, and Ti results in the formation of dense, stable, and insulating/semiconducting oxide films such as  $\text{HfO}_2$ ,<sup>16,61,62</sup>  $\text{Ta}_2\text{O}_5$ ,<sup>63</sup> and  $\text{Nb}_2\text{O}_5$ .<sup>19,62</sup> These oxides are characterized by high dielectric constants and localized oxygen vacancies.<sup>30</sup> During anodization, an electric field drives  $\text{O}^{2-}$  ions or hydroxyl species toward the metal, creating an oxygen-deficient oxide layer with vacancies. These vacancies act as active species in the formation of conductive filaments, facilitating the redox reactions that define the VCM. Unlike the ECM, which relies on the migration of metallic cations (e.g.,  $\text{Ag}^+$  and  $\text{Cu}^{2+}$ ), the VCM operates without significant cation contributions.<sup>9,49,64</sup>

VCM-based switching in anodic memristors was also demonstrated by  $\text{Nb}/\text{NbO}_x/\text{Au}$  memristors, resulting in an amorphous structure with oxygen vacancies distributed throughout the oxide. These oxygen vacancies served as active defects governing the resistive switching behavior. Quantized conductance steps observed during electrical testing confirmed the formation and rupture of atomic-scale conductive filaments, composed of oxygen vacancies, under applied electric fields. The precise control over filament dynamics was attributed to the uniform defect distribution achieved through anodic oxidation. Additionally, the  $\text{Nb}/\text{NbO}_x$  interface acts as a reservoir for oxygen vacancies, facilitating their migration during the SET and RESET processes. This dynamic interaction

Fig. 6 Anodic Hf memristor showing (a) vacancy accumulation, (b) complete and interrupted filaments representing the LRS and HRS and (c) and (d) concurrent filaments leading to multilevel switching.<sup>16</sup>

between the vacancies and the oxide layer enabled reliable switching between the HRS and the LRS.<sup>18</sup>

#### 2.4. Interfacial resistive switching

IS is also known as non-filamentary switching and is found in MIM structures, which have a semiconducting oxide. This switching mode is gentle and, in most cases, electroforming-free. These types of memristors are often characterized by excellent stability and non-linear current traits with self-rectification properties. Physical or chemical reactions at the oxide/electrode interface govern IS. The two main mechanisms behind IS are non-filamentary ion migration and charge trapping.

Typically, a Schottky contact is needed between one of the electrodes and the semiconductor for the non-filamentary ion migration to occur. Therefore, a Schottky barrier is formed, which increases in height or decreases with the movement of charges or vacancies under the applied electric field.<sup>65,66</sup> The switching takes place when changes in the concentration of oxygen vacancies occur near the Schottky contact. If a negative voltage is applied to the TE, oxygen vacancies are attracted to it, which leads to an increase in the concentration of vacancies at the upper part of the active layer, while the vacancy concentration is decreased across the thickness of the layer. In contrast, if a positive voltage is applied to the TE, the vacancies migrate away from the upper boundary, thus reducing their concentration near the Schottky contact.<sup>57</sup>

p-type semiconductors have oxygen vacancies as their primary charge carriers, and therefore, the LRS signifies their uniform distribution. When the vacancies migrate towards the TE, a depleted region is created near the BE, leading to the HRS.

Oxygen vacancies typically act as donor-like defects in n-type semiconductors (e.g.,  $\text{TiO}_2$ ,  $\text{Nb}_2\text{O}_5$ ,  $\text{Ta}_2\text{O}_5$ , and  $\text{HfO}_2$ ), contributing free electrons as the main charge carriers. In these materials, a uniform distribution of vacancies corresponds to the HRS because it limits the formation of conductive filaments. In contrast, the migration and clustering of vacancies to form localized conductive pathways result in the HRS. Thus, non-filamentary memristors rely on the movement and redistribution of oxygen vacancies or ions across the active interface. The accumulation of oxygen vacancies near the interface reduces the height of the Schottky barrier, resulting in an LRS. Conversely, their depletion increases the barrier height, restoring the HRS. This process is driven by the applied electric field during operation. Initially, electrons become trapped at the TE/oxide interface, creating a negatively charged interfacial layer. The negative charge attracts positively charged oxygen vacancies, causing them to accumulate near the interface. The movement and redistribution of these vacancies modulate the device's resistance by altering the Schottky barrier height, resulting in transitions between the HRS and the LRS.<sup>57</sup>

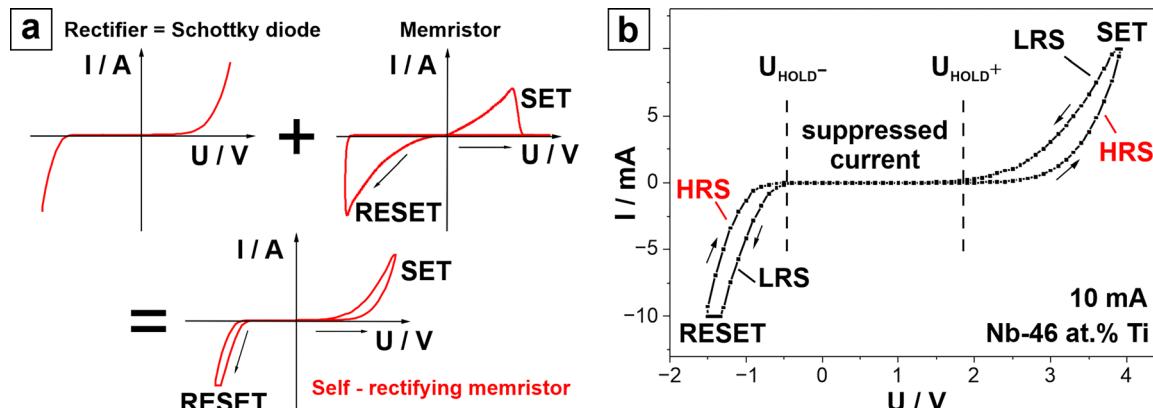

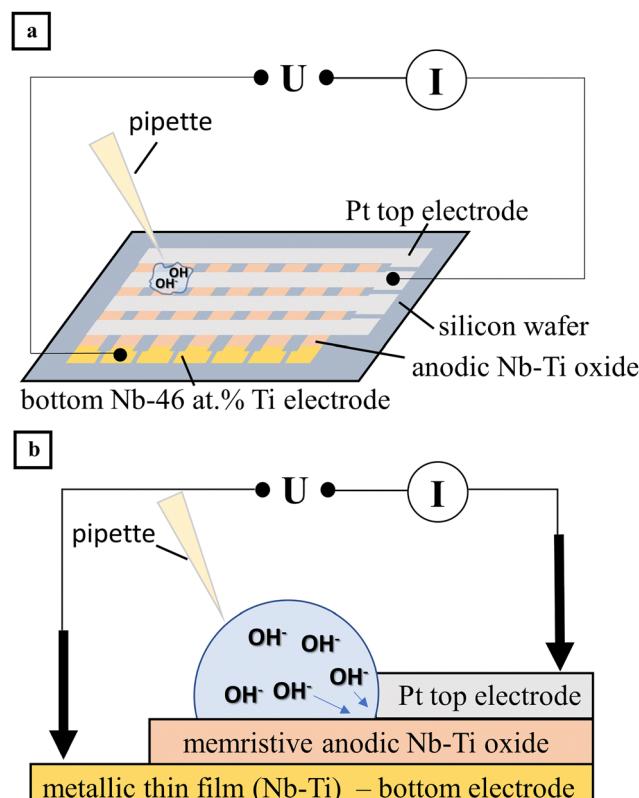

Interfacial resistive switching in anodic memristors was demonstrated for Nb-Ti alloys during a high throughput combinatorial study. The metallic BEs were prepared by co-sputtering with varying Ti contents (22–64 at% Ti) prior to their anodization for memristor fabrication.<sup>7</sup> The anodic memristors obtained were confirmed to be non-filamentary *via* transmission electron microscopy (TEM), showing a homogeneous oxide layer, with no sign of conductive filaments. The memristors were specified as a self-rectifying interfacial type. Based on  $I$ - $U$  sweeps analysis, a deviation from traditional memristive sweeps is observed, as shown in Fig. 7. Fig. 7(a)

Fig. 7 (a) Typical  $I$ - $U$  sweeps for a rectifier, a memristor and a self-rectifying memristor. (b)  $I$ - $U$  sweep of the Nb – a 46 at% Ti anodic memristor.<sup>7</sup>

illustrates typical  $I$ - $U$  curves from three device types: a rectifier, a memristor, and a self-rectifying memristor for comparison. In Fig. 7(b), the anodic memristor highlights its similarity to self-rectifying memristors. Initially, the device is in the HRS, with the current increasing only after applying a positive hold voltage  $U_{\text{HOLD}}$  (at approximately 2 V). Beyond this voltage, the current rises sharply until the device reaches a SET voltage –  $U_{\text{SET}}$  (4 V), where it transitions into the LRS. As the voltage is reduced, the LRS current is suppressed, and a further negative voltage bias leads to current reactivation at  $U_{\text{HOLD}}^-$  (0.5 V). The device then returns to the HRS at a reset voltage  $U_{\text{RESET}}$  (–1.5 V). Current suppression between the holding potentials is a characteristic of self-rectifying behavior and is attributed to the formation of Schottky barriers at the interfaces.<sup>7</sup>

The gradual transition between the HRS and the LRS observed in the  $I$ - $U$  curve corresponds to interfacial switching mechanisms. A complementary study describes anodic  $\text{TiO}_2$  memristors as exhibiting forming-free, bipolar resistive switching with self-rectifying behavior. A gradual resistive transition and multilevel states suggest a switching mechanism, potentially influenced by uniform defect structures within the anodic oxide layer.<sup>22</sup>

## 2.5. Hybrid resistive switching

Hybrid resistive switching mechanisms combine aspects of both, interfacial and filamentary switching. These processes occur simultaneously or sequentially, contributing to the overall resistive behavior of the device. Devices with this mechanism usually display short-lived or partial filaments concurrent with changes in the Schottky barrier height at the electrode–oxide interface, caused by electric field and ion redistribution influences. These hybrid devices combine the gradual resistance changes of interfacial mechanisms alongside the sudden switching associated with filamentary processes.<sup>67</sup>

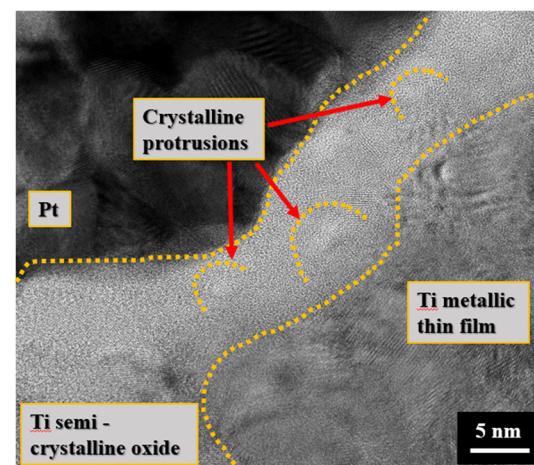

An example of hybrid resistive switching is anodic Ti memristors. Devices fabricated in phosphate buffer exhibited self-rectifying and volatile behavior, usually attributed to interfacial resistive switching mechanisms. TEM analysis revealed the presence of crystalline protrusions within a semi-crystalline  $\text{TiO}_2$  matrix, suggesting the formation of partial filaments as

observable in Fig. 8. This structural observation supports a hybrid interfacial memristive switching model, where both interfacial barrier modulation and partial filament formation contribute to the device's resistive switching behavior. Hybrid devices exhibit higher HRS/LRS ratios of  $10^4 \Omega$ , ensuring good distinguishability between the two states, for reliable operation. In addition to this advantage, their self-rectifying qualities allow for lower power consumption.<sup>24</sup>

## 3. Defect engineering for resistive switching

A critical factor for enhancing resistive switching, as well as the lifetime and stability of memristive devices, is intentionally controlling and creating defects within the oxide layer. Intrinsic defects such as oxygen vacancies and stoichiometric or crystallographic irregularities not only are byproducts of oxide formation but also play an active role in defining the type of resistive switching (see Fig. 8). Therefore, the filament formation (or lack of) and the device's reliability are directly influenced. Defect engineering can be carried out by

Fig. 8 TEM image of the anodic memristor grown on a Ti thin film with the Pt top electrode (adapted from ref. 24).

introducing dopants to stabilize oxygen vacancies or modify electronic properties. Furthermore, this can be achieved by material type, configuration and post-process heat treatments. An extremely favorable way to create intrinsic defects is by anodization, due to its simplicity and cost-effectiveness as recently demonstrated in combinatorial studies on Hf-Ta alloys.<sup>47,48</sup> By selecting appropriate electrolytes and adjusting process parameters, such as the potential and scan rates, the oxide layer can be tuned for selected applications.<sup>16,68-70</sup> The intrinsic formation of defects through the anodic process of memristive film formation and the control of dopants *via* electrolyte selection represent clear advantages of anodic memristors. In classical memristive device fabrication routes, these aspects need to be addressed separately by appropriate deposition/doping procedures which are time consuming and increase the overall costs.

To further emphasize the influence of defect engineering, Table 2 provides an overview based on fabrication methods for HfO<sub>2</sub>, TiO<sub>2</sub>, Nb<sub>2</sub>O<sub>5</sub>, and Ta<sub>2</sub>O<sub>5</sub> based devices. This is followed by a subsection presenting anodic alloys, in which the composition is tuned electrochemically, mainly based on electrolyte selection. The most common electrolytes used for anodic oxidation are phosphate buffer (PB), citrate buffer (CB) and borate buffer (BB). For each entry, the most important resistive switching characteristics are reported: HRS/LRS ratio, switching mode, multilevel capability, dominant switching mechanism, endurance type and cycles, and forming behavior. While absolute values depend on device design and testing conditions, the overview aims to indicate that anodic memristors are able to achieve comparable results to other commonly used AL fabrication methods. Several entries listed for the anodic memristors either match or exceed values of the other fabrication techniques, such as the sol-gel method, ALD and sputtering. This shows that anodization, while being a simpler, lower-cost and energy efficient method, is still able to produce reliable memristive devices.

### 3.1 Electrolyte selection

The choice of electrolyte is vital for the performance of anodic memristors. It governs the formation and properties of the oxide layer.<sup>30,80</sup> The electrolyte composition, pH and ionic species directly influence the defect density, stoichiometry, and structural uniformity.<sup>80</sup> Furthermore, it can govern the anodization kinetics, including the oxide growth rate and thickness.<sup>30</sup> For example, PB solutions can stabilize oxide by complexing with metal ions, leading to uniform and compact oxide layers.<sup>24,30</sup> In addition, the electrolyte species can be incorporated into the oxide layer during anodization, modifying its conductivity and enhancing its qualities, *e.g.* by pinning the atomic path of filament formation and deletion, leading to improved multilevel resistive switching and device lifetime.<sup>30</sup> For instance, in anodic Ti-based memristors, the use of PB as an electrolyte typically results in unipolar switching, whereas citrate buffer CB leads to bipolar switching. The devices fabricated in PB exhibit superior HRS/LRS ratios of 10<sup>4</sup>, compared to those in CB with only 10<sup>2</sup>. This effect can be attributed to the

higher oxide resistance of memristors prepared in PB and the incorporation of phosphate species into the oxide layer.<sup>24</sup>

The incorporation of phosphate species is also reported for Ta,<sup>21</sup> Nb<sup>19</sup> and Hf<sup>61</sup> based anodic memristors. In the case of Ta devices, the anodization in PB results in advantages in the lifetime and stability of the memristors during reading and writing. While CB and BB devices withstand only 10<sup>4</sup> and 10<sup>5</sup> cycles, respectively, the PB device exhibits endurance up to 10<sup>6</sup> cycles without signs of degradation. The reasoning behind the excellent performance of the PB anodized Ta oxide memristor is related to oxyphosphate formation, causing spatial pinning of CF positions during reading and writing operations. This allows the CF's positioning to be predefined *via* anodization and improves its stability. Meanwhile, no incorporation of borate or citrate species was found, resulting in poorer memristive characteristics for these anodic oxides. A similar situation is reported for Nb<sub>2</sub>O<sub>5</sub> memristors, where the electrolyte choice leads to drastic differences in device behaviour, comparable to Ti and Ta based devices. Oxides grown in CB show multilevel switching properties, while PB anodized oxides have a prolonged lifetime and stability in the LRS and the HRS. The exact values and mechanisms behind the RS behaviour can be referred to in Table 1.<sup>19</sup>

### 3.2. Influence of the active layer thickness

Anodic oxidation allows for a fine control of the AL thickness, but reports show that stable memristive behaviour exists only within a certain oxide thickness window. For anodic oxides on Ti, Ta and Nb, with the oxide thickness ranging between roughly 30 and 200 nm, an approximately linear thickness-voltage relationship of 1.6 to 2 nm V<sup>-1</sup> was reported. This shows that the thickness can be adjusted very reproducibly just by the electrochemical parameters used during the anodic oxidation. Within this range, however, the memristive behaviour was found to depend strongly on the thickness governed by the anodization potentials applied. Thinner oxides grown at 10 V showed no memristive behaviour at all, while optimum anodization parameters were found at 25 V. These devices with an intermediate layer thickness exhibited the most pronounced *I-U* sweeps and therefore highest ON/OFF ratios. Memristive responses were found to degrade with higher applied cell voltage (30–90 V).<sup>81</sup>

A similar trend is observed in an anodic TiO<sub>2</sub> memristor, where devices based on thinner oxides fabricated potentiostatically with very short anodization times of 1 and 3 s (at 30 V) showed degraded ON/OFF ratios and smaller hysteresis openings, while longer anodization times of 60 s (at 30 V) led to asymmetric and unstable *I-U* characteristics. In contrast, memristors with intermediate oxide thicknesses grown for 10 s (at 30 V) allowed for the most symmetric and reproducible memristive *I-U* responses, with the highest ON/OFF ratios.<sup>6</sup>

In reports on anodic TiO<sub>2</sub> nanotube memristors, the nanotube layer thickness was varied between 80, 120, 160 and 200 nm at 10 V for 5, 10, 15 and 20 minutes, respectively. All devices were tested for their HRS/LRS ratios depending on the number of switching cycles. The lowest HRS/LRS ratios (below

Table 2 Representative RS performance of valve metal devices grouped by active layer fabrication methods

| Material | AL                                               | AL fabrication                                                 | HRS/LRS ratio                                   | Switching type                   | Multilevel switching       | Switching mechanism                 | Memory                                 | Endurance cycles                                | Electro-forming Ref.                |

|----------|--------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|----------------------------------|----------------------------|-------------------------------------|----------------------------------------|-------------------------------------------------|-------------------------------------|

| Hf       | HfO <sub>2</sub>                                 | Sol gel ALD Sputtering                                         | 10 <sup>3</sup> 10 <sup>2</sup> 10 <sup>2</sup> | Bipolar Bipolar Bipolar          | — 5 levels 12 levels       | Filamentary Filamentary Filamentary | Non-volatile Non-volatile —            | — 10 <sup>4</sup> —                             | No Yes No 32 71 72                  |

|          | BB                                               | Anodization                                                    | 10 <sup>0</sup>                                 | Bipolar                          | 2 levels 4 levels 1 level  | Filamentary                         | Non-volatile                           | 10 <sup>2</sup> 10 <sup>5</sup>                 | Yes Yes 16                          |

|          | CB                                               |                                                                | 10 <sup>1</sup>                                 |                                  | —                          |                                     |                                        | 10 <sup>5</sup>                                 |                                     |

|          | PB                                               |                                                                | 10 <sup>0</sup>                                 | Unipolar Unipolar                | —                          | Filamentary                         | Non-volatile                           | — 10 <sup>3</sup>                               | Yes Yes 73 74                       |

| Nb       | Nb <sub>2</sub> O <sub>5</sub>                   | Sol gel Sputtering                                             | — $\approx 10^3$                                | Unipolar Unipolar                | 8 levels 4 levels          | Filamentary                         | Threshold and non-volatile             | 10 <sup>6</sup> 10 <sup>6</sup>                 | Yes Yes 17-19                       |

|          | BB                                               | Anodization                                                    | 10 <sup>2</sup>                                 | Unipolar                         | —                          |                                     |                                        |                                                 |                                     |

|          | PB                                               |                                                                | 10 <sup>2</sup>                                 | Bipolar depending on CC          | —                          |                                     |                                        |                                                 |                                     |

|          |                                                  |                                                                |                                                 | Bipolar Bipolar                  | —                          | Filamentary Mixed                   | Non-volatile Non-volatile              | 10 <sup>4</sup> 10 <sup>3</sup>                 | Yes Yes 75 76                       |

| Ta       | Ta <sub>2</sub> O <sub>5</sub>                   | ALD Sputtering                                                 | — 10 <sup>3</sup>                               | —                                | —                          |                                     |                                        |                                                 |                                     |

|          | BB                                               | Anodization                                                    | 10 <sup>1</sup>                                 | Bipolar                          | 2 levels 2 levels 4 levels | Filamentary                         | Non-volatile                           | 10 <sup>5</sup> 10 <sup>4</sup>                 | Yes Yes 20 and 21                   |

|          | CB                                               |                                                                | $\approx 10^2$                                  |                                  |                            |                                     |                                        |                                                 |                                     |

|          | PB                                               |                                                                | 10 <sup>2</sup>                                 |                                  |                            |                                     |                                        | 10 <sup>6</sup>                                 |                                     |

| Ti       | TiO <sub>2</sub>                                 | Sol gel ALD Sputtering                                         | 10 <sup>2</sup> 10 <sup>3</sup> 10 <sup>2</sup> | Bipolar Bipolar Bipolar          | 3 levels — —               | Interfacial Filamentary Filamentary | Non-volatile Non-volatile Non-volatile | 10 <sup>2</sup> 10 <sup>2</sup> 10 <sup>2</sup> | No Yes Yes 77 78 79                 |

|          | CB                                               | Anodization                                                    | 10 <sup>2</sup>                                 | Bipolar                          | 4 levels 4 levels          | Interfacial                         | Volatile                               | 10 <sup>6</sup> 10 <sup>6</sup>                 | No No 22-24                         |

|          | PB                                               |                                                                | 10 <sup>4</sup>                                 |                                  |                            |                                     |                                        |                                                 |                                     |

|          |                                                  |                                                                |                                                 |                                  |                            |                                     |                                        |                                                 |                                     |

| Hf-Nb    | HfO <sub>2</sub> /Nb <sub>2</sub> O <sub>5</sub> | CB                                                             | 10 <sup>7</sup>                                 | Bipolar                          | 1 level 5 levels 2 levels  | Filamentary                         | Threshold and non-volatile             | 10 <sup>2</sup> 10 <sup>7</sup>                 | No No 54                            |

|          | Hf-18 at% Nb                                     |                                                                |                                                 |                                  |                            |                                     |                                        | 10 <sup>2</sup>                                 |                                     |

|          | Hf-45 at% Nb                                     |                                                                |                                                 |                                  |                            |                                     |                                        |                                                 |                                     |

| Ta-Hf    | Ta > 50 at% Hf                                   | Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub>               | CB                                              | 10 <sup>1</sup>                  | Bipolar Unipolar Bipolar   | 3-4 levels 2 levels 1 level         | Filamentary                            | Threshold and non-volatile                      | 10 <sup>6</sup> 10 <sup>6</sup> N/A |

|          | Ta 50-70 at% Hf                                  |                                                                |                                                 | 10 <sup>7</sup>                  |                            |                                     |                                        |                                                 | Yes Yes                             |

|          | Ta < 70 at% Hf                                   |                                                                |                                                 | 10 <sup>2</sup>                  |                            |                                     |                                        |                                                 |                                     |

| Nb-Ta    | Nb-13-30 at% Ta                                  | Nb <sub>2</sub> O <sub>5</sub> /Ta <sub>2</sub> O <sub>5</sub> | PB                                              | 10 <sup>2</sup> -10 <sup>4</sup> | Unipolar/bipolar           | 3-4 levels depending on CC          | Filamentary                            | Threshold and non-volatile                      | N/A Yes 46                          |

|          | Nb-31-40 at% Ta                                  |                                                                |                                                 | 10 <sup>2</sup>                  |                            |                                     |                                        |                                                 |                                     |

|          | Nb-40-65 at% Ta                                  |                                                                |                                                 | 10 <sup>2</sup> -10 <sup>6</sup> |                            |                                     |                                        |                                                 |                                     |

|          | Nb-66-80 at% Ta                                  |                                                                |                                                 | 10 <sup>2</sup> -10 <sup>4</sup> |                            |                                     |                                        |                                                 |                                     |

|          | Nb-24-36 at% Ti                                  | Nb <sub>2</sub> O <sub>5</sub> /TiO <sub>2</sub>               | PB                                              | 10 <sup>4</sup> -10 <sup>5</sup> | Bipolar                    | 4 levels                            | Interfacial                            | Volatile                                        | 10 <sup>6</sup> No 7                |

| Nb-Ti    | Nb-37-48 at% Ti                                  |                                                                |                                                 | 10 <sup>6</sup>                  |                            |                                     |                                        |                                                 |                                     |

|          | Nb 49-52 at% Ti                                  |                                                                |                                                 | 10 <sup>4</sup> -10 <sup>5</sup> |                            |                                     |                                        |                                                 |                                     |

one order of magnitude) withstanding only 5 cycles were reported for devices with an oxide thickness of 80 nm, while the ratios of approximately 100 were acquired by memristors with 160 and 200 nm thick ALs. The best performing device with an AL thickness of 120 nm exhibited the highest HRS/LRS ratio.<sup>82</sup> Moreover, thicker anodic films have been reported to suffer from poorer mechanical stability and less attractive device characteristics, such as higher electroforming voltages and lower HRS/LRS ratios compared with films of tens up to a few hundred nanometres.<sup>39</sup> All reports taken together emphasize the importance of the AL thickness while tuning devices for optimum performance metrics.

### 3.3. Alloying of bottom electrodes and combinatorial screening for anodic memristors

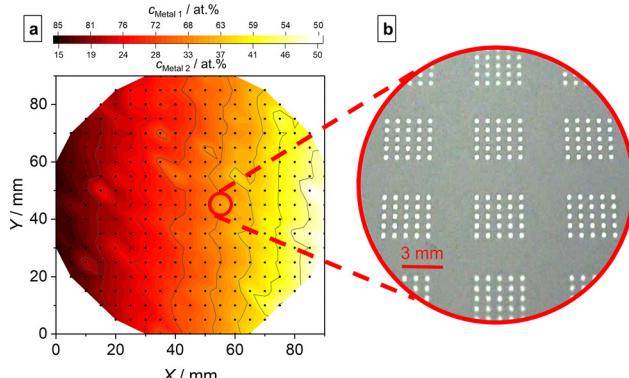

The nature of the BE can also lead to defect engineering of anodic oxide memristors.<sup>68</sup> This is mainly related to the competition for oxygen of different cations which a valve metal alloy will contain. By manipulation of the type and concentration of defects in the oxide layer, switching mechanisms can be controlled to enhance device performance and tailor memristors for specific applications, such as non-volatile memory, neuromorphic computing, or high-density crossbar arrays.<sup>15</sup> To efficiently test different alloys as BEs, a combinatorial approach proved to be a very straightforward method for identification of ideal parent metal electrodes. This involves the simultaneous fabrication of the BE *via* co-sputtering, where the deposition geometry is adjusted to achieve a gradient composition of an alloy on a single substrate. After the co-sputtering of the BE from two (or more) metal targets, energy-dispersive X-ray spectroscopy (EDX) mapping is usually carried out to quantify the compositional gradient obtained across the substrate. This step is crucial, as even small variations in the alloy composition can strongly influence the anodization behaviour and the resulting memristive switching characteristics. By determining the local composition at each position on the Si wafer, the subsequent electrical measurements can be correlated with a specific alloy, allowing a composition to property relationship to be established. An example of an EDX composition map of such a gradient is shown in Fig. 9(a) for a combinatorial library created with two valve metals. Here, the colour scale indicates the local metal content across the library. The follow-up anodization results in the formation of mixed oxide layers. Not only it is straightforward and highly scalable, but it also provides a convenient way to quickly evaluate the memristive properties of various valve metal alloys simultaneously, in a high throughput screening manner. The corresponding finished library, after anodization and TE fabrication, is presented in Fig. 9(b), showing how the continuous composition spread is transformed into an array of individual memristor cells ready for high-throughput electrical screening.<sup>46</sup> This approach simplifies the fabrication process and facilitates the rapid evaluation of memristive properties across a range of compositions. By carefully screening alloys, the defect structure within the oxide layer can be compositionally tuned, enabling easier control over oxygen vacancy distribution, conductivity, and switching behavior.

## COMBINATORIAL MAPPING

○ 5 x 5 anodic memristors per cluster

Fig. 9 (a) Example of EDX mapping for a combinatorial library created by alloying 2 valve metals and (b) an image of a finished anodic library.

In this way, alloying serves as a powerful tool for defect engineering in anodic memristors, allowing optimization for memristor performance in specific applications.<sup>7,15,31,46–48,54,83</sup>

In Fig. 10, intrinsic defect engineering by anodization of a Hf-50 at% Ta bottom electrode is presented as obtained from a combinatorial Hf-Ta study. Inside the active memristive mixed oxide, the presence of small pure HfO<sub>2</sub> crystallites is observable, directly impacting the memristive behaviour allowing a change from bipolar to unipolar devices with enhanced properties. Additionally, an enrichment of Hf species close to the top electrode was related to very different ionic transport numbers for Hf and Ta during their competition for O in the anodization process. Unipolar Hf-Ta anodic memristors have an in-depth homogeneous local chemical state of Hf and lower electronic polarizabilities for O and Hf. This is considered as beneficial for the memristive endurance and retention performance.<sup>31</sup>