Cite this: *RSC Adv.*, 2025, **15**, 45417

Received 2nd September 2025

Accepted 9th November 2025

DOI: 10.1039/d5ra06569k

rsc.li/rsc-advances

## ALD-grown semimetallic $\text{TiS}_x$ for hole injection into monolayer $\text{WSe}_2$

M. Saifur Rahman, <sup>\*a</sup> Chan-Wen Chiu <sup>b</sup> and Suzanne E. Mohney <sup>\*ac</sup>

Semimetal contacts have recently emerged as promising due to the remarkably low contact resistance of Bi and Sb to n-channel field effect transistors (FETs) prepared from two-dimensional (2D) transition metal dichalcogenide (TMD) semiconductors. However, hole injection in 2D semiconductors remains a bottleneck, hindering application of 2D devices in advanced logic nodes. In this study, we investigate the use of atomic layer deposition (ALD) to fabricate high work function semimetallic  $\text{TiS}_x$  interlayers for efficient hole injection into  $\text{WSe}_2$ , a 2D semiconductor of considerable interest due to its potential for next-generation scaled electronics. By employing ALD-grown semimetallic  $\text{TiS}_x$  combined with capping the device with  $\text{MoO}_x$ , we achieved a hole current of  $\sim 64 \mu\text{A } \mu\text{m}^{-1}$  at  $V_D = -1 \text{ V}$ , a contact resistance of  $10 \pm 3 \text{ k}\Omega \mu\text{m}$ , and an  $I_{\text{ON}}/I_{\text{OFF}}$  ratio exceeding  $10^6$  at room temperature. Hole injection may be favored because of a high work function and low density of states at the Fermi level of  $\text{TiS}_x$ , promoting a low Schottky barrier to the valence band of  $\text{WSe}_2$ , and by the van der Waals nature of the contacts. Performance is further aided by channel doping by  $\text{MoO}_x$ .

## Introduction

Achieving low-resistance contacts for 2D p-channel field effect transistors (FETs) remains a key challenge for their integration into advanced technology nodes. Significant progress has been made with semimetallic contacts such as Bi<sup>1</sup> and Sb<sup>2</sup> and low-melting-point soft metal contacts (*e.g.*, Sn and In),<sup>3</sup> both of which have reduced contact resistance ( $R_C$ ) and enhanced performance of n-channel FETs. However, the performance of p-channel FETs fabricated from TMDs is still compromised by high contact resistance.<sup>4</sup> These semimetal and soft metal contacts have poor band alignments for hole injection, leading to high Schottky barrier (SB) heights, high  $R_C$ , and low current delivery.  $\text{WSe}_2$  has emerged as a promising TMD for FETs capable of supporting both n- and p-channels.<sup>5,6</sup> Moreover, recent progress in scalable methods for synthesizing and transferring TMDs—particularly monolayer  $\text{WSe}_2$ —has opened new opportunities for practical device integration.<sup>7</sup>

A few studies have explored contact materials with high work functions such as  $\text{MoO}_x$  and Pt for hole injection. For example, FETs with the contact configuration  $\text{Pd}/\text{MoO}_x/\text{WSe}_2$  exhibited on currents on the order of  $10^{-7} \text{ A } \mu\text{m}^{-1}$ ,<sup>8</sup> while Pt/ $\text{WSe}_2$  contacts resulted in contact resistances for hole injection of  $5.7 \text{ k}\Omega \mu\text{m}$ .<sup>9</sup> There has been progress in van der Waals (vdW)

contact schemes for hole injection, realized through metal transfer techniques<sup>10</sup> or optimized evaporation,<sup>11</sup> avoiding covalent bonds with semiconductor that can lead to charge redistribution and significant perturbations in the 2D electronic band structure,<sup>12,13</sup> which can result in Fermi-level pinning, high Schottky barriers, and increased contact resistance. Moreover, various doping techniques such as  $\text{NO}_x$ ,<sup>14</sup> or  $\text{O}_2$  plasma<sup>15</sup> treatment have been employed, resulting in markedly reduced contact resistance on exfoliated multilayer flakes. However, all techniques fall short in achieving performance comparable to NMOS devices.<sup>1,2</sup>

Another approach that has been explored is the use of 2D metals with high work functions. For example, 2D  $\text{TaSe}_2$  has been used for hole injection into laser-doped regions of  $\text{WSe}_2$  for p-channel FETs.<sup>16</sup> Growing interest in employing 2D metallic contacts, such as  $\text{VS}_2$ ,<sup>17</sup> and  $\text{NbS}_2$ ,<sup>18</sup> for 2D  $\text{MoS}_2$ -based n-channel FETs, is similarly driven by their potential to reduce contact resistance for electron injection. When used on top of the semiconductor, such contacts interact weakly with 2D semiconductors through van der Waals (vdW) forces, leading to weaker Fermi level pinning.<sup>19</sup> Moreover, the work function of 2D semimetals like graphene can be adjusted using an external electric field, providing control over the Schottky barrier height at 2D semimetal/semiconductor junctions.<sup>20</sup>

Recent studies have demonstrated the potential of the layered semimetal titanium disulfide ( $\text{TiS}_2$ ), in creating contacts to  $\text{MoS}_2$ . Using density functional theory (DFT), Gao *et al.* predicted that  $\text{TiS}_2$  could be used as an ohmic contact on  $\text{MoS}_2$  for hole injection and a Schottky contact for electrons, making it a versatile contact material.<sup>21</sup> Zhang *et al.*<sup>22</sup> explored the use of

<sup>a</sup>Department of Electrical Engineering, Penn State University, PA 16802, USA. E-mail: mqr5905@psu.edu; sem2@psu.edu

<sup>b</sup>Department of Chemical Engineering, Penn State University, PA 16802, USA

<sup>c</sup>Department of Materials Science and Engineering, Penn State University, PA 16802, USA. E-mail: mohney@psu.edu

2D semimetals with high work function as gate electrodes for n-channel transistors. The authors experimentally demonstrated that using the 2D semimetal  $\text{TiS}_2$  with a measured ultrahigh work function (6.6 eV) by Kelvin-probe force microscopy (KPFM) as the gate can lead to transistors with a sub-0.1 V threshold voltage. This result paves the way for low-power electronics with improved gate control.

Research on atomic layer deposited (ALD)-grown  $\text{TiS}_x$  contacts for n-channel  $\text{MoS}_2$  field-effect transistors further highlights the potential of this material and the use of ALD for source/drain contacts.<sup>23</sup> The ALD-grown  $\text{TiS}_x$  contacts of varying thicknesses to ALD-grown  $\text{MoS}_2$  were compared with conventional evaporated Ti contacts. The authors found that  $\text{MoS}_2$  FETs with approximately 1.2 nm thick  $\text{TiS}_x$  contacts outperformed Ti contacts, as key device metrics such as  $I_{\text{ON}}$  and  $R_{\text{C}}$  showed significant improvement with the use of the ultrathin  $\text{TiS}_x$  interlayers layers, despite exhibiting a higher Schottky barrier height than the Ti contacts, as well as modest device performance due to the use of ALD-grown  $\text{MoS}_2$ . Another study suggests that  $\text{TiS}_2$ /monolayer  $\text{MoS}_2$  heterojunctions prepared by depositing  $\text{TiS}_2$  by ALD exhibit reduced Fermi-level pinning (FLP) compared with conventional evaporated metal electrodes due to the formation of clean van der Waals contacts having an unexpectedly low work function of 4.33 eV measured by KPFM, which in turn improves the overall performance of the devices, including on current, subthreshold swing, and threshold voltage.<sup>24</sup>

This work investigates the application of ALD-grown semimetallic  $\text{TiS}_x$  thin films for efficient hole injection into  $\text{WSe}_2$ . By leveraging the advantages of ALD, a powerful technique suitable for industrial-scale applications, we have exploited  $\text{TiS}_x$  for efficient hole injection in  $\text{WSe}_2$ -based devices. ALD enables the conformal deposition of layers, including as contacts for FETs, allowing for increasingly complex device architectures through precise control over film thickness and composition. This low-temperature thin-film synthesis method is compatible with conventional Si technology, in ideal cases offering excellent large-area uniformity, sub-monolayer thickness control, and conformality for high aspect ratio features. This research builds upon the growing interest in 2D semimetals for advanced transistor applications and contributes to the development of

high-performance  $\text{WSe}_2$  devices. Our investigation demonstrates the potential of  $\text{WSe}_2$  p-channel FETs (pFETs) with semimetallic  $\text{TiS}_x$  contacts combined with  $\text{MoO}_x$  capping, achieving a remarkable on-state current of  $64 \mu\text{A} \mu\text{m}^{-1}$  at  $V_D = -1 \text{ V}$  for the best device and a contact resistance of  $10 \pm 3 \text{ k}\Omega \mu\text{m}$ . These results underscore the viability of  $\text{WSe}_2$  for CMOS applications and highlight the significant progress in overcoming the hurdles associated with hole injection in 2D semiconductors.

## Experimental approach

### Materials synthesis and characterization

Monolayer  $\text{WSe}_2$  was synthesized by metal-organic chemical vapor deposition (MOCVD) on double-side polished 2" pre-scored *c*-plane sapphire as previously described<sup>25</sup> were obtained from the 2D Crystal Consortium (2DCC) at Pennsylvania State University and cleaved into smaller pieces for sample fabrication. Atomic force microscopy (AFM) images and Raman spectra are shown in Fig. S1.

Titanium sulfide ( $\text{TiS}_x$ ) was grown by thermal ALD using tetrakis(dimethylamido)titanium (TDMATi) and hydrogen sulfide ( $\text{H}_2\text{S}$ ). The substrate and chamber were heated to 100 °C and TDMATi was set at 75 °C. The  $\text{H}_2\text{S}$  flow was supplied at 40 sccm and diluted by 70 sccm Ar. The growth of  $\text{TiS}_x$  in a saturation study was monitored using an *in situ* quartz crystal microbalance (QCM), as shown in Fig. S2. The QCM was coated with  $\text{TiS}_x$  prior to the saturation study (during chamber conditioning) to minimize the effect of a nucleation delay on the measurement. The saturation study was conducted to confirm that  $\text{TiS}_x$  growth was a self-limiting process. Based on the saturation study, the dose for saturation of TDMATi was found to be 0.06 s, while for  $\text{H}_2\text{S}$  it was 2 s.

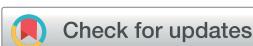

The recipe for the  $\text{TiS}_x$  layer was a 0.06 s TDMATi pulse followed by a 15 s Ar purge. The  $\text{H}_2\text{S}$  was then introduced for 30 s (longer than the minimum dose required for saturation but consistent with Basuvalingam *et al.*<sup>26</sup>) and another 30 s Ar purge was performed to remove unreacted  $\text{H}_2\text{S}$  and byproducts from the reactor. A nucleation delay occurred while depositing  $\text{TiS}_x$  on  $\text{WSe}_2$ . AFM images (Fig. 1) reveal that 50 cycles of  $\text{TiS}_x$  layer on  $\text{WSe}_2$  is not fully continuous, displaying islands. In contrast,

Fig. 1 AFM images: (a) 50 cycles of  $\text{TiS}_x$  on  $\text{WSe}_2$  (b) 100 cycles of  $\text{TiS}_x$  on  $\text{WSe}_2$ .

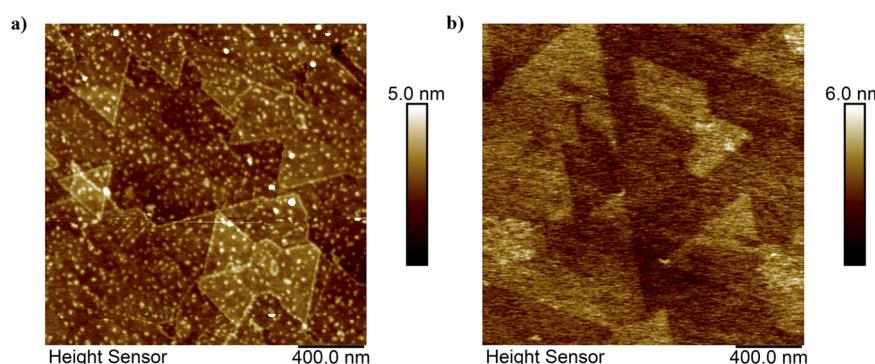

Fig. 2 Raman spectra of ALD grown  $\text{TiS}_x$  at 100  $^{\circ}\text{C}$  (a) on  $\text{SiO}_2/\text{Si}$  and (b) on  $\text{WSe}_2$ .

100 cycles of  $\text{TiS}_x$  appear to achieve complete coverage of the  $\text{WSe}_2$  surface.

Step edges were also measured using AFM (Fig. S3). A measurable step edge was not detected after 50 cycles. However,

84 cycles resulted in a layer  $\sim 5$  nm thick, while 100 cycles resulted in  $\sim 7$  nm and 150 cycles resulted in  $\sim 13$  nm.

Fig. 2 shows the Raman spectrum of ALD grown  $\text{TiS}_x$  on  $\text{SiO}_2/\text{Si}$ . The synthesized  $\text{TiS}_x$  in Fig. 2(a) shows two Raman peaks at

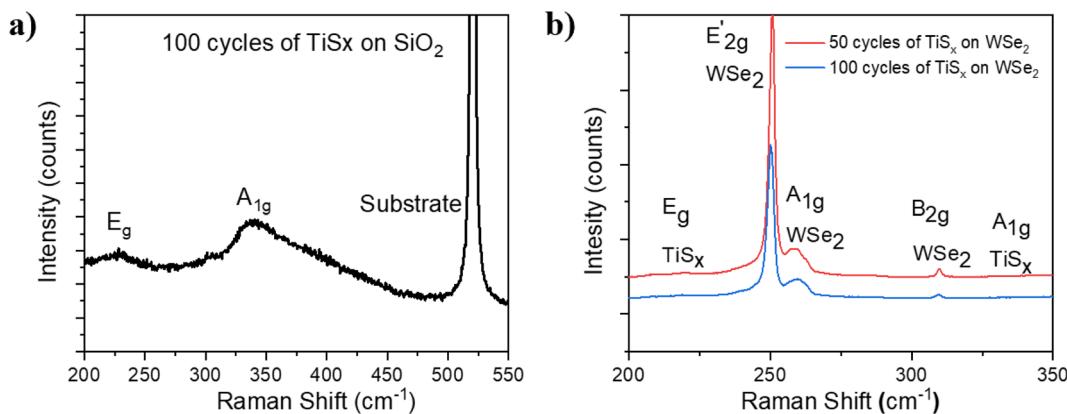

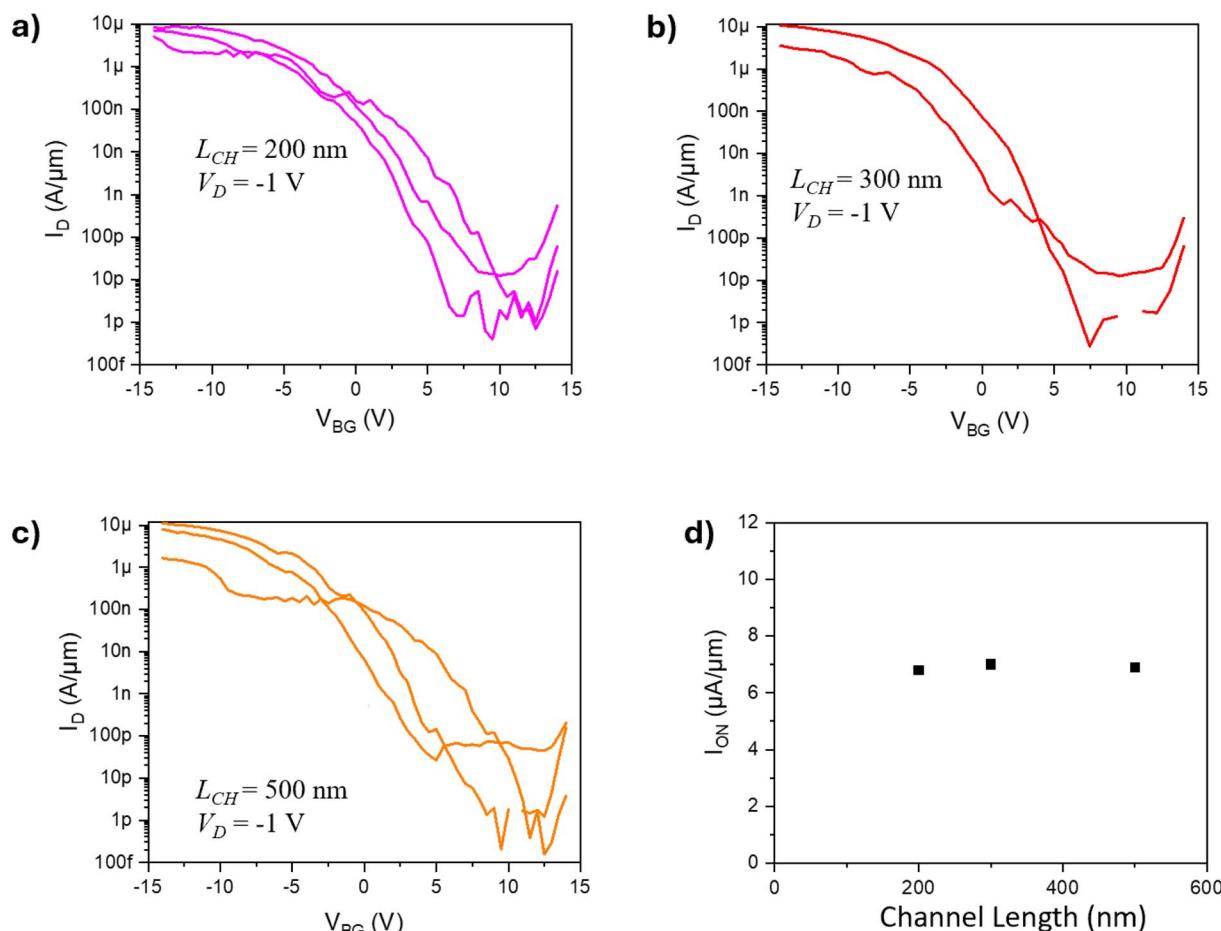

Fig. 3 Au contacts to  $\text{WSe}_2$ . Transfer characteristics with different channel lengths of (a) 200 nm, (b) 300 nm, and (c) 500 nm and (d) maximum ON current variation in different channel lengths.

~230 and ~340 cm<sup>-1</sup>, corresponding to the in-plane E<sub>g</sub> and out-of-plane A<sub>1g</sub> modes of 1T-TiS<sub>2</sub>.<sup>24</sup> Fig. 2(b) presents a comparison of the Raman spectra for 100 cycles and 50 cycles of TiS<sub>x</sub> deposited on WSe<sub>2</sub>. The peaks of WSe<sub>2</sub> show no noticeable changes or deterioration, confirming that the underlying WSe<sub>2</sub> remains intact, suggesting that van der Waals (vdW) contacts might be formed by depositing TiS<sub>x</sub> onto WSe<sub>2</sub> (as was the case for TiS<sub>x</sub> onto MoS<sub>2</sub>).<sup>24</sup>

High resolution X-ray photoelectron spectroscopy (XPS) of a freshly deposited layer of TiS<sub>x</sub> deposited at 100 °C was performed in a PHI-VersaProbe II (Physical Electronics Inc.) using a monochromated Al source. An initial survey was collected, and peaks were correct using the position of the C 1s. A 2 kV Ar ion beam was then used to etch layers, and high-resolution spectra for the O 1s, C 1s, N 1s, Ti 2p, W 5p and S 3s peaks were collected at the outset and after each cycle of ion-beam etching to obtain a depth profile. Data analysis was performed using CasaXPS software. A freshly exfoliated TiS<sub>2</sub> crystal was also used to calibrate the relative sensitivity factors (RSF) of Ti 2p and S 3s. Using XPS, we found a Ti : S ratio of 1 : 1.7 in the interior of the deposited layer. Some oxygen was observed in the film (<10%), bringing the ratio of Ti : (S + O) to approximately 1 : 1.9. The depth profile is shown in Fig. S4.

## Device fabrication

To fabricate the devices, we transferred the WSe<sub>2</sub> monolayer onto Al<sub>2</sub>O<sub>3</sub>/Pt/Ti/p + Si or Si<sub>3</sub>N<sub>4</sub>/p + Si *via* poly(methyl methacrylate) (PMMA)-assisted wet-transfer.<sup>27</sup> To define the channel regions of the WSe<sub>2</sub> FETs, we adhered to the recipe detailed in our recent publication.<sup>28</sup> For defining the source and drain contacts, we introduce a lift-off method for TiS<sub>x</sub> grown at 100 °C using a dual PMMA photoresist. Both A3 and A6 PMMA layers were spin-coated onto the samples at 4000 rpm. Electron beam lithography was then employed to define the contact patterns, followed by development in the same MIBK : IPA solution. Contacts were deposited using ALD for TiS<sub>x</sub> and e-beam evaporation for 30 nm of Au. Finally, the samples underwent a lift-off process to remove excess resist and metal by immersion in acetone for 1 h, followed by IPA for an additional 30 min. Capping of devices by MoO<sub>x</sub> was accomplished using thermal evaporation at a rate of 0.05 nm s<sup>-1</sup> for a thickness of 10 nm.

## Results and discussion

First, we measured control devices with Au contacts (reference devices), then devices with TiS<sub>x</sub> interlayer beneath the Au

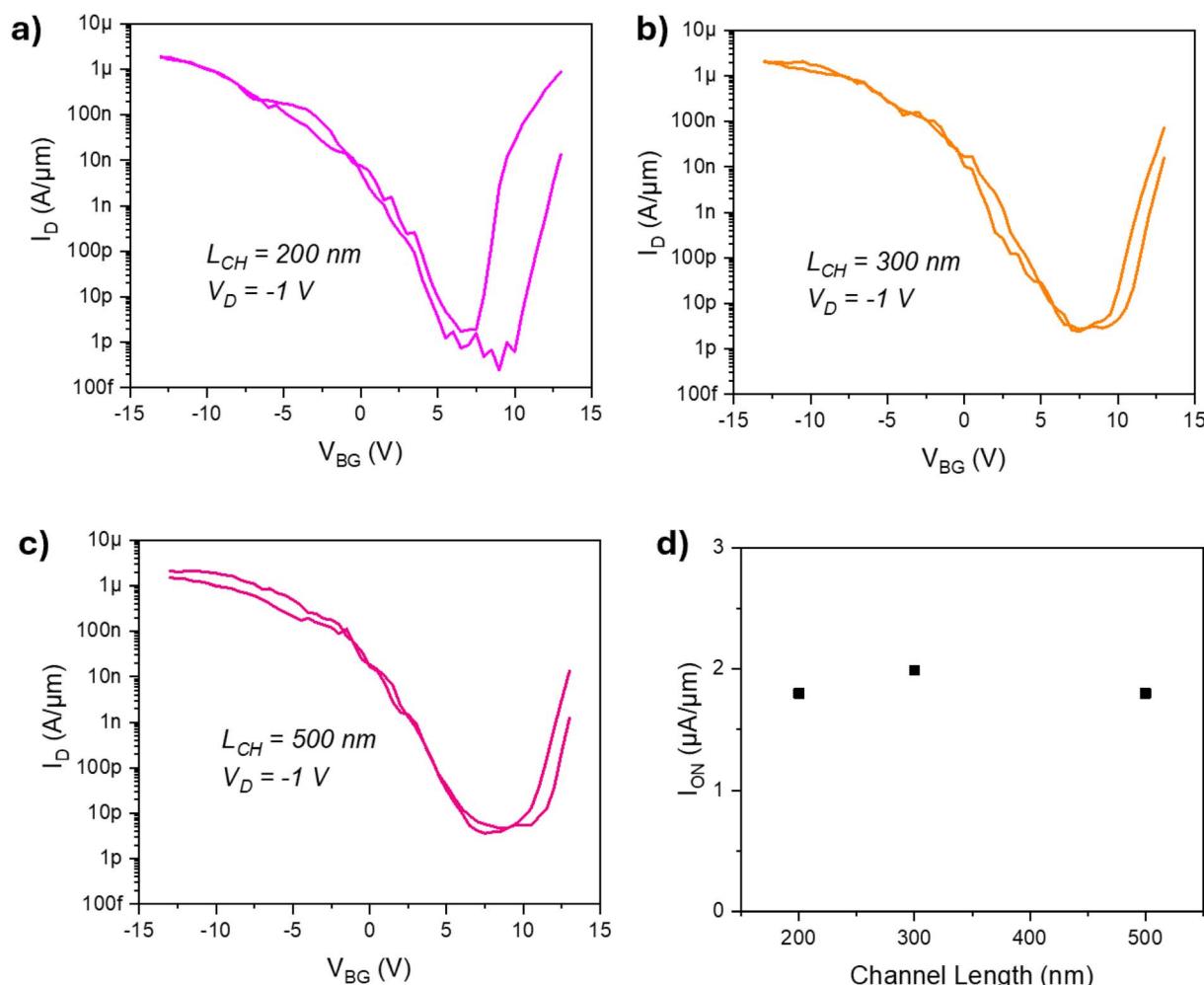

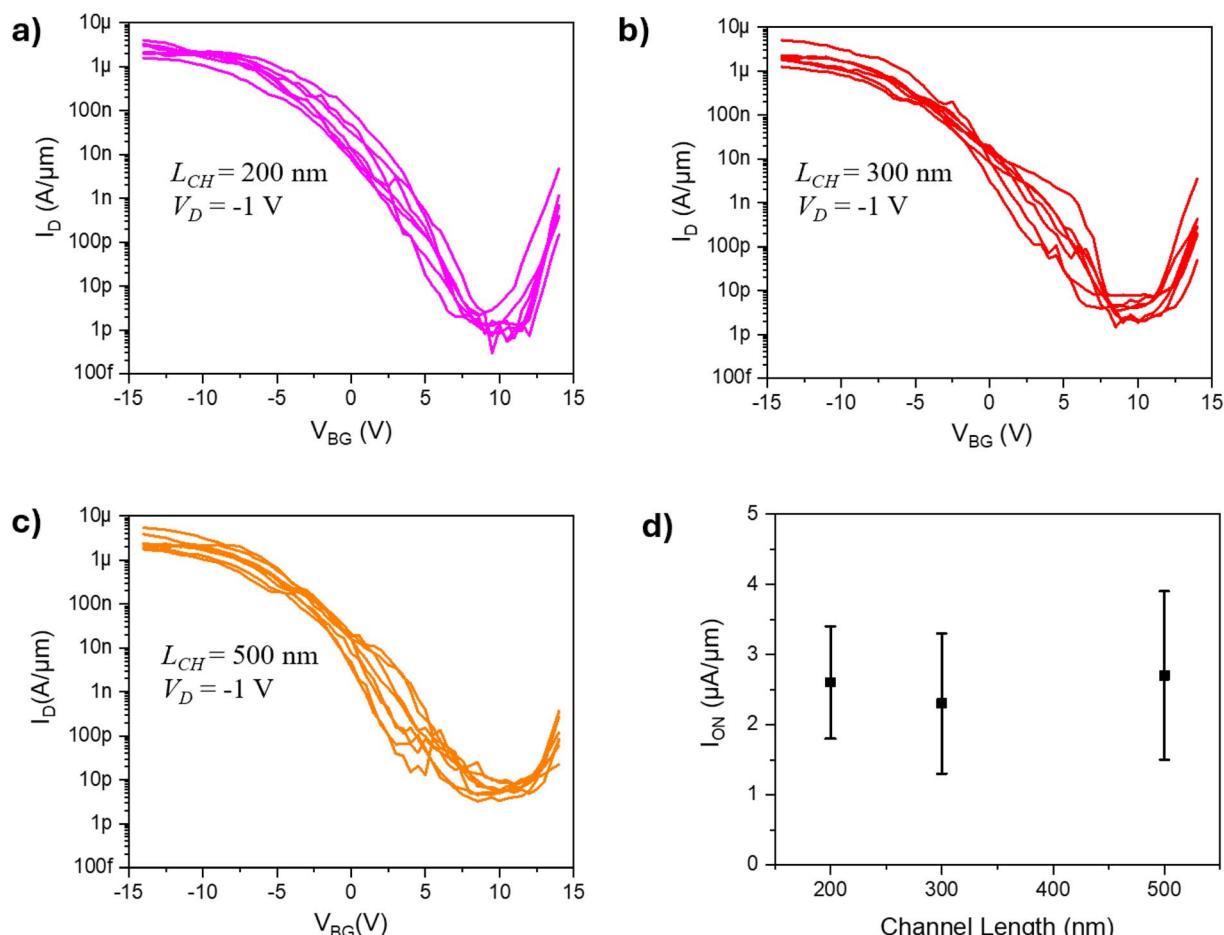

Fig. 4 7 nm TiS<sub>x</sub> contacts to WSe<sub>2</sub>. Transfer characteristic curves with different channel lengths of (a) 200 nm, (b) 300 nm, and (c) 500 nm and (d) maximum ON current variation in different channel lengths.

contacts. The transfer characteristics, *i.e.*, source-to-drain current ( $I_D$ ) *versus*  $V_{BG}$  of the WSe<sub>2</sub> FETs for a constant drain voltage ( $V_D$ ) of  $-1$  V, are shown for different channel lengths  $L_{CH} = 200$  nm, 300 nm, and 500 nm with no TiS<sub>x</sub> (reference Au contacts) in Fig. 3(a–c). The devices display ambipolar behavior. Fig. 3(d) shows the variation in  $I_{ON}$  current for different channel lengths. The maximum ON current varies slightly with channel length, with 200 nm channels showing an average maximum ON current of  $1.9 \mu\text{A} \mu\text{m}^{-1}$ , 300 nm channels yielding  $2 \mu\text{A} \mu\text{m}^{-1}$ , and 500 nm channels exhibiting  $1.8 \mu\text{A} \mu\text{m}^{-1}$  for the p-channel. The average subthreshold slope is  $1.4 \text{ V dec}^{-1}$  for the 200 nm channel,  $1.7 \text{ V dec}^{-1}$  for the 300 nm channel and  $1.6 \text{ V dec}^{-1}$  for the 500 nm channel while the mobility is  $0.41 \text{ cm}^2 \text{ V}^{-1} \text{ s}$  for the 200 nm channel,  $0.30 \text{ cm}^2 \text{ V}^{-1} \text{ s}$  for the 300 nm channel, and  $0.27 \text{ cm}^2 \text{ V}^{-1} \text{ s}$  for the 500 nm channel, respectively. We note that the measured field-effect mobility can be affected by the contacts and is not a fundamental materials property.

Then we studied the contacts with two different TiS<sub>x</sub> thicknesses beneath Au. All devices with TiS<sub>x</sub> contacts, regardless of thickness, continued to exhibit ambipolar characteristics but showed an enhanced p-branch compared to the reference device. This improvement is likely due to the higher work

function of TiS<sub>x</sub>, which exceeds that of Au ( $\sim 5.2$  eV). Thus, TiS<sub>x</sub> contacts appear to enhance hole injection, likely due to its high work function and the formation of clean contacts with WSe<sub>2</sub>. The transfer characteristics curve and maximum ON current variation with 100 cycles ( $\sim 7$  nm) TiS<sub>x</sub> contacts with different channel lengths are shown in Fig. 4. For the 7 nm contact, the ON current also varies with channel length: 200 nm channels exhibit an average maximum ON current of  $6.8 \mu\text{A} \mu\text{m}^{-1}$ , 300 nm channels yield  $7.0 \mu\text{A} \mu\text{m}^{-1}$ , and 500 nm channels show  $6.9 \mu\text{A} \mu\text{m}^{-1}$ . The average subthreshold slope is  $2 \text{ V dec}^{-1}$  for the 200 nm channel,  $1.6 \text{ V dec}^{-1}$  for the 300 nm channel, and  $1.8 \text{ V dec}^{-1}$  for the 500 nm channel, respectively, while the average mobility is  $0.89 \text{ cm}^2 \text{ V}^{-1} \text{ s}$  for the 200 nm channel,  $0.43 \text{ cm}^2 \text{ V}^{-1} \text{ s}$  for the 300 nm channel, and  $0.65 \text{ cm}^2 \text{ V}^{-1} \text{ s}$  for the 500 nm channel. Table S1 provides the device parameters for all these samples in our study.

The average ON-state current is nearly four times higher than the devices with the Au reference contacts. However, decreasing the TiS<sub>x</sub> thickness from 100 cycles ( $\sim 7$  nm) to 84 cycles ( $\sim 5$  nm) resulted in a decrease in average maximum ON current from  $6.8 \mu\text{A} \mu\text{m}^{-1}$  to  $2.6 \mu\text{A} \mu\text{m}^{-1}$  for the 200 nm channel, while from  $7.0 \mu\text{A} \mu\text{m}^{-1}$  to  $2.3 \mu\text{A} \mu\text{m}^{-1}$  for the 300 nm channel, and from  $6.9 \mu\text{A} \mu\text{m}^{-1}$  to  $2.7 \mu\text{A} \mu\text{m}^{-1}$  for the

Fig. 5 5 nm TiS<sub>x</sub> contacts to WSe<sub>2</sub>. Transfer characteristics with different channel lengths of (a) 200 nm, (b) 300 nm, and (c) 500 nm. (d) Maximum ON current variation in different channel lengths with standard deviation.

500 nm channel shown in Fig. 5. A similar decreasing trend in ON current was also observed in a previous study for  $\text{TiS}_x/\text{MoS}_2$ .<sup>23</sup> When including all data points from the TLM structures at a fixed overdrive voltage such as  $-11.5$  V for 5 nm and  $-13$  V for 7 nm  $\text{TiS}_x$  contacts, the resulting TLM plots (Fig. S5) do not yield a clear trend, making it unsuitable for extracting

the contact resistance for both cases. The performance was slightly better for contacts with 100 cycles ( $\sim 7$  nm) of  $\text{TiS}_x$  interlayers. We repeated the measurement with a 7 nm  $\text{TiS}_x$  layer on a Si wafer with a 100 nm  $\text{Si}_3\text{N}_4$  dielectric and observed a similar on-state current to the devices with 50 nm  $\text{Al}_2\text{O}_3$  as the dielectric, as shown in Fig. S6.

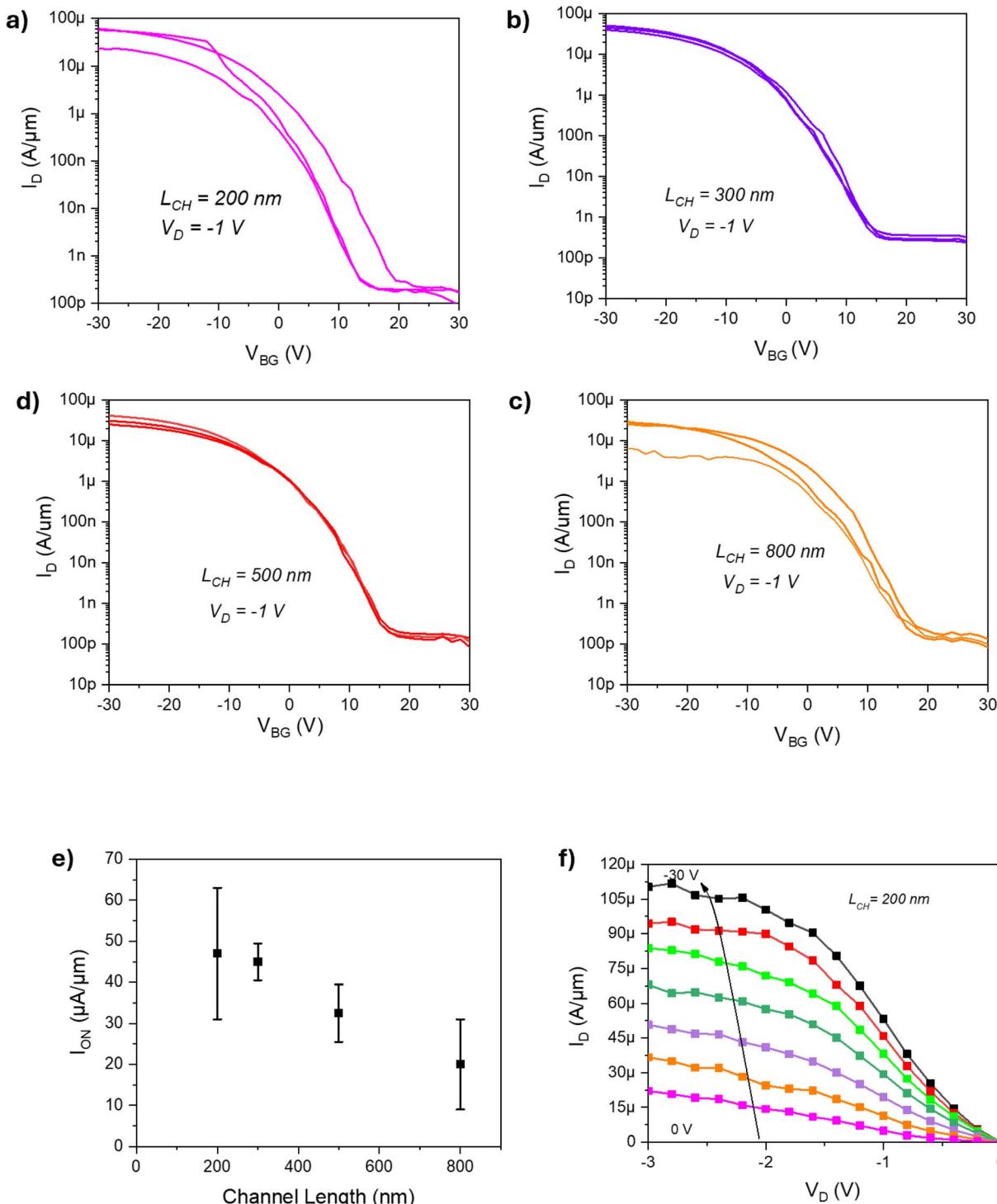

Fig. 6 Transfer characteristics, *i.e.*, source-to-drain current ( $I_D$ ) versus back-gate voltage ( $V_{BG}$ ) for a constant drain voltage for different channel lengths: (a) 200 nm, (b) 300 nm, (c) 500 nm, (d) 800 nm. (e) Maximum ON current variation with standard deviation. (f) Output characteristics ( $I_D$ – $V_D$ ) for different back-gate voltages.

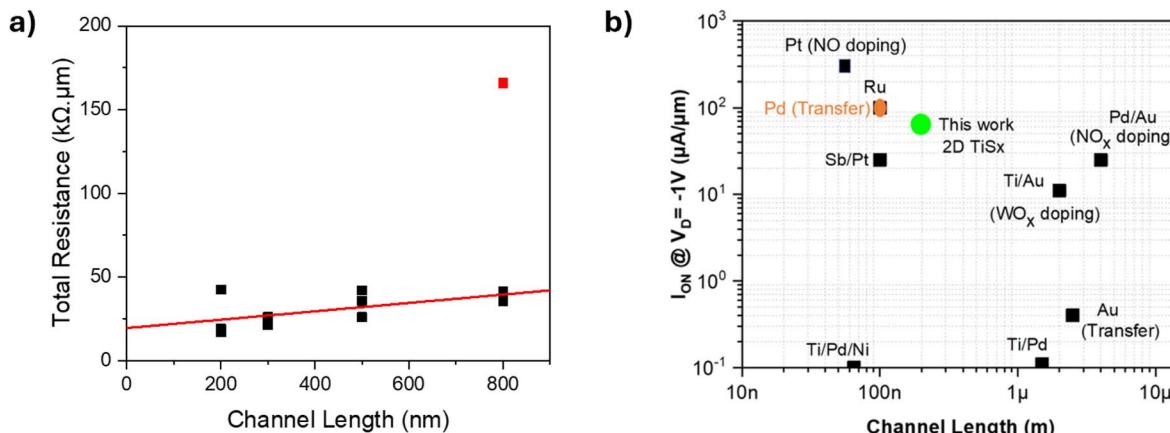

Fig. 7 (a) Resistance vs. channel length for the extraction of contact resistance ( $n_s = 1.51 \times 10^{13} \text{ cm}^{-2}$ ). (b) Comparison of  $I_{\text{ON}}$  at  $V_D = -1 \text{ V}$  for the best 7 nm  $\text{TiS}_x$  contacts with  $\text{MoO}_x$  capping on 1L  $\text{WSe}_2$  p-channel FETs.

### MoO<sub>x</sub> capping to boost performance

To further enhance the  $I_{\text{ON}}$ , we capped the pFETs with a 10 nm  $\text{MoO}_x$  layer (sheet resistance  $> 1 \text{ M}\Omega \square^{-1}$ ) deposited *via* thermal evaporation. Modulation doping as well as an enhancement of  $I_{\text{ON}}$  can be induced by a  $\text{MoO}_x$  capping layer on pFETs.<sup>7</sup> Following the optimization of  $\text{TiS}_x$  contacts and capping layers, we observed enhanced transport characteristics in the  $\text{WSe}_2$  pFETs by incorporating  $\text{MoO}_x$  caps. The transfer characteristics for all monolayer  $\text{WSe}_2$  pFET are shown in Fig. 6(a-d). The originally ambipolar behavior observed in  $\text{WSe}_2$  FETs with  $\text{TiS}_x$  contacts was converted to completely unipolar (p-type) transport through  $\text{MoO}_x$  doping. The variation in ON current is shown in Fig. 6(e). The maximum  $I_D$  for a pFET with the 7 nm  $\text{TiS}_x$ /30 nm Au contact and a 10 nm  $\text{MoO}_x$  cap is  $64 \mu\text{A} \mu\text{m}^{-1}$  for  $V_D = -1 \text{ V}$ . This represents around  $6 \times$  improvement in ON current compared to devices without  $\text{MoO}_x$ , using  $\text{TiS}_x$  contacts alone. Fig. 6(f) shows a representative output characteristic for a one-monolayer  $\text{WSe}_2$  pFET. Initially, we observe linear behavior up to  $V_D = -0.1 \text{ V}$ ; however, as the drain voltage increases, particularly around  $V_D = -1 \text{ V}$ , the  $I_D$ - $V_D$  characteristics become somewhat increasingly nonlinear. The nonlinearity in contact behavior is likely due to not being perfectly ohmic. Similar nonlinearities have been reported for Pt contacts to  $\text{WSe}_2$  and Pd contacts to  $\text{MoS}_2$ ,<sup>11</sup> and Cr contacts to laser doped  $\text{WSe}_2$ ,<sup>16</sup> which were all attributed to the presence of Schottky barriers. Likewise, a small Schottky barrier was observed for ALD-grown  $\text{TiS}_x$  contacts to  $\text{MoS}_2$ .<sup>24</sup> Transfer-length method (TLM) test structures were used to estimate the contact resistances of the optimized monolayer  $\text{WSe}_2$  pFETs to extract  $R_C$ . Since the device yield was relatively low ( $\sim 25\%$ ) excluding the devices gave almost no current, we were unable to obtain a complete set of data from a single TLM structure. The low device yield can be attributed to several factors: the  $\text{WSe}_2$  may contain gaps regions, the  $\text{TiS}_x$  film may not have nucleated uniformly across the contact area, and physical damage such as probe-induced scratching during measurements may have made it impossible to probe some devices.

To estimate the contact resistance, we combined results from multiple TLM structures at a fixed overdrive voltage ( $-32.5 \text{ V}$ ), which translates into a carrier density of  $n_s = 1.51 \times 10^{13} \text{ cm}^{-2}$ . To better extract the slope for contact resistance, we excluded a data point (marked in red) that deviated significantly. We extracted contact resistance of  $10 \pm 3 \text{ k}\Omega \mu\text{m}$  from the Fig. 7(a). The most recent p-channel  $\text{WSe}_2$  FETs using high-work function 2D  $\text{TaSe}_2$  combined with laser doping<sup>16</sup> reported a contact resistance of  $11 \text{ k}\Omega \mu\text{m}$ , which is similar.

Some improvements for future devices are recommended. The subthreshold slope (SS) was  $3.5 \text{ V dec}^{-1}$ , significantly higher than the ideal value of  $\sim 60 \text{ mV dec}^{-1}$ , attributed to the thicker oxide stack and non-idealities like interface traps.<sup>29</sup> To improve the SS, the use of high- $k$  dielectric materials and a thinner oxide stack could be employed.<sup>30</sup> We also observed hysteresis in our  $\text{WSe}_2$ -based FETs, as shown in Fig. S7, which could be due to charge trapping and measurements being conducted under ambient conditions.<sup>31,32</sup> To see saturation in the transfer characteristics, we therefore chose gate voltage sweeping from positive to negative for analysis.

Fig. 7(b) benchmarks the  $I_{\text{ON}}$  versus channel length for our study, alongside previous studies of monolayer CVD and exfoliated  $\text{WSe}_2$  FETs.<sup>7,14,33-39</sup> The  $I_{\text{ON}}$  for our best pFET is high among CVD 1L  $\text{WSe}_2$  reported in the literature. These devices demonstrate high performance for pFETs, making them a promising technology for advancing  $\text{WSe}_2$  FETs toward 2D CMOS electronics and advanced logic applications.

### Conclusion

In this study, we leveraged atomic layer deposition (ALD) to create high-work function semimetallic  $\text{TiS}_x$  contacts to facilitate efficient hole injection into  $\text{WSe}_2$ . The electrical performance of various contact configurations was evaluated for efficient hole injection into  $\text{WSe}_2$ .  $\text{MoO}_x$  capping layer onto the monolayer  $\text{WSe}_2$  p-channel also led to a dramatic improvement in the on-state current. The  $\text{TiS}_x$ /Au-contacted FETs with 200 nm channels achieved a maximum  $I_{\text{ON}}$  of  $\sim 64 \mu\text{A} \mu\text{m}^{-1}$  at  $V_D =$

–1 V. Additionally, the devices with the low contact resistance of  $10 \pm 3 \text{ k}\Omega \mu\text{m}$  at a carrier concentration of  $1.51 \times 10^{13} \text{ cm}^{-2}$  exhibited an  $I_{\text{ON}}/I_{\text{OFF}}$  ratio exceeding  $10^6$ , indicating excellent switching performance. Thus, our approach utilizing ALD-grown  $\text{TiS}_x$  interlayers in source/drain contacts with  $\text{MoO}_x$  capping of the channel presents a promising pathway for fabricating high-performance 2D FETs with significantly lower contact resistance for future nanoelectronics.

## Author contributions

M. S. R. conceived the idea and developed the study under the guidance of S. E. M. M. S. R. fabricated the devices, conducted the electrical measurements and characterized the data. C. W. C. conducted the growth of ALD and XPS of  $\text{TiS}_x$  films and x-ray photoel. M. S. R and C. W. C wrote the draft, and S. E. M revised the manuscript.

## Conflicts of interest

There are no conflicts to declare.

## Data availability

Data are provided in the supplementary information (SI), and for the growth of the  $\text{WSe}_2$  epilayers, in the repository cited as ref. 19.

Supplementary information: AFM image showing a monolayer of  $\text{WSe}_2$  with some bilayers (triangular shape) along with a Raman spectrum of CVD-grown  $\text{WSe}_2$  before metallization. Approximate GPC from QCM saturation study. Representative AFM image of a step edge. XPS depth profile of a  $\text{TiS}_x$  film deposited on  $\text{WSe}_2/\text{Al}_2\text{O}_3$  at  $100^\circ\text{C}$  by ALD. Data points from TLM test structures. 7 nm  $\text{TiS}_x$  contacts to  $\text{WSe}_2$  on  $\text{Si}_3\text{N}_4$ . Hysteresis in devices with Au contacts for  $V_D = -1 \text{ V}$ . Contact configurations and device performance. See DOI: <https://doi.org/10.1039/d5ra06569k>.

## Acknowledgements

The authors acknowledge the primary financial support of the National Science Foundation (NSF) through ECCS 2227346. Epilayers were provided by the Penn State 2D Crystal Consortium–Materials Innovation Platform (2DCC-MIP) under NSF DMR 2039351. The authors are also grateful to Yu Sheng Li at Penn State for help with AFM and Eilam Yalon and Emmanuel Ber at The Technion for helpful discussion.

## References

- 1 P. C. Shen, C. Su, Y. Lin, A. S. Chou, C. C. Cheng, J. H. Park, M. H. Chiu, A. Y. Lu, H. L. Tang, M. M. Tavakoli, G. Pitner, X. Ji, Z. Cai, N. Mao, J. Wang, V. Tung, J. Li, J. Bokor, A. Zettl, C. I. Wu, T. Palacios, L. J. Li and J. Kong, Ultralow Contact Resistance between Semimetal and Monolayer Semiconductors, *Nature*, 2021, **593**(7858), 211–217, DOI: [10.1038/s41586-021-03472-9](https://doi.org/10.1038/s41586-021-03472-9).

- 2 A.-S. Chou, T. Wu, C.-C. Cheng, S.-S. Zhan, I.-C. Ni, S.-Y. Wang, Y.-C. Chang, S.-L. Liew, E. Chen, W.-H. Chang, C.-I. Wu, J. Cai, H.-S. P. Wong and H. Wang, Antimony Semimetal Contact with Enhanced Thermal Stability for High Performance 2D Electronics, in. *2021 IEEE International Electron Devices Meeting (IEDM)*, IEEE, 2021, pp. 721–724, DOI: [10.1109/IEDM19574.2021.9720608](https://doi.org/10.1109/IEDM19574.2021.9720608).

- 3 A. Kumar, K. Schauble, K. M. Neilson, A. Tang, P. Ramesh, H.-S. P. Wong, E. Pop and K. Saraswat, Sub-200  $\Omega \cdot \mu\text{m}$  Alloyed Contacts to Synthetic Monolayer  $\text{MoS}_2$ , in. *2021 IEEE International Electron Devices Meeting (IEDM)*, IEEE, 2021, pp. 731–734, DOI: [10.1109/IEDM19574.2021.9720609](https://doi.org/10.1109/IEDM19574.2021.9720609).

- 4 Y. Wang and M. Chhowalla, Making Clean Electrical Contacts on 2D Transition Metal Dichalcogenides, *Nat. Rev. Phys.*, 2022, **4**(2), 101–112, DOI: [10.1038/s42254-021-00389-0](https://doi.org/10.1038/s42254-021-00389-0).

- 5 S. Das and J. Appenzeller,  $\text{WSe}_2$  Field Effect Transistors with Enhanced Ambipolar Characteristics, *Appl. Phys. Lett.*, 2013, **103**(10), 103501, DOI: [10.1063/1.4820408](https://doi.org/10.1063/1.4820408).

- 6 Z. Wang, Q. Li, Y. Chen, B. Cui, Y. Li, F. Besenbacher and M. Dong, The Ambipolar Transport Behavior of  $\text{WSe}_2$  Transistors and Its Analogue Circuits, *NPG Asia Mater.*, 2018, **10**(8), 703–712, DOI: [10.1038/s41427-018-0062-1](https://doi.org/10.1038/s41427-018-0062-1).

- 7 A.-S. Chou, Y.-T. Lin, Y. C. Lin, C.-H. Hsu, M.-Y. Li, S.-L. Liew, S.-A. Chou, H.-Y. Chen, H.-Y. Chiu, P.-H. Ho, M.-C. Hsu, Y.-W. Hsu, N. Yang, W.-Y. Woon, S. Liao, D.-H. Hou, C.-H. Chien, W.-H. Chang, I. Radu, C.-I. Wu, H.-S. Philip Wong and H. Wang, High-Performance Monolayer  $\text{WSe}_2$  p/n FETs via Antimony-Platinum Modulated Contact Technology towards 2D CMOS Electronics, in. *2022 International Electron Devices Meeting (IEDM)*, IEEE, 2022; pp. 721–724, DOI: [10.1109/IEDM45625.2022.10019491](https://doi.org/10.1109/IEDM45625.2022.10019491).

- 8 S. Chuang, C. Battaglia, A. Azcatl, S. McDonnell, J. S. Kang, X. Yin, M. Tosun, R. Kapadia, H. Fang, R. M. Wallace and A. Javey,  $\text{MoS}_2$  P-Type Transistors and Diodes Enabled by High Work Function  $\text{MoO}_x$  Contacts, *Nano Lett.*, 2014, **14**(3), 1337–1342, DOI: [10.1021/nl4043505](https://doi.org/10.1021/nl4043505).

- 9 N. H. Patoary, J. Xie, G. Zhou, F. Al Mamun, M. Sayyad, S. Tongay and I. S. Esqueda, Improvements in 2D P-Type  $\text{WSe}_2$  Transistors towards Ultimate CMOS Scaling, *Sci. Rep.*, 2023, **13**(1), 3304, DOI: [10.1038/s41598-023-30317-4](https://doi.org/10.1038/s41598-023-30317-4).

- 10 Y. Liu, S. Liu, Z. Wang, B. Li, K. Watanabe, T. Taniguchi, W. J. Yoo and J. Hone, Low-Resistance Metal Contacts to Encapsulated Semiconductor Monolayers with Long Transfer Length, *Nat. Electron.*, 2022, **5**(9), 579–585, DOI: [10.1038/s41928-022-00808-9](https://doi.org/10.1038/s41928-022-00808-9).

- 11 Y. Wang, J. C. Kim, Y. Li, K. Y. Ma, S. Hong, M. Kim, H. S. Shin, H. Y. Jeong and M. Chhowalla, P-Type Electrical Contacts for 2D Transition-Metal Dichalcogenides, *Nature*, 2022, **610**(7930), 61–66, DOI: [10.1038/s41586-022-05134-w](https://doi.org/10.1038/s41586-022-05134-w).

- 12 J. Kang, W. Liu, D. Sarkar, D. Jena and K. Banerjee, Computational Study of Metal Contacts to Monolayer Transition-Metal Dichalcogenide Semiconductors, *Phys. Rev. X*, 2014, **4**(3), 031005, DOI: [10.1103/PhysRevX.4.031005](https://doi.org/10.1103/PhysRevX.4.031005).

- 13 C. Gong, L. Colombo, R. M. Wallace and K. Cho, The Unusual Mechanism of Partial Fermi Level Pinning at

Metal–MoS<sub>2</sub> Interfaces, *Nano Lett.*, 2014, **14**(4), 1714–1720, DOI: [10.1021/nl403465v](https://doi.org/10.1021/nl403465v).

14 P. Zhao, D. Kiriya, A. Azcatl, C. Zhang, M. Tosun, Y.-S. Liu, M. Hettick, J. S. Kang, S. McDonnell, S. KC, J. Guo, K. Cho, R. M. Wallace and A. Javey, Air Stable P-Doping of WSe<sub>2</sub> by Covalent Functionalization, *ACS Nano*, 2014, **8**(10), 10808–10814, DOI: [10.1021/nn5047844](https://doi.org/10.1021/nn5047844).

15 C. Pang, T. Y. T. Hung, A. Khosravi, R. Addou, Q. Wang, M. J. Kim, R. M. Wallace and Z. Chen, Atomically Controlled Tunable Doping in High-Performance WSe<sub>2</sub> Devices, *Adv. Electron. Mater.*, 2020, **6**(8), 1901304, DOI: [10.1002/aelm.201901304](https://doi.org/10.1002/aelm.201901304).

16 B. Liu, X. Yue, C. Sheng, J. Chen, C. Tang, Y. Shan, J. Han, S. Shen, W. Wu, L. Li, Y. Lu, L. Hu, R. Liu, Z. J. Qiu and C. Cong, High-Performance Contact-Doped WSe<sub>2</sub> Transistors Using TaSe<sub>2</sub> Electrodes, *ACS Appl. Mater. Interfaces*, 2024, **16**(15), 19247–19253, DOI: [10.1021/acsami.4c01605](https://doi.org/10.1021/acsami.4c01605).

17 W. S. Leong, Q. Ji, N. Mao, Y. Han, H. Wang, A. J. Goodman, A. Vignon, C. Su, Y. Guo, P.-C. Shen, Z. Gao, D. A. Muller, W. A. Tisdale and J. Kong, Synthetic Lateral Metal–Semiconductor Heterostructures of Transition Metal Disulfides, *J. Am. Chem. Soc.*, 2018, **140**(39), 12354–12358, DOI: [10.1021/jacs.8b07806](https://doi.org/10.1021/jacs.8b07806).

18 H. Bark, Y. Choi, J. Jung, J. H. Kim, H. Kwon, J. Lee, Z. Lee, J. H. Cho and C. Lee, Large-Area Niobium Disulfide Thin Films as Transparent Electrodes for Devices Based on Two-Dimensional Materials, *Nanoscale*, 2018, **10**(3), 1056–1062, DOI: [10.1039/C7NR07593F](https://doi.org/10.1039/C7NR07593F).

19 Y. Liu, P. Stradins and S.-H. Wei, Van Der Waals Metal–Semiconductor Junction: Weak Fermi Level Pinning Enables Effective Tuning of Schottky Barrier, *Sci. Adv.*, 2016, **2**(4), e1600069, DOI: [10.1126/sciadv.1600069](https://doi.org/10.1126/sciadv.1600069).

20 Y.-J. Yu, Y. Zhao, S. Ryu, L. E. Brus, K. S. Kim and P. Kim, Tuning the Graphene Work Function by Electric Field Effect, *Nano Lett.*, 2009, **9**(10), 3430–3434, DOI: [10.1021/nl901572a](https://doi.org/10.1021/nl901572a).

21 J. Gao and M. Gupta, Titanium Disulfide as Schottky/Ohmic Contact for Monolayer Molybdenum Disulfide, *npj 2D Mater. Appl.*, 2020, **4**(1), 26, DOI: [10.1038/s41699-020-00161-5](https://doi.org/10.1038/s41699-020-00161-5).

22 T. Zhang, J. Miao, C. Huang, Z. Bian, M. Tian, H. Chen, R. Duan, L. Wang, Z. Liu, J. Qiao, Y. Xu, B. Yu and Y. Zhao, 2D Semimetal with Ultrahigh Work Function for Sub-0.1 V Threshold Voltage Operation of Metal–Semiconductor Field-Effect Transistors, *Mater. Des.*, 2023, **231**, 112035, DOI: [10.1016/j.matdes.2023.112035](https://doi.org/10.1016/j.matdes.2023.112035).

23 R. Mahlouji, W. M. M. E. Kessels, A. A. Sagade and A. A. Bol, ALD-Grown Two-Dimensional TiS<sub>x</sub> Metal Contacts for MoS<sub>2</sub> Field-Effect Transistors, *Nanoscale Adv.*, 2023, **5**(18), 4718–4727, DOI: [10.1039/D3NA00387F](https://doi.org/10.1039/D3NA00387F).

24 H. Yoon, S. Lee, J. Seo, I. Sohn, S. Jun, S. Hong, S. Im, Y. Nam, H.-J. Kim, Y. Lee, S. Chung and H. Kim, Investigation on Contact Properties of 2D van Der Waals Semimetallic 1T-TiS<sub>2</sub>/MoS<sub>2</sub> Heterojunctions, *ACS Appl. Mater. Interfaces*, 2024, **16**(9), 12095–12105, DOI: [10.1021/acsami.3c18982](https://doi.org/10.1021/acsami.3c18982).

25 H. Zhu, N. Nayir, T. H. Choudhury, A. Bansal, B. Huet, K. Zhang, A. A. Puretzky, S. Bachu, K. York, T. V. Mc Knight, N. Trainor, A. Oberoi, K. Wang, S. Das, R. A. Makin, S. M. Durbin, S. Huang, N. Alem, V. H. Crespi, A. C. T. van Duin and J. M. Redwing, Step Engineering for Nucleation and Domain Orientation Control in WSe<sub>2</sub> Epitaxy on C-Plane Sapphire, *Nat. Nanotechnol.*, 2023, **18**(11), 1295–1302, DOI: [10.1038/s41565-023-01456-6](https://doi.org/10.1038/s41565-023-01456-6).

26 S. B. Basuvalingam, Y. Zhang, M. A. Bloodgood, R. H. Godiksen, A. G. Curto, J. P. Hofmann, M. A. Verheijen, W. M. M. Kessels and A. A. Bol, Low-Temperature Phase-Controlled Synthesis of Titanium Di- and Tri-Sulfide by Atomic Layer Deposition, *Chem. Mater.*, 2019, **31**(22), 9354–9362, DOI: [10.1021/acs.chemmater.9b02895](https://doi.org/10.1021/acs.chemmater.9b02895).

27 F. Zhang, C. Erb, L. Runkle, X. Zhang and N. Alem, Etchant-Free Transfer of 2D Nanostructures, *Nanotechnology*, 2018, **29**(2), 025602, DOI: [10.1088/1361-6528/aa9c21](https://doi.org/10.1088/1361-6528/aa9c21).

28 M. Saifur Rahman, A. D. Agyapong and S. E. Mohney, Effect of Physical Vapor Deposition on Contacts to 2D MoS<sub>2</sub>, *J. Appl. Phys.*, 2024, **136**(22), 224303, DOI: [10.1063/5.0231261](https://doi.org/10.1063/5.0231261).

29 S. Ghosh, Y. Zheng, Z. Zhang, Y. Sun, T. F. Schranghamer, N. U. Sakib, A. Oberoi, C. Chen, J. M. Redwing, Y. Yang and S. Das, Monolithic and Heterogeneous Three-Dimensional Integration of Two-Dimensional Materials with High-Density Vias, *Nat. Electron.*, 2024, **7**(10), 892–903, DOI: [10.1038/s41928-024-01251-8](https://doi.org/10.1038/s41928-024-01251-8).

30 J.-S. Ko, A. Shearer, S. Lee, K. Neilson, M. Jaikissoon, K. Kim, S. Bent, K. Saraswat and E. Pop, Achieving 1-Nm-Scale Equivalent Oxide Thickness Top Gate Dielectric on Monolayer Transition Metal Dichalcogenide Transistors with CMOS-Friendly Approaches, in: *2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits)*, IEEE, 2024, pp. 1–2, DOI: [10.1109/VLSITechnologyandCir46783.2024.10631360](https://doi.org/10.1109/VLSITechnologyandCir46783.2024.10631360).

31 F. Ali, H. Choi, N. Ali, Y. Hassan, T. D. Ngo, F. Ahmed, W. Park, Z. Sun and W. J. Yoo, Achieving Near-Ideal Subthreshold Swing in P-Type WSe<sub>2</sub> Field-Effect Transistors, *Adv. Electron. Mater.*, 2024, **10**(9), 2400071, DOI: [10.1002/aelm.202400071](https://doi.org/10.1002/aelm.202400071).

32 C. Liu, X. Yan, P. Zhou and D. W. Zhang, Mobility Enhancement and Hysteresis Phenomenon in WSe<sub>2</sub> FETs, in: *2016 IEEE 16th International Conference on Nanotechnology (IEEE-NANO)*, IEEE, 2016, pp. 180–183, DOI: [10.1109/NANO.2016.7751488](https://doi.org/10.1109/NANO.2016.7751488).

33 K. Maxey, C. H. Naylor, K. P. O'Brien, A. Penumatcha, A. Oni, C. Mokhtarzadeh, C. J. Dorow, C. Rogan, B. Holybee, T. Tronic, D. Adams, N. Arefin, A. Sen Gupta, C.-C. Lin, T. Zhong, S. Lee, A. Kitamura, R. Bristol, S. B. Clendenning, U. Avci and M. Metz, 300 Mm MOCVD 2D CMOS Materials for More (Than) Moore Scaling, in: *2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits)*, IEEE, 2022, pp. 419–420, DOI: [10.1109/VLSITechnologyandCir46769.2022.9830457](https://doi.org/10.1109/VLSITechnologyandCir46769.2022.9830457).

34 C.-C. Chiang, H.-Y. Lan, C.-S. Pang, J. Appenzeller and Z. Chen, Air-Stable P-Doping in Record High-Performance Monolayer WSe<sub>2</sub> Devices, *IEEE Electron Device Lett.*, 2022, **43**(2), 319–322, DOI: [10.1109/LED.2021.3135312](https://doi.org/10.1109/LED.2021.3135312).

35 B. Liu, Y. Ma, A. Zhang, L. Chen, A. N. Abbas, Y. Liu, C. Shen, H. Wan and C. Zhou, High-Performance WSe<sub>2</sub> Field-Effect Transistors *via* Controlled Formation of In-Plane Heterojunctions, *ACS Nano*, 2016, **10**(5), 5153–5160, DOI: [10.1021/acsnano.6b00527](https://doi.org/10.1021/acsnano.6b00527).

36 L. Kong, X. Zhang, Q. Tao, M. Zhang, W. Dang, Z. Li, L. Feng, L. Liao, X. Duan and Y. Liu, Doping-Free Complementary WSe<sub>2</sub> Circuit *via* van Der Waals Metal Integration, *Nat. Commun.*, 2020, **11**(1), 1866, DOI: [10.1038/s41467-020-15776-x](https://doi.org/10.1038/s41467-020-15776-x).

37 M. Yamamoto, S. Nakaharai, K. Ueno and K. Tsukagoshi, Self-Limiting Oxides on WSe<sub>2</sub> as Controlled Surface Acceptors and Low-Resistance Hole Contacts, *Nano Lett.*, 2016, **16**(4), 2720–2727, DOI: [10.1021/acs.nanolett.6b00390](https://doi.org/10.1021/acs.nanolett.6b00390).

38 M. Li, X. Zhang, Z. Zhang, G. Peng, Z. Zhu, J. Li, S. Qin and M. Zhu, Unipolar P-Type Monolayer WSe<sub>2</sub> Field-Effect Transistors with High Current Density and Low Contact Resistance Enabled by van Der Waals Contacts, *Nano Res.*, 2024, **17**(11), 10162–10169, DOI: [10.1007/s12274-024-6942-5](https://doi.org/10.1007/s12274-024-6942-5).

39 H.-Y. Lan, C.-P. Lin, L. Liu, J. Cai, Z. Sun, P. Wu, Y. Tan, S.-H. Yang, T.-H. Hou, J. Appenzeller and Z. Chen, Uncovering the Doping Mechanism of Nitric Oxide in High-Performance P-Type WSe<sub>2</sub> Transistors, *Nat. Commun.*, 2025, **16**(1), 4160, DOI: [10.1038/s41467-025-59423-9](https://doi.org/10.1038/s41467-025-59423-9).