# **RSC Advances**

# **PAPER**

View Article Online

View Journal | View Issue

Cite this: RSC Adv., 2025, 15, 38082

# Ab initio quantum transport investigation of Sub-3 nm $\beta$ -InSe transistors for future high-performance nanoelectronics

Mughira Ghafoor,<sup>a</sup> Rajwali Khan,<sup>\*b</sup> Salah Ud Din, <sup>b</sup>\*<sup>c</sup> Akif Safeen,<sup>d</sup> Quihui Li,<sup>a</sup> Xingyue Yang,<sup>a</sup> Zongmeng Yang<sup>a</sup> and Jing Lu<sup>\*aefghi</sup>

Recently, field-effect transistors (FETs) based on triple-layer InSe have been experimentally fabricated with a channel length of 10–20 nm. They show better performance than Si FETs in terms of transconductance and room-temperature ballistic ratio. Their device performance limits at shorter physical lengths remain to explore. We used the *ab initio* quantum transport simulation method to study monolayer (ML) and bilayer (BL) n-type  $\beta$ -InSe FETs with gate lengths ( $L_{\rm g}$ ) of 2 and 3 nm. The on-state current ( $l_{\rm on}$ ) values of the ML and BL n-type  $\beta$ -InSe FETs at both 2 and 3 nm  $L_{\rm g}$  can achieve the International Roadmap Technology for Semiconductors (ITRS) high-performance (HP) device standards. Specifically, the devices achieve  $l_{\rm on}$  values of 1236 and 648  $\mu$ A  $\mu$ m<sup>-1</sup> at  $L_{\rm g}=2$  nm for the ML and BL n-type  $\beta$ -InSe FETs, respectively, surpassing the standard on-state current (528  $\mu$ A  $\mu$ m<sup>-1</sup>) defined in the 2013 ITRS edition for HP applications. The power-delay product (power consumption), delay time, and energy-delay product (energy consumption) of ML and BL n-type  $\beta$ -InSe also meet the ITRS requirements for HP applications. The ML and BL n-type  $\beta$ -InSe FETs can be potential candidates for future electronics at sub-3 nm physical nodes.

Received 20th August 2025 Accepted 29th September 2025

DOI: 10.1039/d5ra06179b

rsc.li/rsc-advances

#### 1 Introduction

Current silicon-based traditional field-effect transistors (FETs) have approached a critical point due to short-channel effects (SCEs). SCEs appear drastically in logic switches with ultrashort channel lengths ( $L_{\rm ch}$ ) because of poor gate electrostatic control. As the  $L_{\rm g}$  decreases, the lateral electric field created by the drain and source electrodes begins to lower the potential barrier for carrier injection at the source electrode (a phenomenon known as drain-induced barrier lowering [DIBL]). This results in a large gate voltage swing (subthreshold swing (SS)),

which makes it difficult to turn off the transistor and leads to high power consumption and excessive heat dissipation. These SCEs are a bottleneck for the further development of Si-based devices.<sup>5</sup> So, it is pressing to find alternative channel materials to alleviate SCEs that could promote ultrasmall FETs at the commercial level.<sup>6</sup> Among two-dimensional (2D) layered semiconductor materials, the III–VI semiconductor indium selenide (InSe)<sup>7</sup> has garnered great attention due to its atomic-scale thickness, which provides excellent electrostatic gate control, and its dangling-bond-free and smooth surface, which produces high charge carrier mobility.<sup>8,9</sup> 2D InSe has a suitable direct bandgap of 1.26 eV and a high carrier mobility of 10<sup>3</sup> cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>10</sup> These advantages make InSe superior to other 2D channel materials for next-generation electronic applications.<sup>11,12</sup>

Recently, Jiang *et al.*<sup>13</sup> fabricated three-layered 2D InSe ultrashort ballistic transistors with  $L_{\rm ch}$  values of 10 and 20 nm, using yttrium-doped InSe (Y-InSe) as electrodes to achieve an ohmic contact with a negligible Schottky barrier, and an effective HfO<sub>2</sub> oxide thickness of 2.6 nm, operated at a bias voltage of 0.5 V. The 10-nm InSe FET exhibited effectively suppressed short-channel effects, with an on-state current of over 1 mA  $\mu$ m<sup>-1</sup>, a low SS of 75 mV per decade, a DIBL of 22 mV per V, and a current on/off ratio ( $I_{\rm on}/I_{\rm off}$ ) of >10<sup>7</sup>. This FET has the best on-state current of 1.43 mA  $\mu$ m<sup>-1</sup> with  $L_{\rm g}=20$  nm at  $V_{\rm bias}=0.7$  V. So, one interesting question arises: what is the device performance limit of few-layered InSe FETs with a gate-length below

<sup>&</sup>quot;State Key Laboratory for Mesoscopic Physics and School of Physics, Peking University, Beijing 100871, P. R. China. E-mail: jinglu@pku.edu.cn

<sup>&</sup>lt;sup>b</sup>National Water and Energy Center, United Arab Emirates University, Al Ain, 15551, United Arab Emirates. E-mail: rajwali@uaeu.ac.ae

School of Microelectronics, Southern University of Science and Technology, Shenzhen, China. E-mail: salah@sustech.edu.cn

<sup>&</sup>lt;sup>4</sup>Department of Physics, University of Poonch Rawalakot, Rawalakot, 12350, Pakistan <sup>c</sup>Collaborative Innovation Center of Quantum Matter, Beijing 100871, P. R. China

Beijing Key Laboratory for Magnetoelectrical Materials and Devices (BKL-MEMD),

Peking University, Beijing 100871, P. R. China

<sup>\*</sup>Peking University Yangtze Delta Institute of Optoelectronics, Nantong 226010, P. R. China

<sup>&</sup>lt;sup>h</sup>Key Laboratory for the Physics and Chemistry of Nanodevices, Peking University, Beijing 100871, P. R. China

Beijing Key Laboratory of Quantum Devices, Peking University, Beijing 100871, P. R. China

Paper

5 nm if an ohmic contact and an ultrathin effective oxide thickness of high-k dielectric are achieved?

The relationship between device performance and the number of layers is a research direction of great concern in 2D FETs. Device performance depends on the number of layers: on one hand, the increase in the number of layers of channel material provides additional conduction channels, leading to a high on-state current; on the other hand, an increase in the number of layers results in weak electrostatic gate controllability, thereby degrading the performance of the device. For example, recently, quantum transport simulation of sub-1 nm ML and BL WSe<sub>2</sub> FETs by Yang in 2025 reported that the device performance of the BL WSe<sub>2</sub> FET decreases in terms of on-state current (435  $\mu$ A  $\mu$ m<sup>-1</sup>) compared to the ML WSe<sub>2</sub> FET (712  $\mu$ A μm<sup>-1</sup>). The performance degraded due to the degradation of gate controllability and changes in the band structure. Experimentally, few-layer MoS<sub>2</sub> FETs with sub-10 nm gate lengths have exhibited good device performance against SCEs with an on/off ratio of 10<sup>5</sup>-10<sup>7</sup>, excellent switching with near-ideal subthreshold swing (SS) of 67-140 mV dec<sup>-1</sup>, and leakage currents of lower than  $10^{-6}\,\mu\text{A}\,\mu\text{m}^{-1}$ . <sup>15-18</sup> Significantly, Qi Zhang et al. fabricated cutting-edge 1T'-2H hetero-phase BL MoTe<sub>2</sub> field-effect transistors featuring a gate length of 4 nm, which exhibit remarkable switching performance characterized by a subthreshold swing of approximately 73 mV per decade and an on/off current ratio of >105.19

Our research plans to explore the theoretical performance limits of monolayer and bilayer β-phase InSe transistors. Herein, we investigated 5-nm-Lch double-gated (DG), layerdependent n-type β-InSe metal-oxide-semiconductor FETs (MOSFETs) by minimizing the  $L_g$  to 2 and 3 nm via ab initio quantum transport simulations. Excellent gate controllability was attained in the n-type ML  $\beta$ -InSe FETs. Notably, the on-state currents of 1236 and 1291  $\mu A \mu m^{-1}$  at  $L_g = 2$  and 3 nm, respectively, meet the HP device requirement of the 2028 ITRS standard, as outlined in the 2013 edition.20 The best device performance results, such as  $I_{\text{on}}$ , delay time ( $\tau$ ), and power-delay product (PDP), were obtained when  $L_g$  was scaled down to 2 nm for the optimized layer-dependent n-type β-InSe FETs at a fixed bias voltage of  $V_{\rm dd} = 0.57$  V. The on-state currents of the n-type ML and BL β-InSe FETs were 1236 and 648 μA μm<sup>-1</sup>, respectively, at  $L_{\rm g}=2$  nm, both surpassing the required HP ITRS criteria (528  $\mu$ A  $\mu$ m<sup>-1</sup>). Therefore, our theoretical prediction for In Se in the  $\beta$ -phase confirms it as an excellent channel material candidate for sub-3 nm physical node transistors in highperformance applications. 21,22

# 2 Computational details

The structural optimization of few-layer  $\beta$ -InSe was conducted using density functional theory (DFT) as implemented in the CASTEP code. <sup>23,24</sup> The exchange-correlation functional was based on the generalized gradient approximation (GGA) in the form of the Perdew–Burke–Ernzerhof (PBE). <sup>25</sup> The plane-wave basis set with an energy cut off of 450 eV was selected at a temperature of 300 K. The structure was relaxed using norm-conserving pseudopotentials, with a stress tolerance of 0.001 eV

${\rm \AA}^{-1}$  and a force tolerance of 0.01 GPa between two points. The k-point mesh for structure relaxation was set to  $11 \times 11 \times 1$ . The Heyd–Scuseria–Ernzerhof (HSE) exchange–correlation functional was adopted for band structure calculations.  $^{26}$  The spin–orbit interaction was excluded. A dense Monkhorst–Pack k-point mesh of  $31 \times 31 \times 1$  was used for band structure calculations. To eliminate artificial interactions in supercells due to periodic boundary conditions and to account for van der Waals (vdW) interactions, two corrections are considered: the DFT-D2 correction and the dipole correction.  $^{27,28}$  A 15 Å vacuum buffer space was considered along the z-direction to weaken interactions between the adjacent slabs in the 2D layered structure. After optimizing the primitive cell, a rectangular supercell was formed according to the transport orientation.

The transport properties of the FET device configurations were simulated with the density functional theory (DFT) combined with the nonequilibrium Green's function (NEGF), as employed in QuantumATK 2022.29 The exchange-correlation potential in the form of GGA-PBE was applied in all the device transport calculations. DFT-GGA is good for the single-electron approximation and tends to underestimate the band gap of intrinsic semiconductors. However, the channel is surrounded by a gate and dielectric, which strongly screens the electronelectron interaction.<sup>30</sup> The double-zeta (ζ) polarized (DZP) basis set was employed to accurately capture the shape of the molecular orbitals. The temperature was fixed at 300 K, and the real-space density mesh cut-off energy was set to 80 hartree. The DFT-GGA implementation was rigorous enough to determine the carrier transport in the FET configuration. The periodic, Neumann, and Dirichlet-type boundary conditions were used on the boundaries along the transverse, vertical, and transport directions, respectively.31 The β-InSe channel is located in the xz-plane, while transport is along the z-direction (Fig. 2(a)). To guarantee that the electrostatic potential in the central region is adequately screened, we prolonged the electrodes at the interface by extending their unit cell two times (11.5 Å) in the zdirection.<sup>32</sup> The periodicity of the channel in the x-direction (the plane of the β-InSe sheet, perpendicular to the transport direction z) was set to 32  $k_x$  points, and y was the confinement direction. We choose a dense k-point mesh along the periodic direction because electronic states with periodic boundaries are characterized precisely by selecting a fine sampling number of the k-points. 33 The injection of electrons/holes was set as a 32  $\times$  $1 \times 175$  Monkhorst-Pack k-point mesh in the x, y, and z directions, respectively, within the irreducible Brillouin zone.

In the two-probe MOSFET model, the device consists of a central region (including the scattering region) and the electrode region; the left and right electrodes are semi-infinite. The impact of the electrodes on the surface of the scattering region is taken into account in the form of self-energies  $\sum_{1/r,k\parallel}$ , <sup>34</sup> which are calculated from the electrode Hamiltonians and coupling Hamiltonians. The reciprocal lattice vector  $k_{\parallel}$  points along the surface-parallel direction (orthogonal to the transmission direction) in the irreducible Brillouin zone (IBZ). <sup>35</sup> The Hamiltonian matrix H of the central region, together with the overlap matrix S, generates the retarded Green's function matrix that includes the self-energies from the electrodes:

$$G_{k_{\parallel}}(E) = [(E + i\delta_{+})S_{k_{\parallel}} - H_{k_{\parallel}} - \sum_{l,k_{\parallel}} - \sum_{r,k_{\parallel}}]^{-1},$$

(1)

where  $\delta_+$  is an infinitesimal positive number. The transmission coefficient  $T_{k_{\parallel}}(E)$  is the average of the k-dependent transmission coefficient over the IBZ, defined as follows:

$$T_{k_{\parallel}}(E) = Tr \left[ \Gamma_{k_{\parallel}}^{1}(E) G_{k_{\parallel}}(E) \Gamma_{k_{\parallel}}^{r}(E) G_{k_{\parallel}}^{\dagger}(E) \right]. \tag{2}$$

Here, the gamma function  $I_{k_\parallel}^{1/\mathrm{r}}(E)$  stands for the energy-level broadening  $i(\Sigma_{1/\mathrm{r},k_\parallel}-\Sigma_{1/\mathrm{r},k_\parallel}^\dagger)$  of the right and left electrodes, expressed as self-energies, and the retarded  $G_{k_\parallel}(E)$  and advanced  $G_{k_\parallel}^\dagger(E)$  Green's functions are obtained from the NEGF method. Using the Landauer–Büttiker formula,<sup>36</sup> the drain current  $I_{\mathrm{ds}}$  at a given gate voltage  $V_{\mathrm{g}}$  and bias voltage  $V_{\mathrm{b}}$  is calculated as follows:

$$I_{ds}(V_{b}, V_{g}) = \frac{2e}{h} \int_{-\infty}^{+\infty} \{T(E, V_{b}, V_{g}) [f_{S}(E - \mu_{S}) - f_{D}(E - \mu_{D})]\} dE,$$

(3)

where  $f_{\rm S/D}$  is the Fermi–Dirac distribution function, and  $\mu_{\rm S/D}$  is the electrochemical potential of the source and drain electrodes.

The DFT method based on the single-electron approximation is used to model electron behavior in the FET configuration. The reliability of the *ab initio* quantum transport simulation is validated by comparing the calculated band gap of ML MoSe<sub>2</sub>, which is 1.52 eV at the DFT-GGA level, with an experimentally obtained value of 1.58 eV from angle-resolved photoemission spectroscopy.<sup>37</sup> It is also verified by a predicted high on-state current of 1.5 mA  $\mu m^{-1}$  for the ML InSe FET with  $L_{\rm g}=7$  nm, which well matches the observed value of 1.5 mA  $\mu m^{-1}$  for the trilayer  $\beta$ -InSe FET with  $L_{\rm g}=20$  nm.  $^{38,39}$

## 3 Results

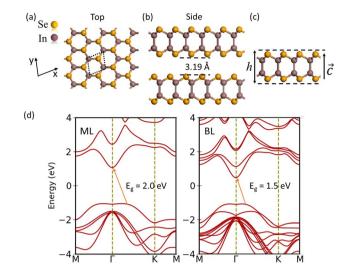

The ML β-phase InSe has a honeycomb lattice composed of a quadruple atomic sheet arranged in the order Se-In-In-Se. The structure exhibits strong covalent bonding within each layer, while weak van der Waals (vdW) forces exist between adjacent layers.40,41 The hexagonal primitive cell is labeled with a black-colored frame, as shown in Fig. 1(a), and shows the AB stacking sequence40 in Fig. 1(b). The optimized lattice parameters of ML  $\beta$ -InSe are as follows: a = 4.08 and c = 25.85 Å, which are consistent with previous experimental5 and theoretical results. 42,43 Fig. 1(c) exhibits the Se-Se height (h) of the ML β-InSe and the layer distance of 5.31 (ref. 42) and 3.19 Å,<sup>2</sup> respectively. The layered β-InSe structure shows a decrease in bandgap due to the quantum confinement effect. With the increase in the number of layers, the valence and conduction bands split into sub-bands, resulting in a reduced bandgap. The results illustrated in Fig. 1(d) indicate that the bandgap of β-InSe decreases from monolayer to bulk.5

In the  $\beta$ -InSe band structures, the conduction band minimum (CBM) is at the  $\Gamma$ -point, while the valence band maximum (VBM) is at the  $\Gamma$ -K direction, resulting in an indirect bandgap. It is noteworthy that the electronic band structure of  $\beta$ -InSe has a conversion from direct to indirect bandgap with

Fig. 1 (a) Top and side views of the bulk 2H-phase  $\beta$ -InSe structure. (b) The Layer stacking and layer distance. (c) The thickness of the ML InSe and the lattice vector along the c-direction. (d) The electronic band structures of ML and BL  $\beta$ -InSe at high-symmetric points in the irreducible Brillouin zone. The positions of the valence band maxima, conduction band minima, and the band gap ( $E_{\alpha}$ ) are indicated.

a decrease in the number of layers. <sup>44</sup> The band structures of the ML and BL hexagonal  $\beta$ -InSe, calculated with DFT-HSE approaches, are 2.0 and 1.5 eV, respectively, which is consistent with a previous report. <sup>26</sup> The band near the conduction band maxima is steeper than the valence band minima. It identifies a lighter electron-effective mass than that of the hole, which is clear evidence of high electron carrier current in the n-type  $\beta$ -InSe MOSFETs. In Fig. 1(d), from the band dispersion spectrum point of view, the electron effective mass  $(m_{\rm h}^*=0.23~m_0)$  is smaller than the hole effective mass  $(m_{\rm h}^*=2.5~m_0)$ . The effective mass is the reciprocal of the curvature of the band dispersion spectrum. A small effective mass increases carrier velocity  $\nu=\frac{1}{h}\frac{{\rm d}E}{{\rm d}k}=\frac{\hbar k}{m^*}$ , and thus the current.

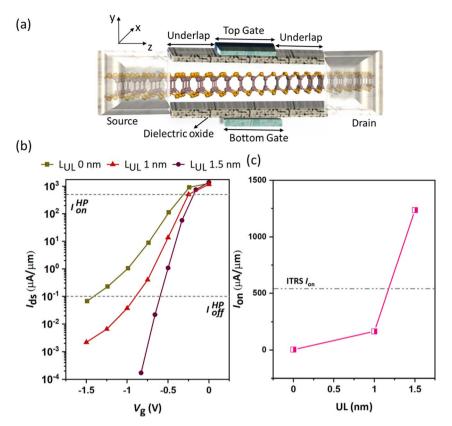

A schematic view of our double-gated (DG)  $\beta$ -InSe device with a 5 nm channel is illustrated in Fig. 2(a). In a FET, the potential generated by the source and drain consistently competes with the potential induced by the gate. The lesser the influence of the source and drain on the gate, the more effectively it can be controlled and adjusted by the gate. The length to which the electrical potential from the source and drain penetrates the channel is defined as the natural length  $\lambda$ :

$$\lambda = \sqrt{\alpha \frac{T_{\rm ch} T_{\rm ox} \varepsilon_{\rm ch}}{\varepsilon_{\rm ox}}},\tag{4}$$

where  $\alpha$  is the gate coefficient, while  $\varepsilon_{\rm ch}/\varepsilon_{\rm ox}$  and  $T_{\rm ch}/T_{\rm ox}$  is the dielectric constant and thickness of the gate oxide and channel, respectively. The  $\lambda$  is calculated to be 0.41 and 0.67 nm for ML and BL  $\beta$ -InSe, respectively, using  $\varepsilon_{\rm ch}=8.15$ . The increase in  $\lambda$  specifies a reduction in gate controllability over the channel due to the increasing number of layers. The drain and source electrodes are heavily doped with an n-type doping concentration

Fig. 2 (a) Schematic of the double gate (DG) InSe MOSFET with the underlap length on both sides of the gate as an extension region of the channel. The source and drain are symmetrically n-type doped. (b) Transfer characteristic and (c)  $I_{on}$  at different underlap lengths of  $L_{UL} = 0$ , 1, and 1.5 nm for the n-type ML DG β-InSe MOSFETs.

$(N_{\rm S/D})$  of 1  $\times$  10<sup>13</sup> cm<sup>-2</sup>. A high dielectric material (high-k), HfO2, with a dielectric constant of 20 and an effective oxide thickness (EOT) of 1.5 and 1.7 nm for  $L_g = 2$  and 3 nm, respectively, is employed. To further enhance the performance of devices, the device structure with underlap length  $(L_{UL})$ , i.e., an ungated section, is considered in the n-type few-layer β-InSe MOSFETs. The optimal  $L_{\rm UL}$  of 1.5 and 1 nm is symmetrically selected on both sides of the metal gate for  $L_g = 2$  and 3 nm, respectively. However, the whole length of the channel is equivalent to the sum of the underlap lengths and gate length, formulated as ( $L_{\rm ch} = L_{\rm g} + 2L_{\rm UL}$ ), and does not exceed 5-nm. The supply voltages ( $V_{\rm dd} = V_{\rm bias}$ ) are fixed to 0.57 and 0.59 V, according to the HP ITRS 2013 standard for  $L_{\rm g}=2$  and 3 nm, respectively. In transfer curves, the off-state voltage  $(V_{\text{off}})$  is the gate voltage at which the off-state current ( $I_{\rm off}$ ) is just 0.1  $\mu A$  $\mu m^{-1}$  for the HP-ITRS devices (2013 version) for the target year 2028. However,  $I_{on}$  can be evaluated at the specific on-state gate voltage  $(V_{g(on)} = V_{g(off)} + V_{dd})$  for n-type devices, where  $V_g$  is the gate voltage.

#### 3.1 Current

The conventional FET works on the operational principle of controlling the drain current  $(I_{\rm ds})$  by changing the gate voltage  $(V_{\rm gs})$  between the gate and the source. High switching speed demands a quick response from the FET to change in  $V_{\rm g}$ . This requires strong gate controllability in the FET devices. In this

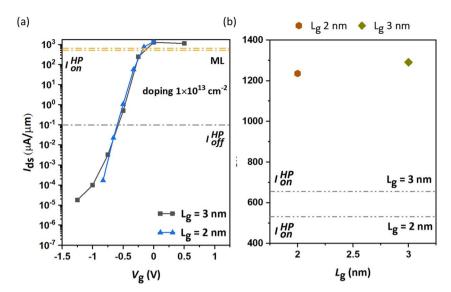

study, we begin our investigation of n-type doping  $(1 \times 10^{13}$ cm<sup>-2</sup>) in ML  $\beta$ -InSe with  $L_{\rm g}=2$  nm to get the transfer characteristics under  $L_{\rm UL}=0,\,1,\,{\rm and}\,\,1.5\,{\rm nm},\,{\rm as}\,{\rm shown}\,{\rm in}\,{\rm Fig.}\,\,2({\rm b}).$  It can be observed that the on-state current increases sharply with an increase in the UL region, reaching 4, 166, and 1236  $\mu$ A  $\mu$ m<sup>-1</sup> for the n-type ML  $\beta$ -InSe, as illustrated in Fig. 2(c). We selected the optimal UL length of 1.5 nm for different  $L_g$  values of 2 and 3 nm. The current  $(I_{ds})$  transfer characteristics for the n-type ML β-InSe MOSFET devices at  $L_{\rm g}=2$  and 3 nm are shown in Fig. 3(a). The on-state currents for the gate lengths of 2 and 3 nm are nearly comparable, at 1236 and 1291  $\mu A \mu m^{-1}$ , respectively, and outperforms the HP ITRS device requirement of  $I_{\rm on}$  (528 and 650  $\mu A~\mu m^{-1}$ ), as shown in Fig. 3(b). The evidential best-performing transfer characteristics  $(I_{on})$  at different gate lengths encourage us to choose InSe MOSFETs with  $L_g = 2$  nm for layer-dependent device performance.

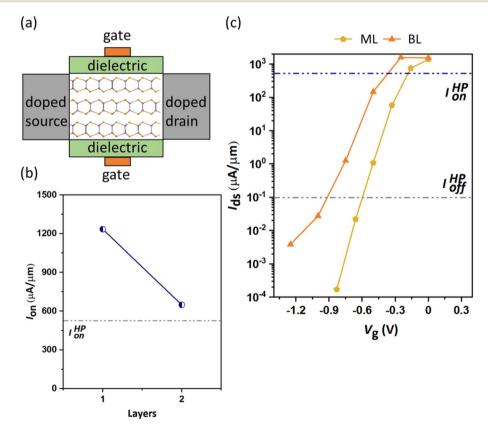

The schematic view of the layered DG β-InSe channel configuration is shown in Fig. 4(a). The crucial figure of merit for logic devices,  $I_{\rm on}$ , is obtained for ML and BL n-type β-InSe MOSFETs, as presented in the layer-dependent transfer characteristics in Fig. 4(b). All the calculated transfer curves for the n-type β-InSe MOSFETs could easily reach the HP off-state current (0.1  $\mu$ A  $\mu$ m<sup>-1</sup>) for devices with  $L_{\rm g}=2$  nm, and the onstate current values of the ML and BL β-InSe devices surpass the HP ITRS device requirements (528  $\mu$ A  $\mu$ m<sup>-1</sup>). Specifically,  $I_{\rm on}$  for ML and BL n-type β-InSe FETs are 1236 and 648  $\mu$ A  $\mu$ m<sup>-1</sup>,

Fig. 3 (a) Transfer characteristics and (b)  $I_{on}$  at different gate lengths of  $L_{q}=2$  and 3 nm for the n-type ML  $\beta$ -InSe MOSFETs.

respectively, compared to the HP ITRS target for 2028. The gradual decrease in on-state currents of the layer-dependent n-type  $\beta$ -InSe FETs with increasing layer number is illustrated in Fig. 4(c). The relationship between the number of layers often leads to more conductive channels as the number of layers increases. On the other hand, an increase in channel thickness

may lead to a reduction in the gate control ability. Based on the figure of merit,  $I_{\rm on}$ , the performance of layer-dependent n-type β-InSe MOSFETs is predicted to degrade with an increasing number of layers, which may be attributed to the weakened gate control ability associated with the increase in the number of layers of the channel material.

Fig. 4 (a) Schematic of the layered InSe channel MOSFET. (b) Transfer characteristics at different layers with a fixed  $L_g$  of 2 nm. (c) Figure of merit,  $I_{on}$  for the n-type devices.

Fig. 5  $I_{\rm on}$  versus  $L_{\rm g}$  of the ML DG MOSFETs at sub-5 nm  $L_{\rm g}$  and different UL structures for HP devices.

Notably, the performance decline when moving from ML to BL  $\beta$ -InSe can be explained by several fundamental physical mechanisms. These mechanisms pertain to alterations in the electronic structure, carrier mobility, and interlayer interactions that take place during the transition from ML to a BL material. ML  $\beta$ -InSe features a direct bandgap. However, upon transitioning to BL  $\beta$ -InSe, the system frequently shifts to an indirect bandgap. This transition renders ML  $\beta$ -InSe more advantageous for certain applications in comparison to BL  $\beta$ -InSe. In BL  $\beta$ -InSe, the electronic structure is influenced by interlayer

interactions, leading to energy level splitting and a transition to an indirect bandgap. Typically, carrier mobility diminishes as the number of layers increases in 2D materials. This reduction is primarily due to interlayer coupling that occurs in BL configurations. Specifically, in the BL, carriers encounter additional scattering from interlayer interactions, which are not present in the ML scenario. Consequently, the electrical conductivity and carrier mobility in BL  $\beta$ -InSe are generally lower than those in ML  $\beta$ -InSe, thereby constraining its performance in transistor applications or high-speed electronics. Our calculated  $I_{\rm on}$  for n-type ML and BL  $\beta$ -InSe FETs with  $L_{\rm g}=2$  nm is comparable to that of other ML 2D-material MOSFETs with longer  $L_{\rm g}$ , for example, MoS<sub>2</sub>,<sup>47</sup> ReS<sub>2</sub>,<sup>48</sup> GeS,<sup>49</sup> SnSe<sub>2</sub>,<sup>50</sup> InSe,<sup>12,51</sup> and silicane,<sup>52</sup> as shown in Fig. 5.

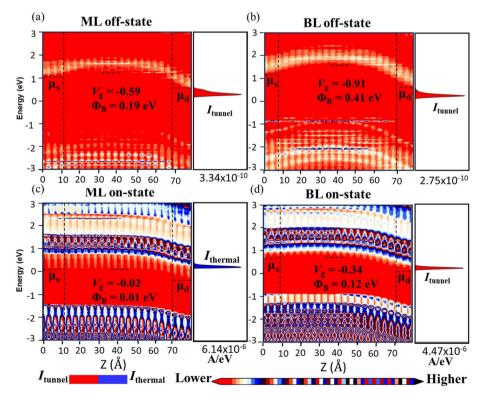

The gate modulation and current variation mechanisms are unveiled by the position-fixed local density of states (LDOS) and the current spectrum of 2-nm- $L_{\rm g}$  n-MOSFETs for ML and BL β-InSe at a bias of  $V_{\rm dd}=0.57$  V, as shown in Fig. 6. We investigated the layered structure of β-InSe by simulating device performance at different gate voltages to analyze the on- and off-state currents. The high value of  $\Phi_{\rm B}$  leads to a sharp decrease in current with increasing gate voltage. The energy difference between the Fermi level of the source and the conduction band minima (CBM) of the channel is referred to as the electron activation energy ( $\Phi_{\rm B}$ ). Under a gate modulation of 0.57 V,  $\Phi_{\rm B}$  decreases gradually from off-state values of 0.19 and 0.41 eV to on-state values of 0.01 and 0.12 eV, respectively, corresponding to gate voltages ranging from off-state -0.59 and -0.91 V to on-

Fig. 6 Local device density of states and spectral currents of the ML and BL n-type  $\beta$ -InSe MOSFETs with  $L_g=2$  nm at the (a and b) off- and (c and d) on-states, with  $L_{UL}=1.5$  nm.  $V_{dd}=\mu_d-\mu_s=0.57$  eV.

state -0.02 and -0.34 eV, in increasing order from the ML to BL n-type β-InSe, respectively. The CBM within the channel region increases with an increasing number of layers in the  $\beta$ -InSe channel material. This leads to a reduction in off-state current from ML to BL, recorded as 3.34  $\times$   $10^{-10}$  and 2.75  $\times$   $10^{-10}$  A eV<sup>-1</sup>, respectively (0.1  $\mu A$   $\mu m^{-1}$  for the ITRS HP goal). Conversely, the on-state currents decrease from ML to BL n-type β-InSe, recorded as  $6.14 \times 10^{-6}$  and  $4.47 \times 10^{-6}$  A eV<sup>-1</sup>, respectively. Usually,  $I_{\rm on}$  is composed of both thermionic current and tunnelling current; however, in our investigation of layer-dependent n-type  $\beta$ -InSe, the transport characteristics are primarily influenced by tunneling current ( $I_{tunnel}$ ), except for the on-state n-type ML β-InSe device. The lack of thermal current indicates a significant barrier height in the source-to-drain region, resulting in minimal contribution from thermal current to the overall current. This evidence is verified by the current spectra shown in Fig. 6. For the on-state LDOS of the ML β-InSe MOSFET, the barrier height is reduced to zero. Therefore, the current saturates, and the thermal current  $I_{\text{threm}}$  becomes dominant.

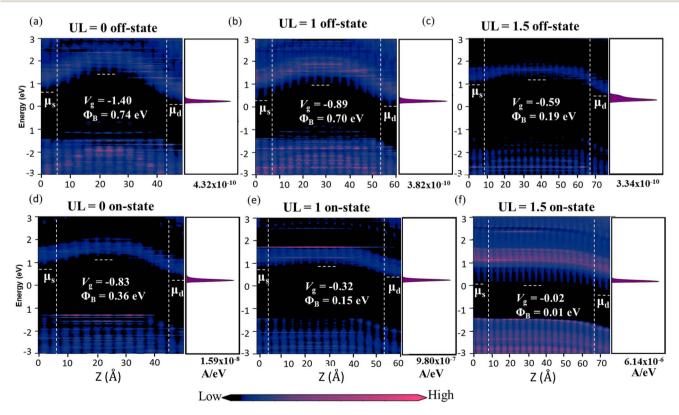

The local density of states and spectral current are illustrated in Fig. 7 to assess the performance of transistors across various UL structures. As  $L_{\rm UL}$  increases from 0 to 1 and 1.5 nm, the effective channel length of the device increases, tunneling leakage current reduces (Fig. 7(a-c)), and the on-state current increases (Fig. 7(d-f)). The improvement in gate control due to longer  $L_{\rm UL}$  is reflected in the enhanced modulation of the band edge locations at smaller  $V_{\rm g}$  values. Therefore, the short-

channel effects are suppressed significantly. In this investigation, we take n-type ML  $\beta$ -InSe DG MOSFETs with  $L_g = 2$  nm and varying UL lengths as an example. By keeping the off-state current fixed at 0.1 μA μm<sup>-1</sup>, the energy barrier is high at 0.74, 0.70, and 0.19 eV for  $L_{\rm UL} = 0$ , 1, and 1.5 nm, respectively, and the three spectral currents are of the same order of magnitude. The CBMs of the n-type ML β-InSe MOSFETs move downward in the channel region under gate modulation of 0.57 eV, and hence the devices turn into the on-state. The  $\Phi_{\rm B}$  for  $L_{\rm UL} = 0$  nm is 0.36 eV, which decreases significantly to 0.15 and 0.01 eV for  $L_{\rm UL} = 1$  and 1.5 nm, respectively. It can be predicted that enhanced electrostatics induced by increasing UL length favor a high on-state current. The magnitude of the spectral current indicates the increase in current with long  $L_{\rm UL}$ : 1.59  $\times$  $10^{-8}$ ,  $9.80 \times 10^{-7}$ , and  $6.14 \times 10^{-6}$  for  $L_{\rm UL} = 0$ , 1, and 1.5 nm, respectively. The current mainly comes from transmissions above the source chemical potential  $(\mu_s)$  in terms of spectral current. The on-state current enhances rapidly to 4, 166, and 1236  $\mu A \mu m^{-1}$  for  $L_{UL} = 0$ , 1, and 1.5 nm, respectively.

## 3.2 Subthreshold swing

Subthreshold swing (SS) is an important index for assessing gate controllability in MOSFETs within the subthreshold region. It can be described as the change in gate voltage necessary to change the drain current by one order of magnitude. It is formulated as SS =  $\frac{\partial V_{\rm gs}}{\partial \log I_{\rm ds}}$ . The lowest limit of SS is

Fig. 7 Local device density of states and spectral currents of the ML n-type  $\beta$ -InSe MOSFETs at different UL structures with  $L_g=2$  nm at the (a–c) off- and (d–f) on-states.  $V_{dd}=\mu_d-\mu_s=0.57$  eV.

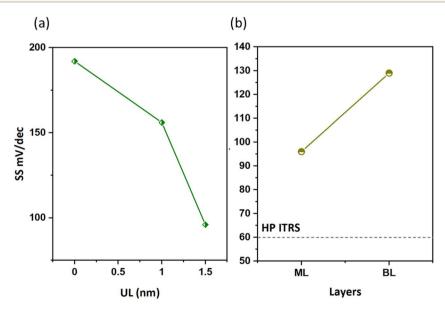

60 mV dec<sup>-1</sup> according to the "Boltzmann tyranny". 45 We extracted SS from the transfer characteristics of ML and fewlayered n-type DG β-InSe MOSFETs with different UL values, as shown in Fig. 8(a and b). SS decreases rapidly as  $L_{\text{III}}$  increases from 0 to 1 and 1.5 nm. SS at UL = 0 and 1 nm is calculated as 192 and 156 mV dec<sup>-1</sup>, respectively, while SS decreases rapidly to 96 mV  $dec^{-1}$  when  $L_{UL}$  is further increased to 1.5 nm at the same gate length, as shown in Fig. 8(a). By implementing a longer UL length, SS experiences a significant reduction. The reason for adopting an elongated UL structure lies in its ability to enhance the effective channel length, thereby mitigating leakage through the source-to-drain electrode and improving the efficiency of gate electrostatics. Notably, to achieve a small value of SS, we suggest a long UL structure, particularly for  $L_g$ 2 nm in the fabrication of layered β-InSe MOSFETs. For n-type DG β-InSe MOSFETs, SS is 96 for ML β-InSe FET devices. As the number of layers increases to BL, SS increases rapidly to 129 mV dec<sup>-1</sup> due to short-channel effects, as shown in Fig. 8(b). Large variations in gate voltage are required to switch the transistor between the off- and on-states. It also predicts that the source-to-drain leakage current is more effectively suppressed in ML than in BL β-InSe MOSFETs. Increasing the number of layers inhibits tunnelling between the source and the drain, as it leads to an increase in channel thickness and reduction in electrostatic control. Thereby, a smaller SS presents better gate controllability of the channel. SS is expressed as

$$SS = \left(\frac{\partial \lg I_{\rm ds}}{\partial V_{\rm g}}\right)^{-1} = \left(r_{\rm tunnel}SS_{\rm tunnel}^{-1} + (1 + r_{\rm tunnel})SS_{\rm therm}^{-1}\right)^{-1}, \tag{5}$$

where

$$SS_{\rm tunnel} = \left(\frac{\partial \lg I_{\rm tunnel}}{\partial V_{\rm g}}\right)^{-1}, \quad SS_{\rm therm} = \left(\frac{\partial \lg I_{\rm ds}}{\partial V_{\rm g}}\right)^{-1} \quad \text{and}$$

$$r_{\rm tunnel} = \frac{I_{\rm tunnel}}{I_{\rm ds}}. \quad \text{In ultrasmall-channel MOSFETs, tunnelling}$$

current is a major contributor. So,  $r_{\rm tunnel} \neq 0$ , and SS is less likely to approach the thermal limit of 60 mV dec $^{-1}$ . In case of

long channel lengths, the current comes from thermionic injection, so  $r_{\text{tunnel}} = 0$ , and SS reaches the lower thermionic limit (60 mV  $dec^{-1}$ ).

We evaluate device performance using another critical parameter: transconductance  $(g_m)$ . In the subthreshold region,  $g_{\rm m}$  is to estimate gate control for different layers of n-type  $\beta$ -InSe FETs. It is defined as the change in current per unit change in gate voltage, which can be formulated as  $g_{\rm m}=\frac{{

m d}I_{

m d}}{{

m d}V_{

m c}}$ . The  $g_{

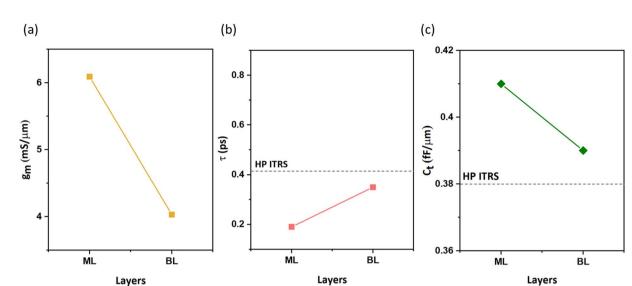

m m}$ values for n-type ML and BL DG β-InSe MOSFETs are plotted in Fig. 9(a). For the n-type ML and BL  $\beta$ -InSe FET devices,  $g_m$  values are 6.09 and 4.03 mS  $\mu$ m<sup>-1</sup>, respectively. In layered β-InSe,  $g_{\rm m}$ gradually decreases as the number of layers increases. A large value of gm indicates excellent gate control and explains the large  $I_{\text{on}}$  observed for the n-type ML and BL  $\beta$ -InSe FETs, which is larger than the HP ITRS on-state current standard. The gradual decrease in  $g_{\rm m}$  from ML to BL  $\beta$ -InSe FETs reflects weak gate control in the channel.

#### 3.3 Intrinsic delay time and power consumption

To measure the performance limits of few-layer n-type β-InSe FETs, the other figures of merit, such as delay time, total capacitance  $C_t$ , and power dissipation (PDP), are listed in Table 1. These figures of merit are shown in Fig. 9(b). The intrinsic delay time(au) =  $\frac{C_{\rm t}V_{\rm dd}}{I_{\rm on}}$  is a valid metric to evaluate device switching speed. The total capacitance  $C_t$  is the sum of the gate capacitance  $(C_g)$  and the fringing capacitance  $(C_f)$  $2C_{\rm t}$ ). So, the total capacitance is three times the gate capacitance,  $C_{\rm t}=3 \times \frac{\partial Q_{\rm ch}}{W \partial V_{\rm g}}$ , where  $\partial Q_{\rm ch}=Q_{\rm on}-Q_{\rm off}$  is the total charge in the central region of the device, where  $\partial V_{\rm ch} = V_{\rm on}$  –  $V_{\text{off}}$ , and W is the width of the 2D  $\beta$ -InSe sheet. The  $C_t$  of n-type ML and BL  $\beta$ -InSe FETs are calculated as 0.41 and 0.39 fF  $\mu$ m<sup>-1</sup>, respectively.  $C_t$  values for the n-type ML and BL  $\beta$ -InSe FETs can

Fig. 8 Subthreshold swing for n-type DG  $\beta$ -InSe MOSFETs with different UL structures (a) and for the layers of the n-type DG  $\beta$ -InSe MOSFETs (b)

**RSC Advances**

Fig. 9 (a) Transconductance, (b) total capacitance (c) and intrinsic delay time of the ML and BL n-type DG  $\beta$ -InSe MOSFETs at  $L_{\alpha}=2$  nm.

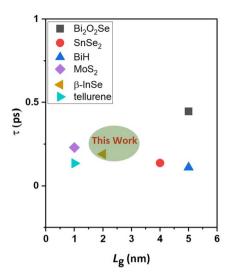

satisfy the ITRS requirement of 0.38 fF  $\mu m^{-1}$  for HP devices, as outlined in the 2013 version standard. The  $C_{\rm t}$  values of n-type  $\beta$ -InSe FETs decrease with increasing number of layers, as shown in Fig. 9(c). Additionally,  $\tau$  is proportional to  $C_{\rm t}$  and inversely proportional to  $I_{\rm on}$ . The ML and BL n-type  $\beta$ -InSe FETs with  $L_{\rm g}=2$  nm show  $\tau$  values of 0.190 and 0.350 ps, corresponding to currents of 1236 and 648  $\mu$ A  $\mu$ m<sup>-1</sup>, respectively, and can meet the set standard for the HP ITRS (0.410 ps) devices. The small values of  $\tau$  indicate superior performance in terms of switching capability. However, large values of the delay time result in low switching speeds for the transistor applied in a digital circuit. Our calculated  $\tau$  for ML n-type  $\beta$ -InSe FETs shows a switching rate comparable to sub-5 nm  $L_{\rm g}$  ML 2D-material FETs with long channel lengths, as illustrated in Fig. 10.

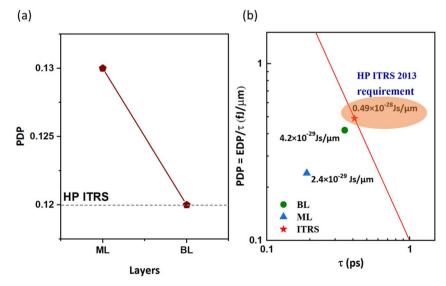

Power dissipation serves as a crucial metric for assessing energy consumption during a single on-off switching event. PDP can be determined using the equation PDP =  $V_{\rm dd}I_{\rm on}\tau = C_{\rm t}V_{\rm dd}^2$ . Fig. 11(a) illustrates the relationship between PDP and the number of layers against the ITRS 2013 standard for high-performance applications. According to the ITRS, PDP is proportional to  $C_{\rm t}$  at a fixed  $V_{\rm dd}=0.57$  V. In Fig. 11(a), PDP decreases from ML to BL n-type  $\beta$ -InSe FETs. Owing to the

monotonic decline in  $C_t$ , the n-type β-InSe FETs exhibit a symmetry reduction in PDP for the ML and BL n-type β-InSe FET configurations, with calculated values of 0.13 and 0.12 fJ  $\mu m^{-1}$ , respectively. The calculated PDP for the ML n-type β-InSe FET is 0.1 points higher than the HP ITRS standard value of 0.12 fJ  $\mu m^{-1}$  for the target year 2028. PDP values for the BL n-type β-InSe FETs align with the standard value of 0.12 fJ  $\mu m^{-1}$ . PDPs are close to the HP IRDS standard, which suggests a low power consumption and fast switching compared to the ML MoS<sub>2</sub> MOSFET (0.195 fJ  $\mu m^{-1}$ ).<sup>53</sup> For transistors, fast-switching speed and low power dissipation are preferred. However, these two goals frequently present a conflict, making it difficult to accomplish both at the same time. A high  $I_{\rm on}$  improves switching speed and power consumption, as reflected in the data shown in Table 1.

By taking switching speed and power dissipation into consideration, the energy-delay product (EDP) can be calculated by the following formula: PDP =  $\frac{EDP}{\tau}$ . The smaller the EDP, the better the device performance. EDPs for the layered structure configuration of the n-type  $\beta$ -InSe FETs are shown in Fig. 11(b). In this figure, the ITRS 2013 standard for the 2028 target is represented by a red star. The red line represents the equation

Table 1 Ballistic performance of n-type β-InSe DGFETs against the ITRS 2013 requirements for HP transistors of the next decades.  $L_{\rm g}$ : gate length. UL: underlap length.  $I_{\rm on}$ : on-state current. SS: subthreshold swing.  $g_{\rm m}$ : transconductance.  $C_{\rm t}$ : total capacitance.  $\tau$ : delay time. PDP: power-delay product. EDP: energy-delay product

| Parameters | L <sub>g</sub> (nm) | UL<br>(nm) | Doping<br>(cm <sup>-2</sup> ) | $I_{ m off}$ μΑ μ ${ m m}^{-1}$ | $I_{\rm on}$ μΑ μm $^{-1}$ | SS mV $\mathrm{dec^{-1}}$ | $C_{ m t}~{ m fF}~{ m \mu m}^{-1}$ | $g_{ m m}~{ m mS}~{ m \mu m}^{-1}$ | τ ps  | PDP fJ $\mu m^{-1}$ | EDP Js μm <sup>-1</sup> |

|------------|---------------------|------------|-------------------------------|---------------------------------|----------------------------|---------------------------|------------------------------------|------------------------------------|-------|---------------------|-------------------------|

| ITRS       | 2                   |            |                               | 0.1                             | 650/528                    |                           | 0.38                               |                                    | 0.410 | 0.12                | $0.49 \times 10^{-28}$  |

| ML n-type  | 2                   | 0          | $1 \times 10^{13}$            | 0.1                             | 4                          | 192                       |                                    |                                    |       |                     |                         |

| ML n-type  | 2                   | 1          | $1 \times 10^{13}$            | 0.1                             | 166                        | 156                       |                                    |                                    |       |                     |                         |

| ML n-type  | 2                   | 1.5        | $1 \times 10^{13}$            | 0.1                             | 1236                       | 96                        | 0.41                               | 6.09                               | 0.190 | 0.13                | $2.4\times10^{-29}$     |

| BL n-type  | 2                   | 1.5        | $1 \times 10^{13}$            | 0.1                             | 648                        | 129                       | 0.39                               | 4.03                               | 0.350 | 0.12                | $4.2 \times 10^{-29}$   |

| ML n-type  | 3                   | 1.5        | $1 \times 10^{13}$            | 0.1                             | 1291                       | 82                        | 0.60                               | 7.26                               | 0.272 | 0.20                | $4.9 \times 10^{-29}$   |

Fig. 10 Comparison of the switching speed of the ML n-type DG  $\beta$ -InSe MOSFETs with other 2D-material FETs at sub-5 nm  $L_{\alpha}$ .

PDP =  $\frac{\text{EDP}}{\tau}$ , where the EDP value is the requirement of the HP ITRS (0.492 × 10<sup>-28</sup> Js μm<sup>-1</sup>) for the target year 2028. The EDPs of ML and BL n-type β-InSe FETs are 2.4 × 10<sup>-29</sup> and 4.2 × 10<sup>-29</sup> Js μm<sup>-1</sup>, respectively, fulfilling the HP ITRS standard (0.492 × 10<sup>-28</sup> Js μm<sup>-2</sup>). EDP falls below the ITRS 2013 requirements, suggesting a promising future for n-type β-InSe FETs. To assess the performance of ML and BL n-type β-InSe MOSFETs, device performance metrics, especially  $I_{\rm on}$ ,  $\tau$ , and PDP, are analyzed and compared with those of ML FETs based on other 2D heterostructure materials. All comparative data are derived from theoretical calculations using ballistic transport theory. The  $I_{\rm on}$  of the ML n-type β-InSe FET (1236 μA μm<sup>-1</sup>) is higher than that of the BL n-type β-InSe FET (648 μA μm<sup>-1</sup>) and relatively higher than a few other 2D-material FETs with long  $L_{\rm g}$

values, as shown in Fig. 4(b).5 Notably, τ calculated for ML ntype β-InSe FETs shows a much smaller value, at 0.190 ps, which is lower than the ITRS HP standard, while the switching speed of the ML n-type  $\beta$ -InSe FET is comparable to that of other 2D-material FETs with long  $L_{\rm g}$  values, as shown in Fig. 10. The PDP of ML n-type  $\beta$ -InSe FET is 0.13 fJ  $\mu$ m<sup>-1</sup>, which is high and has a direct relation to the on-state current, while BL n-type β-InSe FETs own a low PDP value of 0.12 fJ  $\mu m^{-1}$  because of their reduced on-state current. PDP of 2D heterostructure is 0.018 fJ  $\mu m^{-1}$  for HP applications. The EDP for the ML n-type  $\beta$ -InSe FET  $(2.4 \times 10^{-29} \text{ Js } \mu\text{m}^{-1})$  is observed to be lower than the ITRS HP standard, as well as certain few-layer n-type β-InSe FETs. The high value of EDP is observed in the MoS2 FET with a channel length of 10 nm, while the best performance is attributed to the black phosphorus (BP) FET.55 The EDP values of the few-layer n-type β-InSe FETs are the average of the above devices, demonstrating excellent performance.

# 4 Discussion

In the search for 2D-material FETs that can replace conventional Si FETs, no 2D semiconductor-based experimental FETs have exhibited performance that could exceed that of Si FETs, while few-layer InSe has emerged as an interesting option. In 2D material FETs, achieving both low-resistance ohmic contacts and ultrathin effective oxide thicknesses simultaneously present significant challenges. Recently, Jiang *et al.* in 2023 (ref. 13 and 56) fabricated an ohmic-contact ballistic InSe FET with a channel length ranging from 10 to 20 nm. Yttrium doping (Y-doping) was applied at the top layer of the few-layered InSe to improve the contact between the 2D channel and the electrode, which induces a phase transition from semiconductor to semimetal. The Y-doped InSe and the top layer of pristine InSe have no Fermi Level Pinning effect, so the ohmic contact is formed, having a small resistance of  $64~\Omega~\mu m$ . An ultrathin high-

Fig. 11 (a) Power-delay product (PDP) of the n-type ML and BL  $\beta$ -InSe FETs at  $L_g=2$  nm and UL = 1.5 nm and (b) benchmarks of power dissipation (PDP = EDP/ $\tau$ ) vs. the effective delay time ( $\tau$ ) of the n-type ML and BL  $\beta$ -InSe FETs against the ITRS 2013 edition (represented by red star) for HP applications.

k dielectric material, HfO<sub>2</sub>, with an EOT of 2.6 nm, was utilized as the gate oxide. It is quite challenging to grow an ultrathin high-k dielectric layer on the dangling-bond-free surface of 2D materials. The best on-state current and transconductance are achieved for the triple-layer (TL) InSe FET with  $L_{\rm g}=20$  nm, at 1.20 and 1.43 mA  $\mu m^{-1}$  and 6.0 and 7.2 mS  $\mu m^{-1}$  at  $V_{dd}$  of 0.5 and 0.7 V, respectively. The triple-layer 2D InSe  $I_{\rm on}$  attains a theoretically predicted  $I_{\rm on}$  of 1.5 mA  $\mu {\rm m}^{-1}$  at  $L_{\rm g}=7~{\rm nm}.^{12}$  The significantly high on-state current is due to reduced carrier scattering because of small surface roughness and the danglingbond-free surface. On the other hand, the high on-state current in multilayer devices is attributed to the availability of a large density of states. Notably, the on-state current of 2D InSe FETs decreases monotonically from TL to ML. The poor performance of ML 2D InSe FETs is ascribed to direct Y-doping on the ML InSe to form electrodes. Covalent interactions occur in the lateral direction between Y-InSe and the semiconductor InSe, creating metal-induced gap states and resulting in a Schottky barrier. Another reason for the poor performance of low-current ML 2D InSe is the structural instability. An improved approach is utilizing BL InSe as electrodes, with doping applied only on the top layer. This method facilitates the formation of an Ohmic contact between the doped and undoped InSe layers.

Our theoretical simulation study predicts that, by realizing an ultrathin high-k dielectric of 1.5 nm and by realizing ohmic contact electrodes, ML and BL n-type  $\beta$ -InSe FETs outperform at  $I_{\rm on}$  values of 1236 and 648  $\mu$ A  $\mu$ m $^{-1}$ , respectively. The thicker channel experiences a decline in the degradation of the electrostatic control exerted by the gate.

# 5 Conclusion

In this work, we studied the ballistic limit of sub-3 nm ML and BL DG n-type β-InSe FETs by employing ab initio quantum transport simulations. The optimized ML n-type β-InSe FET was used at  $L_g = 2$  and 3 nm to explore the performance of devices for high  $I_{\rm on}$  of 1236 and 1291  $\mu A \mu m^{-1}$ , respectively. Thus, to further study few-layer n-type β-InSe FETs, the best device configuration was selected with  $L_{\rm g}=2$  nm and an optimal  $L_{\rm UL}$  of 1.5 nm to keep a  $L_{ch}$  of 5 nm, and employing a high-k dielectric HfO<sub>2</sub> gate dielectric with a thickness of 1.5 nm. It is predicted that ML and BL n-type  $\beta$ -InSe FETs can easily fulfill the HP ITRS device requirements. Other crucial figures of merit, such as  $\tau$ , PDP, and EDP, for ML and BL n-type β-InSe FETs are well matched with HP ITRS requirements of the 2013 version for the 2028 target. Thus, ML and BL n-type β-InSe FETs outperform several other 2D-material FETs, demonstrating strong potential for future nanoelectronics applications.

## Conflicts of interest

There are no conflicts to declare.

# Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

# Acknowledgements

This work is supported by the National Natural Science Foundation of China (Grants No. 12274002), the Ministry of Science and Technology of China (No. 2022YFA1203904), the Fundamental Research Funds for the Central Universities, the High-performance Computing Platform of Peking University, and the MatCloud + high throughput materials simulation engine.

## References

- 1 G. Iannaccone, F. Bonaccorso, L. Colombo and G. Fiori, Quantum engineering of transistors based on 2D materials heterostructures, *Nat. Nanotechnol.*, 2018, **13**, 183–191.

- 2 T. Shen, J. C. Ren, X. Liu, S. Li and W. Liu, Van der Waals Stacking Induced Transition from Schottky to Ohmic Contacts: 2D Metals on Multilayer InSe, *J. Am. Chem. Soc.*, 2019, 141, 3110–3115.

- 3 S. K. Su, *et al.*, Layered Semiconducting 2D Materials for Future Transistor Applications, *Small Struct.*, 2021, 2, 2000103.

- 4 Y. Taur and H. Tak, Fundamentals of Modern VLSI Devices-Fundamentals of Modern VLSI Devices, 2nd edn, Ning Frontmatter More information.

- 5 M. Dai, et al., Properties, Synthesis, and Device Applications of 2D Layered InSe, Adv. Mater. Technol., 2022, 7, 2200321.

- 6 O. Ü. Aktürk, V. O. Özçelik and S. Ciraci, Single-layer crystalline phases of antimony: Antimonenes, *Phys. Rev. B:Condens. Matter Mater. Phys.*, 2015, **91**, 235446.

- 7 G. Han, Z. G. Chen, J. Drennan and J. Zou, Indium selenides: Structural characteristics, synthesis and their thermoelectric performances, *Small*, 2014, **10**, 2747–2765.

- 8 F. Liu, Y. Wang, X. Liu, J. Wang and H. Guo, A Theoretical Investigation of Orientation-Dependent Transport in Monolayer MoS2 Transistors at the Ballistic Limit, *IEEE Electron Device Lett.*, 2015, **36**, 1091–1093.

- 9 M. Chhowalla, D. Jena and H. Zhang, Two-dimensional semiconductors for transistors, *Nat. Rev. Mater.*, 2016, 1, 16052.

- 10 W. Feng, X. Zhou, W. Q. Tian, W. Zheng and P. A. Hu, Performance improvement of multilayer InSe transistors with optimized metal contacts, *Phys. Chem. Chem. Phys.*, 2015, 17, 3653–3658.

- 11 D. A. Bandurin, *et al.*, High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe, *Nat. Nanotechnol.*, 2016, 12(3), 223–227.

- 12 Y. Wang, *et al.*, Many-Body Effect and Device Performance Limit of Monolayer InSe, *ACS Appl. Mater. Interfaces*, 2018, 10, 23344–23352.

- 13 J. Jiang, L. Xu, C. Qiu and L. M. Peng, Ballistic two-dimensional InSe transistors, *Nature*, 2023, **616**, 470–475.

- 14 X. Yang, et al., Ab-Initio Quantum Transport Simulation of Sub-1 nm Gate Length Monolayer and Bilayer WSe2 Transistors: Implications for Ultra-Scaled CMOS Technology, ACS Appl. Nano Mater., 2025, 8, 3460–3470.

Paper

- 15 H. Wan, et al., 3 nm Channel MoS2 Transistors by Electromigration of Metal Interconnection, ACS Appl. Electron. Mater., 2023, 5, 247-254.

- 16 A. Nourbakhsh, et al., MoS2 Field-Effect Transistor with Sub-10 nm Channel Length, Nano Lett., 2016, 16, 7798-7806.

- 17 J. Tian, et al., Scaling of MoS2 Transistors and Inverters to Sub-10 nm Channel Length with High Performance, Nano Lett., 2023, 23, 2764-2770.

- 18 K. Xu, et al., Sub-10 nm Nanopattern Architecture for 2D Material Field-Effect Transistors, Nano Lett., 2017, 17, 1065-1070.

- 19 Q. Zhang, et al., Simultaneous synthesis and integration of two-dimensional electronic components, Nat. Electron., 2019, 2, 164-170.

- 20 International Technology Roadmap for Semiconductors (ITRS) - Semiconductor Industry Association, 2015, https:// www.semiconductors.org/resources/2015-internationaltechnology-roadmap-for-semiconductors-itrs/.

- 21 S. U. Din, M. ul Haq, D. Baohui and L. Zhu, Design and synthesis of α-Bi2Mo3O12/CoSO4 composite nanofibers for high-performance SO2F2 sensors at room temperature, Mater. Today Nano, 2022, 17, 100154.

- 22 A novel ethanol gas sensor based on α-Bi<sub>2</sub>Mo<sub>3</sub>O<sub>12</sub>/Co<sub>3</sub>O<sub>4</sub> nanotube-decorated particles - RSC Advances, RSC Publishing, DOI: 10.1039/D0RA02591G, https:// pubs.rsc.org/en/content/articlehtml/2020/ra/d0ra02591g.

- 23 M. D. Segall, et al., First-principles simulation: ideas, illustrations and the CASTEPcode, J. Phys.: Condens. Matter, 2002, 14, 2717.

- 24 S. J. Clark, et al., First principles methods using CASTEP, Z. Kristallogr., 2005, 220, 567-570.

- 25 J. P. Perdew, K. Burke and M. Ernzerhof, Generalized Gradient Approximation Made Simple, Phys. Rev. Lett., 1996, 77, 3865.

- 26 Y. Guo and J. Robertson, Band structure, band offsets, substitutional doping, and Schottky barriers of bulk and monolayer InSe, Phys. Rev. Mater., 2017, 1, 044004.

- 27 S. Tsuzuki and T. Uchimaru, Accuracy of intermolecular interaction energies, particularly those of hetero-atom containing molecules obtained by DFT calculations with Grimme's D2, D3 and D3BJ dispersion corrections, Phys. Chem. Chem. Phys., 2020, 22, 22508-22519.

- 28 S. Grimme, Semiempirical GGA-type density functional constructed with a long-range dispersion correction, J. Comput. Chem., 2006, 27, 1787-1799.

- 29 S. Smidstrup, et al., QuantumATK: an integrated platform of electronic and atomic-scale modelling tools, J. Phys.: Condens. Matter, 2019, 32, 015901.

- 30 S. Gao and L. Yang, Renormalization of the quasiparticle band gap in doped two-dimensional materials from manybody calculations, Phys. Rev. B, 2017, 96, 155410.

- 31 A. H. D. Cheng and D. T. Cheng, Heritage and early history of the boundary element method, Eng. Anal. Bound. Elem., 2005, 29, 268-302.

- 32 S. Smidstrup, et al., QuantumATK: an integrated platform of electronic and atomic-scale modelling tools, J. Phys.: Condens. Matter, 2019, 32, 015901.

- 33 Á. Szabó, R. Rhyner and M. Luisier, Ab initio simulation of single- and few-layer MoS2 transistors: Effect of electronphonon scattering, Phys. Rev. B:Condens. Matter Mater. Phys., 2015, 92, 035435.

- 34 Z. Bai, T. Markussen and K. S. Thygesen, Electron Transport across a metal/MoS\$ 2\$ Interface: Dependence on Contact Area and Binding Distance, 2013.

- 35 H. Zhang, et al., Interfacial Properties of Monolayer Antimonene Devices, Phys. Rev. Appl., 2019, 11, 064001.

- 36 Electronic Transport in Mesoscopic Systems Supriyo Datta Google https://books.google.com/books? Books, hl=en&lr=&id=28BC-ofEhvUC&oi=fnd&pg

- =PR12&dq=Datta,+S.+Electronic+Transport+in

- +Mesoscopic+Systems,+Revised+ed.%3B+

Cambridge+University+Press:+Cambridge,

- +U.K.,+1997.&ots=mMWYAu5lis&sig

- =K1pPeCwJoGkvbPd9JwTJ9 8D8Xc#v=onepage&g&f=false.

- 37 Y. Liang and L. Yang, Carrier plasmon induced nonlinear band gap renormalization in two-dimensional semiconductors, Phys. Rev. Lett., 2015, 114, 063001.

- 38 Y. Wang, et al., Many-Body Effect and Device Performance Limit of Monolayer InSe, ACS Appl. Mater. Interfaces, 2018, 10, 23344-23352.

- 39 J. Jiang, L. Xu, C. Qiu and L. M. Peng, Ballistic twodimensional InSe transistors, Nature, 2023, 616, 470-475.

- 40 C. Carlone, S. Jandl and H. R. Shanks, Optical Phonons and Crystalline Symmetry of InSe, Phys. Status Solidi B, 1981, 103, 123-130.

- 41 Q. Hao, et al., Phase Identification and Strong Second Harmonic Generation in Pure ∈-InSe and Its Alloys, Nano Lett., 2019, 19, 2634-2640.

- 42 Y. Wang, et al., Many-Body Effect and Device Performance Limit of Monolayer InSe, ACS Appl. Mater. Interfaces, 2018, 10, 23344-23352.

- 43 B. Shi, et al., n-Type Ohmic contact and p-type Schottky contact of monolayer InSe transistors, Phys. Chem. Chem. Phys., 2018, 20, 24641-24651.

- 44 G. W. Mudd, et al., The direct-to-indirect band gap crossover in two-dimensional van der Waals Indium Selenide crystals, Sci. Rep., 2016, 6, 1-10.

- 45 I. Ferain, C. A. Colinge and J. P. Colinge, Multigate transistors as the future of classical metal-oxidesemiconductor field-effect transistors, Nature, 2011, 479, 310-316.

- 46 F. L. Yang et al., 5nm-gate nanowire FinFET, Digest of Technical Papers - Symposium on VLSI Technology, pp. 196-197, 2004, DOI: 10.1109/VLSIT.2004.1345476.

- 47 Y. Guo, et al., Sub-5 nm monolayer germanium selenide (GeSe) MOSFETs: towards a high performance and stable device, Nanoscale, 2020, 12, 15443-15452.

- 48 R. Quhe, J. Chen and J. Lu, A sub-10 nm monolayer ReS2 transistor for low-power applications, J. Mater. Chem. C, 2019, 7, 1604-1611.

- 49 H. Li, Q. Wang, F. Liu and J. Lu, Lifting on-state currents for GeS-based tunneling field-effect transistors with electrode optimization, Appl. Surf. Sci., 2022, 602, 154297.

- 50 H. Li, et al., Device performance limit of monolayer SnSe2 MOSFET, Nano Res., 2022, 15, 2522–2530.

- 51 S. U. Din, *et al.*, Indium-doped BiFeO<sub>3</sub> gas sensors for the high-sensitivity and selective SO<sub>2</sub>F<sub>2</sub> detection, *J. Alloys Compd. Communications*, 2024, 3, 100021.

- 52 L. Tao, *et al.*, Silicene field-effect transistors operating at room temperature, *Nat. Nanotechnol.*, 2015, **10**(3), 227–231.

- 53 S. B. Desai, *et al.*, MoS2 transistors with 1-nanometer gate lengths, *Science*, 2016, **354**, 99–102.

- 54 Y. Wang, *et al.*, Many-body Effect, Carrier Mobility, and Device Performance of Hexagonal Arsenene and Antimonene, *Chem. Mater.*, 2017, **29**, 2191–2201.

- 55 J. Zhu, et al., High-Performance Two-Dimensional InSe Field-Effect Transistors with Novel Sandwiched Ohmic Contact for Sub-10 nm Nodes: a Theoretical Study, Nanoscale Res. Lett., 2019, 14, 1–8.

- 56 H. Li, Q. Li and J. Lu, Ohmic-contact Ballistic 2D InSe Transistors: Promising Candidates for More Moore Electronics, vol. 67, 2024.