# Nanoscale Horizons

The home for rapid reports of exceptional significance in nanoscience and nanotechnology

Accepted Manuscript

This article can be cited before page numbers have been issued, to do this please use: T. T. T. Tun, J. Huo and K. Ang, *Nanoscale Horiz.*, 2025, DOI: 10.1039/D5NH00675A.

This is an Accepted Manuscript, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about Accepted Manuscripts in the <u>Information for Authors</u>.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this Accepted Manuscript or any consequences arising from the use of any information it contains.

# **New Concepts**

This work demonstrates finely tunable multilevel conductance states in tin hexathiophosphate ( $SnP_2S_6$  or SPS) memristors, a material where systematic analog switching studies remain limited. By achieving up to 325 stable conductance states, this study highlights the capability of SPS to support high-resolution analog memory and neuromorphic computing. The ability to reliably access a large number of states within a fixed ON/OFF ratio provides additional insight into how conductance modulation can be extended in emerging 2D materials. Alongside conductance tuning, device-level synaptic behaviors such as long-term potentiation and depression were also explored, with their implications assessed through artificial neural network simulations. Together, these results establish SPS as an exploratory platform for investigating multilevel switching in 2D memristors, broadening the range of materials available for in-memory and brain-inspired computing research.

# COMMUNICATION

# High-Density Conductance States and Synaptic Plasticity in SnP<sub>2</sub>S<sub>6</sub> Memristors for Neuromorphic Computing†

Received 00th January 20xx Accepted 00th January 20xx

DOI: 10.1039/x0xx00000x

Published on 22 November 2025. Downloaded on 11/26/2025 6:49:10 AM.

Thaw Tint Te Tun, Jiali Huo and Kah-Wee Ang\*

Memristors with programmable conductance are considered promising for energy-efficient analog memory and neuromorphic computing in edge AI systems. To improve memory density and computational efficiency, achieving multiple stable conductance states within a single device is particularly important. In this work, we demonstrate multilevel conductance tuning in few-layer tin hexathiophosphate (SnP<sub>2</sub>S<sub>6</sub>, SPS) memristors, achieving 325 stable states through a pulse-based programming scheme. By analyzing conductive filament evolution, we devised a voltage-pulse approach that effectively suppresses current noise, thereby maximizing the number of distinguishable states within the device ON/OFF ratio. Furthermore, we experimentally emulated synaptic plasticity behaviors including long-term potentiation and depression, and validated their performance through artificial neural network simulations on digit classification. These results highlight the potential of SPS memristors as high-resolution analog memory and as building blocks for neuromorphic computing, offering a pathway toward compact and efficient architectures for next-generation edge intelligence.

#### Introduction

The growing integration of artificial intelligence (AI) in edge devices has accelerated the development of embedded AI and ambient intelligence (AmI) systems, where real-time, lowpower, and efficient computing is essential. 1 Conventional von Neumann architectures, limited by the separation of memory and processing units, suffer from high latency, energy inefficiency, and restricted throughput, making them less suitable for always-on applications.<sup>2, 3</sup> To address these challenges, non-von Neumann paradigms such as in-memory computing have been proposed. Memristors are promising

Department of Electrical and Computer Engineering, National University of Singapore, 4 Engineering Drive 3, Singapore 117583. E-mail: eleakw@nus.edu.sq supplementary information DOI: 10.1039/x0xx00000x

candidates owing to their simple two-terminal structure, scalability, and low power operation.4-6 Their ability to modulate conductance in response to voltage enables analog memory functions and synaptic plasticity behaviors relevant for neuromorphic computing.<sup>7, 8</sup> Depending on their operating mechanisms, memristive devices can be broadly categorized into electrical, optoelectronic, and ionic types. Electrical memristors, such as those based on filamentary or interfacial resistive switching, have been extensively studied for their scalability and CMOS compatibility.9, 10 Optoelectronic memristors combine optical and electrical stimuli to achieve light-assisted programming and enhanced control over conductance states. 11, 12 Ionic memristors, in which ion migration directly modulates channel conductivity, offer high analog tunability and potential for bioinspired signal processing.13

Among these various device types, memristors with multiple stable conductance states are particularly attractive for neural network applications, especially at the edge, where they allow direct mapping of pretrained weights, reduce retraining overhead, and support adaptive tuning during deployment. Such high-resolution control also promotes consistent synaptic behavior across devices, improving learning accuracy and inference stability. Beyond neuromorphic computing, analog programmability in memristors offers opportunities for broader applications, including scientific and mortal computing. 14, 15 Nonetheless, achieving precise and reliable analog tuning over a wide dynamic range remains a key challenge, particularly in two-dimensional (2D) material-based

2D materials have recently attracted attention for resistive switching (RS) devices due to their atomic thickness, low switching voltages,16,17 reduced device variability,18 and ability to exhibit both threshold and bipolar RS behaviors. 16, 19 Among them, nanoporous metal chalcogenophosphates (MP<sub>2</sub>X<sub>6</sub>; M = Sn, Ge, Pb; X = S, Se, Te) show potential for electronic applications.<sup>20-25</sup> Within this family, tin hexathiophosphate

b a C Au 20 mm f d е 10 10 € 10-10-6 Current 10<sup>4</sup> 10 10 10-Median Line -0--2-0 V 10-8 -1.0 -0.5 0.0 0.5 1.0 1.5 LRS Current HRS Current Voltage (V) Voltage (V) h g € 10-5 Current ( 10-10-8

Fig. 1 (a) Cross-sectional BF-TEM image of the as-fabricated Ti/SnP<sub>2</sub>S<sub>6</sub>/Au memristor. (b) Cross-sectional EDS map highlighting the SnP<sub>2</sub>S<sub>6</sub> layer. (c) Schematic illustration of the memristor device structure. (d) I-V curves of the memristor over 100 switching cycles with an Icc of 1 mA during SET processes. The corresponding distributions of (e) HRS and LRS currents, and (f) V<sub>SET</sub> and V<sub>RESET</sub>. (g) Zoomed-in optical microscopy image of a 6 × 6 CBA of SnP<sub>2</sub>S<sub>6</sub> memristors. The distributions of (h) HRS and LRS currents and (i)  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  for I-V curves measured across 36 devices from the CBA. In both (e) and (h), each box represents the distribution of multiple repeated measurements of LRS and HRS currents. The central line inside each box indicates the median current, while the box edges correspond to the interquartile range (IQR). The dot within each box represents the mean current, and the vertical whiskers extend to values within 1.5×IQR, with any points beyond this range plotted as outliers. In (e), (f), (h), and (i),  $\mu$  denotes the mean,  $\sigma$  denotes the standard deviation, and  $C_v$  denotes the coefficient of variance.

LRS Current

HRS Current

(SnP<sub>2</sub>S<sub>6</sub> or SPS) is particularly notable due to its wide indirect bandgap of 2.2 eV, ambient stability, room-temperature ferroelectricity, and strong light-matter interactions.<sup>26-30</sup> Despite these favorable attributes, systematic demonstrations of finely tunable analog conductance states in SPS memristors remain limited.

Here, we explore the potential of SPS memristors for analog memory and neuromorphic applications by demonstrating multilevel conductance tuning using a high-precision pulse programming (H3P) approach combined with a denoising strategy. The H3P scheme employs conditional logic and

predefined pulse sequences without requiring device-specific calibration, while the denoising process reduces current fluctuations that often limit the resolution of conductance states. This combination enables up to 325 stable states to be accommodated within the available ON/OFF window. While the approach is expected to be broadly useful for filamentary RS systems, its application to SPS represents an early demonstration of high-resolution conductance control in this material. Beyond conductance tuning, we emulate long-term potentiation (LTP) and depression (LTD) through tailored pulse trains and incorporate the measured responses into artificial

-1.0

Voltage (V)

1.5

Journal Name

neural network (ANN) simulations using MLP+NeuroSim V3.0. The simulations indicate that improved linearity in LTP/LTD responses correlates with higher classification accuracy, underscoring the importance of pulse scheme design when linking device behavior to system performance. This work thus provides an exploratory demonstration of finely tunable analog states and neuromorphic functions in SPS memristors.

#### **Results and discussion**

Published on 22 November 2025. Downloaded on 11/26/2025 6:49:10 AM.

#### **Device Structure and the Switching Performance in SPS memristors**

The cross-sectional structure of the fabricated SPS memristor was examined using bright-field transmission electron microscopy (BF-TEM), which confirmed the Ti/Au/SnP<sub>2</sub>S<sub>6</sub>/Ti/Au layer sequence (Fig. 1(a)). Elemental mapping via energydispersive spectroscopy (EDS) further verified the presence of Sn, P, and S in the switching layer and indicated an SPS thickness of approximately 8 nm (Fig. 1(b)). A schematic illustration of the effective device architecture is provided in Fig. 1(c), showing the exfoliated SPS flake sandwiched between the top Ti active electrode and the bottom Au electrode. Spectroscopic characterization was also performed on the exfoliated SPS flakes. The Raman spectrum (Fig. S2(a), ESI†) shows three peaks at ~142, ~169, and ~265 cm-1, consistent with previous reports.<sup>26, 27</sup> The photoluminescence spectrum (Fig. S2(b), ESI†) also matches earlier results, 27, 28 further confirming the material's properties.

Electrical characterization of the SPS memristor demonstrated reproducible bipolar RS behaviour (Fig. 1(d)). During a positive voltage sweep from 0 to 2 V with a compliance current (I<sub>CC</sub>) of 1 mA, the device transitions from a highresistance state (HRS) to a low-resistance state (LRS). Conversely, under a negative voltage sweep from 0 to -2 V, the device resets to the HRS without requiring an Icc. All pristine devices undergo an initial forming process, with a mean forming voltage of ~3 V (Fig. S3, ESI†). To assess temporal variations in switching voltages, the device was subjected to 100 direct current (DC) cycles. The results show a switching memory window exceeding 10<sup>2</sup> (Fig. 1(e)), with minimal variations in SET and RESET voltages (V<sub>SET</sub> and V<sub>RESET</sub>). Statistical analysis (Fig. 1(f)) indicates mean  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  of 1.14 V and -0.94 V, with standard deviations of 0.0758 V and 0.0832 V, respectively. These variations are comparable to those reported for highperformance memristors (Table S1, ESI+). To elucidate the RS mechanism, EDS scans were performed on SPS memristors in both HRS and LRS states. The line scans (Fig. S4, ESI+) reveal a higher Ti concentration in the SPS switching layer in the LRS compared to the HRS, while the Au concentration remains unchanged in both states. This suggests that Ti ions are actively involved in the switching process, classifying the device as an electrochemical metallization (ECM)-type memristor. To further verify this conclusion, an SPS-based memristor with Au electrodes on both sides was fabricated. When subjected to voltage sweeps up to ±6 V, the device did not exhibit any RS behaviour (Fig. S5, ESI+), confirming that Au ions do not contribute to the switching process.

In addition to evaluating temporal or cycle-to-cycle (C2C) variations, spatial or device-to-device (D2D) variations were analysed through electrical measurements on a 6 × 6 CBA of SPS memristors fabricated on a uniformly thick SPS nanosheet (Fig. 1(g) and S6, ESI†). DC sweep cycles were recorded for all 36 devices, each undergoing six switching cycles (Fig. S7, ESI†). Both I-V characteristics and statistical analyses of the HRS and LRS currents confirm consistent switching behaviour, with a switching memory window comparable to that observed in C2C measurements (>102) (Fig. 1(h) and S7, ESI+). Furthermore, across all 36 devices, statistical analysis yields mean  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  of 1.08 V and -0.79 V, with standard deviations of 0.0994 V and 0.0968 V, respectively (Fig. 1(i) and S8, ESI+), indicating minimal D2D variations in switching voltage. Retention measurements on a representative device confirm stable LRS and HRS levels for 10<sup>4</sup> s without degradation (Fig. S9(a), ESI<sup>†</sup>), while endurance tests on the same device show reproducible switching up to 10<sup>4</sup> cycles (Fig. S9(b), ESI<sup>+</sup>), suggesting the potential for stable non-volatile memory operation.

# Multiple Conductance States using a High-Precision Pulse **Programming Scheme with Denoising Process**

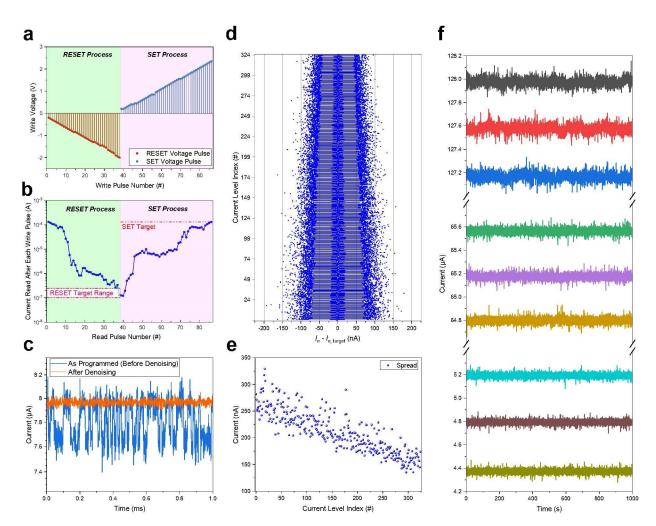

In the context of in-memory computing, the number of distinguishable current levels plays a key role in determining a memristor's information storage capacity. In this study, we employed the H3P scheme to achieve 325 distinct conductance states in SPS memristors, providing a demonstration of multilevel tuning in a 2D material system. Table S1 (ESI+) provides representative reports of multilevel tuning in other 2D memristor systems. Our H3P scheme utilizes ramped stair pulses with positive or negative biases to induce SET or RESET transitions, respectively. For example, when tuning the device conductance from a higher LRS current of 130 µA to a lower LRS current of 72 µA, negatively ramped stair pulses ranging from -0.2 V to -4.5 V are applied. If the conductance falls below the target of 72 µA, positively ramped stair pulses (0.2 V to 4 V) are subsequently applied. This process is iterated until the conductance stabilizes within an acceptable range around the target value (72  $\pm$  0.2  $\mu$ A). An illustration of this process is shown in Fig. 2(a) and 2(b).

However, without an effective denoising strategy, the programmed current levels exhibit noticeable fluctuations (Fig. 2(c)), reducing the minimum distinguishable range between adjacent conductance states. In ECM-based memristors, such as the SPS memristor studied here, such fluctuations can be mitigated by disrupting weak filaments while preserving stronger ones, a process referred to as the denoising mechanism.14 In our scheme, after reaching the target range, we applied a sequence of positive-negative denoising pulse pairs that effectively suppressed current fluctuations within an acceptable precision margin (target current ± 0.15 µA), which was empirically determined as the minimum stable margin during the denoising process. The full details of the H3P scheme and its denoising procedure are shown in Fig. S10 (ESI+). This approach enabled the generation of 325 distinct current levels in SPS memristors (Fig. 2(d)), suggesting their suitability for

COMMUNICATION

Journal Name

Fig. 2 (a) Example of SET and RESET operations using stair pulses with ramped-up voltage amplitudes under the H3P scheme. (b) Corresponding current measured by a 0.2 V/1 µs read pulse following each SET or RESET pulse in (a). (c) As programmed and after denoising currents of the memristor, read using a constant voltage of 0.2 V. (d) Distribution of current deviation ( $I_n - I_{n, \text{target}}$ ) across 325 programmed conductance states achieved in a memristor using the H3P scheme with denoising. Each box represents 1000 data points (10 s retention monitoring per level), with box edges indicating the IQR, whiskers extending to 1.5×IQR, and the central dot marking the mean. (e) Current spread corresponding to the deviations shown in (d). In both (d) and (e), current level index 0 corresponds to the highest current level, while index 324 represents the lowest. (f) Retention measurements of three representative current levels from each of the high, medium, and low conductance ranges after denoising.

multi-bit memory in-memory analog computing applications.

To evaluate the robustness of the multilevel states, we analyzed current fluctuation behavior and inter-level separability across three representative devices. Each of the 325 programmed levels was monitored for 10 s. The analysis of current deviation from the target (Fig. 2(d) and S12, ESI+) reveals noise distributions with minimal state overlap after denoising, a trend consistently observed across all three devices despite minor variations in noise characteristics. Scatter plots of current deviation metrics (Fig. S13, ESI†) further illustrate differences in distribution width and noise behavior between devices. Nonetheless, the minimum inter-level spacing (~400 nA) remains significantly larger than the observed current fluctuations at each level (Fig. 2(e) and S13, ESI+), ensuring clear

separation between adjacent states. The lack of significant overlap confirms the precision and reliability of the multilevel programming scheme. Furthermore, the retention stability of these states was further verified up to 103 s across three conductance ranges (Fig. 2(f)), showing stable state maintenance over time. In terms of energy and time consumption, the H3P scheme with denoising process consumes an average of ~116 nJ and requires ~7 ms to achieve stable conductance state (Fig. S14, ESI†). These measurements were obtained using a passive device controlled by a B1500A semiconductor analyzer, suggesting that further optimization of the programming scheme could improve both energy efficiency and switching speed. In this context, the H3P scheme primarily serves to establish stable and reproducible conductance levels, rather than being a continuously active

COMMUNICATION

Journal Name

Published on 22 November 2025. Downloaded on 11/26/2025 6:49:10 AM.

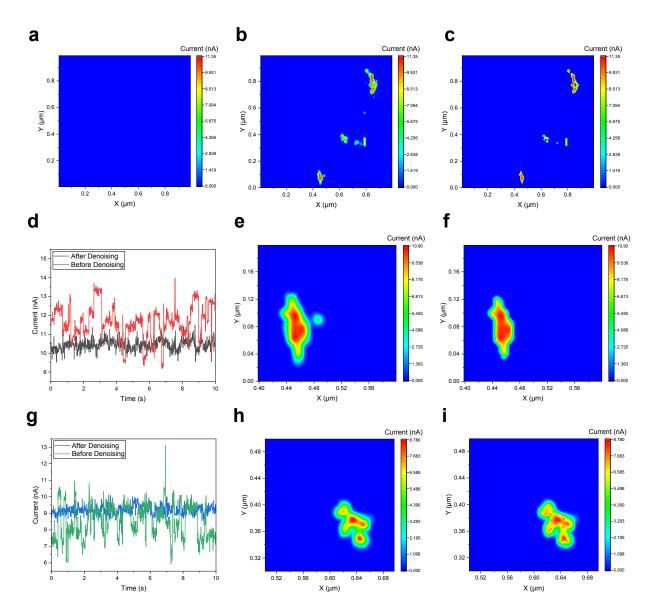

Fig. 3 (a) Current map obtained from C-AFM scanning on the pristine area of the SnP<sub>2</sub>S<sub>6</sub> surface. (b) Current map obtained from the same area after applying electrical stress of 3 V. (c) Current map obtained from the same area after the application of sub-threshold positive and negative voltages, following the 3 V stress in (b). (d) Currents measured before and after denoising using a sub-threshold negative voltage, read at a constant voltage of 0.1 V during C-AFM measurements. (e) Current map obtained from C-AFM scanning, corresponding to the before denoising state in (d). (f) Current map corresponding to the after denoising state in (d). (g) Currents measured before and after denoising using a sub-threshold positive voltage, read at a constant voltage of 0.1 V during C-AFM measurements. (h) Current map obtained from C-AFM scanning, corresponding to the before denoising state in (g). (i) Current map corresponding to the after denoising state in (g). All C-AFM scans were acquired using a read voltage of 0.1 V.

operation. For applications such as edge inference, where trained neural networks are downloaded from cloud servers to local devices for real-time recognition or decision-making and only infrequently updated, the additional energy involved in this scheme is expected to remain moderate.14

To explore the applicability of the proposed H3P scheme in memristors for edge-inference computing, implemented a proof-of-concept temporal convolutional network (TCN) classifier using a 6 × 6 SPS memristor CBA, where multiply-and-accumulate (MAC) operations were executed

based on conductance states programmed via H3P (Fig. S15, ESI†). This demonstration illustrates how high-resolution conductance tuning can be applied to a representative edgeinference task. Using accelerometer features from the HAR70+ dataset,31 the TCN model was trained in software and the six 3 × 3 convolutional kernels were quantized to 8-bit precision. These values were then programmed into the memristor array using the H3P and denoising process. A pre-characterized MAC dataset was generated by measuring column-wise current outputs for all input voltage combinations, which were

COMMUNICATION Journal Name

subsequently retrieved during inference to execute convolution steps, with remaining layers processed in software. The hardware-assisted TCN achieved a classification accuracy of 82.81%, which, although lower than the 90.96% obtained from the fully software implementation (Fig. S25, ESI†), indicates that SPS-based hardware can reproduce inference results with reasonable accuracy relative to software baselines. This hardware-assisted inference provides an exploratory validation that H3P-tuned multilevel states in SPS memristors can support convolution operations, while highlighting opportunities for further optimization toward closing the performance gap.

# Investigation of Conductive Filament Evolution in Denoising **Process**

To investigate the mechanism underlying the improved fluctuation reduction in current levels of SPS memristors, we examined the evolution of conductive filaments (CFs) during the denoising process. As SPS memristors operate via an ECM mechanism, CFs play a key role in resistive switching. Analysing their evolution under different voltage stimuli provides insights into how denoising influences switching stability. 14, 32-34 Conductive Atomic Force Microscopy (C-AFM) was employed for this analysis. To facilitate C-AFM measurements, a customized structure was fabricated to replicate the electrical behaviour of the memristor while ensuring optimal imaging conditions (Fig. S27(a), ESI+). This structure consists of an Aucoated C-AFM probe tip as the top electrode, an SPS nanosheet as the RS medium, and a Ti layer deposited on a silicon substrate as the bottom electrode. While this configuration is a reversed version of the original device, it maintains identical electrical functionality when the probe tip is grounded, and voltage is applied via the Ti bottom layer.

Initially, the selected area of the pristine SPS nanosheet sample was scanned using the read voltage of 0.1 V to check any existing conductive pathways. As shown in Fig. 3(a), the pristine SPS sample area shows no CF, and it serves as the reference to compare after CF formation. The sample area was then scanned with a higher voltage of 3 V to induce CF formation. The subsequent read scan (Fig. 3(b)) reveals the emergence of several small high-current regions, indicating CF formation. After this, a denoising process was mimicked by scanning the same area with sub-threshold positive and negative voltages, replicating the denoising pulses used in the H3P scheme. A follow-up read scan (Fig. 3(c)) showed notable morphological changes: some smaller current regions disappeared while a few more prominent regions became more conductive. These observations suggest that sub-threshold denoising voltages selectively modulate CF morphology, weakening or disrupting unstable filaments.

To further investigate this effect, a more localized analysis was conducted on individual CFs. After forming, the current of a selected CF was monitored for 10 s prior to applying denoising pulses (Fig. 3(d), red line), during which significant current fluctuations were observed. A corresponding C-AFM scan captured the filament structure in this state (Fig. 3(e)). Subsequent application of sub-threshold negative voltage scans

led to a gradual stabilization of the current within an acceptable fluctuation range (Fig. 3(d), black line). The corresponding C-AFM image (Fig. 3(f)) revealed a modified filament structure, showing diminished peripheral branches while the core remained intact. These results suggest that weaker or incomplete filaments are preferentially suppressed, thereby reducing noise sources. A similar trend was observed when subthreshold positive voltage biases were applied to another selected CF. Please note that the selected CF was re-formed to isolate the effect of positive biases. A clear improvement in current stability was observed (Fig. 3(g)), and the corresponding before-and-after C-AFM images (Fig. 3(h) and 3(i)) shows that a few more prominent regions became more conductive. This again confirmed the selective modulation of unstable CF branches. Together, these results support the hypothesis that paired positive-negative denoising pulses reinforce stable filaments while selectively eliminating transient, noise-prone conductive paths. This selective refinement of the conductive network facilitates more precise conductance tuning and effectively expands the number of distinguishable conductance states within a fixed ON/OFF ratio. The observed behaviour is consistent with previous studies on denoising in ECM-based memristors using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> systems.<sup>14</sup>

DOI: 10.1039/D5NH00675A

# **Artificial Synaptic Plasticity and Image Recognition Simulation using** a Synaptic Plasticity based Artificial Neural Network

In addition to their capability to achieve multiple conductance states, SPS memristors can function as electronic synapses, mimicking key properties of biological synapses, which serve as the fundamental units of brain-inspired computing. Structurally, an SPS memristor closely resembles a biological synapse, where the two electrodes act as the pre- and postsynapses, while the SPS switching layer facilitates Ti ion migration, forming CFs analogous to synaptic connections (Fig. 4(a)). For neuromorphic computing applications, long-term potentiation (LTP) and long-term depression (LTD) are essential synaptic functions required for ANNs.35, 36 These properties were demonstrated in SPS memristors, where positive voltage pulses induced LTP by increasing post-synaptic currents, while negative pulses induced LTD, reducing the current (Fig. 4(b)). Additionally, the dependence of excitatory post-synaptic current (EPSC) on pulse amplitude was observed, with larger positive voltage amplitudes resulting in greater EPSC responses, demonstrating synaptic amplitude-dependent plasticity (SADP) (Fig. 4(c)). Similarly, inhibitory post-synaptic currents (IPSC) were induced by applying negative pulses of varying amplitudes, where higher-amplitude negative pulses resulted in a lower final post-synaptic current, starting from a nearly identical initial state (Fig. 4(d) and 4(e)).

Furthermore, the SPS memristors exhibited "learningforgetting-relearning" behaviour, a characteristic of biological synapses. When voltage pulses of alternating polarity were applied, the post-synaptic current initially increased due to positive pulses and subsequently decreased with negative pulses. However, the current did not return to its original state, indicating memory retention effects. With repeated learningCurrent 30 20

10

Published on 22 November 2025. Downloaded on 11/26/2025 6:49:10 AM.

b C a Pulse width/period: 50 µs/500 µs Pulse width/period: 50 μs/500 μs Read at 0.2 V Read at 0.2 V 100 100 (FA) 80 60 Au Bottom 0.9 Biological Synapse Pulse Amplitude (V) d e Pulse width: 50 µs V<sub>LTP</sub>: 0.8 V 90 LTD Pulse period: 500 µs → LTD 120 Read at 0.2 V 100 100 60 80 80 60 V<sub>LTD</sub>: -0.9 V Pulse width: 50 µs 40 Pulse period: 500 Read at 0.2 V 20 20 20 Pulse width/period: 50 µs/500 µs -1.15 V 100 200 -1.10 -1.05 -1.00 -0.95 -0.90 200 400 600 800 Pulse Number (#) Pulse Amplitude (V) Pulse Number (#) h g 80 - Pulse width/period: 50 μs/500 μs Pulse width/period: 50 µs/500 µs 80 LTP LTD ication Accuracy (%) 60 V<sub>LTD</sub>: -1.0 V ₹ 50

Fig. 4 (a) Schematic illustration of the structural similarity between a biological synapse and a Ti/SnP₂S<sub>6</sub>/Au memristor. (b) Tunable LTP and LTD processes by applying pulses with different amplitudes. (c) EPSC of the synaptic memristor, with current values extracted from (b) after 100 positive pulses for each amplitude. (d) Tunable LTD process by applying negative pulses with different amplitudes, while the positive pulse amplitude is fixed at 1.1 V. (e) IPSC of the synaptic memristor, with current values extracted from (d) after 100 negative pulses for each amplitude. (f) Repeated LTP-LTD characteristics, with potentiation and depression pulse amplitudes fixed at 0.8 V and -0.9 V, respectively, resembling learning-forgetting-relearning behaviour. (g) Ten-cycle LTP-LTD characteristics under identical pulses, with potentiation and depression pulse amplitudes fixed at 0.8 V and -1 V, respectively. (h) Ten-cycle LTP-LTD characteristics under non-identical pulses. In both (g) and (h), each box represents the distribution of 10 repeated current measurements acquired at each pulse number. The box edges indicate the IQR, and the whiskers extend to values within 1.5×IQR. The dot inside each box denotes the mean current, and the black solid line connects these mean values across pulses.  $\alpha_0$  and  $\alpha_d$  represent the linearity of potentiation and depression, respectively. For all measurements, the pulse width and period were fixed at 50 µs and 500 µs, respectively. (i) Pattern classification accuracy for online learning simulated using MLP+NeuroSim V3.0, based on experimental LTP and LTD characteristics under two distinct pulse schemes: nonidentical and identical.

100

forgetting-relearning cycles, the post-synaptic progressively increased, resembling biological memory reinforcement (Fig. 4(f)). By adjusting voltage pulse amplitudes, it was also possible to simulate synaptic and neural dynamics relevant to brain-inspired computing. Distinct LTP and LTD responses were observed under both identical and nonidentical pulse amplitude schemes. To assess the C2C variability of the memristor, each scheme was tested over 10 repeated cycles, showing consistent performance with minimal variation

100

Pulse Number (#)

150

(Fig. 4(g) and 4(h)). To evaluate the linearity of LTP and LTD events, we normalized the measured conductance values using:

30

$G-G_{min}$  (1)

where  $G_{\text{max}}$  and  $G_{\text{min}}$  represent the maximum and minimum conductance values, respectively. The linearity of potentiation  $(\alpha_p)$  and depression  $(\alpha_d)$  was then analysed using the following

equation

$$G = \begin{cases} G(G_{LRS}^{\alpha} - G_{HRS}^{\alpha}) \times w + G_{HRS}^{\alpha})^{\frac{1}{\alpha}} & \text{if } \alpha \neq 0 \\ G_{HRS} \times (G_{HRS}^{G_{LRS}})^{W} & \text{if } \alpha = 0 \end{cases}$$

(2)

Online Learning using

Online Learning using

Identical Pulse Scheme

Epoch (#)

DOI: 10.1039/D5NH00675A

COMMUNICATION Journal Name

The results showed that the non-identical pulse scheme exhibited the best linearity, with  $\alpha_p = 1.32$  and  $\alpha_d = 0.91$ . Ideally, a perfectly linear response corresponds to  $\alpha = 1$ . These findings suggest that conductance modulation via non-identical pulse schemes enhances synaptic behaviour. In addition, D2D variability was also assessed by repeating the same process on two other devices randomly selected from the SPS CBA. The results (Fig. S31 and S32, ESI†) show low variation in weight update and similar linearity responses of the devices for the two respective schemes.

To further evaluate the synaptic properties of SPS memristors, we simulated a fully connected perceptron neural network using MLP+NeuroSim V3.0.38,39 The measured LTP and LTD values from both identical and non-identical pulse schemes, including the respective C2C, D2D, and conductance range variations, were incorporated into the simulation to compare their effects on classification accuracy. It is important to note that the  $\alpha_{\rm p}$  and  $\alpha_{\rm d}$  values calculated served as relative evaluation indices for evaluating non-linearity and were not directly implemented in NeuroSim. The simulated neural network comprised 20 × 20 input neurons, 100 hidden neurons, and 10 output neurons, designed for classifying the 10-digit classes of the Modified National Institute of Standards and Technology (MNIST) dataset. The network was trained over 24 epochs, and the resulting classification accuracy was recorded. The results (Fig. 4(i)) indicate that the neural network trained with the non-identical pulse scheme achieved higher accuracy of ~85%, likely due to good linearity in conductance modulation. In contrast, the identical-pulse scheme exhibited faster accuracy improvement during the initial epochs, which can be attributed to its larger effective weight-update step arising from steeper conductance-pulse characteristics. However, this aggressive early learning led to less stable convergence and a lower final accuracy, consistent with an effect widely observed in neural network optimizations, where an excessively large learning rate may accelerate early learning but impede convergence to the optimal solution.<sup>40</sup> While this is the most likely explanation, other factors such as stochastic weight initialization and device-level variation may also play a role. Taken together, these findings highlight the potential of SPS memristors for brain-inspired computing applications, demonstrating effective conductance modulation through pulse parameter tuning.

Building on these promising results, future work may explore integrating SPS memristors into larger CBAs for advanced in-memory computing. As array size increases, factors such as device variability, IR drop, and cross-talk can introduce computational inaccuracies. At Cross-talk, arising from parasitic currents, capacitive coupling, or voltage sharing, can lead to read/write disturbances, signal attenuation, or erroneous current summation during MAC operations, particularly when many low-resistance cells exist in parallel paths. At These effects become increasingly significant with higher array density. Addressing these challenges will require wafer-scale SPS growth to minimize variation, along with access mechanisms to suppress sneak currents and ensure cell isolation. Strategies include one-transistor-one-resistor (1T1R)

architectures, one-selector-one-resistor (1S1R) configurations, and self-rectifying memristor arrays. 10, 44-46 Since SPS devices exhibit abrupt SET transitions and rely on external compliance, selector-free integration is not feasible. While 1T1R or 1S1R integration may be promising, realizing such architectures with SPS memristors will require co-design and fabrication of dedicated access elements, which lie beyond the present scope. Future efforts should explore these directions to unlock full-array integration and broaden the applicability of SPS memristors in neuromorphic and analog computing systems.

#### **Conclusions**

In conclusion, SPS memristors demonstrated repeatable bipolar RS behavior with minimal spatial and temporal variations in switching voltages. Through the H3P scheme combined with a denoising process, up to 325 stable conductance states were reliably achieved. C-AFM investigations revealed that carefully designed denoising pulses effectively minimize incomplete filament formation and suppress current fluctuations, thereby enhancing the stability of the conductance states. Beyond their potential for multi-bit memory storage, SPS memristors also demonstrated the ability to emulate synaptic plasticity behaviors, supporting their applicability in brain-inspired computing. Collectively, these findings highlight the potential of SPS memristors to serve as a high-resolution platform for analog memory and neuromorphic computing, with promising relevance for edge-inference applications.

# **Experimental**

#### **Device Fabrication**

Two-terminal crossbar memristor devices were fabricated on a silicon/silicon dioxide (Si/SiO<sub>2</sub>) substrate. The bottom electrode, consisting of a 5 nm Ti adhesion layer and a 20 nm Au layer, was deposited onto the  $\text{Si/SiO}_2$  substrate via e-beam evaporation. A mechanically exfoliated SPS nanosheet was then transferred onto the bottom electrode. The fabrication was completed by depositing a 30 nm Ti layer and a 20 nm protective Au layer as the top electrode. The top and bottom electrodes were patterned using electron beam lithography (EBL, JBX-6300FS) with poly (methyl methacrylate) (PMMA) as the photoresist and isopropyl alcohol/methyl isobutyl ketone (IPA/MIBK, 1:3) as the developer.

#### **Device Measurement**

All electrical characterizations, including DC measurements and pulse-based measurements, were conducted using a Keysight B1500A semiconductor analyser. During electrical testing, the Ti top electrode was biased, while the Au bottom electrode was grounded. All measurements were performed under ambient conditions at room temperature.

#### **Material Characterization**

The Raman and PL spectra of exfoliated SPS nanosheets were acquired using a Renishaw Raman microscope, equipped with a

9.

11.

Journal Name

532 nm excitation laser and a 50x objective lens, under ambient conditions. The laser power was limited using a 5% filter. The Si peak at 520 cm<sup>-1</sup> was used as a reference for calibration. Crosssectional TEM and EDS were performed using a Talos F200X TEM. Thin lamellae for TEM characterization were prepared using a focused ion beam (FIB, FEI Helios NanoLab). C-AFM scans were conducted using a Park NX20 atomic force microscope.

#### Statistical Analysis

In Fig. 1(e) and 1(f), the sample size is 100 data points. In Fig. 1(h) and 1(i), the sample size is 216 data points, from six cycles across 36 devices. For each current level in Fig. 2(f), the sample size of the current deviation distribution is 1001 data points. The overall mean and standard deviation of the current deviation are -0.02 nA and 33.58 nA, respectively. For Fig. 4(g) and 4(h), statistical analyses are provided in Tables S2 and S3 (ESI+).

#### **Simulations**

Published on 22 November 2025. Downloaded on 11/26/2025 6:49:10 AM.

Details of the simulated TCN are shown in Fig. S15 (ESI+), and the NeuroSim setup parameters are summarized in Table S4 (ESI+).

# **Author contributions**

T. T. T. and J. H. designed the experiments. T. T. T. T. performed the experiments, conducted the device measurement, and wrote the original manuscript. K.-W. A. revised the manuscript and supervised the work. All authors commented the manuscript.

#### Conflicts of interest

There are no conflicts to declare.

#### Data availability

The data supporting this article have been included as part of the Supplementary Information.

#### **Acknowledgements**

This work is supported by the National Research Foundation, Prime Minister's Office, Singapore, under its Competitive Research Program (NRF-CRP24-2020-0002).

#### References

- A. Haque, A. Milstein and L. Fei-Fei, Nature, 2020, 585,

- 2. S. Choi, J. Yang and G. Wang, Adv. Mater., 2020, 32, e2004659.

- 3. K. Sun, J. Chen and X. Yan, Adv. Funct. Mater., 2020, 31.

- D. B. Strukov, G. S. Snider, D. R. Stewart and R. S. 4. Williams, Nature, 2008, 453, 80-83.

- M. Lanza, F. Hui, C. Wen and A. C. Ferrari, Adv. Mater., 2023, 35, e2205402.

- T.-C. Chang, K.-C. Chang, T.-M. Tsai, T.-J. Chu and S. M. Sze, Mater. Today, 2016, 19, 254-264.

- B. Chen, H. Yang, B. Song, D. Meng, X. Yan, Y. Li, Y. Wang, P. Hu, T.-H. Ou, M. Barnell, Q. Wu, H. Wang and W. Wu, Sci. Robot., 2020, 5, eabb6938.

- S. Li, M.-E. Pam, Y. Li, L. Chen, Y.-C. Chien, X. Fong, D. Chi and K.-W. Ang, Adv. Mater., 2022, 34, 2103376.

- S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder and W. Lu, Nano Lett., 2010, 10, 1297-1301.

- K. Zhu, S. Pazos, F. Aguirre, Y. Shen, Y. Yuan, W. Zheng, O. Alharbi, M. A. Villena, B. Fang, X. Li, A. Milozzi, M. Farronato, M. Muñoz-Rojo, T. Wang, R. Li, H. Fariborzi, J. B. Roldan, G. Benstetter, X. Zhang, H. N. Alshareef, T. Grasser, H. Wu, D. Ielmini and M. Lanza, Nature, 2023, **618**. 57-62.

- L. Hu, J. Yang, J. Wang, P. Cheng, L. O. Chua and F. Zhuge, Adv. Funct. Mater., 2021, 31, 2005582.

- 12. J. Yang, L. Hu, L. Shen, J. Wang, P. Cheng, H. Lu, F. Zhuge and Z. Ye, Fundamental Research, 2024, 4, 158-166.

- 13. G. Xu, M. Zhang, T. Mei, W. Liu, L. Wang and K. Xiao, ACS Nano, 2024, 18, 19423-19442.

- 14. M. Rao, H. Tang, J. Wu, W. Song, M. Zhang, W. Yin, Y. Zhuo, F. Kiani, B. Chen, X. Jiang, H. Liu, H. Y. Chen, R. Midya, F. Ye, H. Jiang, Z. Wang, M. Wu, M. Hu, H. Wang, Q. Xia, N. Ge, J. Li and J. J. Yang, *Nature*, 2023, **615**, 823-829.

- 15. W. Song, M. Rao, Y. Li, C. Li, Y. Zhuo, F. Cai, M. Wu, W. Yin, Z. Li, Q. Wei, S. Lee, H. Zhu, L. Gong, M. Barnell, Q. Wu, P. A. Beerel, M. S.-W. Chen, N. Ge, M. Hu, Q. Xia and J. J. Yang, Science, 2024, 383, 903-910.

- X. Feng, Y. Li, L. Wang, S. Chen, Z. G. Yu, W. C. Tan, N. 16. Macadam, G. Hu, L. Huang, L. Chen, X. Gong, D. Chi, T. Hasan, A. V. Y. Thean, Y. W. Zhang and K. W. Ang, Adv. Electron. Mater., 2019, 5.

- 17. A. A. Bessonov, M. N. Kirikova, D. I. Petukhov, M. Allen, T. Ryhanen and M. J. Bailey, Nat. Mater., 2015, 14, 199-204. 18. S. Chen, M. R. Mahmoodi, Y. Shi, C. Mahata, B. Yuan, X. Liang, C. Wen, F. Hui, D. Akinwande, D. B. Strukov and M. Lanza, Nat. Electron., 2020, 3, 638-645.

- 19. Y. Shi, X. Liang, B. Yuan, V. Chen, H. Li, F. Hui, Z. Yu, F. Yuan, E. Pop, H. S. P. Wong and M. Lanza, Nat. Electron., 2018. 1. 458-465.

- 20. M. Lin, P. Liu, M. Wu, Y. Cheng, H. Liu, K. Cho, W.-H. Wang and F. Lu, Appl. Surf. Sci., 2019, 493, 1334-1339.

- V. Haborets, K. Glukhov, J. Banys and Y. Vysochanskii, 21. Integr. Ferroelectr., 2021, 220, 90-99.

- 22. C.-Y. Zhu, Z. Zhang, J.-K. Qin, Z. Wang, C. Wang, P. Miao, Y. Liu, P.-Y. Huang, Y. Zhang, K. Xu, L. Zhen, Y. Chai and C.-Y. Xu, Nat. Commun., 2023, 14, 2521.

- 23. V. K. Sangwan, D. G. Chica, T.-C. Chu, M. Cheng, M. A. Quintero, S. Hao, C. E. Mead, H. Choi, R. Zu, J. Sheoran, J. He, Y. Liu, E. Qian, C. C. Laing, M.-A. Kang, V. Gopalan, C. Wolverton, V. P. Dravid, L. J. Lauhon, M. C. Hersam and M. G. Kanatzidis, Sci. Adv., 2024, 10, eado8272.

- 24. Y. Jing, Z. Zhou, J. Zhang, C. Huang, Y. Li and F. Wang, Phys. Chem. Chem. Phys., 2019, 21, 21064-21069.

- 25. C. Zhu, W. He, Z.-R. Huang, B. Zhu, L.-Q. Yue, P.-Y. Huang, D. Li, J. Wang, L. Zhen, J.-K. Qin and C.-Y. Xu, ACS Nano, 2025, **19**, 2362-2370.

DOI: 10.1039/D5NH00675A COMMUNICATION Journal Name

- 26. Y. Zhang, F. Wang, X. Feng, Z. Sun, J. Su, M. Zhao, S. Wang, X. Hu and T. Zhai, Nano Res., 2021, 15, 2391-2398.

- 27. Y. Zhang, F. Wang, X. Feng, Z. Zhang, K. Liu, F. Xia, W. Liang, X. Hu, Y. Ma, H. Li, G. Xing and T. Zhai, Adv. Funct. Mater., 2022, 32.

- 28 C. He, J. Zhang, L. Gong and P. Yu, Front. Phys., 2024, 19.

- 29. S. Wang, J. Song, L. Zong, J. Yang, B. Li, F. Teng, P. Hu, H. Fan and X. Zhao, J. Mater. Chem. C, 2023, 11, 16941-

- 30. J. Hu, A. Zheng, E. Pan, J. Chen, R. Bian, J. Li, Q. Liu, G. Cao, P. Meng, X. Jian, A. Molnar, Y. Vysochanskii and F. Liu, J. Mater. Chem. C, 2022, 10, 13753-13761.

- 31. A. Ustad, A. Logacjov, S. Ø. Trollebø, P. Thingstad, B. Vereijken, K. Bach and N. S. Maroni, Sensors, 2023, 23, 2368.

- 32. U. Celano, L. Goux, A. Belmonte, K. Opsomer, A. Franquet, A. Schulze, C. Detavernier, O. Richard, H. Bender, M. Jurczak and W. Vandervorst, Nano Lett., 2014, 14, 2401-

- 33. F. Hui and M. Lanza, Nat. Electron., 2019, 2, 221-229.

- 34. Y. Yang, X. Zhang, L. Qin, Q. Zeng, X. Qiu and R. Huang, Nat. Commun., 2017, 8, 15173.

- 35. Z. Weng, H. Zheng, W. Lei, H. Jiang, K.-W. Ang and Z. Zhao, Adv. Funct. Mater., 2024, 34, 2305386.

- 36. Z. Weng, H. Zheng, L. Li, W. Lei, H. Jiang, K.-W. Ang and Z. Zhao, Small, 2024, 20, 2304518.

- 37. S. Kim, H. Ji, K. Park, H. So, H. Kim, S. Kim and W. Y. Choi, ACS Nano, 2024, 18, 25128-25143.

- 38. P. Y. Chen, X. Peng and S. Yu, 2017.

- 39. Y. Luo, X. Peng and S. Yu, presented in part at the Proceedings of the International Conference on Neuromorphic Systems, Knoxville, TN, USA, 2019.

- 40. I. Goodfellow, Y. Bengio and A. Courville, Deep Learning, MIT Press, 2016.

- 41. M. Hu, C. E. Graves, C. Li, Y. Li, N. Ge, E. Montgomery, N. Davila, H. Jiang, R. S. Williams, J. J. Yang, Q. Xia and J. P. Strachan, Adv. Mater., 2018, 30.

- E. Linn, R. Rosezin, C. Kügeler and R. Waser, Nat. Mater., 42. 2010. 9. 403-406.

- 43. C. Li, D. Belkin, Y. Li, P. Yan, M. Hu, N. Ge, H. Jiang, E. Montgomery, P. Lin, Z. Wang, W. Song, J. P. Strachan, M. Barnell, Q. Wu, R. S. Williams, J. J. Yang and Q. Xia, Nat. Commun., 2018, 9, 2385.

- 44. S. Jain, S. Li, H. Zheng, L. Li, X. Fong and K.-W. Ang, Nat. Commun., 2025, 16, 2719.

- K. Jeon, J. Kim, J. J. Ryu, S.-J. Yoo, C. Song, M. K. Yang, D. S. 45. Jeong and G. H. Kim, Nat. Commun., 2021, 12, 2968.

- 46. K. Jeon, J. J. Ryu, S. Im, H. K. Seo, T. Eom, H. Ju, M. K. Yang, D. S. Jeong and G. H. Kim, Nat. Commun., 2024, 15, 129.

The data supporting this article have been included as part of the Supplementary Information.