# Nanoscale Advances

**PAPER**

View Article Online

View Journal | View Issue

Cite this: Nanoscale Adv., 2025, 7,

Received 13th January 2025 Accepted 7th April 2025

DOI: 10.1039/d5na00045a

rsc.li/nanoscale-advances

# An area and power efficient ternary serial adder using phase composite ZnO stack channel FETs†

Kiyung Kim, <sup>©</sup> <sup>a</sup> Sunmean Kim, <sup>b</sup> So-Young Kim, <sup>a</sup> Yongsu Lee, <sup>©</sup> <sup>a</sup> Hae-Won Lee, <sup>a</sup> Seokhyeong Kang<sup>a</sup> and Byoung Hun Lee <sup>©</sup> \*

Multi-valued logic is the subject of ongoing investigation owing to its potential to reduce the complexity of logic circuits and interconnect lengths, thereby reducing system power consumption. In this work, ternary stack channel field-effect transistors (SCFETs) are used as unit devices to realize multi-valued logic. The thickness of each ZnO layer in the SCFET is modulated to obtain the device parameters to control the intermediate-state range and saturation current. Using the experimental results, ternary circuits are modeled and simulated to demonstrate that the unique characteristics of SCFETs can be utilized in designing a ternary full adder. The designed ternary full adder requires only 12 devices (approximately 29% of the binary full adder device count). The ternary serial adder has a competitive power-delay product value of approximately 7 fJ at  $V_{\rm DD}=1$  V and an effective oxide thickness of 1 nm. These results indicate that SCFET-based ternary circuits are a promising alternative for extremely low-power applications.

#### Introduction

In recent years, the physical scaling limits of complementary metal-oxide-semiconductor (CMOS) technology have become evident, and numerous workarounds, such as using backside power distribution networks and monolithic and heterogeneous three-dimensional (3D) integration, are being actively pursued. In addition, more disruptive technologies, such as quantum computing, analog computing, and multi-valued logic (MVL), are receiving increasing attention. Recent studies on MVL technology primarily aim to realize lower power consumption at the system level by reducing the circuit complexity and interconnect length. 3.4

However, replacing an entire binary logic system with an MVL system remains challenging. The most considerable obstacle is the absence of logic design fundamentals, such as Boolean logic. Notably, several device studies feature ternary inverters as an application, despite the lack of comprehensive design methodologies for more high-level logic circuits, such as NMIN, NMAX, and ADDER. Although some proposals incorporate advanced ternary architectures, they employ the conventional binary device model, which tends to increase the complexity of circuit design. This approach is contrary to the underlying motivation of MVL technology. Therefore, a suitable

circuit design method and proper unit MVL devices are essential for the practical realization of ternary systems. Moreover, the unit MVL device should be compatible with the CMOS integration process and can be fabricated using low-thermal-budget integration processes, considering the potential cointegration with CMOS devices or monolithic 3D integration in the back-end-of-line structure.

Thus far, numerous devices have been proposed for MVL applications,<sup>5,6</sup> including various heterojunction devices exhibiting negative differential transconductance (NDT),<sup>7-12</sup> quantum dot gate field-effect transistors (FETs),<sup>13-15</sup> carbon nanotube FETs (CNTFETs),<sup>16-20</sup> graphene barristors<sup>21</sup> and ternary CMOSs.<sup>22-24</sup> Unfortunately, in most cases, the reported device development has not progressed beyond the demonstration of a ternary inverter or cannot fulfill the requirements for process feasibility and scalability.

Recently, Lee *et al.*<sup>25</sup> proposed a ternary stack channel FET (SCFET), which contains two stacked nanosheet channels, for ternary logic applications. The stepwise ternary current-voltage (I–V) characteristics of the SCFET were optimized by saturating the conduction current of the first channel using a novel zero-differential transconductance (ZDT) mechanism. ZDT is a new conduction mechanism discovered in ZnO channels comprising phase composite structures, which have crystalline and amorphous structures mixed in a specific manner to yield a unique band structure, limiting the total number of carriers in the conduction band by mobility-edge quantization.<sup>25</sup> In this structure, the level and range of the intermediate-state current (I<sub>1</sub>) can be modulated by adjusting the thickness of each channel.<sup>26</sup> Following the demonstration of the n-type SCFET, a p-type SCFET was demonstrated by Lee *et al.*

<sup>&</sup>lt;sup>a</sup>Department of Electrical Engineering, Pohang University of Science and Technology, Cheongam-ro 77, Nam-gu, Pohang, Gyeongbuk, 37673, Republic of Korea. E-mailbhlee1@postech.ac.kr

<sup>&</sup>lt;sup>b</sup>School of Electronic and Electrical Engineering, Kyungpook National University, Daegu, 41556, Republic of Korea

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: https://doi.org/10.1039/d5na00045a

in 2023,27 enabling the development of a complementary ternary circuit.

Among various ternary circuit proposals, the ternary full adder (TFA) design using CNTFETs proposed by Moaiyeri et al.28 is simple and intuitive. In their design, a standard ternary inverter (STI) requires six CNTFETs. A critical limitation of this proposal is that CNTs with eight different diameters are required to implement the TFA, which makes the design infeasible. We found that the SCFET has a strong architectural synergy with Moaiyeri's TFA design because each STI can be realized with only two SCFETs, and the unique versatility of  $I_1$ modulation can be used to implement the three types of STIs more practically.

In this work, we studied the impacts of physical parameters of SCFETs having ZnO/Al-2,3-dimercapto-1-propanol (Al-DMP)/ ZnO stack channels. Experimental data were systematically analyzed and reflected in the SPICE model for the SCFET. Using the newly developed device model, a ternary serial adder (TSA) was designed to minimize the power-delay product (PDP). A TSA using SCFETs was designed with a low device count of 33 and PDP of 7.15 fJ. The PDP value was one-third that of the design using the CNTFETs, confirming that SCFET-based ternary circuit technology has the potential to be a technical choice for extremely low-power applications.

#### Experimental section

#### **Fabrication process of ZnO SCFETs**

A lift-off photoresist for the buried gate was patterned using iline photolithography. A 70 nm oxide trench was formed on a 300 nm-thick SiO<sub>2</sub> substrate using inductively coupled plasma reactive ion etching (ICP-RIE) with Ar (30 sccm) and CF<sub>4</sub> (30 secm) plasma. The working pressure was 10 mTorr, and the process time was 110 s. The trench was filled with a 10 nm-thick Ti adhesion layer and a 60 nm-thick Al layer using electronbeam (E-beam) evaporation. Upon using the photoresist strip in the lift-off process, the buried gate was polished to remove the rabbit ear defects at the edge of the metal pattern. The Al<sub>2</sub>O<sub>3</sub> gate dielectric layer was deposited via thermal ALD with a trimethyl-aluminum (TMA) precursor at 200 °C. For the uniform deposition of the channel material, the Al<sub>2</sub>O<sub>3</sub> surface was changed from hydrophobic to hydrophilic using a UV-ozone generator. The first ZnO layer was deposited using a novel high-pressure (1.1-1.3 Torr) and long-dosing time (20 s) ALD process. The Al-DMP/Al<sub>2</sub>O<sub>3</sub> SL and second ZnO layer were sequentially deposited using the same ALD process. Diethyl zinc (DEZ) and H<sub>2</sub>O sources were used for ZnO. TMA and 2,3dimercapto-1-propanol (DMP) were used for Al-DMP. TMA and H<sub>2</sub>O were used for Al<sub>2</sub>O<sub>3</sub>. A 70 nm Al layer patterned by the Ebeam evaporation and lift-off process was employed for the source and drain electrodes. Finally, the channel area was defined using the ICP-RIE process.

#### Results & discussion

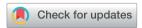

A three-dimensional (3D) schematic of an SCFET is shown in Fig. 1a. In the fabrication process, the lift-off patterns for the

Fig. 1 (a) Schematic structure of the ZnO/AlDMP/ZnO SCFET. (b) Fabrication process flow. (c) Top-down optical photograph of the fabricated device. (d) TEM photograph of the stacked channel structure.

buried gate were formed using photolithography on a 300 nmthick SiO<sub>2</sub> substrate. Subsequently, the 70 nm oxide trench was etched using inductively coupled plasma reactive ion etching (ICP-RIE). The oxide trench was filled with a 10 nmthick Ti adhesion layer and a 60 nm-thick Al layer. Upon using the photoresist strip in the lift-off process, the buried gate was completed with a polishing process to remove the rabbit ear defects at the edge of the metal pattern. The Al<sub>2</sub>O<sub>3</sub> gate dielectric layer was then deposited via thermal atomic layer deposition (ALD). The first ZnO layer, Al-DMP/Al<sub>2</sub>O<sub>3</sub>, the separation layer (SL), and the second ZnO layer were deposited in sequence using a novel high-pressure (approximately 1.3 Torr) and longdosing time (approximately 20 s) ALD process that can form a very thin (2-4 nm) and dense film.26 A 70 nm Al layer patterned using the lift-off process was used as the source and drain electrodes. Finally, the channel area was defined using the ICP-RIE process. The process flow and a top-down optical image of the fabricated SCFET are shown in Fig. 1b and c, respectively. A cross-sectional transmission electron microscopy (TEM) photograph of the stacked channel is shown in Fig. 1d.

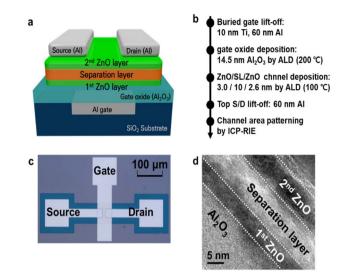

The  $I_D$ - $V_G$  curve of an n-type SCFET exhibits two distinct threshold voltages, which define three operational states (Fig. 2a). When the gate voltage  $(V_{GS})$  is below the first threshold voltage, the device is in an off-state (green area) where only offcurrent  $(I_{\mathrm{OFF}})$  flows through the channels. Upon exceeding the first threshold voltage  $(V_{th,1})$ , the current increases to an intermediate state level (blue area), where the current is saturated to a specific value  $(I_1)$  determined by the first ZnO layer. As the gate bias increases further and reaches the second threshold voltage  $(V_{\rm th,2})$ , the current begins to increase once more, entering the on-current region (red area). The primary current paths passing through two channel layers, yielding the stepwise ternary I-V curve, are schematically shown in Fig. 2b-d. Two channels are turned on sequentially because of the differences in the threshold voltage. First, when  $V_{GS}$  is lower than  $V_{th,1}$ , the device

Fig. 2 (a) Experimental  $I_{\rm D}$ – $V_{\rm G}$  characteristics of the n-type ZnO SCFET. The current transport mechanism for ternary operation of n-type SCFETs at (b) off state, (c) intermediate state, and (d) on state.

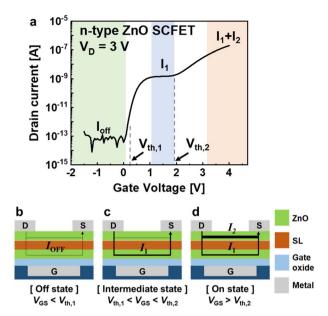

Fig. 3 Experimental and simulated  $I_{\rm D}-V_{\rm G}$  characteristics of the SCFET modulated using the thickness of the (a) first and (b) second ZnO layers (symbols: experimental data and solid lines: simulated data). (c)  $I_{\rm D}-V_{\rm G}$  characteristics of ZnO FETs modulated using the ZnO channel thickness. (d) Carrier concentration of ZnO channels with varied thickness. All direct current (DC) measurements were performed using a semiconductor parameter analyzer. The carrier concentration was measured using an SKPM.

remains in the off state, as illustrated in Fig. 2b. As  $V_{\rm GS}$  increases above  $V_{\rm th,1}$ , the conductivity of the first layer increases, as shown in Fig. 2c; however, the current level saturates to  $I_1$  because of the constant carrier concentration in the conduction band. Finally, when  $V_{\rm GS}$  exceeds  $V_{\rm th,2}$ , the second layer becomes conductive, and the device has the total current  $I_1 + I_2$ , as shown in Fig. 2d. Further analysis of the carrier transport mechanism can be found in ref. 26.

Fig. 3a and b illustrate the  $I_D$ - $V_G$  curves of the n-type SCFET modulated as functions of the thicknesses of the first and second ZnO channel layers  $(t_1 \text{ and } t_2)$ , respectively. The symbols represent the experimental data, and the solid lines indicate the simulation results obtained using the semi-empirical SCFET model explained below. As  $t_1$  increases,  $I_1$  increases, and only  $V_{\text{th},1}$  shifts slightly. These experimental results can be explained by the change in the carrier concentration of each channel layer, which is affected by the thickness and gate bias. 26,29 To support this claim, the electrical characteristics of single channel ZnO FETs and the variation in the carrier concentration with channel thickness are shown in Fig. 3c and d. By contrast, when  $t_2$  increases, the entire  $I_D$ - $V_G$  curve shifts to the left in each case. According to the simple device model described in Fig. 2,  $t_2$ should affect only  $V_{\text{th},2}$ . However, the experimental results show that  $V_{\text{th},1}$  and  $V_{\text{th},2}$  move simultaneously as  $t_2$  changes. Even though the process temperature is extremely low, the deposition process for the 2nd ZnO layer is a few tens of minutes (288 s for one ALD cycle). Thus, the extended thermal cycle appears to have some impact on  $V_{th1}$ .

The thickness of the Al-DMP/Al $_2O_3$  SL also affected the SCFET characteristics (Fig. S1, ESI $^{\dagger}$ ). However, when the thickness exceeds 10 nm, the  $V_{\rm th,1}$  shifts to the negative side, which is too severe to be used for logic circuit design. Additionally, the bidirectional I-V sweep showed a small hysteresis (<80 mV) in the subthreshold region (Fig. S2, ESI $^{\dagger}$ ). Therefore, the SL thickness changes and hysteresis were not considered in the subsequent modeling. All electrical characteristics data were measured using a semiconductor parameter analyzer (Keithley 4200) at 25 °C in ambient air. The carrier concentration of ZnO FETs was measured using scanning Kelvin probe microscopy (SKPM).

To simulate the applicability of SCFETs, a SPICE model was developed using the experimental parameters as summarized in Table 1. In this work, compared to the previously reported SCFET,  $^{26}$  a thinner  $t_1$  (3.0 nm) was used to obtain the extremely low  $I_1$  for low power consumption. In addition, the  $t_2$  range was expanded from 2.6 to 3.8 nm to model more negatively shifted I-V curves. These data were used to design a model for the low-power circuits discussed in the next section. Essentially, our model emulates a ternary device by combining two FETs with

Table 1 Experimental parameters used in the SCFET model

|           | EOT (nm) | $L_{\mathrm{ch}}\left(\mu\mathrm{m}\right)$ | $W_{ m ch}$ ( $\mu  m m$ ) | $t_1$ (nm) | $t_2$ (nm) | I <sub>1</sub> (nA) |

|-----------|----------|---------------------------------------------|----------------------------|------------|------------|---------------------|

| 25        | 5.6      | 60                                          | 24                         | 2.8        | 2.8        | 3.0                 |

| 26        | 9.0      | 12                                          | 24                         | 3.2-5.0    | 2.6-3.6    | 1-100               |

| This work | 8.2      | 12                                          | 16                         | 3.0-4.2    | 2.6-3.8    | 0.4-12              |

Paper

different threshold voltages. The model for each FET is

expressed by the following eqn (1):30,31

$$I_{\rm DS} = G_0 \left(\frac{W}{L}\right) \exp(\kappa (V_{\rm GS} - V_{\rm ON})^{\alpha}) V_{\rm DS} + I_{\rm off}$$

(1)

where  $G_0$  is a parameter related to the mobility; W and L represent the width and length, respectively, of the channel;  $\kappa$  and  $\alpha$  are empirical parameters for compact modeling;30,31 Von represents the turn-on voltage at which the drain current begins to increase; and  $I_{\rm off}$  represents the off-current. For the saturation region,  $V_{\rm DS}$ can be replaced with  $(V_{GS} - V_{on})$ . The difference in  $V_{on}$  between the two FETs defines the intermediate state.  $V_{\mathrm{on},1}$  is a function of  $t_1$  and  $t_2$ ,  $V_{\text{on},2}$  is a function of  $t_2$ , and the intermediate-state current  $I_1$  is primarily affected by  $t_1$ , according to the experimental results. Detailed correlation and equations are shown in Fig. S3, ESI.† This model matches the measured data with over 95% accuracy, as shown in Fig. 3a and b.

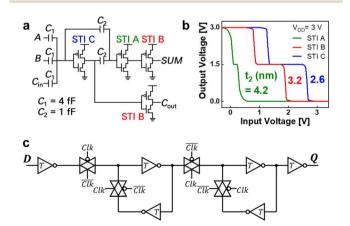

We simulated the functionality and performance of the TSA to evaluate the feasibility of the SCFET as unit devices for a synchronous ternary logic system. The TSA design requires one TFA and a ternary flip-flop (TFF). Fig. 4a shows the circuit diagram of the TFA designed with capacitors and three types of STIs, with only 13 devices, including the capacitors. This number is even smaller than that of a binary full adder (42 devices) designed with silicon CMOS transistors. The simulated transfer characteristics of the three different STIs-A, B, and C—are shown in Fig. 4b. For these three STIs, the  $t_2$  values were adjusted to 4.2, 3.2, and 2.6 nm, respectively. A p-type SCFET model used in STIs was also developed using the experimental data from a dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT)-based SCFET<sup>27</sup> (Fig. S4, ESI†), but the thickness dependence was assumed to be the same as that of n-type SCFETs. The p-type SCFET needs further study with much thinner p-type semiconductor materials.

The TFF was designed as a positive edge-triggered masterslave D flip-flop using STI B and transmission gates, as shown in Fig. 4c. The TFF captures a ternary value using a positive

Fig. 4 (a) Circuit diagram of a ternary full adder using capacitors. (b) Simulated transfer characteristics of standard ternary inverters (STIs) A, B, and C. (c) Circuit diagram of the ternary flip-flop. The inverter symbol with a capital "T" represents STI B.

feedback loop of back-to-back STIs at a positive edge of the binary clock signal using binary FET-based transmission gates. The proposed TFF was designed using 12 SCFETs and eight binary FETs.

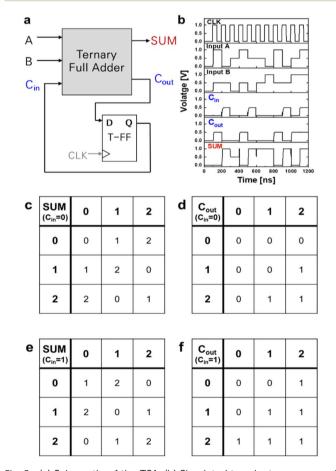

Finally, the TSA was designed by combining the TFA and TFF circuits as shown in Fig. 5a. The transient responses of the TSA circuit were investigated using Synopsys HSPICE with a 0.01 GHz operation frequency and 1 ns transient time. The fanout load capacitance of each STI was 1 fF, and the  $C_1$  and  $C_2$  values were 4 and 1 fF, respectively. For this simulation, the device parameters used for the SCFET model were adjusted to  $V_{DD} =$ 1 V,32 effective oxide thickness (EOT) = 1 nm, and channel length = 100 nm, for reasonable comparison with previous studies. The thickness of the ZnO layer was varied within a reasonable range,  $t_1 = 3.0$ –4.2 nm and  $t_2 = 2.6$ –4.2 nm, to design the different STIs shown in Fig. 4a. As illustrated in Fig. 5b, when specific input signal patterns (A, B) were inserted, the output carry signal  $(C_{out})$  was successfully fed again to the input carry  $(C_{in})$  node after one positive edge cycle through the TFF. Consequently, a serial addition operation that matched the clock signal was verified. The truth tables of the TSA are shown in Fig. 5c-f.

Fig. 5 (a) Schematic of the TSA. (b) Simulated transient responses of the TSA; simulation was performed using Synopsis HSPICE. Truth tables of (c) SUM and (d)  $C_{out}$  when  $C_{in} = 0$  and (e) SUM and (f)  $C_{out}$ when  $C_{in} = 1$ .

Nanoscale Advances Paper

Table 2 Power and delay of TSAs designed with SCFETs and CNTFETs

|                      | # Of the devices | Normalized $I_1$ | Power (µW) | Delay (ns) | PDP (fJ) |

|----------------------|------------------|------------------|------------|------------|----------|

| SCFET (this work)    | 33               | 1                | 13.83      | 6.71       | 92.80    |

|                      |                  | 1/3              | 5.188      | 7.01       | 36.37    |

|                      |                  | 1/10             | 1.677      | 8.52       | 14.29    |

|                      |                  | 1/30             | 0.5771     | 12.9       | 7.44     |

|                      |                  | 1/100            | 0.2108     | 33.9       | 7.15     |

| CNTFET <sup>31</sup> | 55               | X                | 3.079      | 6.54       | 20.11    |

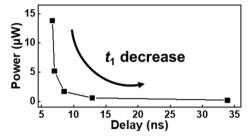

Fig. 6 Simulation result showing the tradeoff relationship between power and delay with a reduction in the first ZnO layer thickness  $t_1$ .

To compare the energy efficiencies of SCFET-based TSAs with that of the TSA designed with CNTFETs,33 the average power consumption and worst propagation delay were simulated (Table 2). In the case of SCFETs, the TSA performance was examined by varying  $t_1$ , which controls the level of  $I_1$ .  $t_1$  significantly influences the power and delay because most of the power consumption and the worst delay are determined by the charging and discharging steps of the half- $V_{\rm DD}$  state, which are related to  $I_1$ . Consequently, as  $t_1$  decreases, the PDP improves faster than the delay degradation. The tradeoff between power and delay as a function of  $t_1$  is shown in Fig. 6. Under the minimal  $I_1$  (1/100) condition, the TSA consumed one-tenth the power of the CNTFET-based TSA and exhibited one-third of the PDP. Although our proposed design still requires SCFETs with three different channel thicknesses, it is still more practical than the fabrication of CNTFETs with six different CNT diameters. Thus, SCFETs are promising alternatives to CNTFETs in ternary circuit applications.

#### Conclusions

We demonstrated a low-power TSA using SCFET technology that features a minimal device count of 33 and a PDP of approximately 7 fJ at  $V_{\rm DD} = 1$  V and EOT = 1 nm. These performance results are highly competitive with those of an ideal CNTFETbased circuit. SCFETs can be a practical solution to realize the various ternary logic circuits proposed using multi-diameter CNTFETs, primarily because the fabrication process is more practical owing to the low-thermal-budget deposition process, excellent thickness controllability, and wafer-scale process compatibility. Considering that it has the lowest PDP among alternative technologies, the ternary circuit using SCFETs is a promising technology for extreme low-power applications.

### Data availability

All data generated or analysed during this study are included in this published article [and its ESI†].

#### **Author contributions**

K. K. and S. K. contributed equally to this work. K. K., S. K., and B. H. L. conceived the idea and designed the experiments and simulation. K. K. and S.-Y. K. executed experiments and performed material and electrical characterization studies. S. K. contributed to the circuit design and simulation. All authors were involved in discussions.

#### Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

This research was supported by the Nanomaterials Development Program and Core Technology Development Project for the National Semiconductor Research Laboratory through the National Research Foundation of Korea (NRF) (No. RS-2022-NR068233 and No. RS-2023-00260813) funded by the Ministry of Science and ICT (MSIT), Korea.

#### Notes and references

- 1 M. T. Bohr, in Proceedings of the International Electron Devices Meeting, 1995, pp. 241-244.

- 2 Beyond CMOS and Emerging Materials Integration, The International Road Map of Semiconductors and Devices (IRDS), 2022.

- 3 S. L. Hurst, Multiple-valued logic—its status and its future, IEEE Trans. Comput., 1984, 33, 1160.

- 4 K. Kim, S. Kim, Y. Lee, D. Kim, S.-Y. Kim, S. Kang and B. H. Lee, in IEEE 50th International Symposium on Multiple-Valued Logic (ISMVL), 2020, pp. 155-158.

- 5 M. Andreev, S. Seo, K.-S. Jung and J.-H. Park, Adv. Mater., 2022, 34, 2108830.

- 6 H. Yoo and C.-H. Kim, J. Mater. Chem. C, 2021, 9, 4092-4104.

- 7 X. Xiong, J. Kang, Q. Hu, C. Gu, T. Gao, X. Li and Y. Wu, Adv. Funct. Mater., 2020, 30, 1909645.

- 8 H. Son, H. Choi, J. Jeon, Y. J. Kim, S. Choi, J. H. Cho and S. Lee, ACS Appl. Mater. Interfaces, 2021, 13, 8692-8699.

- 9 C.-J. Park, H. J. Park, J. Y. Kim, S.-H. Lee, Y. Lee, J. Kim and J. Joo, Semicond. Sci. Technol., 2020, 35, 065020.

- 10 A. Nourbakhsh, A. Zubair, M. S. Dresselhaus and T. Palacios, Nano Lett., 2016, 16, 1359-1366.

- 11 H. Yoo, S. On, S. B. Lee, K. Cho and J.-J. Kim, Adv. Mater., 2019, 31, 1808265.

- 12 C. Lee, C. Lee, S. Lee, J. Choi, H. Yoo and S. G. Im, Nat. Commun., 2023, 14, 3757.

- 13 S. Karmakar, E. Suarez and F. C. Jain, J. Electron. Mater., 2011, 40, 1749-1756.

- 14 S. Karmakar, M. Gogna, E. Suarez and F. C. Jain, IET Circuits Dev. Syst., 2015, 9, 111-118.

- 15 S. Karmakar, J. A. Chandy, M. Gogna and F. C. Jain, J. Electron. Mater., 2012, 41, 2184-2192.

- 16 S. Lin, Y.-B. Kim and F. Lombardi, IEEE Trans. Nanotechnol., 2011, 10, 217-225.

- 17 S. A. Ebrahimi, M. R. Reshadinezhad, A. Bohlooli and M. Shahsavari, Microelectron. I., 2016, 53, 156-166.

- 18 M. K. Q. Jooq, M. H. Moaiyeri and K. Tamersit, IEEE Trans. Circuits Syst. II, 2020, 2162.

- 19 A. Raychowdhury and K. Roy, IEEE Trans. Nanotechnol., 2005, 4. 168-179.

- 20 S. Kim, S.-Y. Lee, S. Park, K. R. Kim and S. Kang, IEEE Trans. Circuits Syst. I, 2020, 67, 3138-3151.

- 21 S. Heo, S. Kim, K. Kim, H. Lee, S. Kim, Y. J. Kim, S. M. Kim, H. Lee, S. Lee, K. R. Kim, S. Kang and B. H. Lee, IEEE Electron Dev. Lett., 1948, 39, 2018.

- 22 S. Shin, E. Jang, J. W. Jeong, B.-G. Park and K. R. Kim, IEEE Trans. Electron Dev., 2015, 62, 2396.

- 23 J. W. Jeong, Y.-E. Choi, W.-S. Kim, J.-H. Park, S. Kim, S. Shin, K. Lee, J. Chang, S.-J. Kim and K. R. Kim, Nat. Electron., 2019, 2, 307-312.

- 24 Y. Kang, J. Kim, S. Kim, S. Shin, E.-S. Jang, J. W. Jeong, K. R. Kim and S. Kang, in IEEE 47th International Symposium on Multiple-Valued Logic (ISMVL), 2017, pp. 25–30.

- 25 L. Lee, J. Hwang, J. W. Jung, J. Kim, H.-I. Lee, S. Heo, M. Yoon, S. Choi, N. Van Long, J. Park, J. W. Jeong, J. Kim, K. R. Kim, D. H. Kim, S. Im, B. H. Lee, K. Cho and M. M. Sung, Nat. Commun., 1998, 10, 2019.

- 26 S.-Y. Kim, K. Kim, A. R. Kim, H.-I. Lee, Y. Lee, S.-M. Kim, S. H. Yu, H.-W. Lee, H. J. Hwang, M. M. Sung and B. H. Lee, Adv. Electron. Mater., 2021, 7, 2100247.

- 27 Y. Lee, H. Kwon, S.-M. Kim, H.-I. Lee, K. Kim, H.-W. Lee, S.-Y. Kim, H. J. Hwang and B. H. Lee, Nano Convergence, 2023, 10, 12.

- 28 M. H. Moaiyeri, R. F. Mirzaee, K. Navi and O. Hashemipour, Nano Micro Lett., 2011, 3, 43-50.

- 29 J. Jeong and Y. Hong, IEEE Trans. Electron Dev., 2012, 59, 710-714.

- 30 S. Lee, D. Striakhilev, S. Jeon and A. Nathan, IEEE Electron Dev. Lett., 2013, 35, 84.

- 31 X. Cheng, S. Lee, G. Yao and A. Nathan, J. Disp. Technol., 2016, 12, 898-906.

- 32 K. Kim, S.-Y. Kim, Y. Lee, H.-W. Lee, H. Kwon, H.-I. Lee and B. H. Lee, in IEEE Silicon Nanoelectronics Workshop (SNW), 2022, pp. 1-2.

- 33 M. H. Moaiyeri, M. Nasiri and N. Khastoo, Eng. Sci. Technol. Int. J., 2016, 19, 271-278.