Cite this: *Nanoscale Adv.*, 2025, 7, 1596

Received 4th October 2024

Accepted 21st January 2025

DOI: 10.1039/d4na00825a

[rsc.li/nanoscale-advances](http://rsc.li/nanoscale-advances)

## Chemical etching of silicon assisted by graphene oxide under negative electric bias†

Yuta Goto, Toru Utsunomiya, \* Takashi Ichii and Hiroyuki Sugimura

Chemical etching of silicon assisted by graphene oxide (GO) has been attracting attention as a new method to fabricate micro- or nano-structures. GO promotes the reduction of an oxidant, and holes are injected into silicon, resulting in the preferential dissolution of the silicon under GO. In the conventional etching method with GO, the selectivity of the etching was low due to the stain etching caused by nitric acid. We developed an etching method that applies a negative bias to the p-type silicon substrate. The silicon under GO was more selectively etched in an etchant consisting of hydrofluoric acid and nitric acid than the silicon uncovered by GO. We assume that this is attributed to the difference in hole concentration in the silicon under GO and in the bare silicon. In addition, the in-plane diffusion of holes in silicon is suppressed by this method, resulting in the formation of highly anisotropic pores. From this study, we found that GO-assisted silicon etching occurs with a similar principle to metal-assisted chemical etching. The negative-bias etching with GO has the potential to be a simple and highly anisotropic microfabrication method.

## 1. Introduction

In recent years, catalyst-assisted chemical etching has been widely studied as one of the highly anisotropic etching processes for silicon microfabrication. Especially, noble metal nanoparticles have been utilized as the catalyst materials, which promote the reduction of the oxidant and inject holes into the silicon in a solution consisting of hydrofluoric acid and an oxidant. Therefore, the silicon under the noble metal is preferentially oxidized and dissolved. This method is well-known as metal-assisted chemical etching (MacEtch).<sup>1,2</sup> Some studies of MacEtch have proved that it can selectively etch silicon and fabricate silicon micro-nano-structures, which can be applicable to antireflective coatings.<sup>3,4</sup> Although MacEtch is facile and less expensive than dry etching, there are still some issues that need to be solved for its practical use. Especially, residual noble metals may produce deep-level traps in semiconductors and adversely affect device performance.<sup>5</sup> In order to replace noble metals in the wet process, there have been several reports about the assisted chemical etching of semiconductors with non-noble metals<sup>6–9</sup> and nanocarbon materials<sup>10–13</sup> as catalysts. Graphene oxide (GO) is a two-dimensional material that has a graphene-like structure partially modified with oxygen functional groups. GO can be produced in large quantities from graphite in simple processes and deposited through spin-

coating the dispersion.<sup>14,15</sup> Kubota *et al.* successfully applied GO as a catalyst for the etching of silicon,<sup>16–18</sup> and InP.<sup>19</sup> Xu *et al.* recently demonstrated the potential of GO-assisted etching for utilizing the silicon micro- or nano-structures in a solar cell.<sup>20</sup> They revealed that the reflectivity of the silicon was reduced to 9.9%, due to the surface texturing by GO. In addition, Mikurino *et al.* obtained a micropatterned trench structure combining GO-assisted germanium etching with photolithography and a lift-off process.<sup>21</sup> Due to their chemical composition, GO sheets can be easily removed, which is attributed to the photochemically generated active oxygen species.<sup>22</sup> The method can control the geometry of GO sheets on a substrate, leading to well-defined structures. Microcontact printing of GO sheets is another feasible way to pattern GO on a silicon substrate. Kubota *et al.* obtained the periodic silicon microstructure with this method and GO-assisted silicon etching.<sup>18</sup> The nanopatterning techniques of graphene or GO, such as nanosphere lithography,<sup>23</sup> laser lithography,<sup>24,25</sup> or scanning probe lithography<sup>26,27</sup> have also been proposed. For these advantages, GO is expected to be an alternative catalyst material to noble metals at catalyst-assisted chemical etching processes. The etching rate is reported to be  $\sim 1.5 \mu\text{m h}^{-1}$  when nitric acid is used as an oxidant,<sup>17</sup> which is much bigger than the one with hydrogen peroxide ( $\sim 1.0 \text{ nm h}^{-1}$ ).<sup>16</sup> However, unnecessary etching of the bare silicon in the vicinity of the GO sheets occurs due to the diffused holes. This results in the decrease of the anisotropy of the pores that are formed by the enhanced dissolution of the silicon covered by GO. Additionally, the formation of a porous layer is observed across the entire silicon surface.<sup>17</sup> These features are also reported at MacEtch<sup>1,28–30</sup> using noble metals.

Department of Materials Science and Engineering, Graduate School of Engineering, Kyoto University, Yoshida-honmachi, Sakyo-ku, Kyoto 606-8501, Japan. E-mail: [utsunomiya.toru.5v@kyoto-u.ac.jp](mailto:utsunomiya.toru.5v@kyoto-u.ac.jp)

† Electronic supplementary information (ESI) available. See DOI: <https://doi.org/10.1039/d4na00825a>

For fabricating silicon nanostructures through patterned catalysts, it is necessary to develop a further method to etch only the silicon under catalysts more selectively in controllable ways.

Applying an external electric bias during MacEtch is a method to control etching behavior.<sup>31–33</sup> Li *et al.* reported that the application of negative bias during Au-based MacEtch successfully suppressed side etch and improved the etching rate.<sup>32</sup> They assumed that the negative bias suppresses the in-plane diffusion of excess holes by electrostatic force, and holes are attracted to the backside of the silicon substrate. In the case of GO-assisted etching, nitric acid was used as the oxidant,<sup>17</sup> which is different from the reported MacEtch with bias applications.<sup>31–33</sup> Also, nitric acid can cause the stain etching of silicon, leading to the formation of a porous layer even without catalysts. Therefore, it has not been known whether the application of bias is an effective method of controlling GO-assisted etching behavior with an etchant consisting of hydrofluoric acid and nitric acid. Improving the selectivity of the GO-assisted silicon etching paves the way for the fabrication of micro- and nano-structures using the patterned GO sheets.

In this research, we succeeded in suppressing side etch and porous layer formation in GO-assisted p-type (100) silicon etching by applying a negative bias. The negative bias reduces the concentration of holes that governs the initiation of the etching reaction on the silicon surface, leading to the improved selectivity of etching. As the GO-assisted etching behavior can be controlled by applying bias, it is revealed that the mechanism of the etching is analogues to the one of MacEtch.

## 2. Experimental

As silicon substrates, we employed single-side polished, p-type (100) wafers with a resistivity of 1–30  $\Omega$  cm purchased from Electronics and Materials Corp. The cleaved silicon wafers were ultrasonically cleaned with acetone, ethanol, and ultrapure water, in that order. Subsequently, the substrates were exposed to Xe excimer lamp (wavelength: 172 nm, 10 mW cm<sup>-2</sup>; Ushio Co., Ltd.) for 20 min to remove organic contamination. The GO sheets are loaded onto the cleaned silicon substrate by spin-coating the GO dispersion (500 rpm for 15 s, followed by 2000 rpm for 100 s). We prepared GO using a modified Hummers' method.<sup>15</sup>

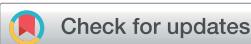

We have carried out the electrochemical etching on the silicon samples, using the cell configurations shown in Fig. 1a. The cell was made of polytetrafluoroethylene, and purchased from BAS Inc. An In–Ga liquid alloy was deposited to make an ohmic contact between the back side of the silicon sample and a current collector of Cu plate.<sup>34</sup> The O-ring (P-6, inner diameter: 5.8 mm; AIR WATER MACH Inc.) was inserted between the cell and the sample to prevent liquid leakage. The prepared silicon substrate and a Pt wire were used as a working and a counter electrode, respectively. The etchant was a mixture of HF (50%, semiconductor industry grade; Morita Chemical Industries Co., Ltd.) and HNO<sub>3</sub> (6.3 wt%, for volume analysis, Fujifilm Wako Pure Chemicals Corp.), and the composition is 29 mol L<sup>-1</sup> HF, and 5.3  $\times$  10<sup>-3</sup> mol L<sup>-1</sup> HNO<sub>3</sub>. HF is hazardous acid, which can

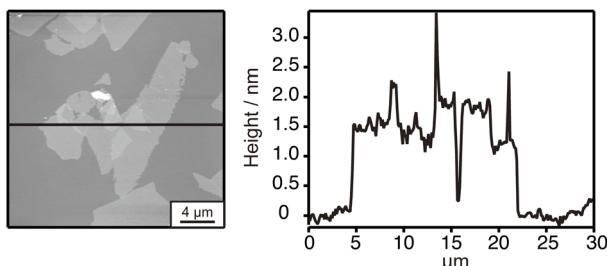

Fig. 1 (a) Schematic illustration of the experimental setup of electrochemically GO-assisted silicon etching. (b) An AFM topographic image and cross-sectional profile along the line after spin-coating the GO dispersion on a silicon substrate.

result in serious tissue damage, and must be handled with extreme care in a fume hood while wearing appropriate chemical safety protection. For the etching process, we immersed the sample at room temperature for 16 min to easily compare with previous results<sup>17</sup> unless otherwise stated. Approximately, 1.5 mL of the solution was used for electrochemical etching. To apply the bias between the silicon substrate and a Pt wire, we used a potentiostat (HZ-7000; Hokuto Denko Corp.). The surface height of the etched sample was observed by atomic force microscopy (AFM, MFP-3D; Oxford Instruments) with an Al-backside-coated Si cantilever (SI-DF40, spring const. 42 N m<sup>-1</sup>, resonance frequency 280 kHz; Hitachi High-Tech) in amplitude-modulation mode. The cross-sectional images of the etched sample were observed by scanning electron microscopy (SEM, JSM-6500F; JEOL, Ltd). Cross-sectional SEM and 3D laser microscopy (OLS4000-SAT; Olympus) were used to estimate the pore depth of the etched sample. The surface conditions of the samples were characterized by Fourier transform infrared spectroscopy (FT-IR, INVENIO; BRUKER Corp.) in the ATR mode using a germanium ATR crystal (GATR, Harrick).

## 3. Results and discussion

### 3.1. GO-assisted etching under negative bias

First, we observed the silicon substrate before the etching procedures. Fig. 1b shows an AFM topographic image of the silicon substrate after spin-coating the GO dispersion. The height of the deposited sheets is *ca.* 1 nm except for the overlapped areas, indicating the monolayer GO can be deposited using this spin-coating condition with pretreatments.<sup>35</sup> Most of

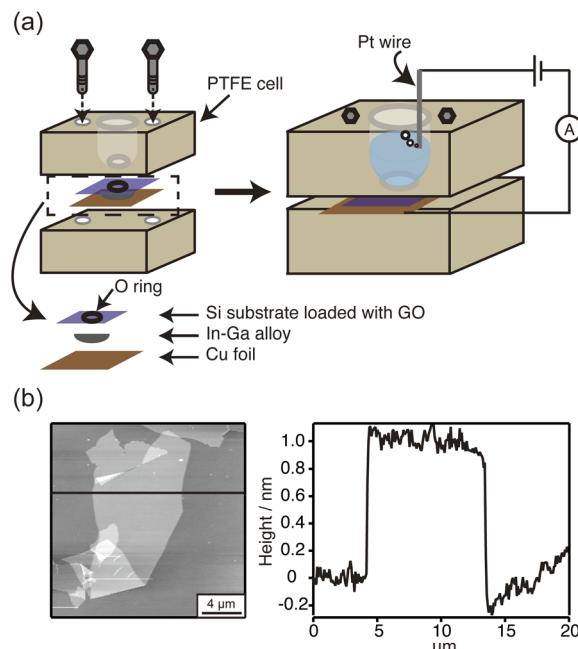

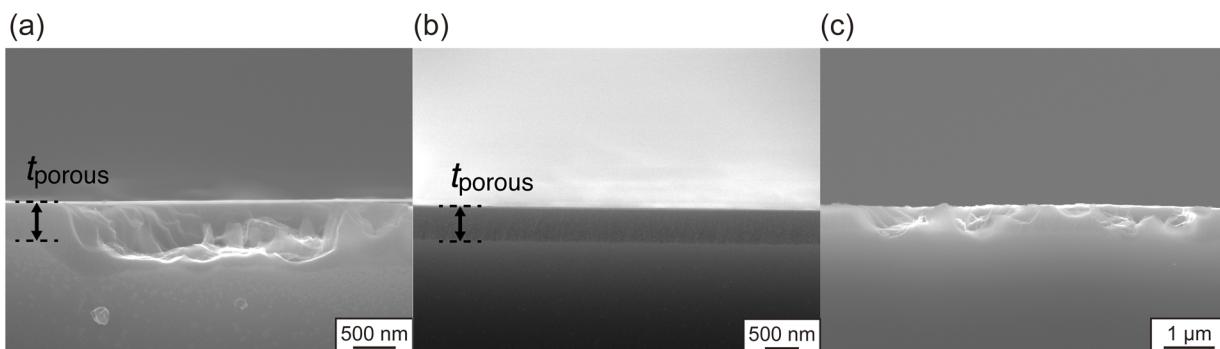

the GO sheets were distributed as a monolayer as shown in Fig. S1 in the ESI.† The detailed characteristic of GO is also shown in Fig. S2 in the ESI.† Fig. 2 shows cross-sectional SEM images of silicon substrates loaded with GO after etching for 16 min under open circuit potential (OCP), which is equivalent to just immersing the GO-loaded silicon substrate without electrode connections. As shown in Fig. 2a, the etched pore with *ca.* 3.5  $\mu$ m width and *ca.* 600 nm depth was observed. The width of this pore corresponds to the sheet size of GO, indicating that the preferential dissolution of Si proceeds at the GO-covered area at the similar etching rate to Kubota's result.<sup>17</sup> We referred to this etched pore with GO sheets as a "micrometer-width pore" hereafter. A porous layer, which shows the different dark gray contrast, was observed as well as micrometer-width pores, as indicated by an arrow in Fig. 2a. The thickness of the porous layer ( $t_{\text{porous}}$  in Fig. 2) is similar to the depth of the micrometer-width pores. A slight increase in the thickness of the porous layer near the micrometer-width pores was also seen. It is explained that this is caused by the diffusion of holes injected into Si from GO, which promotes oxidation and dissolution of Si, as in the case of MacEtch.<sup>28,36</sup>

The formation of a porous layer was also observed in the bare silicon region, and the thickness is the same as that of the porous layer around GO (Fig. 2b). In addition, in Fig. 2c, the shape of the micrometer-width pores formed by GO-assisted etching shows low anisotropy. These results reveal that GO assists silicon etching only in its vicinity and the injected holes from GO decrease the anisotropy of formed micrometer-width pores. The porous layer is formed by stain etching with an etchant containing HF and  $\text{HNO}_3$ , which proceeds by the following reaction.<sup>37</sup>

The nearly constant thickness of the porous layer at the GO-loaded silicon substrate indicates that the injected holes can be consumed over a wide area of silicon surfaces.

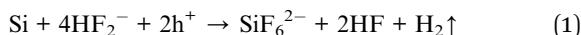

In order to control the micrometer-width pore structure and suppress the porous layer formation, we apply the bias voltage to the GO-loaded Si samples. Fig. 3a shows a cross-sectional SEM image of a silicon substrate loaded with GO after etching

Fig. 3 Cross-sectional SEM images of the silicon loaded with GO sheets after 16 min etching under (a)  $-2.0$  V, (b)  $-3.0$  V, (c)  $-3.5$  V at room temperature. Insets show higher magnification. (d) The relationship between the applied bias and the etching depth after etching for 16 min.

for 16 min under  $-2.0$  V. The obtained pore shows the width of *ca.* 3  $\mu$ m and the depth of *ca.* 400 nm, indicating that a micrometer-width pore can be formed at this etching condition and that the pore structure is similar to Fig. 2a. In contrast, the deep porous layer formation was not observed in the vicinity of the micrometer-width pore. The thickness of the porous layer decreased by 100 nm or less. In Fig. 3b, the silicon loaded with GO was etched under  $-3.0$  V. This cross-sectional SEM image shows that the apparent contrast of a porous layer cannot be observed in any regions, and the anisotropy of the micrometer-width pores was improved. When the silicon loaded with GO was etched under  $-3.5$  V, the micrometer-width pores with high anisotropy were still seen (Fig. 3c). Fig. 3d shows the relationship between the applied bias and the etching depth of the micrometer-width pores after etching for 16 min. As well as the decrease of the thickness of the porous layer, the depth of micrometer-width pores decreases with applying external bias.

Fig. 2 Cross-sectional SEM images of the etched silicon (a) loaded with GO sheets, (b) not loaded with GO sheets. (c) Shows cross-sectional SEM image of the etched silicon loaded with GO sheets at lower magnification.

Fig. 4 An AFM topographic image and cross-sectional profile along the line of GO sheets after 16 min etching under  $-5.0$  V at room temperature.

These results indicate that applying the negative bias can suppress the porous layer formation, and that optimization of the bias voltage is required for anisotropic micrometer-width pore formation. The enhancement of the etching rate under any negative bias, as Li *et al.* reported,<sup>32</sup> was not seen in the etching with GO. This possible reason will be discussed in the next section.

We performed the etching of the silicon loaded with GO under  $-5.0$  V to further investigate the effect of negative bias on the etching rate. Fig. 4 shows the AFM topographic image of the sample etched under  $-5.0$  V for 16 min. Several micrometer scale convex regions with a height of *ca.* 1 nm are obtained. The height of the convex regions in Fig. 4 and 1b is very analogous and agrees well with monolayer GO.<sup>33</sup> We also observed that the smoothness of the bare silicon region was identical before and after etching, indicating that the structural features remained even after etching under  $-5.0$  V. From these results, we inferred that the etching rates of GO-loaded silicon and bare silicon areas are equal at  $-5.0$  V, and they are considerably small.

### 3.2. The mechanism of GO-assisted silicon etching under the negative bias

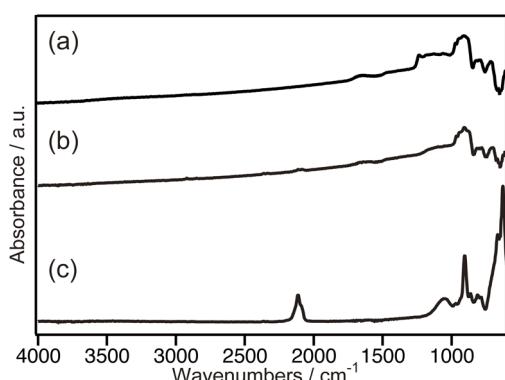

We observed FT-IR spectra of a bare silicon substrate etched under some conditions, as shown in Fig. 5. The sharp peak around  $2100\text{ cm}^{-1}$  was observed in the silicon etched under

Fig. 5 Absorbance spectra in the IR region of silicon surfaces (a) before etching, after 16 min etching under (b)  $-5.0$  V, and (c) no bias at room temperature.

OCP (Fig. 5c), corresponding to Si-Hx.<sup>38</sup> The dangling bonds of silicon after etching are predominantly occupied by hydrogen atoms.<sup>38</sup> However, the silicon etched under  $-5.0$  V did not show the peak around  $2100\text{ cm}^{-1}$ , as shown in Fig. 5b, which is similar to the silicon sample before etching (Fig. 5a). This suggests that the surface silicon atoms are not hydrogen-terminated after etching under  $-5.0$  V (Fig. 5b). From these results, we found that applying  $-5.0$  V during etching inhibits the etching reaction in both the GO-loaded and bare silicon regions. The broad peaks around  $1100\text{ cm}^{-1}$  are composed of Si-O-Si anti-symmetric stretches and Si-O vibration.<sup>39</sup> Hydrofluoric acid removes the silicon oxide layer according to the following equation.

This reaction is not mediated by the transfer of electrons, and it is expected to proceed rapidly because the hydrofluoric acid concentration is rich in the etchant used in this experiment. Nevertheless, those absorption peaks at the etched surface could be attributed to the cleaning of them with ultra-pure water and their exposure to ambient air after etching.

Kolasinski revealed that the sticking coefficient of  $\text{F}^-$  (aq) on a H-terminated Si surface is  $<5 \times 10^{-11}$  and the presence of the hole in the valence band of the silicon increases the coefficient of  $\text{F}^-$  (aq) by 11 orders of magnitude.<sup>40</sup> According to the model of the silicon etching mechanism proposed by Gerischer<sup>41</sup> and modified by Kolasinski,<sup>40</sup> when holes are injected into hydrogen-terminated silicon atoms on the surface, the sticking coefficient of  $\text{F}^-$  (aq) is increased and Si-H is replaced by Si-F. Since the fluorine-terminated silicon atoms on the surface are chemically unstable, they react with hydrofluoric acid and dissolve as  $\text{SiF}_6^{2-}$ . Therefore, the distribution of holes near the Si surface, which can be modulated by the bias voltage, is a crucial factor for controlling the etching reaction. The reduction reaction of  $\text{HNO}_3$  proceeds as follows.

Note that the reduction of the nitrite ion to nitric oxide occurs simultaneously, however, eqn (3) is considered to be the rate-determining step.<sup>42</sup> The holes injected by  $\text{HNO}_3$  reduction increase the sticking coefficient of  $\text{F}^-$  (aq) of surface silicon atoms and promote the reaction described in eqn (1).

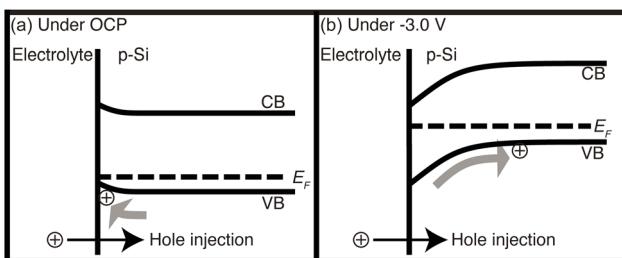

Fig. 6 shows the schematic band diagrams of the p-type silicon/solution junction for describing the influence of applying the external bias. When the silicon is immersed into the electrolyte consisting of hydrofluoric acid and nitric acid, without the external circuit connection, the dissolution of silicon atoms and porous layer formation proceed as shown in Fig. 2. Combining that with the increase of the sticking coefficient of  $\text{F}^-$  (aq) in the presence of holes, the accumulation layer for supplying holes to the interface can be formed when the bare silicon is in contact with the etchant under OCP (Fig. 6a). Since the flux of the injected holes through  $\text{HNO}_3$  reduction is large, we supposed that the Fermi level of the whole silicon

Fig. 6 Schematic band diagrams showing the mechanism of etching, (a) shows the interface between the electrolyte and the bare silicon under OCP, whereas (b) shows under the  $-3.0$  V. CB, VB, and  $E_F$  are the conduction band edge, the valence band edge, and the Fermi level of the p-type silicon, respectively.

sample can shift to a lower level. The similar Fermi level shift has been considered in the case of the etching of p-type silicon using anodically biased electrodes in contact.<sup>43</sup> When the negative bias is applied to the silicon, the energy levels of the silicon shift upward, as shown in Fig. 6b. This will form the downward band bending at the p-type silicon/solution junction, and the injected holes through  $\text{HNO}_3$  reduction easily travel to the bulk silicon and are consumed at the counter electrode, not for the silicon dissolution. Since the sticking coefficient of  $\text{F}^-$  (aq) in the absence of holes is extremely small, it is assumed that the rate at which silicon atoms on the surface react with hydrofluoric acid is expected to become very slow.

In the case of the GO-covered silicon, GO enhances the reduction of  $\text{HNO}_3$  and increases the number of injected holes in the valence band.<sup>17</sup> This can lead to the lowering of the Fermi level, and the increase of the holes in the accumulated layer, resulting in the enhanced silicon dissolution. When a negative bias such as  $-3.0$  V is applied to the silicon, the energy level of the silicon shifts upward similarly. However, the modulation of band bending near GO sheets is supposed to be insufficient, and then the consumption of the injected holes *via* silicon etching can still proceed. Thus, the silicon beneath GO is selectively etched, and the formation of the porous layer in the bare silicon region is suppressed. Meanwhile, when the negative bias is large enough, such as  $-5.0$  V, the depletion layer is formed at the p-type silicon/solution junction, regardless of GO

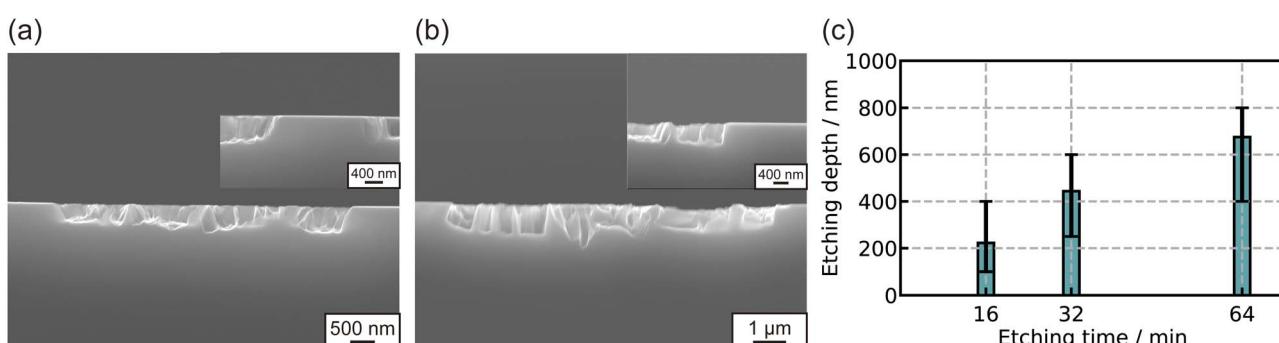

sheets immobilization, and the whole etching reactions are inhibited. The cross-sectional SEM images of the GO-coated silicon that was etched under  $-3.0$  V for  $32$  min and  $64$  min are shown in Fig. 7a and b, respectively. The apparent contrast of the porous layers was not observed, and similar anisotropic micrometer-width pores with Fig. 3b were obtained at longer etching durations, indicating the remaining selectivity of the etching reaction under this negative bias of  $-3.0$  V. Fig. 7c shows the relationship between the etching time and the etching depth of the micrometer-width pores under  $-3.0$  V. As the etching time increases, the depth of the micrometer-width pores also increases. These results support the schematic band diagram in Fig. 6. Furthermore, the average roughness of the surface of the bare silicon region under OCP and negative bias was obtained from AFM images (Fig. S3 in the ESI<sup>†</sup>). Those results show the suppression of etching of the bare silicon region under negative bias and also support the band diagram modulation by applying external bias.

It is noted that some multilayer GO sheets did not promote silicon etching, compared to the monolayer GO as shown in Fig. S4 in the ESI<sup>†</sup>. This observation is consistent with Kubota's results<sup>17,18</sup> and shows no discrepancies with the tunnelling of holes through GO towards the GO/p-type silicon interface. The fact that band bending is possible by applying external bias implies that GO-assisted etching has a similar mechanism to MacEtch,<sup>44</sup> which means GO contributes as a localized power supply.

Contrary to the report of Li *et al.*,<sup>32</sup> the enhancement of the etching rate was not observed. This could be explained by the difference in the number of holes that are generated *via* catalysts and that can diffuse in-plane in silicon. In MacEtch using noble metals as catalysts, a large number of holes are generated, and the excess holes can diffuse in-plane.<sup>31,36</sup> Meanwhile, the number of holes generated by GO is relatively small as the side etch was seen just near the vicinity of the micrometer-width pores (Fig. 2a). Therefore, the excess holes in GO-assisted etching can barely contribute to the increase of the etching rate for micrometer-width pores under negative bias.

Then, the suppression of the porous layer in the vicinity of micrometer-width pores can be explained as follows. Under OCP, holes are injected from GO to the silicon surface, and

Fig. 7 Cross-sectional SEM images of the etched silicon loaded with GO sheets under  $-3.0$  V for (a)  $32$  min, and (b)  $64$  min, respectively. Insets show higher magnification. (c) The relationship between the etching time and the etching depth under  $-3.0$  V.

etching is considered to preferentially proceed from the edges or grain boundaries of the GO from the viewpoint of mass transport.<sup>45,46</sup> At this time, the excessive holes diffuse not only toward the silicon under the GO, but also toward its vicinity, resulting in side etch. This is supposed to cause a decrease in the anisotropy of the micrometer-width pores. Meanwhile, as already described above, negative bias draws holes to the backside of the silicon substrate, suppressing excessive hole diffusion and resulting in highly anisotropic micrometer-width pores.

Our preliminary results of the etching under negative bias with microcontact printing of GO sheets are shown in Fig. S5 in the ESI.† Although the microscale assembly of GO sheets and selective etching features were obtained, the in-plane nanoscale patterning of GO sheets has remained a challenge. However, in the future, the introduction of patterned GO deposition techniques mentioned earlier<sup>23–27</sup> to our developed etching methods can contribute to the controlled surface structures with micro- and nano-scale features of silicon.

## Conclusions

We report a technique for selective etching of silicon covered with GO by applying negative bias in an etchant consisting of hydrofluoric acid and nitric acid. This is attributed to the difference in hole concentration injected through nitric acid reduction at the deposited GO sheets and at the bare silicon surface. The presence of holes drastically increases the sticking coefficient of  $F^-$  (aq) on silicon atoms and initiates etching. We found that the application of negative bias suppresses the diffusion of excess holes injected into silicon and improves the micrometer-width pore anisotropy. Similar to MacEtch, the band modulation by bias application is possible in GO-assisted etching, indicating that GO can act as a source for very localized anodic oxidation. By applying an appropriate magnitude of negative bias, it is still possible to achieve a faster etching rate than that of the conventional solution composed of hydrofluoric acid and hydrogen peroxide.<sup>16</sup> This technique is expected to be able to fabricate silicon micro- or nano-structures, owing to the facile synthesis and fabrication of GO and its low-cost process. Considering that GO sheets can be easily deposited over large areas by spin-coating, large-area and highly uniform silicon microstructures could be obtained if the stability of GO on the silicon substrate can be improved and the catalytically active sites can be identified.

## Data availability

The data supporting the findings of this study have been included as part of the ESI.†

## Author contributions

Y. Goto drafted the original paper and performed the experiments. T. Utsunomiya, T. Ichii, and H. Sugimura coordinated the project, and contributed to the interpretation of the results.

All authors discussed the results and contributed to the preparation of the paper.

## Conflicts of interest

There are no conflicts of interests to declare.

## Acknowledgements

This work was partially supported by JSPS KAKENHI grants JP20H02450, JP24K01179, the Kyoto University Foundation, and the Iketani Science and Technology Foundation. Part of this work was supported by the Kyoto University Nano Technology Hub in “Advanced Research Infrastructure for Materials and Nanotechnology in Japan (ARIM Japan)” sponsored by the Minister of Education, Culture, Sports, Science, and Technology (MEXT), Japan.

## Notes and references

- 1 X. Li and P. W. Bohn, *Appl. Phys. Lett.*, 2000, **77**, 2572–2574.

- 2 Z. P. Huang, N. Geyer, L. F. Liu, M. Y. Li and P. Zhong, *Nanotechnology*, 2010, **21**, 465301.

- 3 S. K. Srivastava, D. Kumar, P. K. Singh and V. Kumar, in *2009 34th IEEE Photovoltaic Specialists Conference (PVSC)*, IEEE, Philadelphia, PA, USA, 2009, pp. 001851–001856.

- 4 S. K. Srivastava, D. Kumar, S. W. Schmitt, K. N. Sood, S. H. Christiansen and P. K. Singh, *Nanotechnology*, 2014, **25**, 175601.

- 5 A. J. Tavendale and S. J. Pearton, *J. Phys. C Solid State Phys.*, 1983, **16**, 1665–1673.

- 6 J. D. Kim, M. Kim, C. Chan, N. Draeger, J. J. Coleman and X. Li, *ACS Appl. Mater. Interfaces*, 2019, **11**, 27371–27377.

- 7 M. Gayrard, J. Voronkoff, C. Boissière, D. Montero, L. Rozes, A. Cattoni, J. Peron and M. Faustini, *Nano Lett.*, 2021, **21**, 2310–2317.

- 8 K. Kim, S. Choi, H. Bong, H. Lee, M. Kim and J. Oh, *Nanoscale*, 2023, **15**, 13685–13691.

- 9 K. Yamamoto, T. Utsunomiya, T. Ichii and H. Sugimura, *Jpn. J. Appl. Phys.*, 2024, **63**, 04SP28.

- 10 J. Kim, D. H. Lee, J. H. Kim and S.-H. Choi, *ACS Appl. Mater. Interfaces*, 2015, **7**, 24242–24246.

- 11 T. Hirano, K. Nakade, S. Li, K. Kawai and K. Arima, *Carbon*, 2018, **127**, 681–687.

- 12 Y. Hu, H. Fu, J. Wang, R. Sun, L. Wu, Y. Liu, J. Xu, J. Liu and K.-Q. Peng, *Corros. Sci.*, 2019, **157**, 268–273.

- 13 H. Asoh, D. Sekido and H. Hashimoto, *Mater. Sci. Semicond. Process.*, 2021, **121**, 105327.

- 14 W. S. Hummers and R. E. Offeman, *J. Am. Chem. Soc.*, 1958, **80**, 1339.

- 15 M. Hirata, T. Gotou, S. Horiuchi, M. Fujiwara and M. Ohba, *Carbon*, 2004, **42**, 2929–2937.

- 16 W. Kubota, R. Ishizuka, T. Utsunomiya, T. Ichii and H. Sugimura, *Jpn. J. Appl. Phys.*, 2019, **58**, 050924.

- 17 W. Kubota, T. Utsunomiya, T. Ichii and H. Sugimura, *Langmuir*, 2021, **37**, 9920–9926.

18 W. Kubota, R. Yamaoka, T. Utsunomiya, T. Ichii and H. Sugimura, *ACS Appl. Nano Mater.*, 2022, **5**, 11707–11714.

19 W. Kubota, T. Utsunomiya, T. Ichii and H. Sugimura, *Jpn. J. Appl. Phys.*, 2023, **62**, SG1040.

20 Y. Xu, Q. Zhao, J. Chen, J. Zhang and B. Xu, *Phys. Scr.*, 2024, **99**, 085914.

21 R. Mikurino, A. Ogasawara, T. Hirano, Y. Nakata, H. Yamashita, S. Li, K. Kawai, K. Yamamura and K. Arima, *J. Phys. Chem. C*, 2020, **124**, 6121–6129.

22 Y. Tu, T. Utsunomiya, T. Ichii and H. Sugimura, *ACS Appl. Mater. Interfaces*, 2016, **8**, 10627–10635.

23 M. Wang, L. Fu, L. Gan, C. Zhang, M. Rümmeli, A. Bachmatiuk, K. Huang, Y. Fang and Z. Liu, *Sci. Rep.*, 2013, **3**, 1238.

24 R. D. Rodriguez, G. V. Murastov, A. Lipovka, M. I. Fatkullin, O. Nozdrina, S. K. Pavlov, P. S. Postnikov, M. M. Chehimi, J.-J. Chen and E. Sheremet, *Carbon*, 2019, **151**, 148–155.

25 T. Zou, B. Zhao, W. Xin, Y. Wang, B. Wang, X. Zheng, H. Xie, Z. Zhang, J. Yang and C. Guo, *Light Sci. Appl.*, 2020, **9**, 69.

26 G. Lu, X. Zhou, H. Li, Z. Yin, B. Li, L. Huang, F. Boey and H. Zhang, *Langmuir*, 2010, **26**, 6164–6166.

27 H. Li, Z. Ying, B. Lyu, A. Deng, L. Wang, T. Taniguchi, K. Watanabe and Z. Shi, *Nano Lett.*, 2018, **18**, 8011–8015.

28 C. Chartier, S. Bastide and C. Lévy-Clément, *Electrochim. Acta*, 2008, **53**, 5509–5516.

29 M. L. Chourou, K. Fukami, T. Sakka, S. Virtanen and Y. H. Ogata, *Electrochim. Acta*, 2010, **55**, 903–912.

30 A. Matsumoto, K. Furukawa, S. Majima, K. Iwamoto and S. Yae, *J. Electrochem. Soc.*, 2021, **168**, 112504.

31 P. Lianto, S. Yu, J. Wu, C. V. Thompson and W. K. Choi, *Nanoscale*, 2012, **4**, 7532.

32 L. Li, X. Zhao and C.-P. Wong, *ACS Appl. Mater. Interfaces*, 2014, **6**, 16782–16791.

33 E. Torralba, S. Le Gall, R. Lachaume, V. Magnin, J. Harari, M. Halbwax, J.-P. Vilcot, C. Cachet-Vivier and S. Bastide, *ACS Appl. Mater. Interfaces*, 2016, **8**, 31375–31384.

34 L. Liu, K. Peng, Y. Hu, X. Wu and S. Lee, *Adv. Mater.*, 2014, **26**, 1410–1413.

35 Y. Tu, T. Ichii, T. Utsunomiya and H. Sugimura, *Appl. Phys. Lett.*, 2015, **106**, 133105.

36 K. Tsujino and M. Matsumura, *Electrochim. Solid-State Lett.*, 2005, **8**, C193.

37 V. Lehmann, *The Electrochemistry of Silicon: Instrumentation, Science, Materials and Applications*, Wiley-VCH, Weinheim, 2002.

38 X. H. Sun, S. D. Wang, N. B. Wong, D. D. D. Ma, S. T. Lee and B. K. Teo, *Inorg. Chem.*, 2003, **42**, 2398–2404.

39 É. Vázsonyi, E. Szilágyi, P. Petrik, Z. E. Horváth, T. Lohner, M. Fried and G. Jalsovszky, *Thin Solid Films*, 2001, **388**, 295–302.

40 K. W. Kolasinski, *Phys. Chem. Chem. Phys.*, 2003, **5**, 1270–1278.

41 H. Gerischer and W. Mindt, *Electrochim. Acta*, 1968, **13**, 1329–1341.

42 M. T. De Groot and M. T. M. Koper, *J. Electroanal. Chem.*, 2004, **562**, 81–94.

43 T. Sugita, C.-L. Lee, S. Ikeda and M. Matsumura, *ACS Appl. Mater. Interfaces*, 2011, **3**, 2417–2424.

44 K. W. Kolasinski, *Nanoscale Res. Lett.*, 2014, **9**, 432.

45 N. Geyer, B. Fuhrmann, Z. Huang, J. De Boor, H. S. Leipner and P. Werner, *J. Phys. Chem. C*, 2012, **116**, 13446–13451.

46 X. Fan, S. Wagner, P. Schädlich, F. Speck, S. Kataria, T. Haraldsson, T. Seyller, M. C. Lemme and F. Niklaus, *Sci. Adv.*, 2018, **4**, eaar5170.