## HIGHLIGHT

[View Article Online](#)

[View Journal](#) | [View Issue](#)

Cite this: *Mater. Adv.*, 2025,

6, 5410

## Single crystal halide perovskites for resistive switching memory devices and artificial synapse

Hyojung Kim

Contemporary systems in artificial intelligence and edge computing require nonvolatile memories that integrate extremely low programming energy with enduring reliability. Halide perovskites exhibit significant potential due to their lattice structures, which promote the interaction of ionic and electronic transport, thus allowing for reliable resistive switching. Despite advancements, polycrystalline films continue to face challenges such as grain-boundary traps and unpredictable ion migration. Consequently, recent efforts have focused on single-crystal architectures to address these issues. Defect-lean  $ABX_3$  single-crystal halide perovskites meet these requirements as the structured lattice allows swift carrier transport with controlled ion movement. Recent studies have outlined crystallographic principles, manufacturing processes, and interfacial chemistries that produce domains sufficiently coherent to facilitate dependable resistive-switching memories. The removal of grain boundaries in memory elements enhances the stability of ion-mediated electrochemical metallization and valence variation processes, allowing the creation of multilevel states with minimal energy consumption during programming. Ultralow trap populations identified in epitaxial layers promote bias-stable operation when integrated with precisely matched dielectric or polymer interlayers, effectively reducing leakage currents during extended cycling. The orientation of crystals significantly affects the directions of vacancy migration and alters channel conductance, even when subjected to high thermal stress. The integration of insights from growth science and interface modification leads to a comprehensive approach for utilizing simultaneous ionic and electronic transport in single-crystal halide perovskites across various manufacturing scales. Given this foundation, it appears that rapid advancements are on the way for energy-efficient memory and logic components designed for compact, data-intensive electronics that enable artificial intelligence, edge computing, and adaptable wearable technologies shortly.

Received 8th June 2025,

Accepted 2nd July 2025

DOI: 10.1039/d5ma00609k

[rsc.li/materials-advances](http://rsc.li/materials-advances)

## 1. Introduction

The rapid expansion of inference-driven artificial intelligence, edge analytics, and the Internet of Things (IoT) has revealed throughput and energy limitations that are characteristic of conventional von Neumann architectures.<sup>1–7</sup> With the increasing demands for performance and efficiency, there is a growing interest in novel materials for applications such as light-emitting diodes, chemical and gas sensors, low-temperature thin-film transistors, and resistive switching memories.<sup>8–14</sup> Densely integrated circuits are made possible by materials that combine low-energy, large-area manufacturing with ultrafast carrier transport.<sup>15–22</sup> Halide perovskites have attracted significant attention due to their remarkable structural flexibility and concurrent ionic-electronic functionality, establishing this family as a promising foundation for future hardware innovations.<sup>22–27</sup> The significant optoelectronic tunability, extended carrier diffusion lengths, and tolerance to defects

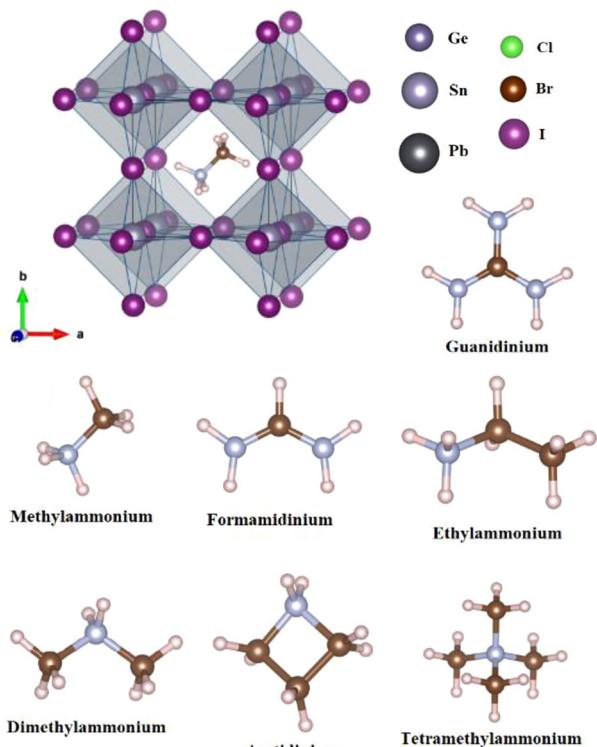

enhance these process benefits, promoting multifunctional characteristics across various form factors and substrates.<sup>28–32</sup> Halide perovskites feature an  $ABX_3$  structure where a monovalent A-site cation, a divalent B-site metal, and a halide X anion are positioned at the edges of a  $BX_6$  octahedron in Fig. 1.<sup>33–35</sup> While the ability for dual ionic and electronic transport allows adaptability, it simultaneously presents distinct challenges. The movement of unstable ions in response to external bias results in hysteresis.<sup>36,37</sup>

Additionally, the grain boundaries formed during the growth of polycrystalline materials serve as sites for recombination and as pathways for leakage. They also increase power consumption and hide the fundamental transport physics essential for optimizing devices. Ion migration activation barriers are raised, leakage is reduced, and trap densities are suppressed when intergranular areas are removed. This review shows the evolution from crystal chemistry to circuit functionality, starting with the crystallographic descriptors that influence phase stability and bandgap modulation, followed by an evaluation of the primary ion migration modes and the consequences for resistive switching. This review integrates these

Department of Semiconductor Systems Engineering, Sejong University, Seoul 05006, Korea. E-mail: [hyojungkim0912@sejong.ac.kr](mailto:hyojungkim0912@sejong.ac.kr)

Fig. 1 Schematic illustration of  $ABX_3$ . In this representation, carbon, nitrogen, and hydrogen atoms are depicted using dark brown, gray, and light pink colors, respectively. Reproduced with permission.<sup>35</sup> Copyright 2023, MDPI.

topics to provide a comprehensive framework for the full utilization of halide perovskites in multifunctional electronic systems.

## 2. Operational principles of resistive switching

Precise adjustment of the electrical impulses applied allows each cell to switch between high-resistance (HRS) and low-resistance (LRS) states during its operation. Before the operation, an electroforming step is typically considered crucial. Achieving the ON or SET state requires a bias that is strong enough to cause filament formation or the accumulation of interfacial charge, which in turn creates a conductive channel for carriers within the switching layer.<sup>38–40</sup> On the other hand, the OFF or RESET state is attained by applying an opposite polarity, which interrupts the previously established way and stops conduction channels within the active layer.<sup>41</sup> Halide-perovskite devices frequently utilize bipolar switching, utilizing reversed electric fields to transition between resistive states. Upon the application of the forward bias, metallic filaments spread through the perovskite lattice, turning the originally insulating layer into a conductive phase suitable for SET operation.<sup>42,43</sup> As the potential approaches 0, the current decreases, and a subsequent reverse field eliminates or removes the filaments, thus reinstating the HRS and finalizing

the RESET process for dependable cycling.<sup>44–47</sup> Unipolar switching simplifies circuit design by allowing SET and RESET operations to occur under the same polarity, thus reducing the need for additional external circuits. The combination of local Joule heating and defect aggregation creates a lasting conductive channel, signifying the conclusion of the SET process.<sup>48–50</sup> The ON/OFF ratio measures the resistance or current in HRS compared to LRS, establishing the switching margin that determines the performance limits for resistive memory elements during read-out conditions. An extensive ON/OFF window reduces the possibility of read errors and allows the storage of multilevel information within a single memory unit with effective bias. Recent literature confirms reproducible conductance plateaus between three and five distinct levels, with ON/OFF ratios sustained for  $10^2$  to  $10^3$  switching cycles across single-crystal and layered halide-perovskite devices, thus, validating multilevel programmability in practice. The switching speed relates to the latency needed for state conversion right after an external bias is applied across the storage medium during active operation. In addition to rapid switching capabilities, it is important to validate long-term reliability metrics, particularly endurance and retention, to guarantee consistent functional integrity throughout the device's operational lifespan during repeated cycling. Across single-crystal and layered halide-perovskite memories, invariant SET/RESET voltages and ON/OFF margins are preserved over  $10^2$ – $10^3$  switching cycles and  $>10^4$  s retention, even under ambient and 85 °C/85% RH stress, thereby furnishing direct evidence of bias-stable operation. Endurance refers to the highest count of electrical cycles that a device can repeatedly switch between HRS and LRS while maintaining the desired ON/OFF ratio reliably. In single-crystal halide perovskites, adjusting uniaxial lattice strain stabilizes switching thresholds and reduces the range of vacancy-formation energies. Deep traps are passivated, leakage is reduced, and the programming energy needed for dependable switching is decreased by doping at the A- or X-site. By coupling these material levers with one-selector-one-resistor (1S-1R) hierarchies, sneak currents are reduced, and passive crossbar arrays can grow to vast sizes without the need for additional transistors. Each memory cell has a threshold-type perovskite selector stacked vertically on top of it. Selector-assisted designs, precision doping, and strain engineering work together to create a viable route toward dense, low-power halide-perovskite memory arrays.

## 3. Halide perovskite single crystals

The bandgap can be tuned by adjusting the crystallite size in thin films, providing an alternate method of improving optical behavior.<sup>51</sup> A recent investigation evaluated ionic migration in high-performance perovskites by analyzing photocurrent hysteresis. The results indicate that external biasing changes the polarity of solar cells regardless of their structural design, composition, or electrode material, emphasizing the significant role of mobile ions in these advanced materials. Rapid ionic

movement is a result of low defect-formation energies and moderate activation barriers, making transport highly sensitive to degradation-related factors during operation.<sup>52–55</sup> Ionic migration is crucial even when photoconversion efficiency may decrease because rapid ion flow gives the lattice physical adaptability. As a result, electronic technologies utilizing halide perovskites can modify or limit ionic displacement based on defined functional needs. The relatively low activation energy linked to ions in halide perovskite matrices facilitates movement through Schottky-type defects, demonstrating clear species mobility and emphasizing the significant impact that structural or compositional changes have on device performance.<sup>54,56,57</sup> Organic A-site cations often take on an orientation at an angle of roughly 30 degrees when operating in less restricted environments. However, an applied electric field disrupts this configuration. The process of collective restructuring, along with the notably high ionic conductivity of halide perovskites, enhances migration, changes current–voltage (*I*–*V*) hysteresis, and reveals the relationship between molecular alignment and ionic mobility within these semiconductors. Single-crystal halide perovskites demonstrate a reduced presence of defects and impurities, as well as an absence of grain boundaries.<sup>58–60</sup> Removing grain boundaries eliminates fast ionic pathways and trap-rich interfaces, yielding more controlled electrochemical filament formation, dissolution and, consequently, markedly improved switching uniformity, endurance, and retention in practical resistive memory devices. Consequently, the activation energies for ion transport under dark conditions exceed those observed in polycrystalline. This lattice extends carrier lifetimes and reduces recombination pathways. Increased activation energies further hinder drift under prolonged bias stress. While completely immobilizing mobile ions is not yet feasible, ongoing studies focus on confining and mixing their drift through the use of grain-boundary-free single crystals, ion-blocking interlayers, and lattice-strain engineering. This approach enables controlled ionic motion, allowing for the effective formation and rupture of conductive filaments, which in turn enables dependable memristive switching. However, an increase in crystallinity substantially reduces the number of mobile ions present. An important demonstration of this enhancement is evident in thin-film electronic components, where reduced ionic drift contributes to long-lasting performance. Halide perovskite layers, known for their unique charge-carrier mobility, can support these components without the need for elevated processing temperatures. Single-crystal variants exhibit reduced ionic flux, allowing low-stress fabrication and promoting practical application. The achievement of stable operation in ambient conditions would mark a crucial advancement for the broader application of halide-perovskite electronics.

## 4. ABX<sub>3</sub> single crystals

In the absence of grain boundaries, single crystals offer a flawless platform for exploring the fundamental properties of

a material. Compared to polycrystalline elements, halide perovskite single crystals consistently demonstrate fundamentally enhanced metrics, with notable improvements in carrier mobility, diffusion length, and trap density. As a result, single-crystal perovskites have been utilized as active materials in field-effect transistors and photodetectors.<sup>61</sup> For next-generation information technology, high-performance optoelectronic behavior is essential, and these measurements support it. Despite this, the application of these crystals, or their composite derivatives, in resistive-switching memories is still limited, particularly when the active layer maintains a single-crystal structure. Younis *et al.* reported the fabrication and resistive-switching performance of pristine CH<sub>3</sub>NH<sub>3</sub>PbBr<sub>3</sub> (MAPbBr<sub>3</sub>) single crystals, as well as those that include PbS quantum dots.<sup>62</sup> Embedding nanocrystals modifies charge transport within the host lattice, adding extra functionality while preserving structural integrity and maintaining a grain-boundary-free nature. Resistive memory devices were constructed using solution-grown MAPbBr<sub>3</sub> single crystals along with their quantum-dot-modifications. Quantum dots significantly enhanced charge conductance and reduced *I*–*V* hysteresis. Devices utilizing unmodified single crystals exhibited negative differential resistance. At the same time, those incorporating PbS inclusions transitioned *via* filamentary conduction, providing enhanced long-term operational stability and consistently reproducible switching windows throughout extensive electrical cycling.

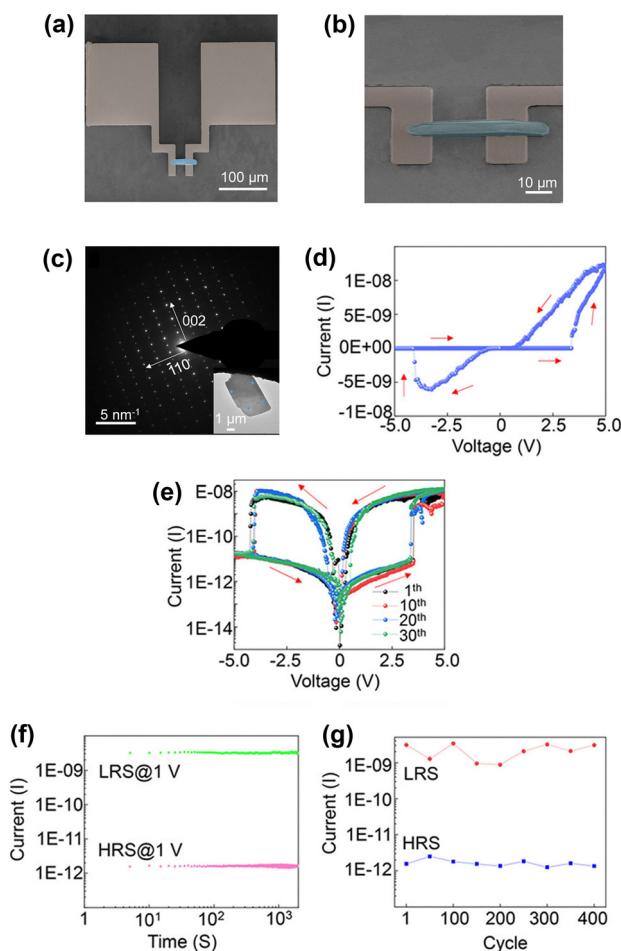

Also, Liu *et al.* demonstrated a low-power resistive switching memory device by assembling single-crystalline CsPbBr<sub>3</sub> on silver (Ag) electrodes.<sup>63</sup> The perovskite film begins to nucleate on the silver electrode and progressively extends until a single crystal connects the two terminals, as illustrated in Fig. 2a. Fig. 2b illustrates that both silver contacts are completely enveloped within the crystal, resulting in a close heterojunction. The absence of visible voids or microcracks confirms the interface's mechanical integrity. In Fig. 2c, the selected area electron diffraction pattern captured at one of four examined locations on the platelet demonstrates its single-crystalline nature. The diffraction array is indexed to the (110) zone of orthorhombic CsPbBr<sub>3</sub>, confirming the structural assignment. The *I*–*V* curve of the device in Fig. 2d exhibits characteristic bipolar, non-volatile resistive switching. The stack, in its unaltered condition, maintains an HRS while conducting approximately 10<sup>–11</sup> A. As the forward bias sweep progresses from 0 to 5 V, there is a notable increase in current, sharply reaching 10<sup>–8</sup> A around 3.4 V, indicating a shift into the LRS. The low state continues until the reverse bias exceeds minus three volts during the next sweep from 0 to –5 V, at which point the structure returns to its initial high level. The elevated condition returns at the start of each new measurement cycle. The *I*–*V* traces gathered across multiple cycles in Fig. 2e align almost exactly with the initial scan, demonstrating consistent switching and remarkable durability. The ON/OFF ratio nearing 10<sup>3</sup> is maintained without noticeable degradation after approximately 10<sup>3</sup> s, as shown in Fig. 2f. The endurance data in Fig. 2g indicates that the disparity between HRS and LRS consistently is around 10<sup>3</sup> across 400 operations.

**Fig. 2** (a) Surface image of CsPbBr<sub>3</sub> single crystal perovskite. (b) Partially enlarged tilted image of the CsPbBr<sub>3</sub> perovskite memory device. (c)  $I$ – $V$  curves for a single crystal CsPbBr<sub>3</sub>-based memory device. (d) 30 cycles of the  $I$ – $V$  curve for a single crystal CsPbBr<sub>3</sub>-based memory device. (e) Retention data of a single crystal CsPbBr<sub>3</sub>-based memory device. (f) Endurance cycles of a single crystal CsPbBr<sub>3</sub>-based memory device. (g) Retention cycles of a single crystal CsPbBr<sub>3</sub>-based memory device. Reproduced with permission.<sup>62</sup> Copyright 2020, American Chemical Society.

Additionally, Li *et al.* utilized a CsPbBr<sub>3</sub> single crystal as the active switching layer in resistive memory devices. Ag/CsPbBr<sub>3</sub>/Ag cells exhibited reliable resistive changes, achieving an exceptionally high ON/OFF ratio exceeding 10<sup>9</sup>, along with a swift response time of 1.8  $\mu$ s.<sup>64</sup> A thorough examination showed that the metal/CsPbBr<sub>3</sub> interface barrier corresponds to Schottky–Mott predictions, suggesting limited Fermi-level pinning. The interface parameter  $S$  for the metal/CsPbBr<sub>3</sub> contact achieved a value of 0.50, indicating a remarkably well-matched junction. This advantageous junction stabilizes the HRS, which subsequently enables the remarkable resistive switching ratio observed, enhancing the potential of perovskite single-crystal platforms for future low-power, high-density memory architectures.

Also, Fernandez-Guillen *et al.* developed the MAPbBr<sub>3</sub> single-crystal perovskite memristor by combining the benefits

of solution-processed thin-film perovskites with those of bulk monocrystals.<sup>65</sup> High structural integrity and exceptional performance were achieved through confined inverse temperature crystallization (ITC), utilizing indium tin oxide (ITO) and poly(triaryl amine) (PTAA) as dual bottom electrodes, with graphite acting directly as the contact. The fabricated memory element exhibited an ON/OFF ratio of 50 and endurance exceeding 10<sup>3</sup> cycles. The *in situ* observation recorded the complete electroforming path, explaining the fundamental processes that regulate resistive switching in halide perovskite structures. A comprehensive examination of temporal kinetic parameters ( $\tau_{\text{kin}}$ ) in the low-frequency domain revealed that changes in ionic transport during electroforming significantly increase current responses by approximately three orders of magnitude. The extracted kinetic profiles showed a decreasing trend. Transition times became shorter over time, indicating a shift from accumulation-controlled behavior to diffusion-dominated operation as the electroforming process progressed. As a result, future device optimization and large-scale integration are supported by a much-expanded understanding of perovskite memristor phenomena.

## 5. 2D layered single crystals

3D perovskites exhibit notable limitations, such as the migration of the methyl-ammonium MA<sup>+</sup> ion, insufficient multilevel storage capability, and poor moisture resistance. Two-dimensional (2D) perovskites featuring alternating organic and inorganic layers exhibit anisotropic charge transport, enhanced humidity tolerance, improved photothermal stability, and significantly diminished ionic migration. Large organic cations incorporated into layered perovskites reduce resistance fluctuations caused by MA<sup>+</sup> movement that affect 3D resistive switching memory devices. Jung *et al.* presented a 2D single-crystal CsPb<sub>2</sub>Br<sub>5</sub> micro sheet resistive switching element fabricated in both vertical and planar configurations.<sup>66</sup> Both geometries show resistive switching. However, the planar device exhibits volatile behavior, while the vertical device demonstrates bipolar switching with retention exceeding 2.5  $\times$  10<sup>4</sup> s, an ON/OFF ratio reaching up to 10<sup>8</sup>, a set voltage under 0.32 V, and multilevel states regulated by the RESET voltage that varies in resistance by approximately two orders of magnitude. The mechanism for switching that regulates the vertical device is centered on the migration of electrochemically active metal species.<sup>67</sup> The structured crystal framework restricts the movement of these mobile ions between cesium layers due to an increased migration barrier in the  $\langle 001 \rangle$  crystallographic direction. The vertically aligned membranes withstand over one thousand switching cycles demonstrate minimal variation from cycle to cycle and maintain their performance even under extended exposure to severe environmental conditions or ongoing electrical stress.

Also, Di *et al.* synthesized the 2D Ruddlesden–Popper phase (PEA)<sub>2</sub>PbI<sub>4</sub> perovskite single crystal using a modified space restriction technique. The Au/(PEA)<sub>2</sub>PbI<sub>4</sub> single crystal/FTO

structures demonstrate remarkable stability in asymmetric bipolar resistive switching.<sup>68</sup> This behavior has been evaluated using multiple voltage sweeps that include both forward and reverse biases. A current ratio of approximately  $10^3$  is achieved with a compliance limit of  $10^{-7}$  A. The significant ratio demonstrates a clear differentiation between low- and high-resistance states, which is essential for non-volatile memory. Experiments conducted with symmetric Au/(PEA)<sub>2</sub>PbI<sub>4</sub> single crystal/Au stacks demonstrate that the symmetry of the electrodes does not affect the observed phenomenon. Throughout the setting process, the *I*-*V* curve transitions from a gradual slope to an abrupt jump, initially linked to electronic effects and subsequently to the formation of conductive filaments due to vacancies. The gradual decrease of SET voltage in Au/(PEA)<sub>2</sub>PbI<sub>4</sub>/FTO devices after numerous switching cycles indicates the inherent internal recovery dynamics associated with the HRS. The random nucleation and rupture of filaments, however, lead to variability in both SET and RESET voltage. The dual switching mechanisms facilitate the programming of Au/(PEA)<sub>2</sub>PbI<sub>4</sub> single crystal/FTO memories at distinct current levels, thus enabling multilevel data storage.

## 6. Double perovskite single crystals

All-inorganic, lead-free double perovskites characterized by the formula  $A_2B^I B^{III}X_6$  offer a promising foundation for long-lasting, eco-friendly devices.<sup>69,70</sup> These lattices emerge when two toxic Pb<sup>2+</sup> ions are simultaneously substituted by a monovalent-trivalent metal pair that exhibits minimal toxicity. Among this family, Cs<sub>2</sub>AgBiBr<sub>6</sub> stands out due to its remarkably extended carrier lifetime, favorable light-effective mass, and low toxicity, which provide significant benefits.<sup>71</sup> Furthermore, remarkable optical absorption and strong stability in ambient air have led to significant investigation of Cs<sub>2</sub>AgBiBr<sub>6</sub> for various optoelectronic applications.

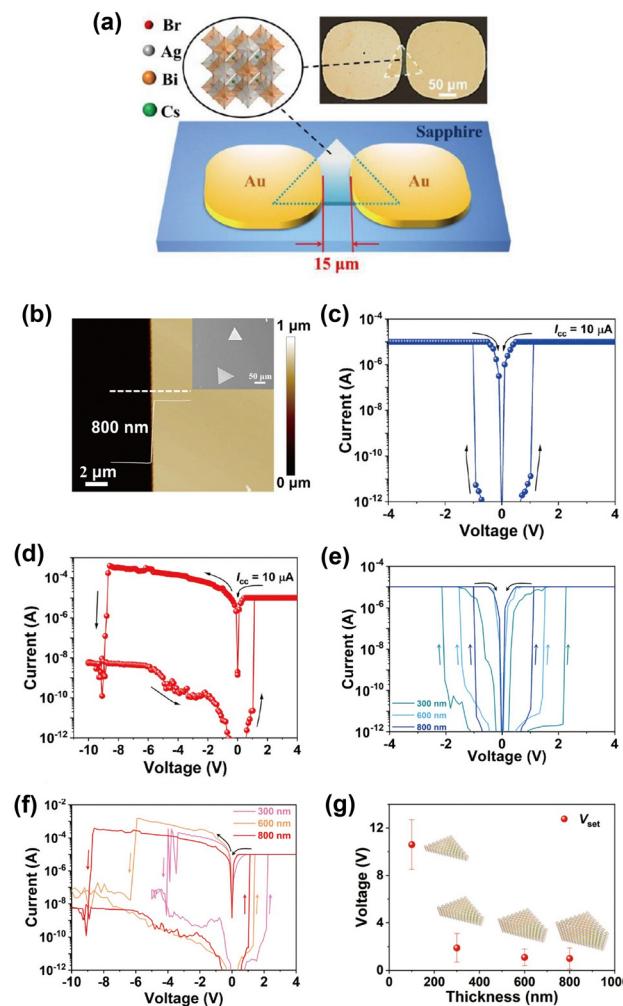

You *et al.* explored a memory device based on single-crystal Cs<sub>2</sub>AgBiBr<sub>6</sub>, which exhibits resistive switching that depends on thickness.<sup>72</sup> Fig. 3a presents a typical as-grown nanoflake that has a thickness of around 800 nm, while the inset optical micrograph illustrates uniform triangular islands measuring 60–80  $\mu$ m. Fig. 3b presents the optical image with a schematic illustration of the device configuration, featuring an active layer that crystallizes in the Cs<sub>2</sub>AgBiBr<sub>6</sub> double-perovskite phase. Two switching modes were identified by successive voltage sweeps; these are resistive switching and threshold switching, which are shown in Fig. 3c and d, respectively. During threshold switching, the change from an HRS to an LRS occurred abruptly at 1.02 V. The following reverse biasing resulted in a symmetric current–voltage response, with a SET potential measured at -0.92 V. In the resistive-switching mode, the device activated at the precise 1.02 V SET level and maintained conductivity until an opposing bias of -8.59 V reverted it to the original HRS. Both modes demonstrated a remarkable ON/OFF current ratio of  $10^7$ , assisted by an extremely low off-state current of  $10^{-12}$  A. To adjust the switching mechanism,

Fig. 3 (a) Illustration of an as-synthesized Cs<sub>2</sub>AgBiBr<sub>6</sub> nanoflake. (b) Schematic diagram and optical microscopy image of the fabricated Cs<sub>2</sub>AgBiBr<sub>6</sub> memory device. (c) The *I*–*V* data of threshold switching in a Cs<sub>2</sub>AgBiBr<sub>6</sub> memory device. (d) The *I*–*V* data of resistance switching in the Cs<sub>2</sub>AgBiBr<sub>6</sub> memory device. (e) *I*–*V* data of 300, 600, and 800 nm thick Cs<sub>2</sub>AgBiBr<sub>6</sub> exhibiting threshold switching (f) *I*–*V* data of Cs<sub>2</sub>AgBiBr<sub>6</sub> with thicknesses of 300 nm, 600 nm, and 800 nm exhibiting resistance switching. (g) The statistically extracted SET voltage was plotted against the thickness of Cs<sub>2</sub>AgBiBr<sub>6</sub>. Reproduced with permission.<sup>70</sup> Copyright 2023, Science China Press and Springer-Verlag GmbH Germany, part of Springer Nature.

functional layers composed of Cs<sub>2</sub>AgBiBr<sub>6</sub> nanoflakes, with thicknesses varying from 70 nm to 800 nm, were utilized. Both threshold behavior (Fig. 3e) and resistive behavior (Fig. 3f) were created by periodic voltage sweeps applied to specimens measuring 300 nm, 600 nm, and 800 nm. Fig. 3g presents a summary of the statistically extracted SET voltages plotted against flake thickness, demonstrating an average decrease in SET from 10.6 V to 1 V as the thickness increased from 100 nm to 800 nm. The observed decrease in SET magnitude indicates that thicker Cs<sub>2</sub>AgBiBr<sub>6</sub> nanoflakes promote the more efficient formation of conductive filaments when subjected to external bias.

## Highlight

Further exploration of lead-free perovskites using a  $\text{Cs}_2\text{AgBi}_6$ -like framework is highly desirable.  $\text{Eu}^{3+}$  has the potential to act as a substitute for  $\text{Bi}^{3+}$  in lead-free double perovskites. Tong *et al.* present results on resistive switching memory devices using the environmentally friendly and air-stable lead-free double perovskite  $\text{Cs}_2\text{AgEuBr}_6$ .<sup>71</sup> A straightforward solution process, combined with vacuum sublimation, produces  $\text{Cs}_2\text{AgEuBr}_6$  crystals, and a memory device was constructed utilizing  $\text{Cs}_2\text{AgEuBr}_6$  films. The analysis images demonstrates that the synthesized  $\text{Cs}_2\text{AgEuBr}_6$  crystals exhibit high crystallinity and smooth morphology. The resulting films exhibit a surface devoid of pinholes and demonstrate excellent crystallization. The memory device using an Au/ $\text{Cs}_2\text{AgEuBr}_6$ /ITO structure features a crossbar architecture designed for straightforward operation and enhanced integration. The Au/ $\text{Cs}_2\text{AgEuBr}_6$ /ITO sandwich-type memory device demonstrates bipolar nonvolatile resistive memory characteristics, achieving an ON/OFF ratio nearing  $10^4$  and a retention duration of 12 000 s.

## 7. Single crystal for artificial synapses

Small n 2D perovskites exhibit anisotropic charge transport, which significantly decreases along the out-of-plane axis. This characteristic makes them especially attractive for resistive memories that can operate at ultra-low program currents. Tian *et al.* introduced a resistive memory device featuring ultra-low operating current using a mechanically exfoliated 2D layered perovskite single crystal.<sup>73</sup> A synthetic protocol produced 2D  $\text{PEA}_2\text{PbBr}_4$  perovskite single crystals that displayed a broadband gap of around 2.9 eV. The crystals were exfoliated into thin layers and subsequently incorporated into a vertical device stack consisting of graphene, 2D perovskite, and Au to investigate the electrical behavior within resistive memory architectures. Following a SET process, a filament approximately 20 nm diameter emerged within the 2D perovskite. The elemental density profile mapping confirmed a mechanism that entails the migration of  $\text{Br}^-$ , leading to the formation of the filament. Monte Carlo simulations observed  $\text{Br}^-$  and vacancy drift throughout filament formation. Due to the significant reduction of charge transport in the out-of-plane direction of the 2D perovskite film, the off current achieved a 10 pA, allowing for device operation while maintaining an ON/OFF ratio of 10. The operating current of 10 pA indicates the lowest value recorded to date for any resistive memory element. The remarkably low program current allowed the resistive memory to achieve a 400 fJ per spike in synaptic switching energy, precisely in line with the metabolic consumption observed in biological synapses. Both short-term potentiation and long-term potentiation were observed in 2D perovskite synaptic cells, suggesting that 2D perovskites may function as vital elements for neuromorphic design.

Also, Cheng *et al.* demonstrated synapses using reversible photo-induced phase transition (PIPT) in an all-inorganic single-crystal  $\text{CsPbBr}_3$  perovskite. All optical synapses using

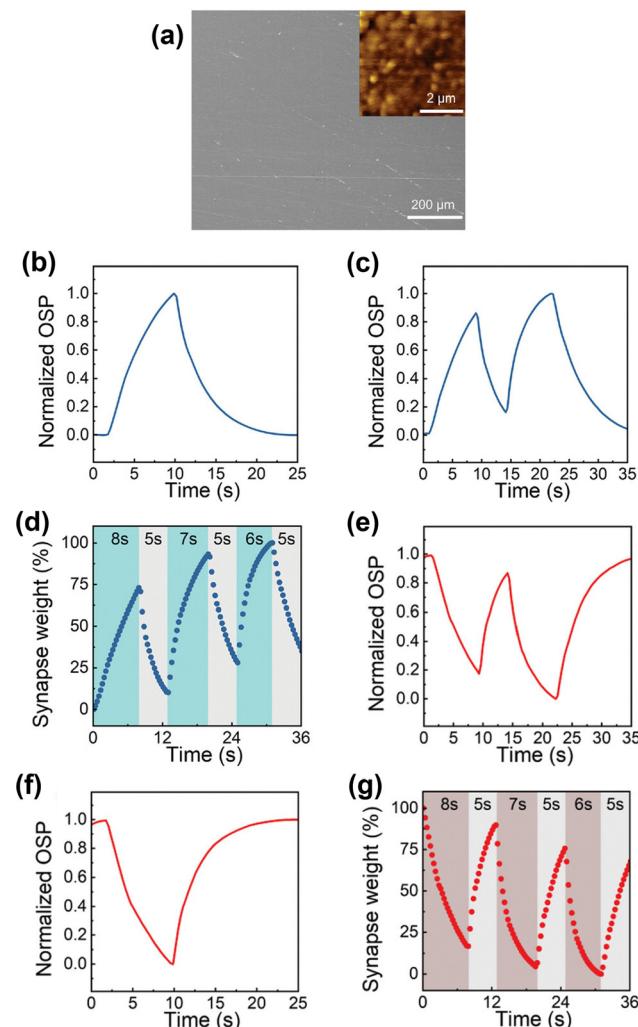

Fig. 4 The behaviors of excitatory synapses are fundamentally rooted in the artificial synapse. (a) Surface of  $\text{CsPbBr}_3$  single crystal. (b) Characteristics of optical EPSPs. (c) A sequence of light pulses initiates PPF, each lasting 8 s, with a 5 s interval between them. (d) The behavior associated with forgetting and learning. And the inhibitory synaptic behaviors are derived from the artificial synapse. (e) Characteristics of optical IPSP. (f) A sequence of light pulses activates the PPF, each lasting 8 seconds, with a 5 s interval between them. (g) The behavior associated with forgetting and learning. Reproduced with permission.<sup>72</sup> Copyright 2024, Wiley-VCH GmbH.

reversible photo-induced phase transitions (PIPT) in all inorganic single-crystal  $\text{CsPbBr}_3$  perovskites were demonstrated.<sup>74</sup> The crystal had a change from an orthorhombic to a tetragonal configuration when encouraged by photons above the bandgap, resulting in a notable modification in the observable birefringence response. Fig. 4a presents the surface morphology analyzed, showing a flat, smooth film. Fig. 4b illustrates an optical excitatory postsynaptic potential (EPSP) response from the artificial synapse, reported following activation by a violet light pulse at 405 nm, delivering 30 mW. Synaptic plasticity serves as the fundamental neurochemical basis for learning and memory in neuroscience, with the understanding that human brains exhibit this phenomenon through mechanisms known as

short-term plasticity (STP) and long-term plasticity (LTP). Fig. 4c demonstrated that 2 consecutive presynaptic optical spikes, spaced 5 s apart, resulted in a postsynaptic peak where the amplitude of the second spike was 13.6% greater. Fig. 4d illustrates the learning-forgetting rehearsal sequence, selected as a representative of long-term potentiation generated by the artificial synapses. The cycle of learning, forgetting, and relearning commenced with a light pulse at 405 nm, lasting 8 s. This pulse enhanced the optical EPSP amplitude, subsequently increasing synaptic weight during the learning phase. Following a 5 s interval of forgetting, a rehearsal light pulse was used for 7 s, succeeded by a similar interval of forgetting. Ultimately, a subsequent light pulse of 6 s was processed once again. Through multiple rehearsal cycles, the weight of retention increased significantly, moving from 72.9% to 93.2% and ultimately reaching 100.0%. In contrast, the weight of forgetting escalated from 10.3% to 28.1% and then to 35.2%. Inhibitory postsynaptic power (IPSP) exemplifies a distinct synaptic behavior occurring when presynaptic neurons release inhibitory neurotransmitters following stimulation. These molecules then bind to receptors on the postsynaptic neuron, leading to a specific response. Fig. 4e illustrates the characteristic optical IPSP behavior demonstrated by the device. Furthermore, the characteristics of paired-pulse facilitation at inhibitory synapses were activated by 2 successive presynaptic spikes, as demonstrated in Fig. 4f. Two spikes, each providing 30 mW for a duration of 8 s, were administered to the artificial synapse, with a 5 s interval between them. The following IPSP response demonstrated a reduced intensity in comparison to the initially recorded value. The features stated for the inhibitory artificial synapse successfully promoted the simulation of comprehensive forgetting learning behavior when subjected to light pulse stimulation, a result depicted in Fig. 4g. In conclusion, the all-optical synapse developed from  $\text{CsPbBr}_3$  single crystal presents promising opportunities for future optical neuromorphic computing systems.

The single-crystal halide perovskites are set to provide low-energy synaptic devices that integrate electrical and optical functions without compromising performance. Continuous progress in crystal engineering and photonic integration is anticipated to drive these materials toward the development of wafer-scale neuromorphic circuits tailored for the next generation of edge intelligence.

## 8. Conclusion

Halide perovskite single crystals have advanced significantly for the development of next-generation memory and neuromorphic circuits. The lack of grain boundaries, coupled with decreased trap populations, has resulted in resistive switching, multilevel programmability, and synaptic behavior, all while making low energy consumption. Lead-free double perovskites and layered 2D perovskites expand the conventional  $\text{ABX}_3$  lattice by improving environmental compatibility, structural anisotropy, and thermal durability, thus broadening the design

possibilities for eco-conscious electronics. Significant challenges continue to demand focus. Industrial production needs to shift to wafer-scale growth while maintaining ultralow defect densities that are essential for performance. Contact stacks require precise band and ion alignment to reduce electrochemical drift over prolonged duty cycles. Consistent performance in both air and under conditions of heat or mechanical stress is essential. To lead predictive models for filament nucleation and vacancy transport, visualization of coupled ionic and electronic motion will be necessary for future advancement. To adjust activation barriers and switching thresholds without compromising carrier mobility, dimensional confinement, lattice strain engineering, and careful doping offer levers. Sneak currents can be reduced, and peripheral logic is made simpler with hierarchical topologies where perovskite selectors divide perovskite memory units. The translation of observed synaptic behaviors into densely interconnected networks will require algorithms that embrace conductance volatility instead of reducing it. Halide perovskite single crystal technology could lead the way in low-power storage, and adaptive sensing if these issues are successfully resolved.

## Author contributions

Hyojung Kim: conceptualization, writing – original manuscript, writing – review & editing, funding acquisition.

## Conflicts of interest

There are no conflicts to declare.

## Data availability

No primary research results, software or code have been included, and no new data were generated or analysed as part of this review.

## Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (RS-2025-00554803).

## References

- 1 S. Kundu, P. B. Ganganaik, J. Louis, H. Chalamalasetty and B. P. Rao, *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, 2022, **30**, 755–768.

- 2 Y. Cho, D. Kim, J. H. Seo, J. H. Chung, Z. Park, K. C. Kwon, J. Ko, T. W. Ha, J. Lee, G. Kim, S. Ro, H. Kim, C. Lee, K. Lee, Y. Shim and D. Cho, *Adv. Sci.*, 2025, 2501293.

- 3 Y.-J. Son, S.-W. Kim, H.-M. Kim, H. Kim, B. Chu and D.-Y. Jeong, *Materials*, 2025, **18**, 1427.

- 4 H. Kim, G. Veerappan and J. H. Park, *Electrochim. Acta*, 2014, **137**, 164–168.

## Highlight

5 H. Kim, G. Veerappan, D. H. Wang and J. H. Park, *Electrochim. Acta*, 2016, **187**, 218–223.

6 H. Kim, B. Kang and C. Moon, *Micromachines*, 2024, **15**, 334.

7 D. Shin, J. Lee, H. Pyo, S. Lee, H. Kang, H. Kim and C. W. Moon, *J. Korean Ceram. Soc.*, 2025, DOI: [10.1007/s43207-025-00509-x](https://doi.org/10.1007/s43207-025-00509-x).

8 J. Lee, H. Kim, M. Hilal and Z. Cai, *J. Mater. Sci.: Mater. Electron.*, 2024, **35**, 1421.

9 J. Lee, H. Kim, M. Hilal and Z. Cai, *Solid State Sci.*, 2024, **156**, 107683.

10 J. Lee, H. Kim, M. Hilal and Z. Cai, *J. Electroceram.*, 2024, **52**, 283–296.

11 G. Li, M. Hilal, H. Kim, J. Lee, Z. Chen, B. Li, Y. Cui, J. Hou and Z. Cai, *Coatings*, 2024, **14**, 1590.

12 G. Li, J. Hou, M. Hilal, H. Kim, Z. Chen, Y. Cui, J.-H. Kim and Z. Cai, *Sensors*, 2024, **24**, 6839.

13 H. Yuan, M. Hilal, Y. Ali, H. M. U. Ayub, Z. Cai, H. Kim, W. Zhang, A. A. Khan, H. S. Abdo, I. A. Alnaser, Y. Hwang and J. I. Han, *Surf. Interfaces*, 2025, **58**, 105888.

14 Z. Song, M. Hilal, H. S. Abdo, Z. Cai, H. Kim and J. I. Han, *J. Ind. Eng. Chem.*, 2025, **144**, 691–699.

15 M. Hilal, Y. Ali, H. Fayaz, Z. Cai, H. Kim, H. S. Abdo and I. A. Alnaser, *Ceram. Int.*, 2025, DOI: [10.1016/j.ceramint.2025.04.343](https://doi.org/10.1016/j.ceramint.2025.04.343).

16 H. Yuan, M. Hilal, Y. Ali, H. S. Abdo, Z. Cai, H. Kim, U. Ullah, H. Fayaz, W. Xie and J. I. Han, *Surf. Interfaces*, 2024, **54**, 105266.

17 M. Hilal, Y. Ali, Z. Cai, H. Kim, H. S. Abdo, I. A. Alnaser and Y. Hwang, *Ceram. Int.*, 2025, **51**, 16246–16256.

18 M. Hilal, Y. Ali, Z. Cai, H. Kim, H. S. Abdo, I. A. Alnaser, Y. Hwang and J. I. Han, *Surf. Interfaces*, 2025, **60**, 106097.

19 M. Hilal, Y. Ali, Z. Cai, H. Kim, H. S. Abdo, I. A. Alnaser and Y. Hwang, *Sens. Actuators, A*, 2025, **388**, 116479.

20 F. Wang, Q. Liu, J. Xia, M. Huang, X. Wang, W. Dai, G. Zhang, D. Yu, J. Li and R. Sun, *Adv. Mater. Technol.*, 2023, **8**, 2201186.

21 S. Ötenkaya and R. Ünal, *J. Korean Ceram. Soc.*, 2025, **62**, 412–436.

22 X. Chen, W. Chen, J. Xu and M. Chen, *Electron. Mater. Lett.*, 2025, **21**, 613–625.

23 H. J. Jung, *Electron. Mater. Lett.*, 2025, **21**, 32–40.

24 A. Usman, A. Ayyaz, Q. Mahmood, N. Algethami, S. A. Mahmoud, I. Boukhris and A. K. Alqorashi, *J. Korean Ceram. Soc.*, 2025, **62**, 526–538.

25 J. S. Han, Q. Van Le, J. Choi, K. Hong, C. W. Moon, T. L. Kim, H. Kim, S. Y. Kim and H. W. Jang, *Adv. Funct. Mater.*, 2018, **28**, 1705783.

26 H. Kim, J. S. Han, J. Choi, S. Y. Kim and H. W. Jang, *Small Methods*, 2018, **2**, 1700310.

27 W. Zhang, G. E. Eperon and H. J. Snaith, *Nat. Energy*, 2016, **1**, 16048.

28 Y. Ha, Y. Son, D. Paik, K.-H. Hong and H. Kim, *Electron. Mater. Lett.*, 2023, **19**, 588–597.

29 Y. Selmani, H. Labrim and L. Bahmad, *J. Korean Ceram. Soc.*, 2024, **61**, 189–200.

30 H. Kim, M.-J. Choi, J. M. Suh, J. S. Han, S. G. Kim, Q. Van Le, S. Y. Kim and H. W. Jang, *NPG Asia Mater.*, 2020, **12**, 21.

31 S. D. Stranks and H. J. Snaith, *Nat. Nanotechnol.*, 2015, **10**, 391–402.

32 H. Lee, D. Gelija, U. Kim, J. Lee and W. J. Chung, *J. Korean Ceram. Soc.*, 2024, **61**, 482–491.

33 I. Hamideddine, N. Tahiri, O. El Bounagui and H. Ez-Zahraouy, *J. Korean Ceram. Soc.*, 2022, **59**, 350–358.

34 M. Javed, M. Benkraouda and N. Amrane, *Int. J. Energy Res.*, 2022, **46**, 18588–18608.

35 A. Alhashmi, M. B. Kanoun and S. Goumri-Said, *Materials*, 2023, **16**, 2657.

36 J. Bisquert, A. Guerrero and C. Gonzales, *ACS Phys. Chem. Au*, 2021, **1**, 25–44.

37 G. An, L. Wang, J. Gao and R. Wang, *Sci. Rep.*, 2019, **9**, 1563.

38 H. M. Cho and H. W. Jang, *Electron. Mater. Lett.*, 2025, **21**, 291–310.

39 H. Kim, D. Hyun, M. Hilal, Z. Cai and C. W. Moon, *Electronics*, 2024, **13**, 3572.

40 H. Kim, M. Choi, J. M. Suh, Y.-S. Shim, I. H. Im, D. Hyun, S. J. Yang, Z. Cai, M. Hilal, M. G. Lee, C. W. Moon, S. Y. Kim and H. W. Jang, *Mater. Sci. Semicond. Process.*, 2024, **182**, 108718.

41 Z. Wang, H. Xu, X. Zhao, Y. Lin, L. Zhang, J. Ma and Y. Liu, *Phys. Status Solidi A*, 2015, **212**, 2255–2261.

42 S. G. Kim, Q. Van Le, J. S. Han, H. Kim, M. Choi, S. A. Lee, T. L. Kim, S. B. Kim, S. Y. Kim and H. W. Jang, *Adv. Funct. Mater.*, 2019, **29**, 1906686.

43 H. Kim, J. S. Han, S. G. Kim, S. Y. Kim and H. W. Jang, *J. Mater. Chem. C*, 2019, **7**, 5226–5234.

44 J. S. Han, Q. Van Le, H. Kim, Y. J. Lee, D. E. Lee, I. H. Im, M. K. Lee, S. J. Kim, J. Kim, K. J. Kwak, M. Choi, S. A. Lee, K. Hong, S. Y. Kim and H. W. Jang, *Small*, 2020, **16**, 2003225.

45 H. Kim, J. S. Kim, J. Choi, Y.-H. Kim, J. M. Suh, M.-J. Choi, Y.-S. Shim, S. Y. Kim, T.-W. Lee and H. W. Jang, *ACS Appl. Mater. Interfaces*, 2024, **16**, 2457–2466.

46 S. G. Kim, J. S. Han, H. Kim, S. Y. Kim and H. W. Jang, *Adv. Mater. Technol.*, 2018, **3**, 1800457.

47 S. Lee, H. Kim, D. H. Kim, W. Bin Kim, J. M. Lee, J. Choi, H. Shin, G. S. Han, H. W. Jang and H. S. Jung, *ACS Appl. Mater. Interfaces*, 2020, **12**, 17039–17045.

48 H. Kim, I. H. Im, D. Hyun, M. Hilal, Z. Cai, S. J. Yang, Y.-S. Shim and C. W. Moon, *J. Korean Ceram. Soc.*, 2025, **62**, 397–411.

49 J. S. Han, Q. Van Le, J. Choi, H. Kim, S. G. Kim, K. Hong, C. W. Moon, T. L. Kim, S. Y. Kim and H. W. Jang, *ACS Appl. Mater. Interfaces*, 2019, **11**, 8155–8163.

50 H. Kim, K. A. Huynh, S. Y. Kim, Q. Van Le and H. W. Jang, *Phys. Status Solidi RRL*, 2020, **14**, 1900435.

51 A. Ummadisingu, S. Meloni, A. Mattoni, W. Tress and M. Grätzel, *Angew. Chem., Int. Ed.*, 2021, **60**, 21368–21376.

52 D. Yang, W. Ming, H. Shi, L. Zhang and M.-H. Du, *Chem. Mater.*, 2016, **28**, 4349–4357.

53 S. Reichert, Q. An, Y.-W. Woo, A. Walsh, Y. Vaynzof and C. Deibel, *Nat. Commun.*, 2020, **11**, 6098.

54 A. Kumar, S. K. Gupta, B. P. Dhamaniya, S. K. Pathak and S. Karak, *Mater Today Energy*, 2023, **37**, 101400.

55 M. Jagadeeswararao, R. E. Galian and J. Pérez-Prieto, *Nanomaterials*, 2023, **14**, 94.

56 P. Knauth and H. L. Tuller, *J. Am. Ceram. Soc.*, 2002, **85**, 1654–1680.

57 H. Baishya, R. Das Adhikari, M. J. Patel, D. Yadav, T. Sarmah, M. Alam, M. Kalita and P. K. Iyer, *J. Energy Chem.*, 2024, **94**, 217–253.

58 N. Phung, A. Al-Ashouri, S. Meloni, A. Mattoni, S. Albrecht, E. L. Unger, A. Merdasa and A. Abate, *Adv. Energy Mater.*, 2020, **10**, 1903735.

59 J. Siekmann, S. Ravishankar and T. Kirchartz, *ACS Energy Lett.*, 2021, **6**, 3244–3251.

60 R. Gegevičius, M. Franckevičius and V. Gulbinas, *Eur. J. Inorg. Chem.*, 2021, 3519–3527.

61 J. Y. Park, Y. H. Lee, H. Kim and L. Dou, *J. Appl. Phys.*, 2023, **134**, 060901.

62 A. Younis, L. Hu, P. Sharma, C. Lin, Y. Mi, X. Guan, D. Zhang, Y. Wang, T. He, X. Liu, B. Shabbir, S. Huang, J. Seidel and T. Wu, *Adv. Funct. Mater.*, 2020, **30**, 2002948.

63 J. Liu, J. Jin, Z. Yang, J. Cai, J. Yue, J. Impundu, H. Liu, H. Wei, Z. Peng, Y. J. Li and L. Sun, *ACS Appl. Mater. Interfaces*, 2020, **12**, 31776–31782.

64 L. Li, Y. Chen, C. Cai, P. Ma, H. Ji and G. Zou, *Small*, 2022, **18**, 2103881.

65 I. Fernandez-Guillen, C. A. Aranda, P. F. Betancur, M. Vallés-Pelarda, C. Momblona, T. S. Ripolles, R. Abargues and P. P. Boix, *Adv. Electron. Mater.*, 2024, **10**, 2300475.

66 U. Jung, D.-S. Woo, S. Kim, Z. Tan and J. Park, *Nano Res.*, 2025, **18**, 94907023.

67 M. Smacchia, C. Gonzales, S. Milita, L. Maserati, D. Cavalcoli and A. Guerrero, 2025, preprint.

68 J. Di, Z. Lin, J. Su, J. Wang, J. Zhang, S. Liu, J. Chang and Y. Hao, *IEEE Electron Device Lett.*, 2021, **42**, 327–330.

69 Ihtisham-ul-haq, M. I. Khan, L. Ben Farhat, H. Elhouiche and R. P. Patil, *J. Korean Ceram. Soc.*, 2025, 359–369.

70 H. Jebari, I. Hamideddine and H. Ez-Zahraouy, *J. Korean Ceram. Soc.*, 2024, **61**, 599–604.

71 T. Tong, C. Liu, J. Xu, H. Min, S. Chen, Y. Lyu and C. Lyu, *J. Mater. Chem. C*, 2023, **11**, 4946–4952.

72 Q. You, F. Huang, F. Fang, J. Zhu, Y. Zheng, S. Fang, B. Zhou, H. Li, C. Han and Y. Shi, *Sci. China Mater.*, 2023, **66**, 241–248.

73 H. Tian, L. Zhao, X. Wang, Y.-W. Yeh, N. Yao, B. P. Rand and T.-L. Ren, *ACS Nano*, 2017, **11**, 12247–12256.

74 P. Cheng, Z. Liu, J. Zhou, R. Kang, X. Wang, X. Li, X. Zhao, J. Zhao and Z. Zuo, *Adv. Opt. Mater.*, 2024, **12**, 2303306.