# **Materials Advances**

View Article Online PAPER

electrochemical aspects†

Cite this: Mater. Adv., 2024, 5. 4209

> Fei Qin, ‡a Yuxuan Zhang, ‡a Zigi Guo, b Tae Joon Park, hongsik Park, bd Chung Soo Kim, e Jeongmin Park, e Xingyu Fu, a Kwangsoo No, f Han Wook Song, g Xiulin Ruan<sup>b</sup> and Sunghwan Lee \*\*

High on/off ratio SiO<sub>2</sub>-based memristors for

neuromorphic computing: understanding the

switching mechanisms through theoretical and

Memristors have emerged as promising elements for brain-inspired computing applications, yet the understanding of their switching mechanisms, particularly in valence change memristors, remains a topic of ongoing debate. We report on the  $SiO_2$ -based memristors, demonstrating a high on/off ratio (>10 $^5$ ). Particularly, this study aims to enhance the fundamental understanding of switching behaviors and mechanisms. Our approach involved an extensive investigation using finite element analysis to provide visual insights into the conductive path evolution in these memristors over the set/reset bias cycle. Electrochemical impedance spectroscopy experimentally validated the theoretical investigations by interpreting the switching behavior through the lens of the equivalent circuit. In addition, we evaluated synaptic characteristics and incorporated them into neural networks for image recognition tasks with MNIST and fashion MNIST datasets. Our comprehensive exploration of both the underlying principles and potential applications is of practical relevance to studies that aim to realize and implement SiO<sub>2</sub>based memristors in neuromorphic computing.

Received 18th December 2023, Accepted 30th March 2024

DOI: 10.1039/d3ma01142a

rsc.li/materials-advances

#### Introduction

The silicon (Si) microelectronics research and industry promisingly consider memristors a promising contender in emerging

memory technologies. This increasing interest in memristors is attributed to their potential performance advantages, including lower power consumption and higher scalability, compared with other non-volatile memory technologies such as FeRAM (ferroelectric RAM) and MRAM (magnetoresistive RAM). These distinct characteristics of memristors position them as a compelling choice for implementing in-memory computing, offering a path to challenge and potentially revolutionize traditional Von Neumann architectures.

A wide range of oxide materials, from semiconductors to high-k materials, including InGaZnO, 2 SiO2, 3 HfO2, 4 and TaOx, 5 have been reported to serve as switching layers in memristors. The majority of materials utilized in memristors are either expensive to grow or only partially compatible with the prevalent Si-based complementary metal-oxide semiconductor (CMOS) manufacturing process. Historically, SiO2 has been one of the most extensively researched dielectric materials, largely due to its direct growth capability out of Si.<sup>6</sup> However, much of this research has been centered around the destructive and irreversible dielectric breakdown for traditional CMOS and very large-scale integration (VLSI) technologies. Recently, a shift in focus has been noted within the memristor field, as SiO<sub>2</sub> has demonstrated reversible soft breakdown behaviors, also known as resistive switching.3,8 This has prompted an

<sup>&</sup>lt;sup>a</sup> School of Engineering Technology, Purdue University, West Lafayette, IN 47907, USA. E-mail: sunghlee@purdue.edu

<sup>&</sup>lt;sup>b</sup> School of Mechanical Engineering, Purdue University, West Lafayette, IN 47907,

<sup>&</sup>lt;sup>c</sup> School of Materials Engineering, Purdue University, West Lafayette, IN 47907, USA <sup>d</sup> School of Electronic and Electrical Engineering, Kyungpook National University, Daegu 41566, Republic of Korea

<sup>&</sup>lt;sup>e</sup> Analysis Technical Center, Korea Institute of Ceramic Engineering and Technology, Iiniu, Gyeongsangnam-do 52851, Republic of Korea

f Department of Materials Science and Engineering, KAIST, Daejeon 34141, Republic

g Center for Mass and Related Quantities, Korea Research Institute of Standard and Science, Daejeon 34113, Republic of Korea

<sup>†</sup> Electronic supplementary information (ESI) available: CV measurements on devices with different thickness of SiO<sub>2</sub>, retention characteristics on 5 nm SiO<sub>2</sub> memristor, the electric field distribution within 5 nm SiO2 switching layer at different stages, I-V DC sweeping characteristics of different thicknesses of SiO2 switching layer, the oxygen vacancy evolution and the electric field distribution of memristor with 10 nm SiO2 switching layer at different stages, gradual switching behavior of the 5 nm SiO2 memristor, physical modeling detail, and image processing detail. See DOI: https://doi.org/10.1039/d3ma01142a

<sup>‡</sup> F. Q. and Y. Z. contributed equally to this work.

Paper

increase in interest and research into the potential applications of SiO<sub>2</sub> within the realm of memristor technologies.<sup>9</sup>

Memristors based on SiO2 have been investigated and reported with an achieved performance of on/off ratio of 10<sup>2</sup>-10<sup>5</sup>.8b,10 Bilayer structure (SrTiO<sub>3</sub>/SiO<sub>2</sub><sup>11</sup>) was demonstrated for realizing stable switching through engineering different ion transport rates in these two layers where the role of SrTiO3 is to confine filament growth. Nanorods of SiO2 were also investigated to lower the firing energy for an artificial neuron. 12 The use of columnar growth in silicon oxide was leveraged to create defect-rich sites at the column edges, resulting in low variability. 10b To further advance the development, it is crucial to fundamentally understand SiO2-based memristors' switching mechanisms, which in turn will provide insightful engineering criteria to address the challenging issues above. Thus far, the oxidation-reduction (redox)-based switching mechanisms have been suggested and categorized into two mechanisms, depending on the composition of the conductive filaments: electrochemical metallization mechanism (ECM) and vacancy-associated valence change mechanism (VCM). In an ECM device, Cu or Ag is widely chosen as an active electrode which can be partially oxidized and then reduced to form the metallic filaments. 13 On the other hand, the conductive path of VCM devices relies on the generation and accumulation of oxygen vacancies.14 The evolution of conductive filaments in the ECM memristors has been evidenced through transmission electron microscopy (TEM),15 and this work enhanced understanding of the switching behavior of ECM and PCM memristors.14 However, the direct visualization of conductive filaments in VCM-based memristors is rarely reported due to the technical difficulties, 16 for example in TEM characterizations, of low image contrast between oxygen-rich and -deficient regions in TEM characterizations, which makes the VCM switching mechanism remain controversial.<sup>17</sup>

In this work, we selected SiO<sub>2</sub> as the switching element for memristor applications. To solely limit the contributing charge carriers to oxygen vacancies for the switching behavior, an inert metal Pd was employed as the top electrode. The dynamic evolution of oxygen vacancy conductive filaments in the SiO<sub>2</sub>based memristors was mechanistically visualized by a numerical solver, which delineates a selective growth process and the inhibition effect exerted on filaments nearby the established dominant paths. The equivalent circuit interpretation from non-destructive electrochemical impedance spectroscopy (EIS) measurements supplementarily corroborated our theoretical understanding about the switching mechanism. Importantly, our SiO2-based memristor can be considered as the weights in artificial neural networks (ANNs) because it exhibited multiconductance phenomena in response to pulse train stimuli. Given these synaptic characteristics, our SiO2-based memristors were incorporated into a neural network for image processing tasks, benchmarking with MNIST and fashion MNIST datasets. Our fundamental studies and concept validation may propel advances in SiO<sub>2</sub>-based memristors, pushing the boundaries towards real-world neuromorphic computing applications.

### Results and discussion

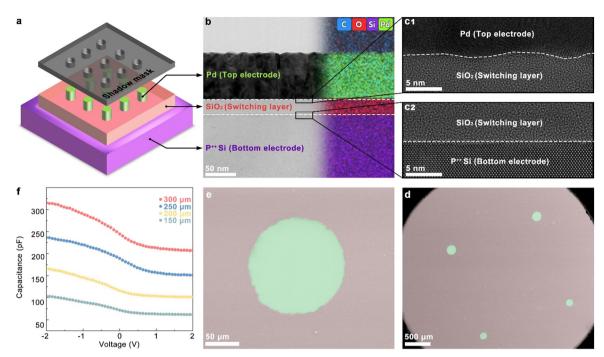

Fig. 1a is a schematic illustration of a SiO<sub>2</sub>-based memristor in a vertical configuration. The top electrodes were defined using in situ shadow masks during the fabrication, of which the circular pattern diameters vary from 150 to 300 µm with a 50 μm increment. A cross-sectional high-angle-annular darkfield (HAADF) TEM micrograph of the SiO<sub>2</sub> memristor is falsecolored and exhibited in Fig. 1b. A vertical memristor structure consisting of top (Pd,  $\sim 100$  nm) and bottom (heavily-doped Si) electrodes and switching layer (SiO2, ~20 nm) between the electrodes was clearly identified. An associated energydispersive X-ray spectroscopy (EDS) mapping image in Fig. 1b indicates the major elements of each layer of the memristor, indicating a clear interface between layers without interdiffusion. In the high-resolution TEM images (Fig. 1c), distinct morphological features are evident: the TE/SiO2 interface exhibits protrusions approximately 1 nm in size (Fig. 1c1), while the SiO<sub>2</sub>/BE interface is characterized by a notably flat surface (Fig. 1c2). A false-colored SEM image of the Pd top electrodes with diameters of 200 and 150 µm is displayed in Fig. 1d and a magnified image of a 150 µm Pd top electrode is shown in Fig. 1e. The typical vertical memristor structure is technically the same as that of a capacitor and particularly the characteristics of the high-resistance state are governed by the dielectric performance of the switching layer (SiO<sub>2</sub> in this study). To evaluate the dielectric property, as an initial figure of merit, of the switching layer and the devices, capacitance-voltage (CV) measurements were conducted on SiO2-based memristors as a function of switching layer thicknesses and top electrode size within a voltage range from -2 V to 2 V under 1 MHz. The CV results from the 5 nm SiO2 switching layer are summarized in Fig. 1f. Overall, the capacitance of 5 nm SiO<sub>2</sub>-based memristors is at  $10^{-10}$  F level. From the C-V measurements, the capacitance densities of the SiO<sub>2</sub> switching layers with different TE sizes are comparable to each other, approximately 3.5-4.2 fF  $\mu$ m<sup>-2</sup>. The relative permittivity extracted from the resulting sputtered SiO<sub>2</sub> is 3.3, which is close to the reference values 3.7-3.9. The slightly lower value may be resulted from the room temperature sputtering condition and mild annealing temperature (550 °C), compared with the reference values obtained from high temperature (1000-1200 °C) thermal oxidation.

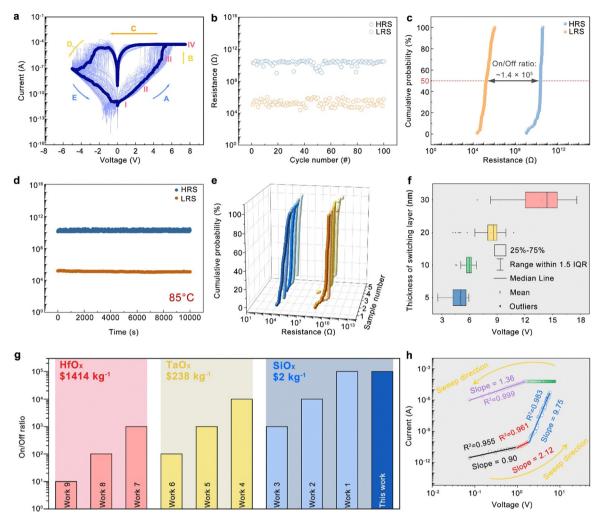

The electrical characteristics of SiO<sub>2</sub>-based memristors were examined by cyclic DC sweeping. The electrical biases were always applied on the palladium top electrode and the P++ Si bottom electrode was grounded. The sweeping bias ranged from -5 V to 7.5 V with a starting voltage of 0 V, and a compliance current  $(I_{cc})$  was set at 60  $\mu$ A during the positive sweeping. Fig. 2a shows the current-voltage (I-V) property of a 5 nm-SiO<sub>2</sub> switching layer memristor, including consecutive 100 cycles of DC sweeping curves with the same measurement parameters. The I-V sweeping curves appear as a butterfly shape which is a typical pattern for a bipolar memristor.<sup>21</sup> The bipolar switching resulted from the formation (with positive biases) and annihilation (with negative biases) of the filament, caused by field induced oxygen vacancy migration

Fig. 1 Pd/SiO<sub>2</sub>/P<sup>++</sup>Si memristors: (a) schematic illustration of device structure of SiO<sub>2</sub>-based memristor with Pd TE and heavily-doped Si BE. (b) A falsecolored cross-sectional HAADF-TEM micrograph, and associated EDS elemental mapping of a Pd/SiO<sub>2</sub>/P<sup>++</sup>Si memristor. (c) High resolution TEM images to reveal the morphology of (c1) the TE/SiO<sub>2</sub> interface, showing  $\sim$ 1 nm protrusions and (c2) the flat SiO<sub>2</sub>/BE interface. (d) A false-colored SEM plan-view image of the top electrodes with diameters of 200  $\mu$ m and 150  $\mu$ m, and (e) an extended image for the typical size 150  $\mu$ m. (f) C-V measurements at 1 MHz for 5 nm-thick SiO<sub>2</sub>-based memristor with various TE diameters (300, 250, 200 and 150 μm).

with alternating opposite directions of bias application. 19 This is different from the unipolar switching which has been proposed, where the annihilation of the filament is achieved by Joule heating using a consistent bias direction. 20 When the bias increased from 0 V to 7.5 V, abrupt current jumps were observed which indicates a conduction filamentary SET process, i.e., a transition from high resistance state (HRS) to low resistance state (LRS). And the transitions (turn on) mostly happened at a voltage ranging from 4 V to 6 V. The LRS was maintained during the sweeping from 7.5 V to 0 V and subsequent 0 V to negative bias. It should be noted that the turn-on voltage of the first cycle of DC sweeping was  $\sim$ 6 V which was applied on the top electrode (Pd). From the SET voltage statistics distribution in Fig. 2f (bottom for 5 nm thick SiO<sub>2</sub>), it is on the maximum side, but not too far from the medium/mean value of  $\sim 5$  V. Thus, we can consider our device to be a near-forming free device, which is defined as the initial SET voltage of the device is similar to the subsequent SET voltages.21 During the negative voltage sweeping, a current level drop was observed which means the cell was turned back to HRS, a RESET process was finished (i.e., off state). The current values at a read voltage of 0.3 V for each sweeping cycle were extracted from the I-V curves, then converted to resistance values and plotted as resistance versus cycle number to yield the endurance performance of the device exhibited in Fig. 2b. The results demonstrate that no deterioration in HRS and LRS during continuous cycling was observed, indicating reasonable endurance of the SiO2-based memristor. A large memory

window, *i.e.*, on/off ratio, is clearly observed as high as  $>10^5$ . To characterize the on/off ratio more quantitatively, the cycleto-cycle statistical distributions of HRS and LRS are demonstrated in Fig. 2c. At the cumulative probability of 50%, the notable high on/off ratio is further validated as  $\sim 1.4 \times 10^5$ . The achieved high on/off ratios are attributed to the low off-state current and the high on-state current. The low off-state current behavior mainly depends on the intrinsic quality of the switching layer (i.e., dielectric property). As the capacitance-voltage characteristics are provided in Fig. 1f, our sputter-processed SiO<sub>2</sub>, followed by air annealing, demonstrates decent dielectric performance, comparable (or slightly less) to bulk and thermally grown SiO2. Therefore, our SiO2-based memristor achieved an off-sate current as low as on the order of 10<sup>-11</sup>-10<sup>-10</sup> A. For the on-state behavior, various parameters are related to the overall on-state property, such as the intrinsic characteristics of the switching layer, thickness, and the transport behavior of the charged carriers (oxygen vacancy in this case), and hence the resulting conductivity of the filament. In addition to these intrinsic and processing parameters of the materials and device, a measurement parameter of the compliance current  $(I_{cc})$  is also an important factor in determining the on/off ratio, as it limits the maximum current flowing through the device. This not only prevents the device from experiencing a hard breakdown but is also proposed to control filament growth. <sup>22</sup> With  $I_{cc}$  = 60  $\mu$ A in our study, the conduction filament, once formed, has sufficient conductivity (Fig. S1 in the ESI†) to achieve a relatively high on-current, thereby

Fig. 2 (a) I-V characteristics of the Pd/SiO<sub>2</sub> (5 nm)/P<sup>++</sup>-Si memristor in semi-log scale, where arrows, labeled in alphabetical order, indicate HRS, SET, LRS, RESET, and HRS, respectively. (b) Endurance graph for 100 cycles, two distinct HRS and LRS remain without damping. The resistance values at HRS and LRS are recorded at a read voltage of 0.3 V. (c) Statistical distribution of resistance at HRS and LRS, from which the on/off ratio is extracted to be  $\sim 1.4 \times 10^5$  at a cumulative possibility of 50%. (d) The retention characteristics of 5 nm SiO<sub>2</sub> memristor at LRS and HRS, examined at 85 °C, exhibit reasonably good performance. (e) The statistical distribution of  $R_{\rm HRS}$  and  $R_{\rm LRS}$  for 5 different devices. The on/off ratios were obtained by using the same method in (b). Similar high on/off ratios of  $\sim 10^5$  are obtained from all the devices. (f) Statistical distribution SET voltages for different thicknesses of SiO<sub>2</sub> switching layers. (g) Comparison of the on/off ratio of the present study with those from the literature. (h) Analysis of electric transport processes of the SiO<sub>2</sub>-based memristor in log-log scale.

exhibiting resistive behavior. Furthermore, the regulated filament can be near-fully ruptured during the RESET process to get the low current again, contributing to the high on/off ratio. To assess the stability of our device, the retention characteristics were evaluated with a read voltage 0.3 V at an evaluated temperature 85 °C. As depicted in Fig. 2d, both the LRS and HRS show a prolonged retention time of  $10^4$  seconds. In regard to the device-to-device variation, all the processing parameters and annealing environment are carefully controlled and monitored for the processing of our SiO<sub>2</sub> memristors, to minimize any processing variations and hence the possible performance variations. The performance of our SiO<sub>2</sub>-based memristors slightly varies among the devices and particularly the on/off ratio is found to be reasonably consistent as shown in Fig. 2e, demonstrating 0.9–1.6  $\times$  10<sup>5</sup>. Additionally, the SET

voltage exhibits very small device-to-device variation of 2.90% (Fig. S2, ESI†). This device-to-device evidence, in conjunction with previous cycle-to-cycle tests, underscores the reasonable reliability of our devices. To evaluate the effect of the thickness of the SiO<sub>2</sub> layer, similar electrical characterizations were also carried out on 10 nm, 20 nm, and 30 nm SiO<sub>2</sub> switching layer memristors. The *I-V* characteristics for these switching layer thicknesses can be found in Fig. S3 (ESI†). It is observable that devices with thicker switching layers require a higher voltage for stable resistive switching. The SET voltages are statistically summarized in Fig. 2f. A clear quantitative trend is confirmed, indicating that SET voltage increases with the thickness of the switching layer. The difference in SET voltage between the 5 nm and 30 nm SiO<sub>2</sub> devices is approximately 9 V. From a practical perspective, thinner SiO<sub>2</sub>-based memristors offer higher energy

efficiency. Fig. 2g compares the on/off ratio of the present study with those available in the literature. For objective comparisons, the other two widely-considered oxides of TaO<sub>r</sub> (as Work  $4,^{24}$  5,  $^{25}$  and  $6^{26}$ ) and HfO<sub>x</sub> (as Work 7,  $^{27}$  8,  $^{28}$  and  $9^{29}$ ) are also included in Fig. 2g as well as  $SiO_x$  (as Work 1,  $^{10e}$  2,  $^{30}$  and  $3^{31}$ ). The achieved on/off ratio of  $>10^5$  from our SiO<sub>2</sub> memristors outperforms those ( $\sim 10^1$ - $10^4$ ) of state-of-the-art HfO<sub>x</sub>- and TaO<sub>r</sub>-based memristors. In addition to the on/off performance, the unit price of these switching materials is also compared. Due to the abundance, SiO<sub>2</sub> is significantly cost-effective (100-700 times lower) than the other competitors. 32 In order to make our comparison more comprehensive, we compared the endurance and retention in our work with those in other literature. The comparisons are presented in Table S1 (ESI†), where our device exhibits reasonable reliability, in terms of both endurance and retention, demonstrating on the order of 10<sup>2</sup> cycles and  $10^4$  s.

**Materials Advances**

To analyze electric transport processes, the linear scale I-V curve in Fig. 4a was replotted in double-log scale in Fig. 2h to examine the power law behavior between the current and voltage (i.e.,  $I \propto V^m$ ). During the HRS, the curve exhibits three regimes where  $m \approx 1$ ,  $m \approx 2$ , m > 2, representing ohmic, trapunfilled (Child's square law), and trap-filled regimes, respectively, according to the well-known space-charge-limited conduction (SCLC) mechanism, describing the electric conduction process in a memristor.<sup>14</sup> During the LRS, the linear fitting slope is close to one with a  $R^2 = 0.999$ , indicating the ohmic conduction mechanism (Fig. S4 shows other conduction mechanisms exhibit inferior fits, ESI†), which is widely considered to be attributed to the formation of a conductive filament bridging the TE and BE in a metallic-like way.<sup>33</sup> Additionally, our area effect study in Fig. S5 (ESI†) shows that the current levels in the LRS do not significantly vary with the size of the electrode, suggesting the presence of filamentary conduction. 10e,34 And the results in Fig. S6 (ESI†) for the temperature effect investigation show that the resistance values increase along with the increase in temperature, a metallic characteristic, indicating the filament is established at LRS.<sup>35</sup> These electric transport, area effect, and temperature effect studies synergistically support that our SiO<sub>2</sub>-based memristors depend on the filamentary switching mechanism, which is further validated by the FEA (Fig. 2) and EIS (Fig. 4c) investigations in our study.

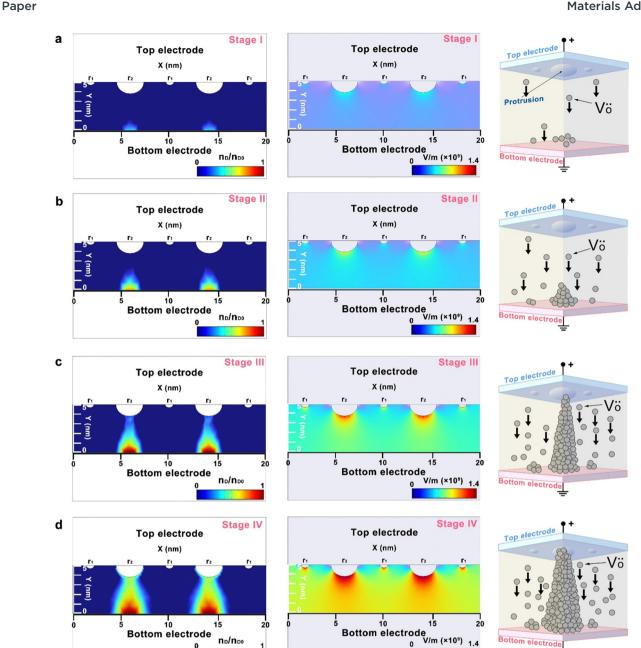

In order to enhance the fundamentals of the switching process through the evolution and rupture of an oxygen vacancy-based conduction filament as well as to complement the macroscale electrical and electrochemical measurements, we performed a series of FEA analyses as a function of applied bias. The physical modeling details are elaborated in Note S1 (ESI†). It should be noted that the switching behavior of the memristor in this study is governed by oxygen vacancies (i.e., VCM) due to the inert Pd (TE) and stably covalent-bonded Si (BE), which indicates that no electrode-related ions are involved in the conduction. A Multiphysics-fields coupled model, which describes the diffusion and drift flux of the  $V_0^{\bullet \bullet}$  at the nanoscale, was adopted to study the switching process of the

memristor. Several protrusions at the top electrode with various radii ( $r_1 = 0.3$  nm,  $r_2 = 1.2$  nm) were considered to reflect the roughness of the TE/SiO2 interface (Fig. 1c1). There is no chemical or structural difference between protrusions and top electrode Pd. In the left of Fig. 3a-d, the overall intensity of  $n_D$ /  $n_{\rm D0}$  (concentration ratio of  $[V_{\rm O}^{\bullet\bullet}]$  at current stage to  $[V_{\rm O}^{\bullet\bullet}]$  at original stage) gradually increased from stage I to stage IV over the course of SET process, indicating the concentration of  $V_0^{\bullet \bullet}$ was augmented in the turn-on process with increasing bias. Compared with the flat region and small protrusions on the top electrode, the protrusions with the larger radius have higher concentrations of  $V_0^{\bullet\bullet}$ , and exhibit a higher intensity of  $n_D/n_{D0}$ , which suggests that the  $V_0^{\bullet\bullet}$  is preferentially concentrated at larger protrusions. This concentration difference can be explained by the variation in the electric field, induced by the intrinsic roughness of the TE/SiO2 interface. The significantly enhanced localized electric field under the large protrusion, as confirmed in the middle of Fig. 3a-d, tends to attract more V<sub>0</sub>. to regions under the protrusions with larger radius. 36 Thus, our FEA analysis indicates that the selectively distributed  $V_0^{\bullet\bullet}$  may limit the random growth of the conduction filaments. This provides an insight for engineering memristors that implementing well defined protrusions may mitigate the issue regarding performance variation of memristors. The bright regions under larger protrusions at stage IV became redder and wider compared with stage III, which implies that the formed conduction filament would grow thicker. Associated schematics at each stage that elaborate the SET process are also shown on the right of our simulation results. When a positive bias is applied to the Pd TE, oxygen ions  $(O^{2-})$  are pulled away from the switching matrix by the external field, migrating towards the Pd TE.<sup>37</sup> This leads to the simultaneous generation of positively charged oxygen vacancies  $(V_0^{\bullet \bullet})$ . In general, this process is often described by the motion of the corresponding oxygen vacancies, i.e., the positively charged oxygen vacancies migrate towards the grounding BE and subsequently accumulate there, forming a conductive filament that bridges the TE and BE.38 Upon arriving at the Pd TE, the oxygen ions are oxidized to O2 and accumulate around the TE/SiO2 interface. 17a,39 The models with different thicknesses of the switching layer were simulated as well (Fig. S7-S9, ESI†). The calculated results are consistent with the model with the SiO2 layer of 5 nm except for the turn-on voltage applied to the top electrode was increased which was led by the thicker SiO2 layer in the models.

EIS is instrumental in acquiring a deeper understanding of the fundamental electrochemical mechanisms through the evaluation of impedance variations at various sinusoidal frequencies and resulting equivalent circuit interpretation. 40 Since redox-based memristors' switching behaviors are reliant on electrochemical reactions, this non-invasive EIS technique provides a unique way to characterize and perceive memristors' switching behavior. 40b,41 Thus, the EIS measurement was carried out on SiO<sub>2</sub>-based memristors. To directly interpret the EIS results on an associated equivalent circuit model, the I-V

Fig. 3 The FEA visualization and schematic elaboration for the evolution of conductive filaments at (a) stage I, where small positive bias for DC sweeping is initially introduced on TE of the device, positively charged oxygen vacancies  $(V_0^{\bullet \bullet})$  are migrating towards BE; (b) stage II, where the magnitude of sweeping DC voltage is increasing, oxygen vacancies start accumulating at BE; (c) stage III, with voltage increasing continuously, the conductive filaments are growing; (d) stage IV, after a SET voltage applied, the conductive filaments are connecting the bottom and top electrodes, where the protrusion radii are  $r_1 = 0.3$  nm,  $r_2 = 1.2$  nm.

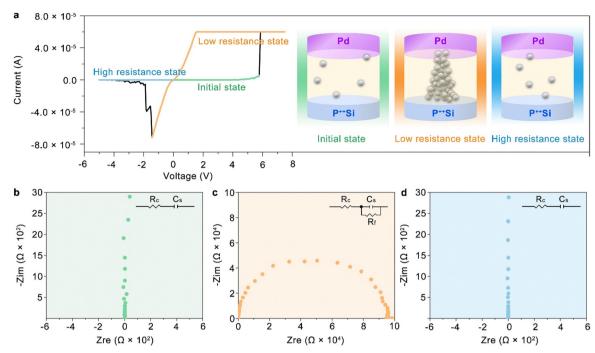

characteristics of memristors (5 nm SiO<sub>2</sub>) were rearranged on a linear-linear scale in Fig. 4a. The green part of Fig. 4a shows I-V characteristics in a linear-linear scale for the initial high resistance state of the memristor. The EIS measurement was employed on the memristor at this state. And the resulting Nyquist plot (left; green) in Fig. 4b, exhibiting a straight line (parallel to the y-axis) supports the capacitive property of HRS of memristors. Based on the simulation, the equivalent circuit at this state consists of a resistor  $R_c$  at  $10^2~\Omega$  level and a capacitor  $C_s$  at  $10^{-10}$  F level, connected in series. The resistance

at this state of the resistor is attributed to contact resistance.<sup>42</sup> The capacitance value is aligned with our CV measurement from pristine devices (Fig. 1f). And this capacitive property at the "initial state" is conceptually explained in the right part of Fig. 4a: the structure of a memristor at the initial state is the same as that of a capacitor and there are few native oxygen vacancies in the SiO2 switching layer. After turning on the memristor, i.e., at the state of Fig. 4a in the orange color period, an EIS measurement was repeated on the SiO<sub>2</sub>-based memristor to understand the on-state conduction behavior of the

Fig. 4 (a) A typical cycle of I-V characteristics from 5 nm SiO<sub>2</sub>-based memristors is shown in a linear-linear scale. The initial HRS, LRS (SET), and HRS (RESET) are colored with green, orange, and blue, sequentially. These three states are schematically explained on the right: the initial HRS of the device has a small number of intrinsic oxygen vacancies (white ball shapes). At LRS, an oxygen vacancy-based conductive filament is well established, connecting the TE and BE. At the HRS resulting from RESET, the conductive filament is dissolved, and fewer oxygen vacancies are present again. (b) A Nyquist plot from EIS measurements on initial HRS of SiO<sub>2</sub>-based memristors, of which the vertical line shape (parallel to the y-axis) indicates the pseudopure capacitive property. Based on the simulation, the equivalent circuit consists of a resistor in series with a capacitor, and it is displayed in the upper right corner. (c) A semicircle shape appears in the Nyquist plot at LRS. Another resistor is paralleled with a capacitor in the simulated equivalent circuit. (d) The Nyquist plot at HRS after RESET becomes a straight-line shape again. The associated equivalent circuit is back to a series connection of one resistor and one capacitor

memristor. A clear semicircle in the Nyquist plot is observed in Fig. 4c (middle; orange). Compared to the equivalent circuit at the initial state, a new resistor  $(R_f)$  at  $10^5 \Omega$  level appears in the equivalent circuit at LRS, and it is connected to the capacitor in parallel. The new resistance value ( $\sim 10^5 \Omega$ ) is aligned with the value measured in the I-V DC sweeping at LRS (Fig. 2a-c). Therefore, the emerged resistor  $(R_f)$  in the equivalent circuit represents the filament(s) in the switching layer which was validated by the electric transport investigations in Fig. 2h (i.e., Ohmic conduction mechanism at LRS). This EIS result complementarily supports the switching behavior suggested by the FEA analysis. At the same time, the majority portion of the memristor is still not connected with the conduction paths, thus, the capacitor component remains in the equivalent circuit. For simplicity, only one conductive path is illustrated in the schematic in Fig. 4a to elucidate the LRS. A RESET process changed the LRS of the memristor back to HRS, as shown in the blue portion of the *I–V* curve in Fig. 4a. The device was turned off and showed the capacitor behavior with a negative bias, similar to the previous HRS state. The EIS measurement in Fig. 4d (right; blue) also verified the HRS of the memristor where a vertically straight line appeared in the Nyquist plot again. The simulated equivalent circuit returns to a configuration of one resistor and one capacitor in series, with values at the same level as the initial state. This capacitive

behavior at HRS (after RESET) indicates that the conduction path was almost completely dissolved (schematically described in Fig. 4a right; blue), and the capacitor symbol describes the state of high resistance of the memristor. The annihilation of filaments can be ascribed to the back motion of oxygen ions under a reverse bias which in turn causes the recombination of oxygen ions and vacancies. Since the filament was regulated by compliance current, it can be near-fully ruptured during the RESET process. Thus, our EIS results on the capacitive properties at initial and after-RESET HRS validate the near formingfree behavior of our memristors as well. Additionally, the EIS measurements at LRS were conducted on SiO2-based memristors featuring varying device areas (Fig. S10, ESI†) and different thicknesses of switching layers (Fig. S11, ESI†). Their Nyquist plots uniformly exhibit semicircular shapes, which corroborates the area effect study shown in Fig. S5 (ESI†) and the FEA in Fig. S7-S9 (ESI†), affirming the filamentary switching mechanism.

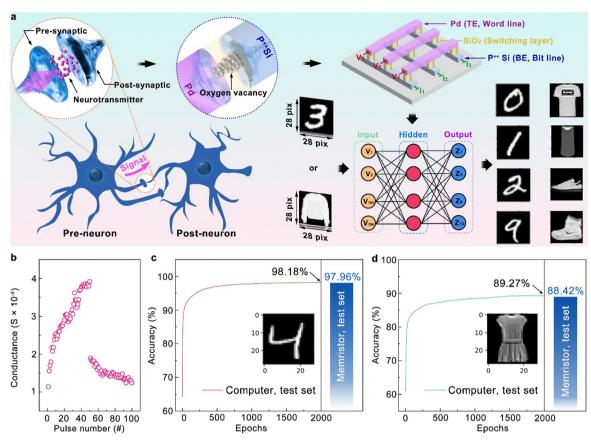

As a two-terminal device, memristors, consisting of a switching layer and two electrodes in a simple sandwich structure closely resemble the structure of a chemical synapse in the brain. This similarity is demonstrated schematically in Fig. 5a, particularly in the orange dashed circle for the synapse and the blue dashed circle for the memristor. The synaptic cleft corresponds to the switching layer of the memristor, while the

This article is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported Licence.

**Paper**

Fig. 5 (a) The process for signal transportation between neurons. The structure and function of the synapse in this process are illustrated in the dashed orange circle (left). In the dashed blue circle (right), the synapse is schematically embedded into the SiO2-based memristor to demonstrate the similarity between them. Next, a SiO<sub>2</sub>-based memristive crossbar prototype is exhibited towards neuromorphic computing. Finally, a neural network for image recognition is explained with instances from MNIST and fashion MNIST data sets (b) the synaptic characteristics evaluated from SiO2-based memristors with 50 identical positive pulses and 50 identical negative pulses, demonstrating gradual variations of the conductance. The model accuracy examinations with (c) MNIST and (d) fashion MNIST as a function of epochs on test sets.

pre-synapse and the post-synapse correspond to the top electrode and the bottom electrode of the memristor, respectively.

In the signal transmission process from one neuron to the next, as illustrated in Fig. 5a, the action potential (i.e., pulse bias in memristor operation) is first transferred from the soma to the end of the neuron (i.e., the presynaptic neuron) via the axon. 43 Then, from the presynaptic neuron, synaptic weights are altered by the release of neurotransmitters. This neurotransmission process leads to the dynamic modulation of synaptic connection intensity. Our SiO<sub>2</sub>-based memristor can mimic this synaptic behavior by tuning the conductance level with electrical pulses. The mechanism of updating weights for SiO<sub>2</sub>-based memristor is similar to a chemical synapse, in which the oxygen vacancies function like neurotransmitters, forming a conductive path in the switching layer (i.e., connecting the top and bottom electrodes) and changing the conductance level of the device.44 A proposed SiO2-based memristor crossbar prototype is illustrated in the upper right corner of Fig. 5. Such crossbar structure features two sets of wire electrodes, categorized as word lines (WLs) and bit lines (BLs). At each junction where these wires intersect, a resistive switching layer is present. Voltage pulses are fed through WLs then traverse

through synaptic crossbar and converge at the BLs. The resulting output current is a function of both the initial input voltages and the conductance properties of the memristors in the crossbar, as described by Ohm's and Kirchhoff's laws. 45 We should note that the practical large-scale crossbar may experience disturbances caused by parasitic effects like series resistance and sneak path complications. The current flowing through the metal wires can cause a notable reduction in voltage, particularly affecting the cell at the greatest distance within the array. This phenomenon ultimately leads to what is commonly termed the "IR drop" problem. This issue not only compromises the reliability of memory read operations but also reduces the accuracy of vector-matrix multiplication computations. Reducing the wire resistance or enhancing the intrinsic resistance of the memristor can effectively address this issue by employing advanced device architectures that promote increased integration and scaling through the reduction of line width/length, along with the utilization of more highly conducting metallization. Another parasitic issue sneak path refers to an unintended electrical pathway that allows current to flow through multiple memristors, rather than through the targeted cell for a particular operation. 46 Such sneak path issue

may trigger operational malfunctions and excessive energy consumption.<sup>47</sup> To alleviate the sneak path issue, various strategies involve redesigning the basic units. For example, adding an access component to the single-memristor (1R) cell can create composite cells like one-transistor-one-memristor (1T1R) or one-switch-one-memristor (1S1R) to suppress the sneak current.48

Neuromorphic computing capability of our SiO2-based memristors was evaluated through pulse measurements with the pulse width of 5 ms and with continuous 50 positive pulses, followed by 50 negative pulses at the amplitude of 5 V for both positive and negative pulses. In Fig. 5b, a prominent multiconductance behavior is observed in the memristor, which mimics the information transportation between synapses. 10 cycles (a total of 1000 pulses) of LTP and LTD behaviors are achieved from our SiO<sub>2</sub>-based memristor (Fig. S12, ESI†), demonstrating consistent repeatability with a relatively linear potentiation behavior and a less linear trend in depression. It should be noted that the resistance state is within the LRS regime during the pulse measurements (i.e., dynamic range) where the conduction filament experiences thickening (potentiation) and shrinkage (depression). 49 To validate this proposed switching mechanism, the retention (Fig. S13a and b, ESI†) and EIS (Fig. S13c-e, ESI†) measurements were conducted at three different LRS states. The Nyquist plots in Fig. S13c-e (ESI†) have a similar shape with one semicircle at LRS to that in the main text Fig. 4c, revealing that the filaments exist at multistates of the device. Thus, the EIS results with the one semicircle shape and increased conductance support our proposed switching mechanism where (1) the synaptic process operates in the dynamic regime (i.e., conduction filament already formed between the TE and BE) and (2) the thickness of the conduction filament increases during the potentiation process.

The asymmetric non-linearity factor (ANL) was calculated by using the following equation:

$$ANL = \frac{G_{P}\left(\frac{N}{2}\right) - G_{D}\left(\frac{N}{2}\right)}{G_{\text{max}} - G_{\text{min}}}$$

where  $G_{\text{max}}$ ,  $G_{\text{min}}$ ,  $G_{\text{P}}(N/2)$ , and  $G_{\text{D}}(N/2)$  represent the conductance maximum, conductance minimum, median value of potentiation, and medium value of depression, respectively.<sup>50</sup> The asymmetric non-linearity factor (ANL) value ranges from "0" to "1", with "0" indicating a completely symmetric scenario.51 As measured from synaptic behavior, our ANL was 0.52 which is comparable to those of other reports, typically ranging 0.12-0.959 (Table S2, ESI†).50,52 Please note that linear programming is favored because it simplifies circuit complexity.<sup>53</sup> And higher non-linear experimental results can decrease inference accuracy.<sup>53</sup>

To demonstrate the neuromorphic computing performance of our memristor, we modeled a deep neural network (DNN) with 784 input neurons, 500 hidden neurons, and 10 output neurons based on our device. Further details on the simulation process are available in Note S2 (ESI†). The DNN is employed to perform image recognition tasks on the MNIST

and fashion-MNIST datasets.54 The computing structure of the DNN is described in Fig. 5a with examples of datasets. The input images are initially converted into 28 × 28 matrices with values ranging from 0 to 255. These matrices are then flattened into vectors of length 784 and fed into the DNN. The 10 output neurons correspond to 10 distinct classes, with the neuron exhibiting the highest value representing the recognized result. The DNN is initially trained on conventional hardware for 2000 epochs, attaining accuracy levels of 98.2% and 89.3% for the MNIST and fashion-MNIST datasets, respectively. Subsequently, the trained weights are translated to conductance values based on our device's conductance changing curve. To facilitate this translation, a proportional mapping scheme is employed that maps continuous weights onto the closest discrete conductance states.<sup>53</sup> Two memristors are utilized to implement positive and negative weights separately, with the maximum discrete weight set at 1 for positive memristors and -1 for negative memristors.<sup>53</sup> Given the finite number of conduction states, the learning accuracy becomes 98.0% and 88.4% for MNIST and fashion-MNIST, respectively (Fig. 5c and d). The marginal reduction (0.2% and 0.9%) in recognition accuracy validates the promise of our memristor for future applications in neural networks and neuromorphic computing.

## Conclusions

We demonstrated high performance SiO2-based memristors which can achieve a noteworthy on/off ratio as high as 1.4 × 10<sup>5</sup> with long-term stability and endurance. The oxygen vacancy-driven switching mechanisms were complementarily identified through theoretical and experimental investigations. A multi-physical field coupled model based finite element simulations systematically revealed the evolution of the conduction filaments as a function of applied bias where the roughness of TE/SiO2 interface plays a significant role. The  $\sim$ 1 nm protrusion causes variations in the local electric field and hence selectively forms a conduction filament, preferably at the higher electric field locations. EIS analyses complement the theoretical switching mechanism investigation by identifying equivalent circuit components of the memristor at initial, SET, and RESET processes. Associated Nyquist plots ascertain pseudo single capacitor behavior at the initial and RESET process, and a parallel structure of a capacitor and a resistor during the SET process. As a proof-of-concept, DNN was demonstrated with the parameters of our SiO<sub>2</sub> memristors. The demonstrated SiO<sub>2</sub>-based memristors featuring a notable high on/off ratio and reasonable reliability as well as low thermal budget processing may be of direct relevance to nextgeneration computing devices that require energy-efficient and parallel processing.

#### Methods

The SiO<sub>2</sub> switching layer was deposited from a sintered ceramic SiO<sub>2</sub> target in a magnetron sputtering system on heavily-doped

Paper Materials Advances

Si wafers ( $< 0.003-0.005 \Omega$  cm). Before the sputtering process, the deposition chamber was pumped down to a base pressure of under  $9 \times 10^{-7}$  Torr. Pure Ar gas (15 sccm) was used as the sputter gas, leading to a working pressure of  $1.7 \times 10^{-3}$  Torr at an RF power of 150 W. Then, the deposited SiO2 layer was annealed at 550 °C for 10 hours. A layer of palladium (Pd) was deposited as the top electrode (TE) on the annealed SiO<sub>2</sub>/Si structure through a thermal evaporation system equipped with a 6 MHz oscillating quartz crystal sensor to monitor the growth rate and thickness. A shadow mask was utilized to define the shape and size of the TE during its fabrication. The thickness of the SiO<sub>2</sub> layer (5, 10, 20, and 30 nm) was verified by a Multi-Wavelength Ellipsometer (FilmSense FS-1) using an incident and detection angle of 65°. An FEI Themis Z TEM microscope equipped with an energy dispersive spectroscopy (EDS) was employed to examine the structures and map elemental distribution in Pd/SiO<sub>2</sub>/P<sup>++</sup>Si memristors. The pattern of the top electrode was verified in plan-view images by an FEI Nova NanoSEM system.

DC current-voltage (I-V) sweeping evaluations of all SiO<sub>2</sub>based memristors were carried out using a semiconductor parameter analyzer (Agilent 4155B) connected to a probe station in a dark shield box. Capacitance-voltage (C-V) characteristics were performed with a precision LCR meter (Agilent 4284A). Electrochemical impedance spectroscopy (EIS) investigations were conducted in an electrochemical workstation (VersaSTAT3 Princeton) by using a frequency range of 1 MHz to 1 Hz. For the pulse measurement, the Agilent 33120A function arbitrary waveform generator provided the pulse profile, which could be conveniently designed by the Agilent IntuiLink Waveform Editor. A digital storage oscilloscope (Hantek DSO4254B) was utilized to monitor the pulse voltages, and the Agilent 4155B SMU was used to record the corresponding current. Physical Modeling details for finite element analysis can be found in Note S1 (ESI†) while detailed simulation for image processing is elaborated in Note S2 in the ESI.†

## **Author contributions**

F. Q. and Y. Z.: conceptualization, characterization for memristors' performance, finite element analysis, draft writing. Z. G.: image processing simulation. C. K., J. P., and K. N.: TEM characterization. X. F.: assistance with electrical measurements. T. P., H. P., H. S., X. R., and S. L.: conceptualization, methodology, supervision, funding acquisition, writing, review, and editing.

#### Conflicts of interest

The authors declare no competing financial interest.

# Acknowledgements

This work was partially supported by National Science Foundation, Award number ECCS-1931088 and CBET-2207302. S. L.

and H. W. S. acknowledge the support from the Improvement of Measurement Standards and Technology for Mechanical Metrology (Grant No. 23011043) by KRISS. The authors would like to thank Dr. Kejie Zhao for providing the electrochemical workstation.

# References

- (a) I. Valov, R. Waser, J. R. Jameson and M. N. Kozicki, Nanotechnology, 2011, 22, 254003; (b) S. Jung, H. Lee, S. Myung, H. Kim, S. K. Yoon, S.-W. Kwon, Y. Ju, M. Kim, W. Yi, S. Han, B. Kwon, B. Seo, K. Lee, G.-H. Koh, K. Lee, Y. Song, C. Choi, D. Ham and S. J. Kim, Nature, 2022, 601, 211.

- 2 (a) C. H. Kim, Y. H. Jang, H. J. Hwang, C. H. Song, Y. S. Yang and J. H. Cho, *Appl. Phys. Lett.*, 2010, 97, 062109; (b) F. Qin, Y. Zhang, H. Park, C. S. Kim, D. H. Lee, Z.-T. Jiang, J. Park, K. No, H. Park, H. W. Song and S. Lee, *Phys. Status Solidi RRL*, 2022, 2200075.

- 3 (a) W. Li, X. Liu, Y. Wang, Z. Dai, W. Wu, L. Cheng, Y. Zhang, Q. Liu, X. Xiao and C. Jiang, Appl. Phys. Lett., 2016, 108, 153501; (b) A. Mehonic, T. Gerard and A. J. Kenyon, Appl. Phys. Lett., 2017, 111, 233502.

- 4 (a) Y. H. Jang, W. Kim, J. Kim, K. S. Woo, H. J. Lee, J. W. Jeon, S. K. Shim, J. Han and C. S. Hwang, *Nat. Commun.*, 2021, **12**, 5727; (b) L. Wu, H. Liu, J. Li, S. Wang and X. Wang, *Nanoscale Res. Lett.*, 2019, **14**, 177.

- 5 (a) M. D. Pickett, D. B. Strukov, J. L. Borghetti, J. J. Yang, G. S. Snider, D. R. Stewart and R. S. Williams, *J. Appl. Phys.*, 2009, **106**, 074508; (b) T. S. Lee and C. Choi, *Nanotechnology*, 2022, **33**, 245202.

- 6 (a) Y. Y. Illarionov, T. Knobloch, M. Jech, M. Lanza, D. Akinwande, M. I. Vexler, T. Mueller, M. C. Lemme, G. Fiori, F. Schwierz and T. Grasser, *Nat. Commun.*, 2020, 11, 3385; (b) K. P. Cheung, *J. Appl. Phys.*, 2022, 132, 144505.

- (a) A. Padovani, D. Z. Gao, A. L. Shluger and L. Larcher, *J. Appl. Phys.*, 2017, 121, 155101; (b) S. Hideki and T. Akira, *Semicond. Sci. Technol.*, 2000, 15, 471; (c) S. J. Moxim, F. V. Sharov, D. R. Hughart, G. S. Haase, C. G. McKay and P. M. Lenahan, *Appl. Phys. Lett.*, 2022, 120, 063502.

- (a) J. Yao, Z. Sun, L. Zhong, D. Natelson and J. M. Tour, *Nano Lett.*, 2010, 10, 4105; (b) A. Mehonic, S. Cueff, M. Wojdak, S. Hudziak, O. Jambois, C. Labbé, B. Garrido, R. Rizk and A. J. Kenyon, *J. Appl. Phys.*, 2012, 111, 074507.

- 9 A. Mehonic, A. L. Shluger, D. Gao, I. Valov, E. Miranda, D. Ielmini, A. Bricalli, E. Ambrosi, C. Li, J. J. Yang, Q. Xia and A. J. Kenyon, *Adv. Mater.*, 2018, 30, 1801187.

- (a) C. Li, L. Han, H. Jiang, M.-H. Jang, P. Lin, Q. Wu, M. Barnell, J. J. Yang, H. L. Xin and Q. Xia, *Nat. Commun.*, 2017, 8, 15666; (b) A. Mehonic, M. S. Munde, W. H. Ng, M. Buckwell, L. Montesi, M. Bosman, A. L. Shluger and A. J. Kenyon, *Microelectron. Eng.*, 2017, 178, 98; (c) N. Ilyas, C. Li, J. Wang, X. Jiang, H. Fu, F. Liu, D. Gu, Y. Jiang and W. Li, *J. Phys. Chem. Lett.*, 2022, 13, 884; (d) C. Li, H. Jiang and Q. Xia, *Appl. Phys. Lett.*, 2013, 103, 062104;

- (e) A. Mehonic, S. Cueff, M. Wojdak, S. Hudziak, C. Labbé, R. Rizk and A. J. Kenyon, Nanotechnology, 2012, 23, 455201.

- 11 N. Ilyas, J. Wang, C. Li, H. Fu, D. Li, X. Jiang, D. Gu, Y. Jiang and W. Li, J. Mater. Sci. Technol., 2022, 97, 254.

**Materials Advances**

- 12 S. Choi, G. S. Kim, J. Yang, H. Cho, C.-Y. Kang and G. Wang, Adv. Mater., 2022, 34, 2104598.

- 13 Y. Huang, Z. Shen, Y. Wu, X. Wang, S. Zhang, X. Shi and H. Zeng, RSC Adv., 2016, 6, 17867.

- 14 J. Zhu, T. Zhang, Y. Yang and R. Huang, Appl. Phys. Rev., 2020, 7, 011312.

- 15 (a) Y. Yang, P. Gao, S. Gaba, T. Chang, X. Pan and W. Lu, Nat. Commun., 2012, 3, 732; (b) J. H. Yoon, J. Zhang, P. Lin, N. Upadhyay, P. Yan, Y. Liu, Q. Xia and J. J. Yang, Adv. Mater., 2020, 32, 1904599.

- 16 (a) M. Buckwell, L. Montesi, S. Hudziak, A. Mehonic and A. J. Kenyon, Nanoscale, 2015, 7, 18030; (b) U. Celano, L. Goux, A. Belmonte, K. Opsomer, A. Franquet, A. Schulze, C. Detavernier, O. Richard, H. Bender, M. Jurczak and W. Vandervorst, Nano Lett., 2014, 14, 2401.

- 17 (a) G. Di Martino, A. Demetriadou, W. Li, D. Kos, B. Zhu, X. Wang, B. de Nijs, H. Wang, J. MacManus-Driscoll and J. J. Baumberg, Nat. Electron., 2020, 3, 687; (b) J. Y. Chen, C. W. Huang, C. H. Chiu, Y. T. Huang and W. W. Wu, Adv. Mater., 2015, 27, 5028.

- 18 B. El-Kareh, Fundamentals of semiconductor processing technologies, Kluwer Academic Publishers, Boston, Massachusetts, 1995.

- 19 Y. Zhang, Z. Wang, J. Zhu, Y. Yang, M. Rao, W. Song, Y. Zhuo, X. Zhang, M. Cui, L. Shen, R. Huang and J. Joshua Yang, Appl. Phys. Rev., 2020, 7, 011308.

- 20 F. M. Simanjuntak, D. Panda, K. H. Wei and T. Y. Tseng, Nanoscale Res. Lett., 2016, 11.

- 21 (a) S. Kumar, M. Das, M. T. Htay, S. Sriram and S. Mukherjee, ACS Appl. Electron. Mater., 2022, 4, 3080; (b) G. S. Kim, H. Song, Y. K. Lee, J. H. Kim, W. Kim, T. H. Park, H. J. Kim, K. Min Kim and C. S. Hwang, ACS Appl. Mater. Interfaces, 2019, 11, 47063.

- 22 (a) M. Song, S. Lee, S. S. T. Nibhanupudi, J. V. Singh, M. Disiena, C. J. Luth, S. Wu, M. J. Coupin, J. H. Warner and S. K. Banerjee, Nano Lett., 2023, 23, 2952; (b) T. S. Lee, N. J. Lee, H. Abbas, H. H. Lee, T. S. Yoon and C. J. Kang, ACS Appl. Electron. Mater., 2020, 2, 1154.

- 23 (a) Z. Liu, P. Cheng, R. Kang, J. Zhou, X. Zhao, J. Zhao and Z. Zuo, Adv. Mater. Interfaces, 2023, 10, 2201513; (b) Y. Sun, X. Yan, X. Zheng, Y. Liu, Y. Zhao, Y. Shen, Q. Liao and Y. Zhang, ACS Appl. Mater. Interfaces, 2015, 7, 7382.

- 24 W. Wang, F. Yin, H. Niu, Y. Li, E. S. Kim and N. Y. Kim, Nano Energy, 2023, 106, 108072.

- 25 J.-H. Ryu, F. Hussain, C. Mahata, M. Ismail, Y. Abbas, M.-H. Kim, C. Choi, B.-G. Park and S. Kim, Appl. Surf. Sci., 2020, 529, 147167.

- 26 O. K. Prasad, S. Chandrasekaran, C.-H. Chung, K.-M. Chang and F. M. Simanjuntak, Appl. Phys. Lett., 2022, **121**, 233505.

- 27 S. Roy, G. Niu, Q. Wang, Y. Wang, Y. Zhang, H. Wu, S. Zhai, P. Shi, S. Song, Z. Song, Z. G. Ye, C. Wenger, T. Schroeder,

- Y. H. Xie, X. Meng, W. Luo and W. Ren, ACS Appl. Mater. Interfaces, 2020, 12, 10648.

- 28 M. Ismail, C. Mahata and S. Kim, J. Alloys Compd., 2022, 892, 162141.

- 29 I. Zrinski, C. C. Mardare, L.-I. Jinga, J. P. Kollender, G. Socol, A. W. Hassel and A. I. Mardare, Appl. Surf. Sci., 2021, **548**, 149093.

- 30 F. Xiong, Z. Wang, E. D. Bøjesen, X. Xiong, Z. Zhu and M. Dong, Small, 2021, 17, 1.

- 31 Y. F. Chang, L. Ji, Y. Wang, P. Y. Chen, F. Zhou, F. Xue, B. Fowler, E. T. Yu and J. C. Lee, Appl. Phys. Lett., 2013, 103, 193508.

- 32 Chemical elements by market price, http://www.leonland. de/elements\_by\_price/en/list, (accessed December 2023).

- 33 H. Dou, X. Gao, D. Zhang, S. Dhole, Z. Qi, B. Yang, M. N. Hasan, J.-H. Seo, Q. Jia, M. Hellenbrand, J. L. MacManus-Driscoll, X. Zhang and H. Wang, ACS Appl. Electron. Mater., 2021, 3, 5278.

- 34 (a) M. Kim, M. A. Rehman, D. Lee, Y. Wang, D.-H. Lim, M. F. Khan, H. Choi, Q. Y. Shao, J. Suh, H.-S. Lee and H.-H. Park, ACS Appl. Mater. Interfaces, 2022, 14, 44561; (b) M.-C. Chen, T.-C. Chang, S.-Y. Huang, S.-C. Chen, C.-W. Hu, C.-T. Tsai and S. M. Sze, Electrochem. Solid-State Lett., 2010, 13, H191.

- 35 (a) N. Ghenzi, M. J. Rozenberg, R. Llopis, P. Levy, L. E. Hueso and P. Stoliar, Appl. Phys. Lett., 2015, 106; (b) Z. Q. Wang, H. Y. Xu, X. H. Li, X. T. Zhang, Y. X. Liu and Y. C. Liu, IEEE Electron Device Lett., 2011, 32, 1442.

- 36 D. Lin, Y. Liu and Y. Cui, Nat. Nanotechnol., 2017, 12, 194.

- 37 J.-Y. Chen, C.-L. Hsin, C.-W. Huang, C.-H. Chiu, Y.-T. Huang, S.-J. Lin, W.-W. Wu and L.-J. Chen, Nano Lett., 2013, 13, 3671.

- 38 T. Wei, Y. Lu, F. Zhang, J. Tang, B. Gao, P. Yu, H. Qian and H. Wu, Adv. Mater., 2023, 35, 2209925.

- 39 (a) D.-H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, X.-S. Li, G.-S. Park, B. Lee, S. Han, M. Kim and C. S. Hwang, Nat. Nanotechnol., 2010, 5, 148; (b) A. Mehonic, M. Buckwell, L. Montesi, M. S. Munde, D. Gao, S. Hudziak, R. J. Chater, S. Fearn, D. McPhail, M. Bosman, A. L. Shluger and A. J. Kenyon, Adv. Mater., 2016, 28, 7486.

- 40 (a) Y. Zhang, C. S. Kim, H. W. Song, S.-J. Chang, H. Kim, J. Park, S. Hu, K. Zhao and S. Lee, Energy Storage Mater., 2022, **48**, 1; (b) C. S. Dash, S. Sahoo and S. R. S. Prabaharan, Solid State Ionics, 2018, 324, 218.

- 41 F. Qin, Y. Zhang, H. W. Song and S. Lee, Mater. Adv., 2023, 4, 1850.

- 42 Y. Li, Y. P. Zhong, J. J. Zhang, X. H. Xu, Q. Wang, L. Xu, H. J. Sun and X. S. Miao, Appl. Phys. Lett., 2013, 103, 043501.

- 43 W. Yi, K. K. Tsang, S. K. Lam, X. Bai, J. A. Crowell and E. A. Flores, Nat. Commun., 2018, 9, 4661.

- 44 (a) W. Huang, X. Xia, C. Zhu, P. Steichen, W. Quan, W. Mao, J. Yang, L. Chu and X. A. Li, Nano-Micro Lett., 2021, 13, 85; (b) R. Waser, R. Dittmann, G. Staikov and K. Szot, Adv. Mater., 2009, 21, 2632.

- 45 Q. Xia and J. J. Yang, Nat. Mater., 2019, 18, 309.

**Paper**

46 (*a*) M. A. Zidan, H. A. H. Fahmy, M. M. Hussain and K. N. Salama, *Microelectron. J.*, 2013, 44, 176; (*b*) Y. Cassuto, S. Kvatinsky and E. Yaakobi, presented at 2013 IEEE International Symposium on Information Theory, 7–12 July 2013, 2013.

- 47 Y. Li and K.-W. Ang, Adv. Intelligent Systems, 2021, 3, 2000137.

- 48 H. Li, S. Wang, X. Zhang, W. Wang, R. Yang, Z. Sun, W. Feng, P. Lin, Z. Wang, L. Sun and Y. Yao, *Adv. Intelligent Systems*, 2021, 3, 2100017.

- 49 S.-O. Park, T. Park, H. Jeong, S. Hong, S. Seo, Y. Kwon, J. Lee and S. Choi, *Nanoscale Horiz.*, 2023, **8**, 1366.

- 50 H. Yeon, P. Lin, C. Choi, S. H. Tan, Y. Park, D. Lee, J. Lee, F. Xu, B. Gao, H. Wu, H. Qian, Y. Nie, S. Kim and J. Kim, *Nat. Nanotechnol.*, 2020, 15, 574.

- 51 A. Shaban, S. S. Bezugam and M. Suri, *Nat. Commun.*, 2021, **12**, 4234.

- 52 (a) J. Park, E. Park, S.-G. Kim, D.-G. Jin and H.-Y. Yu, ACS Appl. Electron. Mater., 2021, 3, 5584; (b) D. S. Kim, H. W. Suh, S. W. Cho, S. Y. Oh, H. H. Lee, K. W. Lee, J. H. Choi and H. K. Cho, Mater. Horiz., 2023, 10, 3382; (c) C. C. Chang, P. C. Chen, T. Chou, I. T. Wang, B. Hudec, C. C. Chang, C. M. Tsai, T. S. Chang and T. H. Hou, IEEE J. Emerging Selected Top. Circuits Systems, 2018, 8, 116; (d) A. Krishnaprasad, D. Dev, S. S. Han, Y. Shen, H.-S. Chung, T.-S. Bae, C. Yoo, Y. Jung, M. Lanza and T. Roy, ACS Nano, 2022, 16, 2866.

- 53 A. Mehonic, D. Joksas, W. H. Ng, M. Buckwell and A. J. Kenyon, *Front. Neurosci.*, 2019, 13, DOI: 10.3389/ fnins.2019.00593.

- 54 (a) Y. Lecun, L. Bottou, Y. Bengio and P. Haffner, *Proc. IEEE*, 1998, **86**, 2278; (b) H. Xiao, K. Rasul and R. Vollgraf, arXiv, 2017, preprint arXiv:1708.07747.