Cite this: *RSC Adv.*, 2022, **12**, 17706

## Quasi-two-dimensional $\alpha$ -molybdenum oxide thin film prepared by magnetron sputtering for neuromorphic computing†

Zhenfa Wu,<sup>a</sup> Peng Shi,<sup>a</sup> Ruofei Xing,<sup>a</sup> Yuzhi Xing,<sup>a</sup> Yufeng Ge,<sup>a</sup> Lin Wei,<sup>\*b</sup> Dong Wang,<sup>a</sup> Le Zhao,<sup>c</sup> Shishen Yan<sup>a</sup> and Yanxue Chen  <sup>\*a</sup>

Two-dimensional (2D) layered materials have attracted intensive attention in recent years due to their rich physical properties, and shown great promise due to their low power consumption and high integration density in integrated electronics. However, mostly limited to mechanical exfoliation, large scale preparation of the 2D materials for application is still challenging. Herein, quasi-2D  $\alpha$ -molybdenum oxide ( $\alpha$ -MoO<sub>3</sub>) thin film with an area larger than 100 cm<sup>2</sup> was fabricated by magnetron sputtering, which is compatible with modern semiconductor industry. An all-solid-state synaptic transistor based on this  $\alpha$ -MoO<sub>3</sub> thin film is designed and fabricated. Interestingly, by proton intercalation/deintercalation, the  $\alpha$ -MoO<sub>3</sub> channel shows a reversible conductance modulation of about four orders. Several indispensable synaptic behaviors, such as potentiation/depression and short-term/long-term plasticity, are successfully demonstrated in this synaptic device. In addition, multilevel data storage has been achieved. Supervised pattern recognition with high recognition accuracy is demonstrated in a three-layer artificial neural network constructed on this  $\alpha$ -MoO<sub>3</sub> based synaptic transistor. This work can pave the way for large scale production of the  $\alpha$ -MoO<sub>3</sub> thin film for practical application in intelligent devices.

Received 26th April 2022

Accepted 9th June 2022

DOI: 10.1039/d2ra02652j

[rsc.li/rsc-advances](http://rsc.li/rsc-advances)

### Introduction

Today, the Internet of Things and artificial intelligence have brought great convenience to our lives in big data analytics, autonomous vehicles, speech and image recognition.<sup>1,2</sup> However, they generate large quantities of complex data and present a huge challenge to the conventional von Neumann architectures. With the background of massive information, neuromorphic computing, seeking inspiration from the human brain to work in parallel and achieve high energy efficiency, hopes to solve computationally hard problems of the conventional computer systems.<sup>3–5</sup> Synapses in the neuromorphic systems can combine information processing and memory by changing the synaptic weight.<sup>1</sup> Interestingly, the electrolyte gated transistor (EGT) can modulate the conductance of the channel by ion migration, which mimics the function of biological synapses very well.<sup>6</sup>

For more than five decades, the traditional transistor has been shrinking exponentially in size in order to increase the switching speed, reduce the power dissipation and improve the integration density.<sup>7</sup> However, scaling down of the transistor is approaching the limitation of miniaturization due to short-channel effects.<sup>8</sup> An alternative solution to solve this bottleneck is using atomically thin semiconductor films, such as 2D materials, as the channel layer of the field effect transistor (FET).<sup>9–15</sup>  $\alpha$ -Molybdenum oxide ( $\alpha$ -MoO<sub>3</sub>), has the well-known layered crystal structure, offers the possibility to obtain ultra-thin film.<sup>16</sup> The layered  $\alpha$ -MoO<sub>3</sub> has unit cell parameters of  $a = 3.96 \text{ \AA}$ ,  $b = 13.86 \text{ \AA}$ ,  $c = 3.70 \text{ \AA}$ , which composed of double layers of linked and distorted MoO<sub>6</sub> octahedra, and belongs to the space group *Pbnm*.<sup>17,18</sup>  $\alpha$ -MoO<sub>3</sub> has been studied as the channel layer of synaptic transistor for neuromorphic computing in recent works.<sup>19,20</sup> Unfortunately, in these works, the  $\alpha$ -MoO<sub>3</sub> film was prepared by the mechanical exfoliation, which could not realize large scale production for practical application. Wang *et al.* have fabricated  $\alpha$ -MoO<sub>3</sub> based two-terminal memristive device prepared by pulsed laser deposition (PLD).<sup>21</sup> However, in their device, the thickness of  $\alpha$ -MoO<sub>3</sub> is 400 nm, which loses the excellent characteristics of 2D material based device. Moreover, the signal transmission and learning functions could not be carried out simultaneously in two-terminal memristive device.<sup>19</sup> Therefore, large scale production of  $\alpha$ -MoO<sub>3</sub> thin film for practical application in neuromorphic computing needs further research.

<sup>a</sup>School of Physics, and State Key Laboratory of Crystal Materials, Shandong University, Jinan, 250100, China. E-mail: cyx@sdu.edu.cn

<sup>b</sup>School of Microelectronics, and State Key Laboratory of Crystal Materials, Shandong University, Jinan, 250100, China. E-mail: wl2003@sdu.edu.cn

<sup>c</sup>School of Electronic and Information Engineering, Qilu University of Technology, Jinan, 250353, China

† Electronic supplementary information (ESI) available. See <https://doi.org/10.1039/d2ra02652j>

In this work, an all-solid-state synaptic transistor based on  $\alpha$ -MoO<sub>3</sub> thin film prepared by magnetron sputtering is designed and studied. The surface morphology, crystal structure and valence characterizations indicate that a highly uniform orthorhombic single phase  $\alpha$ -MoO<sub>3</sub> thin film is obtained. About four orders of reversible conductance modulation is observed in the  $\alpha$ -MoO<sub>3</sub> channel by the protons (H<sup>+</sup>) intercalation/deintercalation under the positive/negative gate voltages. The essential synaptic functions, including potentiation, depression and short-term/long-term plasticity were successfully mimicked. High recognition accuracy is achieved using a simulated artificial neural network built from this  $\alpha$ -MoO<sub>3</sub> synaptic device. Overall, our study paves the way for large scale production of  $\alpha$ -MoO<sub>3</sub> thin film for practical application in intelligent devices.

## Experimental section

### $\alpha$ -MoO<sub>3</sub> thin film preparation and characterizations

A Mo metal target (99.99%) was used to prepare  $\alpha$ -MoO<sub>3</sub> thin film on SrTiO<sub>3</sub>(100) single crystalline substrate (MTI, Hefei) at 450 °C by radio-frequency magnetron sputtering. The working pressure was 0.65 Pa (O<sub>2</sub> 23% + Ar 77%) in a gas flow of 19.0 sccm. The sputtering power was 45 W and the deposition rate was about 0.1 Å s<sup>-1</sup>. The thickness of  $\alpha$ -MoO<sub>3</sub> thin film was about 18 nm. The surface morphology of  $\alpha$ -MoO<sub>3</sub> thin film was checked by atomic force microscope (AFM, Solver P47 PRO, NT-MDT) and scanning electron microscope (SEM, G300 FE-SEM System). The crystal structure and thickness of  $\alpha$ -MoO<sub>3</sub> thin film were characterized by X-ray diffraction (XRD, Smartlab, Rigaku Co). The thickness of  $\alpha$ -MoO<sub>3</sub> thin film was also characterized by a step profiler (Kosaka, ET 150). The chemical composition and bonding states of the  $\alpha$ -MoO<sub>3</sub> thin film were determined by X-ray photoelectron spectroscopy (XPS, Escalab 250).

### Device fabrication

After photolithography patterning, the bottom Cr/Au(3 nm/20 nm) source/drain electrodes were prepared on SrTiO<sub>3</sub>(100) substrate by thermal evaporation and lift-off method. The distance between source and drain electrodes was 20 μm. Then the  $\alpha$ -MoO<sub>3</sub> thin film used as the channel was deposited on the electrodes. And 30 nm amorphous Gd<sub>2</sub>O<sub>3</sub> film was deposited on  $\alpha$ -MoO<sub>3</sub> thin film used as the electrolyte by radio-frequency magnetron sputtering at room temperature. During the deposition of Gd<sub>2</sub>O<sub>3</sub> film, the working pressure was 0.65 Pa (O<sub>2</sub> 50% + Ar 50%) in a gas flow of 19.0 sccm, and the sputtering power was 70 W. Finally, 6 nm Pd film was deposited on Gd<sub>2</sub>O<sub>3</sub> film through a Cu hard mask as the top gate electrode by direct-current magnetron sputtering at room temperature. In this process, an all-solid-state synaptic transistor device is successfully fabricated.

### Electrical measurement

The transfer curves of the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor device were measured using a custom-designed 4-probe station

with two Keithley 2400 source meters under air and vacuum (<2 × 10<sup>-4</sup> Pa) conditions, respectively. The voltage range was from -1.2 V to 2.5 V with a sweep rate of 2 mV s<sup>-1</sup>. The synaptic plasticity of the device was characterized by the 4-probe station in air condition.

## Results and discussion

### Structure and composition of $\alpha$ -MoO<sub>3</sub> thin film

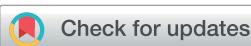

In this work, layered  $\alpha$ -MoO<sub>3</sub> thin film was prepared on SrTiO<sub>3</sub>(100) single crystalline substrate by magnetron sputtering.<sup>22</sup> Fig. 1a exhibits a 2 × 2 μm AFM image (the scale bar is 300 nm) of the  $\alpha$ -MoO<sub>3</sub> thin film, which demonstrates a uniform surface. The root mean square (RMS) roughness is 1.31 nm, indicating that the film is smooth. As deduced from X-ray reflectance spectrum (Fig. S1a, ESI†), the thickness of the  $\alpha$ -MoO<sub>3</sub> thin film is about 18 nm (~14 layers). The thickness of  $\alpha$ -MoO<sub>3</sub> thin film was also confirmed by a step profiler (Fig. S1c and d, ESI†). Fig. 1b shows the top-view SEM image (the scale bar is 2 μm) of this film, which demonstrates that the film is flat and continuous in the whole view. XRD characterization is carried out to study the microstructure of the  $\alpha$ -MoO<sub>3</sub> thin film. As shown in Fig. 1c, the peaks at 2θ = 12.7°, 25.6° and 38.9° correspond to the (020), (040) and (060) planes of  $\alpha$ -MoO<sub>3</sub> (JCPD: 05-0508), respectively.<sup>18,19</sup> It is obvious that there is no impurity peak except the peaks of  $\alpha$ -MoO<sub>3</sub> thin film and SrTiO<sub>3</sub>(100) substrate in Fig. 1c. Because of its thin thickness, the intensity of  $\alpha$ -MoO<sub>3</sub> thin film peaks are relatively weaker than those of bulk  $\alpha$ -MoO<sub>3</sub> single crystal.<sup>18</sup> The XRD results demonstrate that the  $\alpha$ -MoO<sub>3</sub> thin film is single orthorhombic phase with (010) preferred orientation.

The chemical composition and bonding states of the  $\alpha$ -MoO<sub>3</sub> thin film were characterized by XPS (Fig. 1d–f). The carbon C 1s peak at 284.6 eV was used to calibrate the XPS spectra. High-resolution scans of Mo 3d (Fig. 1d) and O 1s (Fig. 1e) were collected and fit with Gaussian–Lorentz distribution using a Shirley background. The binding energy peaks at 232.81 eV and 235.95 eV are the characteristic peaks of Mo 3d5/2 and Mo 3d3/2, respectively, which indicates that Mo in this film has a valence of +6. The binding energy peak at 530.52 eV is the characteristic peak of O 1s. All of these peaks are consistent well with previous reports.<sup>23,24</sup> The total XPS spectrum (150–600 eV) of the  $\alpha$ -MoO<sub>3</sub> thin film is shown in Fig. 1f, in which the characteristic peaks of Mo 3d, C 1s, Mo 3p, Mo 3s and O 1s can be obtained. No peak related to impurity elements appears in the overview spectrum. In short, all the above results indicate high quality single phase  $\alpha$ -MoO<sub>3</sub> thin film was obtained on SrTiO<sub>3</sub>(100) substrate by magnetron sputtering.

### Electrical properties of $\alpha$ -MoO<sub>3</sub> based synaptic transistor

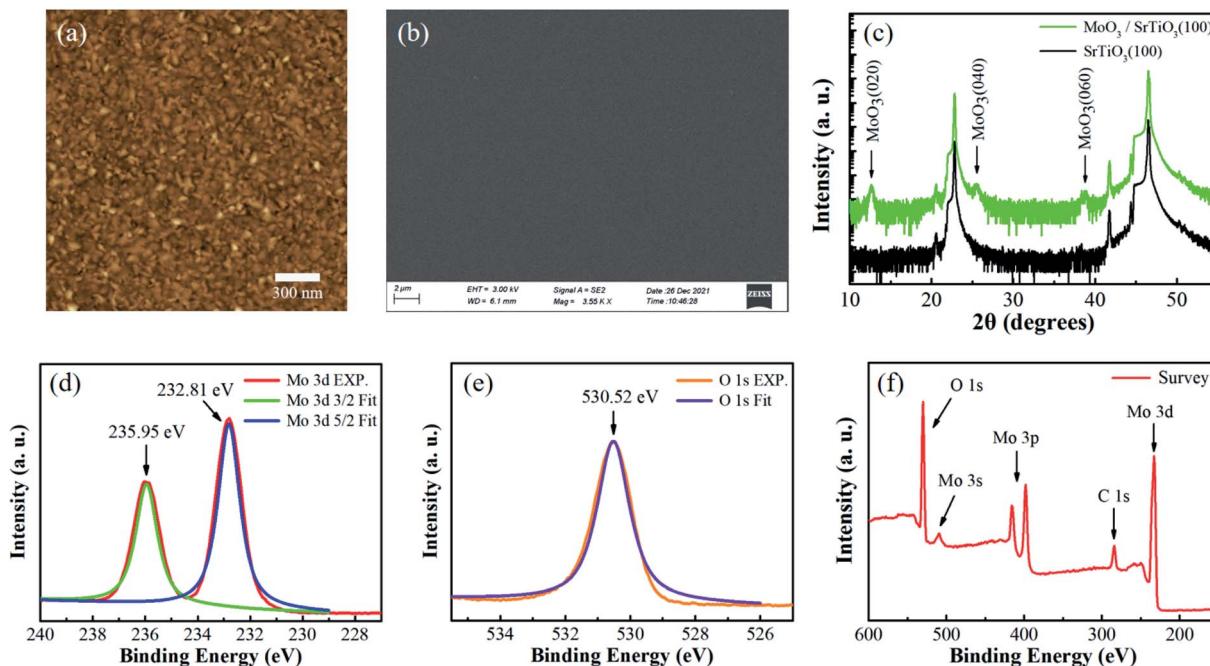

Recently, electrolyte gated synaptic transistors have been studied extensively for neuromorphic computing due to their excellent performance.<sup>6,14,25</sup> In this study, an all-solid-state synaptic transistor based on  $\alpha$ -MoO<sub>3</sub> thin film is successfully fabricated. Fig. 2a and b show the schematic diagrams of the biological synapse and the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor.

Fig. 1 The properties of  $\alpha$ -MoO<sub>3</sub> thin film on SrTiO<sub>3</sub>(100) substrate. (a) AFM image of the  $\alpha$ -MoO<sub>3</sub> thin film, the scale bar is 300 nm. (b) SEM image of the  $\alpha$ -MoO<sub>3</sub> thin film, the scale bar is 2  $\mu$ m. (c) XRD characterization of the  $\alpha$ -MoO<sub>3</sub> thin film and the SrTiO<sub>3</sub> substrate. (d–f) XPS spectra of the  $\alpha$ -MoO<sub>3</sub> thin film. XPS spectra corresponding to the Mo 3d (d) and O 1s (e) core level of the  $\alpha$ -MoO<sub>3</sub> thin film. (f) The overview XPS result (150–600 eV) of the  $\alpha$ -MoO<sub>3</sub> thin film.

The biological synapse is composed of presynaptic neuron, neurotransmitters, synaptic cleft and postsynaptic neuron (Fig. 2a). After an action potential arrived at presynaptic neuron, the neurotransmitters will be released from presynaptic neuron into postsynaptic neuron through combination with specific receptors, resulting in variations of the postsynaptic potential to transmit information.<sup>26–29</sup> Imitating the biological synapse, Gd<sub>2</sub>O<sub>3</sub> solid-state electrolyte and  $\alpha$ -MoO<sub>3</sub> channel are used in the transistor device as the presynaptic neuron and postsynaptic neuron, respectively (Fig. 2b). In this artificial synaptic device, the external stimulus (voltage pulse) applied on the gate electrode will lead to hydrolysis reaction at the interface between Gd<sub>2</sub>O<sub>3</sub> electrolyte layer and top Pd electrode, and create a lot of protons (H<sup>+</sup>) that function as neurotransmitters. These neurotransmitters (H<sup>+</sup>) will be driven across the Gd<sub>2</sub>O<sub>3</sub> electrolyte and injected into  $\alpha$ -MoO<sub>3</sub> channel under a high enough positive gating voltage. As a result, the channel conductance (synaptic weight) will be modulated to transmit information.

In order to characterize the performance of the transistor, the transfer curves were measured in air (Fig. 2c) and under vacuum condition (Fig. 2d), respectively. The gate voltage (V<sub>G</sub>) was swept from 0 V to 2.5 V, 2.5 V to –1.2 V and then back to 0 V. The sweep rate was 2 mV s<sup>–1</sup> and the source drain voltage (V<sub>read</sub>) was 0.5 V. The red and blue lines represent source drain current (I<sub>SD</sub>) and gate current (I<sub>G</sub>), respectively. As we can see, I<sub>SD</sub> increases significantly (about 10<sup>4</sup> times) and shows a clear anti-clockwise hysteresis by sweeping the V<sub>G</sub> in air condition (Fig. 2c). When V<sub>G</sub> was swept to the positive part, H<sup>+</sup> ions will be injected into the MoO<sub>3</sub> channel, resulting in H<sub>x</sub>MoO<sub>3</sub> with

a high conductance state. This process can be described by the following reaction:<sup>16</sup>

In contrast, when V<sub>G</sub> is reduced, H<sup>+</sup> ions will be extracted from the H<sub>x</sub>MoO<sub>3</sub> channel to Gd<sub>2</sub>O<sub>3</sub> film, recovering the low conductance in MoO<sub>3</sub> channel. This process can be described by the following reaction:

The magnitude of I<sub>G</sub> is below 4 nA during the whole sweeping cycle, which is more than three orders smaller than I<sub>SD</sub>, indicating that the leakage current has little effect on I<sub>SD</sub>. However, if the air was pumped out of the probe station chamber and the transfer curve was obtained under vacuum condition, I<sub>SD</sub> increases slightly and shows a tiny anti-clockwise hysteresis by sweeping the V<sub>G</sub> (Fig. 2d). The red and blue lines represent I<sub>SD</sub> and I<sub>G</sub>, respectively. The dramatically different gating responses observed in air and vacuum conditions indicate that the water molecular in air may play a crucial role in modulating the channel conductance.<sup>19,30,31</sup> In addition, some theoretical calculations performed with the density functional theory have also predicted that the conductance of MoO<sub>3</sub> can be changed by hydrogenation.<sup>32–34</sup> The resistance data of the  $\alpha$ -MoO<sub>3</sub> channel were extracted from the I<sub>SD</sub>–V<sub>G</sub> curves, as shown in Fig. 2e and f. The channel resistance changes from 10<sup>8</sup>  $\Omega$  to 10<sup>4</sup>  $\Omega$  and exhibits a clear clockwise hysteresis by sweeping the V<sub>G</sub> in air condition, while it changed slightly under vacuum

Fig. 2 The schematic diagram of (a) the biological synapse and (b) the device structure. The transfer curves of  $\alpha$ -MoO<sub>3</sub> based synaptic transistor measured under (c) air and (d) vacuum conditions, respectively. The gate voltage window was from  $-1.2$  V to  $2.5$  V, and the sweeping rate was  $2$  mV s $^{-1}$ . (e) and (f) show the channel resistance variations during sweeping the gate voltage under air and vacuum conditions, respectively.

condition. The slight channel resistance variation under vacuum condition is caused by residual H<sup>+</sup> ions in the device.

#### Synaptic plasticity of the synaptic transistor

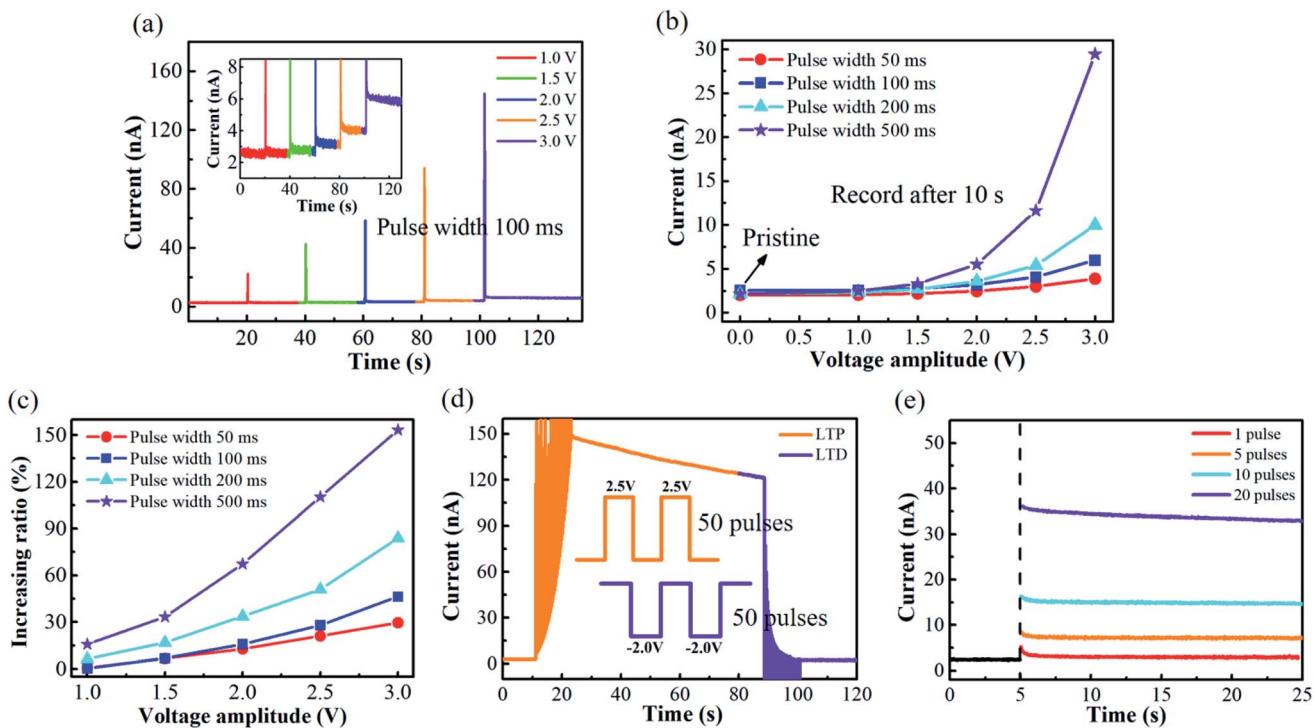

The obvious hysteresis in the transfer curve of this novel transistor lays a good foundation for potential synaptic application. To demonstrate the nonvolatile characteristics, the solid-state  $\alpha$ -MoO<sub>3</sub> transistor was trained by sending a series of voltage pulses to the gate electrode. During the voltage pulses, the source-drain current is recorded at the same time. The synaptic plasticity characteristics of the artificial synaptic transistor device are shown in Fig. 3a. A series of single voltage pulse stimulation with different magnitudes (1.0 V–3.0 V) and identical pulse width of 100 ms were applied to gate electrode, and a source-drain voltage of 0.5 V was applied. Similar to the short-

term plasticity (STP) in biological synapse,  $I_{SD}$  shows a sharp peak response to the  $V_G$ , and quickly decreases to the initial value under low  $V_G$  of 1.0 V and 1.5 V. While under a higher  $V_G$  ( $>2.0$  V), the  $I_{SD}$  could not return to the initial value after the gate stimulation, indicating a nonvolatile behavior. This means that a memory behavior can be realized using higher voltage gating pulses. A more detailed study of the synaptic plasticity characteristics under different  $V_G$  (pulse magnitude: 1.0–3.0 V, pulse width: 50–500 ms) was shown in Fig. 3b and c. These values of  $I_{SD}$  were recorded after 10 s of each spike. It can be clearly seen that the channel conductance change increases with the pulse width and amplitude of  $V_G$ . Voltage pulses with longer duration time and larger magnitude can lead to a higher H<sup>+</sup> doping in the  $\alpha$ -MoO<sub>3</sub> channel, resulting in a larger nonvolatile change of the channel conductance. The energy consumption in plasticity process was estimated. The energy consumption per spike is

Fig. 3 (a) The channel conductance variations under different  $V_G$  (1.0 V–3.0 V) with a fixed pulse width (100 ms). The inset shows the detailed conductance variations after each spike. (b) The channel conductance values (record after 10 s of each spike) and (c) the increasing ratio of channel conductance under different  $V_G$  (1.0 V–3.0 V) with different pulse width (50 ms–500 ms). (d) Long-term potentiation (2.5 V, 100 ms, 50 pulses) and long-term depression (−2.0 V, 100 ms, 50 pulses). (e) Spike number dependent plasticity (SNDP). The pulse numbers increase from 1 to 20 with a fixed  $V_G$  (2.0 V, 100 ms).

about  $5.0 \times 10^{-10}$  J as calculated with the formula  $I_{\text{peak}} \times \Delta t \times V_{\text{read}}$ ,<sup>35</sup> where  $I_{\text{peak}}$ ,  $\Delta t$  and  $V_{\text{read}}$  represent the peak value of the  $I_{\text{SD}}$  ( $\sim 20$  nA), the pulse width (50 ms) and the source drain

voltage (0.5 V), respectively. The energy consumption can be further reduced by device miniaturization for practical application.

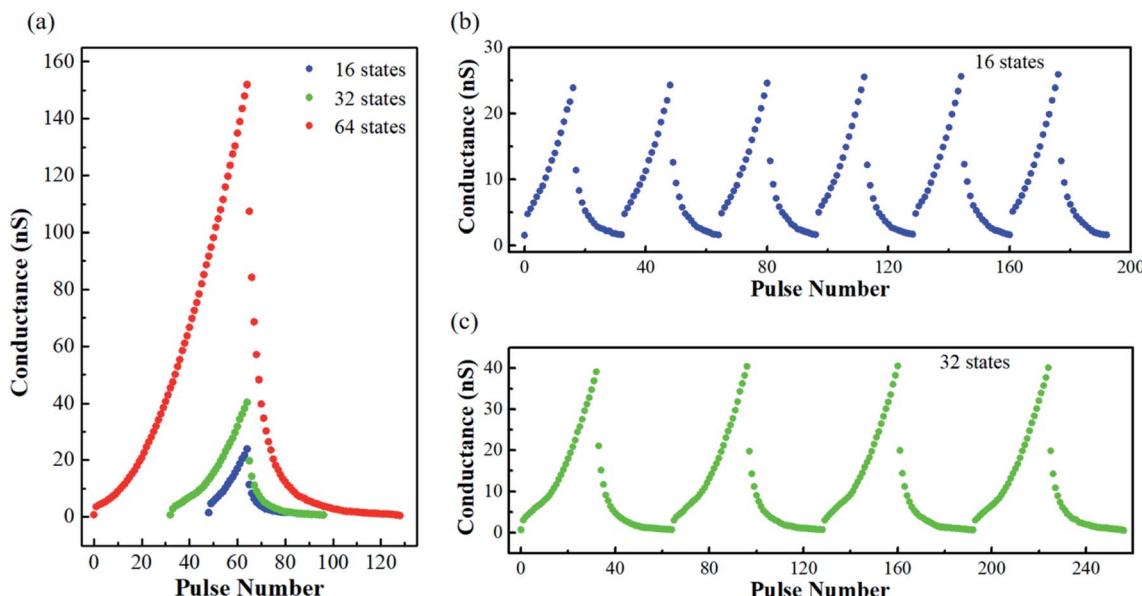

Fig. 4 Analog switching of the synaptic transistor. (a) 16/32/64 multi-level states obtained by applying 16/32/64 positive and negative  $V_G$  pulses. The values of channel conductance were read under a  $V_{\text{read}}$  of 0.5 V. (b) and (c) Cycle testing with 16 and 32 positive/negative  $V_G$  pulses, respectively.

It is well known that bidirectional plasticity, that is the long-term potentiation (LTP) and long-term depression (LTD), is a key concept in synapses. Potentiation and depression represent synaptic strengthening and weakening, respectively. These functions were mimicked in our synaptic transistor device. The channel conductance (synaptic weight) can be reversible modulation by insertion/extraction of  $H^+$  ions into/from the  $\alpha$ -MoO<sub>3</sub> thin film under the positive/negative electric bias. Fig. 3d shows the LTP and LTD of the synaptic transistor. By alternatively applying 50 identical pulses (2.5 V, 100 ms),  $I_{SD}$  gradually increases with the positive gate spikes (LTP), while  $I_{SD}$  decreases

to the initial value (LTD) after 50 negative gate spikes (-2.0 V, 100 ms). Fig. 3e depicts the spike number dependent plasticity (SNPD) of the synaptic transistor, which was measured by monitoring the channel conductance after applying 1, 5, 10 and 20 identical pulses (2.0 V, 100 ms). It is obvious that the  $I_{SD}$  increases with the pulse numbers. Fig. 3e also shows that after the withdrawal of the gate spikes, the channel current decays slowly with time, just like the forgetting process in biological systems. Fig. 3d and e also demonstrate a nonvolatile behavior of the synaptic transistor. However, if the decaying time is much

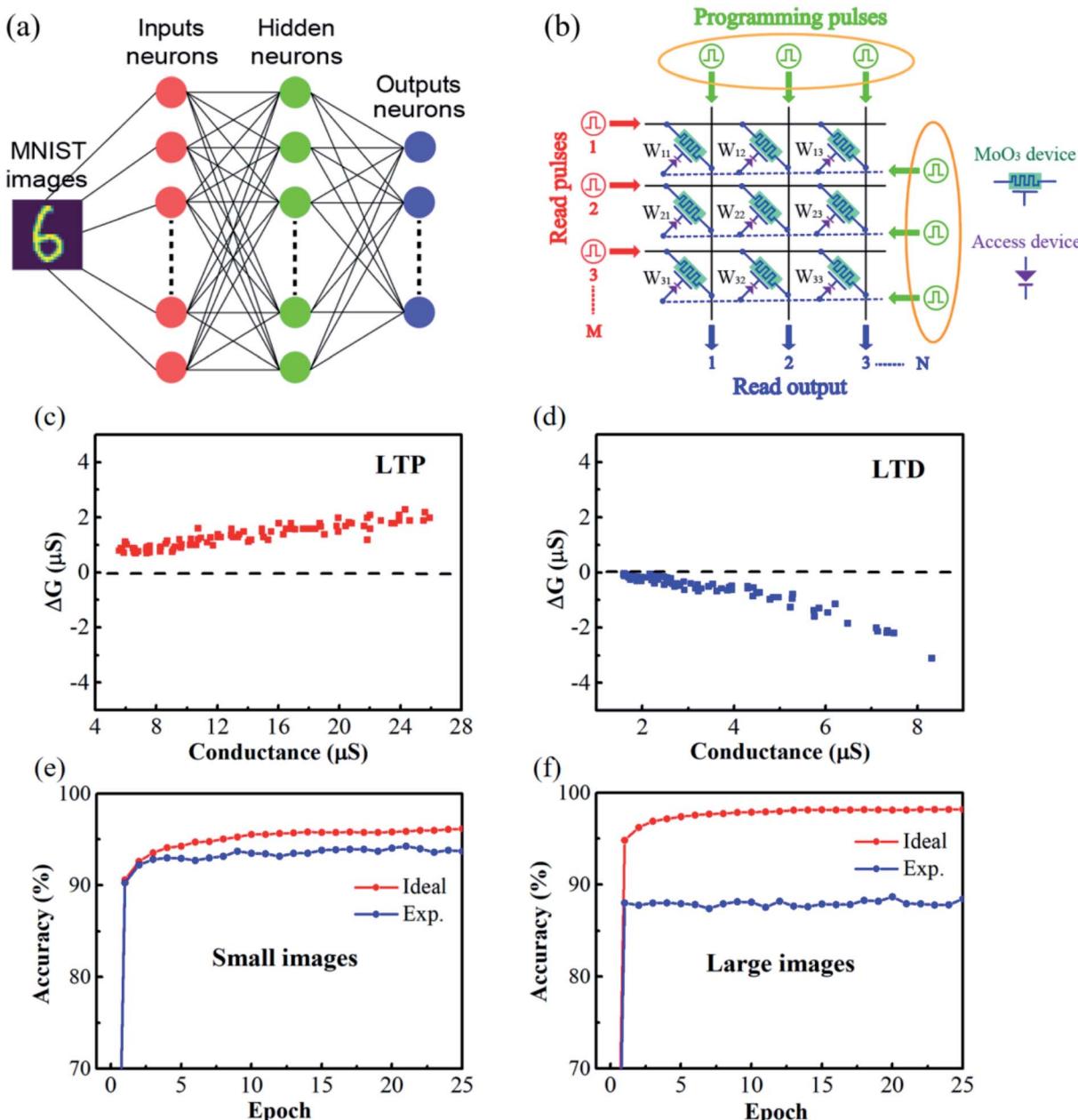

**Fig. 5** The simulation of supervised learning in the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor device. (a) Schematic image of a three-layer (one hidden layer) artificial neural network. (b) Schematic image of the crossbar array made up of  $\alpha$ -MoO<sub>3</sub> based transistor. (c and d) The changes in channel conductance ( $\Delta G$ ) in (c) LTP and (d) LTD processes. (e and f) The recognition accuracy for (e) small images and (f) large images with an ideal device and  $\alpha$ -MoO<sub>3</sub> based device.

longer than the switching time, this decaying process will have little effect on the operation of this synaptic device.

### Analog switching of the synaptic transistor

As shown above, several essential synaptic functions have been realized in the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor device. Realization of multi-states in synaptic weight is a requisite condition for artificial neuromorphic computing. Fig. 4a shows the 16/32/64 multi-level data storage functions obtained by applying 16/32/64 positive (2.0 V, 100 ms) and negative (-2.0 V, 100 ms)  $V_G$  pulses. The values of channel conductance were calculated with  $I_{SD}$  divided by  $V_{read}$ . The  $G_{max}/G_{min}$  ratios of the 16/32/64 multiple states are as large as 15.9/55.2/183.0, respectively, where the  $G_{max}$  and  $G_{min}$  represent the maximum and the minimum (initial) channel conductance values, respectively. Large  $G_{max}/G_{min}$  ratio can provide a potential opportunity to obtain more storage states.

To demonstrate the behaviors of weight update, a repeated 16/32 potentiation and depression cycling test was performed, as shown in Fig. 4b and c. The transistor device exhibits good repeatability and stability. To check the linearity and stability of the weight update behavior during analog switching, the asymmetric ratio (AR) and cycle-to-cycle variation (C2C) were calculated, respectively. The AR can be obtained using the following formula:<sup>20,37,38</sup>

$$AR = \frac{\max|G_P(n) - G_D(n)|}{G_{max} - G_{min}} \quad (3)$$

Where  $n$  (from 1 to 32) is the voltage pulse number of the 32 potentiation and depression cycle,  $G_P(n)$  and  $G_D(n)$  are the channel conductance values at  $n$ th state during the potentiation and depression processes, respectively.  $G_{max}$  and  $G_{min}$  are the maximum and minimum channel conductance values, respectively. The value of AR is zero for ideal linear device. Here, the calculated AR of the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor device is  $0.58 \pm 0.0069$ , which is comparable to previous report.<sup>37</sup> The linearity of our device still needs to be further improved for achieving higher image recognition accuracy, which will be discussed in the next section. The cycle-to-cycle variation (the average of the channel conductance standard deviation divided

by the maximum conductance)<sup>20,26,27</sup> was characterized with 5 sequential switching cycles. It can be defined as:

$$C2C = \frac{\left\{ \sum_{n=1}^{32} \left[ \sum_{m=1}^5 (G_m(n) - \bar{\sigma}(n))^2 \right] / 5 \right\} / 32}{G_{max}} \quad (4)$$

Where  $m$  (from 1 to 5) is the number of cycles,  $n$  (from 1 to 32) is the voltage pulse number of each cycle.  $\bar{\sigma}(n)$  is the mean value of channel conductance in  $n$ th state, which is the average of channel conductance of  $n$ th voltage pulse in 5 switching cycles.  $G_m(n)$  is the channel conductance of  $m$ th cycle in  $n$ th state.  $G_{max}$  is the maximum value of channel conductance. The calculated C2C of the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor device is as low as 1.02%. This low C2C demonstrates a low write noise during neuromorphic computing.

### Simulation of supervised pattern recognition

Finally, the computing performance of the  $\alpha$ -MoO<sub>3</sub> based synaptic transistor was evaluated. As shown in Fig. 5a, a three-layer artificial neural network (one hidden layer) was constructed to perform supervised learning based on a back-propagation algorithm. The neurons of every layer connect with each other. Back-propagation is a widely used method for training artificial neural networks in neuromorphic computing.<sup>39</sup> Two data sets were employed to train this artificial neural network: a small image version (8 × 8 pixels) of handwritten digits from the "Optical Recognition of Handwritten Digits" data set,<sup>40</sup> and a large image version (28 × 28 pixels) of handwritten digits from the "Modified National Institute of Standards and Technology" (MNIST) data set.<sup>41</sup> Fig. 5b shows the crossbar array of the CrossSim simulator, which was used to perform vector-matrix multiplication and outer-product update operations.<sup>36,42</sup> The crossbar array contains read pulses (red color), programming pulses (green color) and read outputs (blue color). The  $\alpha$ -MoO<sub>3</sub> channel conductance represents the synaptic weight.

The LTP/LTD experimental data in Fig. 4b were selected for supervised simulation. The simulating results were demonstrated in Fig. 5c-f. The channel conductance deviation ( $\Delta G$ )

Table 1 Summary of the fabrication methods and synaptic characteristics of synaptic transistor devices

| Device structure                                                                | Active ions           | Channel fabrication method | Channel thickness [nm] | Stability | Energy consumption [J]     | Recognition accuracy | Ref.      |

|---------------------------------------------------------------------------------|-----------------------|----------------------------|------------------------|-----------|----------------------------|----------------------|-----------|

| Gd <sub>2</sub> O <sub>3</sub> / $\alpha$ -MoO <sub>3</sub> /SrTiO <sub>3</sub> | H <sup>+</sup>        | Sputtering                 | 18                     | 1.02%     | $<5.0 \times 10^{-10}$     | 94%                  | This work |

| IL <sup>a</sup> / $\alpha$ -MoO <sub>3</sub> /SiO <sub>2</sub> /Si              | H <sup>+</sup>        | Mechanical exfoliation     | 12.6                   | —         | $9.6 \times 10^{-12}$      | —                    | 19        |

| SL <sup>b</sup> / $\alpha$ -MoO <sub>3</sub> /SiO <sub>2</sub> /Si              | Li <sup>+</sup>       | Mechanical exfoliation     | 18                     | 6.5%      | $1.6 \times 10^{-13}$      | 94%                  | 20        |

| Pt/ $\alpha$ -MoO <sub>3</sub> /Nb-SrTiO <sub>3</sub><br>(two terminal device)  | H <sup>+</sup>        | PLD <sup>c</sup>           | 400                    | 1.4%      | —                          | —                    | 21        |

| IL <sup>a</sup> /VO <sub>2</sub> /Mica                                          | H <sup>+</sup>        | PLD <sup>c</sup>           | 40                     | 2.1%      | $8.8 \times 10^{-13}$      | 95%                  | 26        |

| SL <sup>b</sup> /VO <sub>2</sub> /Polyimide                                     | H <sup>+</sup>        | Sputtering                 | 51                     | 0.17%     | $<6.2 \times 10^{-9}$      | 98%                  | 27        |

| MoS <sub>2</sub> /Na-SiO <sub>2</sub> /Si                                       | Na <sup>+</sup>       | Mechanical exfoliation     | 10                     | —         | $\sim 3.0 \times 10^{-7}$  | 90%                  | 43        |

| MoTe <sub>2</sub> /sr-SiN <sub>x</sub> /Si                                      | e <sup>-</sup> /holes | Mechanical exfoliation     | 7                      | 1.5%      | $\sim 1.0 \times 10^{-10}$ | 91%                  | 44        |

| $\alpha$ -In <sub>2</sub> Se <sub>3</sub> /Ta <sub>2</sub> O <sub>5</sub> /P-Si | e <sup>-</sup> /holes | Mechanical exfoliation     | 30                     | —         | $1.0 \times 10^{-11}$      | 93%                  | 45        |

<sup>a</sup> Ionic liquid. <sup>b</sup> Solid state ionic liquid. <sup>c</sup> Pulsed laser deposition.

between experimental values were characterized to evaluate the device nonideality. In contrast to C2C,  $\Delta G$  is the change of channel conductance induced by single voltage pulse within each cycle. As we can see, the distribution of  $\Delta G$  in LTP process (Fig. 5c) is narrower than that in LTD process (Fig. 5d) over the entire range of  $G$ . The image recognition accuracy of the simulated network after training 25 epochs was plotted in Fig. 5e and f. High image recognition accuracies of 94% for small images (Fig. 5e) and 88% for large images (Fig. 5f) were obtained. Although the recognition accuracy is comparable to recently reported results in  $\alpha$ -MoO<sub>3</sub> based synaptic devices,<sup>19–21</sup> further works are still required to optimize the linearity and symmetry of analogy switching in this device to increase the image recognition accuracy. Finally, the properties of our  $\alpha$ -MoO<sub>3</sub> synaptic transistor were compared with those of other devices reported in the literature, which were summarized in Table 1.<sup>19–21,26,27,43–45</sup> Our solid-state device shows a high stability and good recognition accuracy. What's more, no ionic liquid and organic material is adopted in our device, which make it more compatible with current semiconductor processes.

## Conclusion

In summary, an all-solid-state synaptic transistor based on single phase  $\alpha$ -MoO<sub>3</sub> thin film prepared by magnetron sputtering is designed and fabricated. Four orders of reversible conductance modulation is realized experimentally in the  $\alpha$ -MoO<sub>3</sub> thin film by H<sup>+</sup> ions intercalation/deintercalation. Several essential synaptic behaviors in biological synapse, including STP, LTP/LTD and SNDP are successfully mimicked in our device. An artificial neural network based on  $\alpha$ -MoO<sub>3</sub> based synaptic transistor was constructed to perform supervised learning. High recognition accuracies of 94% and 88% were achieved for Handwritten Digits data set (small images) and MNIST data set (large images), respectively. In addition, both channel material and electrolyte material in this device are prepared by magnetron sputtering, which is compatible with modern semiconductor technology. This work can pave the way for large scale production of quasi-2D material for practical application in synaptic transistor device.

## Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

This work was supported by the National Natural Science Foundation of China (92164206, 11774202), the Shandong Provincial Major Scientific and Technological Innovation Project (2019JZZY020211), the National Key R&D Program of China (2016YFA0301204) and the 111 Project (B13029).

## References

- 1 J. K. Li, C. Ge, J. Y. Du, C. Wang, G. Z. Yang and K. J. Jin, *Adv. Mater.*, 2020, **32**, 1905764.

- 2 H. L. Park, Y. Lee, N. Kim, D. G. Seo, G. T. Go and T. W. Lee, *Adv. Mater.*, 2020, **32**, 1903558.

- 3 C. Mead, *Proc. IEEE*, 1990, **78**, 1629–1636.

- 4 G. Wulfram, S. Henning and D. Gustavo, *Science*, 2012, **338**, 60–65.

- 5 Y. LeCun, Y. Bengio and G. Hinton, *Nature*, 2015, **521**, 436–444.

- 6 H. F. Ling, D. A. Koutsouras, S. Kazemzadeh, Y. van de Burgt, F. Yan and P. Gkoupidenis, *Appl. Phys. Rev.*, 2020, **7**, 011307.

- 7 R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous and A. R. Leblanc, *IEEE J. Solid-State Circuits*, 1974, **9**, 256–268.

- 8 I. Ferain, C. A. Colinge and J. P. Colinge, *Nature*, 2011, **479**, 310–316.

- 9 B. Radisavljevic, M. B. Whitwick and A. Kis, *ACS Nano*, 2011, **5**, 9934–9938.

- 10 W. J. Yu, Z. Li, H. Zhou, Y. Chen, Y. Wang, Y. Huang and X. Duan, *Nat. Mater.*, 2013, **12**, 246–252.

- 11 A. D. Franklin, *Science*, 2015, **349**, aab2750.

- 12 E. Liu, Y. Fu, Y. Wang, Y. Feng, H. Liu, X. Wan, W. Zhou, B. Wang, L. Shao, C. H. Ho, Y. S. Huang, Z. Cao, L. Wang, A. Li, J. Zeng, F. Song, X. Wang, Y. Shi, H. Yuan, H. Y. Hwang, Y. Cui, F. Miao and D. Xing, *Nat. Commun.*, 2015, **6**, 6991.

- 13 W. Cao, J. Kang, D. Sarkar, W. Liu and K. Banerjee, *Int. Electron Devices Meet.*, 2015, **62**, 3459–3469.

- 14 S. J. Liang, B. Cheng, X. Cui and F. Miao, *Adv. Mater.*, 2019, **32**, 1903800.

- 15 C. Pan, C. Y. Wang, S. J. Liang, Y. Wang, T. Cao, P. Wang, C. Wang, S. Wang, B. Cheng, A. Gao, E. Liu, K. Watanabe, T. Taniguchi and F. Miao, *Nat. Electron.*, 2020, **3**, 383–390.

- 16 I. A. De Castro, R. S. Datta, J. Z. Ou, A. Castellanos-Gomez, S. Sriram, T. Daeneke and K. Kalantar-zadeh, *Adv. Mater.*, 2017, **29**, 1701619.

- 17 P. F. Garcia and E. M. McCarron, *Thin Solid Films*, 1987, **155**, 53–63.

- 18 K. Kalantar-zadeh, J. Tang, M. Wang, K. L. Wang, A. Shailos, K. Galatsis, R. Kojima, V. Strong, A. Lech, W. Wlodarski and R. B. Kaner, *Nanoscale*, 2010, **2**, 429–433.

- 19 C. S. Yang, D. S. Shang, N. Liu, G. Shi, X. Shen, R. C. Yu, Y. Q. Li and Y. Sun, *Adv. Mater.*, 2017, **29**, 1700906.

- 20 C. S. Yang, D. S. Shang, N. Liu, E. J. Fuller, S. Agrawal, A. A. Talin, Y. Q. Li, B. G. Shen and Y. Sun, *Adv. Funct. Mater.*, 2018, **28**, 1804170.

- 21 Z. Wang, R. Yang, H. M. Huang, H. K. He, J. Shaibo and X. Guo, *Adv. Electron. Mater.*, 2020, **6**, 1901290.

- 22 R. Shimizu, K. Yamamoto, T. Suzuki, T. Ohsawa, S. Shiraki and T. Hitosugi, *Thin Solid Films*, 2015, **595**, 153–156.

- 23 C. V. Ramana, V. V. Atuchin, L. D. Pokrovsky, U. Becker and C. M. Julien, *J. Vac. Sci. Technol. A*, 2007, **25**, 1166–1171.

- 24 H. Y. Xu, M. K. Akbari, Z. Y. Hai, Z. H. Wei, L. Hyde, F. Verpoort, C. Y. Xue and S. Zhuiykov, *Mater. Des.*, 2018, **149**, 135–144.

- 25 S. L. Dai, Y. W. Zhao, Y. Wang, J. Y. Zhang, L. Fang, S. Jin, Y. L. Shao and J. Huang, *Adv. Funct. Mater.*, 2019, **29**, 1903700.

26 X. Deng, S. Q. Wang, Y. X. Liu, N. Zhong, Y. H. He, H. Peng, P. H. Xiang and C. G. Duan, *Adv. Funct. Mater.*, 2021, **31**, 2101099.

27 Z. F. Wu, P. Shi, R. F. Xing, T. L. Yu, L. Zhao, L. Wei, D. Wang, S. S. Yan, Y. F. Tian, L. H. Bai and Y. X. Chen, *Adv. Electron. Mater.*, 2022, 2200078.

28 A. E. Pereda, *Nat. Rev. Neurosci.*, 2014, **15**, 250–263.

29 L. Wang, S. R. Lu and J. Wen, *Nanoscale Res. Lett.*, 2017, **12**, 1–22.

30 M. T. Huang, A. J. Tan, F. Büttner, H. Liu, Q. F. Ruan, W. Hu, C. Mazzoli, S. Wilkins, C. H. Duan, J. Yang and G. Beach, *Nat. Commun.*, 2019, **10**, 5030.

31 A. J. Tan, M. T. Huang, C. O. Avci, F. Büttner, M. Mann, W. Hu, C. Mazzoli, S. Wilkins, H. L. Tuller and G. Beach, *Nat. Mater.*, 2019, **18**, 35–41.

32 H. F. Cheng, M. C. Wen, X. C. Ma, Y. Kuwahara, K. Mori, Y. Dai, B. B. Huang and H. Yamashita, *J. Am. Chem. Soc.*, 2016, **138**, 9316–9324.

33 L. Y. Xie, Q. Zhu, G. Z. Zhang, K. Ye, C. W. Zou, O. V. Prezhdo, Z. W. Wang, Y. Luo and J. Jiang, *J. Am. Chem. Soc.*, 2020, **142**, 4136–4140.

34 K. Xu, N. B. Liao, W. Xue and H. M. Zhou, *Int. J. Hydrogen Energy*, 2020, **45**, 9252–9259.

35 J. T. Yang, C. Ge, J. Y. Du, H. Y. Huang, M. He, C. Wang, H. B. Lu, G. Z. Yang and K. J. Jin, *Adv. Mater.*, 2018, **30**, 1801548.

36 Y. van de Burgt, E. Lubberman, E. J. Fuller, S. T. Keene, G. C. Faria, S. Agarwal, M. J. Marinella, A. Alec Talin and A. Salleo, *Nat. Mater.*, 2017, **16**, 414–418.

37 I. T. Wang, C. C. Chang, L. W. Chiu, T. Chou and T. H. Hou, *Nanotechnology*, 2016, **27**, 365204.

38 P. Shi, D. Wang, T. L. Yu, R. F. Xing, Z. F. Wu, S. S. Yan, L. Wei, Y. X. Chen, H. X. Ren, C. F. Yu and F. J. Li, *Mater. Des.*, 2021, **210**, 110022.

39 G. W. Burr, R. M. Shelby, S. Sidler, C. Nolfo, J. Jang, I. Boybat, R. S. Shenoy, P. Narayanan, K. Virwani, E. U. Giacometti, B. N. Kurdi and H. Hwang, *IEEE Trans. Electron Devices*, 2015, **62**, 3498–3507.

40 K. Bache and M. Lichman, *UCI machine learning repository*, University of California at Irvine, School of Information and Computer Science, Irvine, CA, 2016.

41 Y. LeCun, L. Bottou, Y. Bengio and P. Haffner, *Proc. IEEE*, 1998, **86**, 2278–2324.

42 E. J. Fuller, F. E. Gabaly, F. Léonard, S. Agarwal, S. J. Plimpton, R. B. Jacobs-Gedrim, C. D. James, M. J. Marinella and A. A. Talin, *Adv. Mater.*, 2017, **29**, 1604310.

43 B. L. Wang, X. W. Wang, E. Z. Wang, C. Y. Li, R. X. Peng, Y. H. Wu, Z. Q. Xin, Y. F. Sun, J. Guo, S. S. Fan, C. Wang, J. S. Tang and K. Liu, *Nano Lett.*, 2021, **21**, 10400–10408.

44 D. Xiang, T. Liu, X. M. Zhang, P. Zhou and W. Chen, *Nano Lett.*, 2021, **21**, 3557–3565.

45 N. Mohta, A. Rao, N. Remesh, R. Muralidharan and D. N. Nath, *RSC Adv.*, 2021, **11**, 36901–36912.