# **Nanoscale**

PAPER View Article Online

Cite this: Nanoscale, 2022, 14, 1432

# Fabrication of voltage-gated spin Hall nano-oscillators

Akash Kumar, (1)\*\* Mona Rajabali, Victor Hugo González, Mohammad Zahedinejad, Afshin Houshang and Johan Åkerman\*\*

We demonstrate an optimized fabrication process for electric field (voltage gate) controlled nano-constriction spin Hall nano-oscillators (SHNOs), achieving feature sizes of <30 nm with easy to handle ma-N 2401 e-beam lithography negative tone resist. For the nanoscopic voltage gates, we utilize a two-step tilted ion beam etching approach and through-hole encapsulation using 30 nm  $HfO_x$ . The optimized tilted etching process reduces sidewalls by 75% compared to no tilting. Moreover, the  $HfO_x$  encapsulation avoids any sidewall shunting and improves gate breakdown. Our experimental results on W/CoFeB/MgO/SiO<sub>2</sub> SHNOs show significant frequency tunability (6 MHz V<sup>-1</sup>) even for moderate perpendicular magnetic anisotropy. Circular patterns with diameter of 45 nm are achieved with an aspect ratio better than 0.85 for 80% of the population. The optimized fabrication process allows incorporating a large number of individual gates to interface to SHNO arrays for unconventional computing and densely packed spintronic neural networks

Received 13th November 2021, Accepted 24th December 2021 DOI: 10.1039/d1nr07505e

rsc.li/nanoscale

### 1 Introduction

The discoveries of the spin Hall effect (SHE)1-3 and the associated spin-orbit torque (SOT)4-6 have played a crucial role in shaping recent research in spintronics.<sup>7,8</sup> Pure spin currents generated by the SHE in heavy metals (such as Pt, W, Ta etc.)9-11 can generate anti-damping SOT in an adjacent ferromagnetic layer, counteract its Gilbert damping, and drive its magnetization into different types of auto-oscillatory precessional motion. 12-14 This has resulted in a new class of nanoscopic wide-band microwave oscillators known as spin Hall nano-oscillators (SHNOs), 13-25 which may be viewed as successors to the earlier spin torque nano-oscillators. 17,26 SHNOs have been studied in a wide range of geometries such as nano-pillars, 12 nano-gaps, 13,16 nano-wires 14,27,28 and nano-constrictions, <sup>15,19</sup> where the nano-constrictions stand out as particularly promising and versatile thanks to their ease of fabrication, direct optical access to the magnetodynamical region, 15,23,29,30 a propensity for mutual synchronization in linear chains<sup>31</sup> and two-dimensional arrays,<sup>32</sup> affording them an order of magnitude higher quality factors, easy implementation of neuromorphic computing concepts. 32-37

Thanks to voltage controlled magnetic anisotropy (VCMA), <sup>38-42</sup> low-power manipulation of spintronic devices can be efficiently implemented <sup>43-45</sup> and the use of voltage gates has been studied in detail for faster magnetization switching, <sup>40</sup> control of spin-orbit torque <sup>46</sup> and spin accumulation. <sup>44</sup> Voltage control of SHNOs was first reported in nano-gap SHNOs, <sup>47</sup> where a large gate underneath the ferromagnetic layer could control the frequency. Recent experimental demonstrations of giant voltage control of SHNOs also reveals an efficient modulation of damping using electric field biasing. <sup>48</sup> Further memristive control of SHNO arrays using resistive switching across voltage gates realizes synaptic neural network based on these oscillators and also shows a path for neuromorphic computing. <sup>34</sup>

Large scale fabrication of nano-electronic devices requires an extensively optimized fabrication process with stable materials. Our previously reported fabrication of large SHNO arrays<sup>32</sup> was performed using high contrast HSQ 2% resist, which is not only expensive but requires storage at low temperature and careful handling for stable results.<sup>49</sup> Apart from this, HSQ resist forms poor quality SiO<sub>2</sub> after the electron beam lithography (EBL) exposure and development,<sup>50</sup> which does not fit the scope of voltage-controlled devices. To circumvent these problems, we have optimized the fabrication process, taking advantage of the widely used and easy to handle ma-N 2401 negative tone EBL resist.<sup>51,52</sup>

In this article, we first discuss the fabrication process flow for voltage-controlled SHNOs. The optimized process provides a complete encapsulation of the gate terminal from the side-

<sup>&</sup>lt;sup>a</sup>Applied Spintronics Group, Department of Physics, University of Gothenburg, 412 96 Gothenburg, Sweden. E-mail: akash.kumar@gu.se, johan.akerman@gu.se <sup>b</sup>NanOsc AB, Stockholm, Sweden

walls of the SHNO metallic layers using tilted ion beam etching (IBE) at two different angles followed by additional over-etching. A 30 nm of through-hole encapsulation using  $\mathrm{HfO}_x$  significantly lowers the shunting events. It allows us to apply voltages as high as 8 V and paves the way for highly dense spintronic neural networks. This approach can also be implemented in other voltage-controlled SOT devices as well as SOT magnetic random access memories (SOT-MRAMs). Furthermore, we discuss results of applying voltage to W/CoFeB/MgO based SHNOs with a moderate perpendicular magnetic anisotropy (PMA) ( $M_{\mathrm{eff}}$  = 0.45 T) where we observe a substantial (6 MHz V<sup>-1</sup>) modulation of the operational frequency.

## 2 Experimental technique

Nanoscale

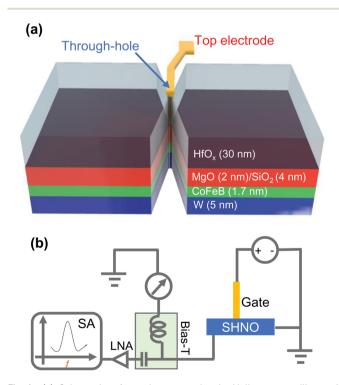

Fig. 1(a) shows a schematic of a voltage-controlled nano-constriction based SHNO. To fabricate these devices, we first deposit thin film heterostructures of W (5 nm)/CoFeB (1.4 nm)/MgO (2 nm)/SiO $_2$  (4 nm) on a high-resistance silicon substrate (HR-Si) ( $\rho$  = 10 000  $\Omega$  cm) using a magnetron sputtering system with a base vacuum of 2  $\times$  10 $^{-8}$  Torr. HR-Si provides good heat conductivity and CMOS compatibility. The stacks are annealed at 300° C for an hour to provide a moderate perpendicular magnetic anisotropy. The effective magnetization

**Fig. 1** (a) Schematic of a voltage-gated spin Hall nano-oscillator. A groove-like through-hole is defined in the  $HfO_x$  30 nm layer for the nano-gate geometry. The top contact DC line for the gate electrode is defined using Pt (5 nm)/Cu (40 nm)/Pt (2 nm). (b) Measurement set-up for analyzing the SHNO auto-oscillations vs. magnetic field, drive current, and gate voltage.

and Gilbert damping of the thin films were measured using ferromagnetic resonance (FMR) spectroscopy. Nano-constriction SHNOs are fabricated using a Raith EBPG 5200 100 keV EBL system. Then, an Oxford Dry etch 400 Plus Ar-ion beametching is used to etch the materials, followed by an optical lithography using a laser writing system to define the top contacts. The fabrication process involves three EBL steps to define mesa, encapsulation through-holes and their DC lines. To achieve high-precision placement of gate holes and the corresponding DC lines, the chip mark detection method along with global mark detection for top contacts are employed. We utilize Pt (5 nm)/Cu (40 nm)/Pt (2 nm) as the DC lines to the electric field gate electrodes and a bilayer of Cu (500 nm)/Pt (20 nm) as top contacts.

Auto-oscillation measurements are performed using our custom-designed probe station with Rohde & Schwarz 40 GHz spectrum analyzer connected to a low-noise amplifier (LNA) [see Fig. 1(b)]. The in-plane current is provided using Keithley 6221 current source and the Bias-T is utilized to separate the AC and DC counterparts. The gate voltage is applied *via* a Keithley 2400 source-meter using separate probe connected to electric gates.

## 3 Fabrication process

As the fabrication of these devices requires high-precision alignment of various fabrication steps, we utilized the chip mark detection method in EBL to write patterns with an accuracy of about 5 nm. For chip mark detection, four square markers of 10 × 10 μm<sup>2</sup> are defined with a center-tocenter (CC) separation of 100 µm in a square configuration using 50 nm Ta layer for high contrast detection over our SHNO stack. The patterns are then written in the centre of these markers. The chip markers are written together with global markers in the first stage of EBL exposure on UVN 2300 negative tone deep UV resist, followed by controlled etching of the Ta layer (to provide high contrast and sharp edges). For device fabrication, we have developed and optimized the EBL process for maN 2401 EBL resist to deliver ultra-small and dense features. Fig. 2(a-c) shows, scanning electron microscope (SEM) images of EBL lithography on 70 nm maN 2401 resist. Highly selective and dense circular patterns as small as 45 nm with a CC separation of 30 nm can be achieved.

The fabrication quality of the intended structures was evaluated through an automated process of the SEM images. Using the Python distribution of the OpenCV open source computer vision library, we filtered and binarized the contours of the circular patterns fabricated using maN 2401 EBL resist and fitted ellipses over them, as seen in the inset of Fig. 2(d). Their aspect ratio and eccentricity helps us quantify how much the final patterns resemble the intended patterns (perfectly circular and evenly spaced). We found that an overwhelming majority of the circles present an aspect ratio very close to unity, with more than 80% of 45 nm circles separated by

Paper

(c) 100 nm (d) 20 (s) 15 (s) 1

Fig. 2 SEM images of the optimized high contrast fabrication process using 70 nm, ma-N 2401 negative tone EBL resist: (a) 45 nm circular patterns optimized with separation of 30 nm, (b) 60 nm circular patterns with 40 nm separation, and (c) 100 nm circular patterns with 50 nm separation. (d) Population distribution of the circle aspect ratio, analyzed using image processing. Inset shows a single circular pattern and how the image analysis fits an ellipse to its perimeter.

30 nm having aspect ratios of at least 0.85, [as shown in Fig. 2(d)]. The bigger patterns showed an even better aspect ratio. The optimized fabrication process is utilized for defining SHNO mesa and DC lines for gate electrodes.

#### 3.1 Fabrication of spin Hall nano-oscillators

Fabrication of voltage-controlled SHNOs starts by preparing the sample for EBL. Before spin coating ma-N 2401 negative tone resist at 7000 rpm for 60 s, the sample is dehydrated using 1 min of oxygen plasma cleaning at RF power of 100  $W_{\rm RF}$ , and 250 mTorr oxygen pressure. To improve resist adhesion to the sample, HMDS (hexamethyldisilazane) vapor coating at 100 °C is utilized. Using EBL, we define a mesa of  $4\times12~\mu{\rm m}^2$  with a bow-tie shaped nano-constriction of 180 nm in the centre. Samples were then developed for 45 s in maD-525. Fig. 3(a) shows the SEM image of the nano-constriction mesa. An optimized EBL dose of 1800  $\mu{\rm C~cm}^{-2}$  with a beam step size of 4 nm is used to define required feature sizes with 3 nA beam current.

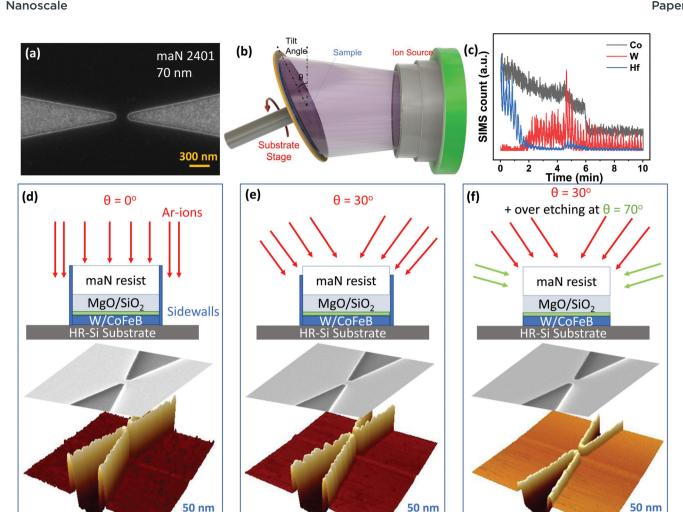

#### 3.2 Controlled ion-beam etching

As the SHNOs require a nano-constriction beneath the voltage-controlled gate of similar size, an optimized IBE is necessary to minimize the fence-like structure formed by sidewall redepositions. This sidewall cleaning not only reduces the current shunting through the gate, but also leads to sharper edges and better profile at the nano-constriction region. Fig. 3(b) shows the schematic of the IBE process, where the  $\theta$  represents the out-of plane angle with respect to film plane. The IBE process is carried out at a beam current  $I_{\text{beam}} = 10 \text{ mA}$

and beam voltages  $V_{\text{beam}} = 500 \text{ V}$ , for a controlled etching process and minimized heating effects on the EBL resist. A constant plate rotation of 5 rpm is used for uniform etching at tilted angles. To study the sidewall formation as a function of tilt angle, we performed IBE at multiple tilt angles and measured the sidewall profile using atomic force microscopy (AFM). As shown in Fig. 3(d), for  $\theta = 0^{\circ}$  tilt, a substantial 43 nm of sidewall is formed. Increasing the tilt angle to  $\theta = 30^{\circ}$ [Fig. 3(e)] reduces the sidewall to 36 nm, which is still quite high and will shunt the nanoscopic gates. To further reduce the vertical sidewalls, we employed a two angle IBE process. The initial etching is performed at  $\theta = 30^{\circ}$  to etch the SiO<sub>2</sub> (4 nm)/MgO (2 nm)/CoFeB (1.4 nm)/W (5 nm), until the secondary-ion mass spectrometer signal for W starts to decline and achieve half strength of its peak value, as shown in Fig. 3(c). This low inclined angle provides uniform etching without reducing the lateral size of the nanoconstriction while removing the side walls to some extent. To remove the side walls completely, tilt angle is increased to 70° and IBE is continued for another 4 minutes. Sidewall height in this case is <10 nm. The sudden change in secondary-ion mass spectrometry intensity at time 6 minutes is because of the tilt angle change from 30° to 70°. When contrasted with constant angle processes [Fig. 3(d and e)], this method provides 75% reduction in sidewalls, as observed by AFM and SEM images [Fig. 3(f)] of after etching and resist removal (carried out using oxygen plasma cleaning for 1 min at 250 mTorr oxygen pressure). A similar approach for fabrication of three terminal magnetic tunnel junctions was realized recently, 54,55 where significant improvement in the tunnel magneto resistance and

0.9

Aspect ratio

0.95

Fig. 3 (a) SEM image of a single 180 nm nano-constriction SHNO using 70 nm thick ma-N 2401 negative tone EBL resist. (b) Schematic of the ion beam etcher (IBE) configuration with its main components. (c) Secondary-ion mass spectrometry signal of various thin film layers during the IBE process. Stack schematic with IBE configurations, SEM images and corresponding AFM image at (d) 0° angle, resulting in large sidewalls of 45 nm, (e) 30° angle resulting in moderate sidewalls of 30-36 nm, and (f)  $30^{\circ} + 4$  minutes over etching at  $70^{\circ}$ , which reduces the sidewalls dramatically to less than 10 nm as clearly seen in the AFM images.

shape of magnetic tunnel junctions is observed with tilted ion beam etching.

#### 3.3 Gate definition and encapsulation

Defining a gate is a critical step for voltage control devices. To have individual access to each of the nanoconstrictions in a 2-dimensional array of SHNOs, it is necessary to make a densely packed gate electrode network. To realize this, we utilize groove like through-hole in the 30 nm HfOx, etched using IBE. This method provides the encapsulation from the sidewalls of the SHNOs along with a complete insulation from the HR-Si. After etching the nano-constriction mesa, a 30 nm HfOx oxide layer is deposited over the whole stack for the encapsulation of the gate contacts. A hole of 150 nm diameter is then defined by EBL in the centre of the nano-constriction region using 100 nm thick AR-P 6200.13 1:1 resist<sup>56</sup> (spin coated at 6000 rpm for 60 s). AR-P resist is a high contrast positive tone EBL resist that helps in defining sharp hole profiles for the nano-scale sizes. Fig. 4(a) shows a cut-through schematic and a SEM image of a hole defined using AR-P resist in the centre of a SHNO nano-constriction covered with 30 nm HfO<sub>x</sub>. At the same time with the holes, we also define large vias  $(4 \times 2 \mu m^2)$  at the edge of SHNO mesa to provide electrical access to the SHNO devices. The AR-P resist requires a lower electron dose of 210 μC cm<sup>-2</sup> compared to ma-N 2401, and is developed in n-amyle acetate solution for 2 minutes. The process is followed by a short rinse in iso-propyl alcohol (IPA). After the EBL, the etching of  $HfO_x$  is performed using the same IBE process but at  $\theta = 0^{\circ}$  and 5 RPM plate rotation throughout the etching process, to obtain a sharp and uniform profile for the hole. Fig. 4(b) depicts the schematic and SEM of the device after etching the encapsulation material. To precisely control the etching process and prevent over-etching the  $HfO_x$ , we deposit 30 nm  $HfO_x$  on a reference

Paper

(a) ARP resist

(b) Crop Electrode

With ARP 100 nm

150 nm

150 nm

150 nm

Fig. 4 Vertical cut-through schematic and SEM images of (a) through-hole defined using 100 nm AR-P resist, (b) the hole in the 30 nm  $HFO_x$  layer after etching, and (c) gate top contacts defined using 70 nm, ma-N 2401 resist over the gate hole. The two rectangular voids on the sides are used for signal (S) and ground (G) contacts. (d) Schematic and optical image of the final gated SHNO; the ground line is shared between the gate ( $G_g$ ) and the SHNO (G). Precise alignment of these layers with less than 5 nm shift was achieved with the EBL chip alignment method described in the text.

sample [Si/Ta (10 nm)] and concurrently etch the reference and the main sample. The etching of  $HfO_x$  is stopped as soon as the secondary-ion mass spectrometer signal for Ta starts to rise.

Later on, after AR-P resist removal with oxygen plasma, a Pt (5 nm)/Cu (40 nm)/Pt (2 nm) sandwich is deposited using magnetron sputtering to define the DC gate line. The optimized EBL process using negative tone maN 2401 resist (as discussed in section III) is utilized for patterning DC lines on top of the defined through-hole. Later, these layers are etched using IBE. Thanks to the chip alignment marks a precise alignment of gate hole and DC lines are achieved to the centre of SHNO nano-contriction [see SEM in Fig. 4(c)]. Fig. 4(d) shows the schematic and optical image of the final device, where lower contact pads are used to bias the SHNOs and upper contact pads can be used for the electric field gating of the SHNOs. Both the voltage gate and the SHNO share the same ground line.

## 4 Voltage control of W/CoFeB/MgO/ SiO<sub>2</sub> based SHNO

In this final section, we discuss the characteristics of the gated SHNOs and their voltage control. Fig. 5(a) first shows that the anisotropic magnetoresistance (AMR) of the SHNO is 0.27% AMR confirming that the gate process has not deteriorated its static properties. Here,  $\varphi$  denotes the in-plane magnetic field angle. Fig. 5(b) then shows the power spectral density (PSD) of the SHNO auto-oscillation as a function of external magnetic field (H) at an ( $\theta$  = ) 75° out-of plane (OOP) angle and a drive current of  $I_{\rm DC}$  = 0.7 mA. As expected, the applied field strength has a very large tuning effect on the fre-

quency. The frequency can be further tuned from 6 to 22 GHz by also varying the OOP angle (not shown). Fig. 5(c) shows the PSD of the auto-oscillations as a function of drive current at H = 0.85 T and 75° OOP angle and the typical non-monotonic current dependence due to edge-to-center mode expansion. The double-sided orange arrow indicates the field and current operating point for the subsequent voltage gated measurement as well as the frequency range that a voltage change from -4 to +4 V is able to cover. The 4 V of voltage bias results in 6.66 MV cm<sup>-1</sup> of electric field at the MgO (2 nm)/ SiO<sub>2</sub> (4 nm) dielectric thickness. Fig. 5(d) shows the actual PSD measurement vs. gate voltage and how the frequency can be tuned up to 6 MHz V<sup>-1</sup>. This value is slightly lower than previously reported<sup>48</sup> because of a significantly weaker PMA  $(M_{\rm eff} = 0.45 \text{ T})$  which results in weaker geometry based amplification of the VCMA. However, we have shown that efficient nano-gating can be realized compared to the broader top gating using different oxides which results in excessive oxide thickness and poor dielectric behavior. 57,58 Moreover, the nanoscopic dimension of the electric gates will now allow much better and reproducible VCMA control and can be scaled to a large number of SHNOs. Larger tunability can be achieved by optimizing the PMA strength of the HM/FM system.<sup>58</sup> The IV measurements of the gate voltage vs. leakage current are shown as an inset in Fig. 5(d). It is observed that only a negligible current of maximum 0.4 µA leaks at 4 V. The optimized process also allows application of up to ±8 V of voltage across the nano-constriction region at a cost of higher leakage current; this voltage range is a factor of 2-3 greater than previously reported.<sup>57</sup>

Memristive gating<sup>34</sup> with active resistive switching electrodes (*e.g.* Ti, Cu and others)<sup>59</sup> can be easily integrated with the present work flow. Such large arrays of SHNOs with individual

$I_{DC} = 0.8 \text{ mA}$ 817 (a) (b)  $\theta = 75^{\circ}$ 13 816.5  $\omega = 20^{\circ}$ Resistance (Ω) 816 3 815.5 2 815 360 180 240 300 0.7  $\varphi$  (degree) H (T) 14.3 0.9 mA (c) H = 0.85 T $\theta = 75^{\circ}$ 14.25  $\varphi$ = 20° 14.2 e (GHz) 14.15 14.1 14.05

Nanoscale Paper

Fig. 5 (a) AMR measurement of a 180 nm SHNO. (b) Auto-oscillation power spectral density (PSD) of the same SHNO vs. field at 0.7 mA and (c) vs. current at 0.85 T and 75° OOP angle. The orange line in (c) marks the operating point, and the arrow the achieved tuning range, for the voltage gated measurement shown in (d) where the SHNO frequency can be tuned about 50 MHz from -4 V to +4 V. The inset in (d) shows the I-V characteristic of the voltage gate

0.8

I<sub>DC</sub> (mA)

non-volatile nano-gates will pave the way for future densely packed synaptic neural network for large scale neuromorphic computing with spintronic oscillators.

sing for statistical calculations of fabricated structures. All authors co-wrote the manuscript.

## Conclusion

In summary, we have developed an optimized fabrication process for voltage gated spin Hall nano-oscillators and other spin-orbit torque devices. The two-step IBE process eliminates detrimental shunting from sidewalls and the HfO<sub>x</sub> throughhole provides good encapsulation of the gates from the sidewalls and substrate. The fabrication approach can also be easily adopted to spin-orbit torque-based magnetic tunnel junctions for better performance. We have also demonstrated significant voltage-controlled frequency tunability in a W/ CoFeB/MgO heterostructure with moderate perpendicular magnetic anisotropy. The optimized process flow can be utilized for parallel memristive gating of large SHNO arrays for neuromorphic and unconventional computing applications.

#### **Author contributions**

The study was devised by AK and JÅ. AK fabricated the devices and performed the experimental measurements with assistance from MR, MZ and AH. VHG performed the image proces-

#### Conflicts of interest

0

$V_{G}(V)$

There are no conflicts to declare.

# Acknowledgements

This work was partially supported by the Horizon 2020 Research and Innovation Programmes No. 835068 "TOPSPIN" and No. 899559 "SpinAge". This work was also partially supported by the Swedish Research Council (VR Grant No. 2016-05980) and the Knut and Alice Wallenberg Foundation.

## References

- 1 J. E. Hirsch, Phys. Rev. Lett., 1999, 83, 1834-1837.

- 2 Y. Tserkovnyak, A. Brataas and G. E. W. Bauer, Phys. Rev. Lett., 2002, 88, 117601.

- 3 J. Sinova, S. O. Valenzuela, J. Wunderlich, C. H. Back and T. Jungwirth, Rev. Mod. Phys., 2015, 87, 1213-1260.

- 4 P. Gambardella and I. M. Miron, Philos. Trans. R. Soc., A, 2011, 369, 3175-3197.

Paper

5 A. Manchon, J. Železný, I. M. Miron, T. Jungwirth, J. Sinova, A. Thiaville, K. Garello and P. Gambardella, *Rev. Mod. Phys.*, 2019, 91, 035004.

- 6 Q. Shao, P. Li, L. Liu, H. Yang, S. Fukami, A. Razavi, H. Wu, K. Wang, F. Freimuth, Y. Mokrousov, M. D. Stiles, S. Emori, A. Hoffmann, J. Åkerman, K. Roy, J.-P. Wang, S.-H. Yang, K. Garello and W. Zhang, *IEEE Trans. Magn.*, 2021, 57, 1–39.

- 7 B. Dieny, I. L. Prejbeanu, K. Garello, P. Gambardella, P. Freitas, R. Lehndorff, W. Raberg, U. Ebels, S. O. Demokritov, J. Akerman, A. Deac, P. Pirro, C. Adelmann, A. Anane, A. V. Chumak, A. Hirohata, S. Mangin, S. O. Valenzuela, M. C. Onbaşlı, M. d'Aquino, G. Prenat, G. Finocchio, L. Lopez-Diaz, R. Chantrell, O. Chubykalo-Fesenko and P. Bortolotti, *Nat. Electron.*, 2020, 3, 446–459.

- 8 V. E. Demidov, S. Urazhdin, A. Anane, V. Cros and S. O. Demokritov, *J. Appl. Phys.*, 2020, **127**, 170901.

- 9 L. Liu, T. Moriyama, D. C. Ralph and R. A. Buhrman, *Phys. Rev. Lett.*, 2011, **106**, 036601.

- 10 C.-F. Pai, L. Liu, Y. Li, H. W. Tseng, D. C. Ralph and R. A. Buhrman, Appl. Phys. Lett., 2012, 101, 122404.

- 11 A. Kumar, R. Sharma, K. I. Ali Khan, C. Murapaka, G. J. Lim, W. S. Lew, S. Chaudhary and P. K. Muduli, *ACS Appl. Electron. Mater.*, 2021, 3, 3139–3146.

- 12 L. Liu, C.-F. Pai, D. C. Ralph and R. A. Buhrman, *Phys. Rev. Lett.*, 2012, **109**, 186602.

- 13 V. E. Demidov, S. Urazhdin, H. Ulrichs, V. Tiberkevich, A. Slavin, D. Baither, G. Schmitz and S. O. Demokritov, *Nat. Mater.*, 2012, 11, 1028.

- 14 Z. Duan, A. Smith, L. Yang, B. Youngblood, J. Lindner, V. E. Demidov, S. O. Demokritov and I. N. Krivorotov, *Nat. Commun.*, 2014, 5, 1–7.

- 15 V. Demidov, S. Urazhdin, A. Zholud, A. Sadovnikov and S. Demokritov, *Appl. Phys. Lett.*, 2014, **105**, 172410.

- 16 M. Ranjbar, P. Dürrenfeld, M. Haidar, E. Iacocca, M. Balinskiy, T. Q. Le, M. Fazlali, A. Houshang, A. A. Awad, R. K. Dumas and J. Åkerman, *IEEE Magn. Lett.*, 2014, 5, 3000504.

- 17 T. Chen, R. K. Dumas, A. Eklund, P. K. Muduli, A. Houshang, A. A. Awad, P. Durrenfeld, B. G. Malm, A. Rusu and J. Åkerman, *Proc. IEEE*, 2016, **104**, 1919–1945.

- 18 H. Mazraati, S. Chung, A. Houshang, M. Dvornik, L. Piazza, F. Qejvanaj, S. Jiang, T. Q. Le, J. Weissenrieder and J. Åkerman, Appl. Phys. Lett., 2016, 109, 242402.

- 19 P. Dürrenfeld, A. a. Awad, A. Houshang, R. K. Dumas and J. Åkerman, *Nanoscale*, 2017, **9**, 1285–1291.

- 20 M. Zahedinejad, A. A. Awad, P. Dürrenfeld, A. Houshang, Y. Yin, P. K. Muduli and J. Åkerman, *IEEE Magn. Lett.*, 2017, 8, 3704804.

- 21 M. Zahedinejad, H. Mazraati, H. Fulara, J. Yue, S. Jiang, A. Awad and J. Åkerman, *Appl. Phys. Lett.*, 2018, **112**, 132404.

- 22 H. Mazraati, M. Zahedinejad and J. Åkerman, *Appl. Phys. Lett.*, 2018, **113**, 092401.

- 23 M. Haidar, A. A. Awad, M. Dvornik, R. Khymyn, A. Houshang and J. Åkerman, *Nat. Commun.*, 2019, **10**, 2362.

- 24 T. M. Spicer, P. S. Keatley, T. H. J. Loughran, M. Dvornik, A. A. Awad, P. Dürrenfeld, A. Houshang, M. Ranjbar, J. Åkerman, V. V. Kruglyak and R. J. Hicken, *Phys. Rev. B*, 2018, 98, 214438.

- 25 B. Divinskiy, V. E. Demidov, S. Urazhdin, R. Freeman, A. B. Rinkevich and S. O. Demokritov, *Adv. Mater.*, 2018, 30, 1802837.

- 26 A. Houshang, E. Iacocca, P. Dürrenfeld, S. R. Sani, J. Åkerman and R. K. Dumas, *Nat. Nanotechnol.*, 2016, 11, 280–286.

- 27 M. Evelt, C. Safranski, M. Aldosary, V. E. Demidov, I. Barsukov, A. P. Nosov, A. B. Rinkevich, K. Sobotkiewich, X. Li, J. Shi, I. N. Krivorotov and S. O. Demokritov, *Sci. Rep.*, 2018, 8, 1269.

- 28 J.-R. Chen, A. Smith, E. A. Montoya, J. G. Lu and I. N. Krivorotov, *Commun. Phys.*, 2020, 3, 187.

- 29 M. Dvornik, A. A. Awad and J. Åkerman, *Phys. Rev. Appl.*, 2018, 9, 014017.

- 30 T. Hache, T. Weinhold, K. Schultheiss, J. Stigloher, F. Vilsmeier, C. Back, S. S. P. K. Arekapudi, O. Hellwig, J. Fassbender and H. Schultheiss, *Appl. Phys. Lett.*, 2019, 114, 102403.

- 31 A. A. Awad, P. Dürrenfeld, A. Houshang, M. Dvornik, E. Iacocca, R. K. Dumas and J. Åkerman, *Nat. Phys.*, 2016, 13, 292–299.

- 32 M. Zahedinejad, A. Awad, S. Muralidhar, R. Khymyn, H. Fulara, H. Mazraati, M. Dvornik and J. Åkerman, *Nat. Nanotechnol.*, 2020, **15**, 47–52.

- 33 A. Houshang, M. Zahedinejad, S. Muralidhar, J. Chęciński, R. Khymyn, M. Rajabali, H. Fulara, A. A. Awad, M. Dvornik and J. Åkerman, *Phys. Rev. Appl.*, 2022, 17, 014003.

- 34 M. Zahedinejad, H. Fulara, R. Khymyn, A. Houshang, M. Dvornik, S. Fukami, S. Kanai, H. Ohno and J. Åkerman, *Nat. Mater.*, 2022, 21, 81–87.

- 35 U. Singh, N. Garg, S. Kumar, P. K. Muduli and D. Bhowmik, *AIP Adv.*, 2021, 11, 045117.

- 36 N. Garg, S. V. Hemadri Bhotla, P. K. Muduli and D. Bhowmik, *Neuromorph. Comput. Eng.*, 2021, 1, 024005.

- 37 D. I. Albertsson, M. Zahedinejad, A. Houshang, R. Khymyn, J. Åkerman and A. Rusu, Appl. Phys. Lett., 2021, 118, 112404.

- 38 H. Ohno, a. D. Chiba, a. F. Matsukura, T. Omiya, E. Abe, T. Dietl, Y. Ohno and K. Ohtani, *Nature*, 2000, **408**, 944–946.

- 39 M. Endo, S. Kanai, S. Ikeda, F. Matsukura and H. Ohno, *Appl. Phys. Lett.*, 2010, **96**, 212503.

- 40 W.-G. Wang, M. Li, S. Hageman and C. Chien, *Nat. Mater.*, 2012, 11, 64–68.

- 41 R. Liu, W. Lim and S. Urazhdin, *Phys. Rev. B: Condens. Matter Mater. Phys.*, 2014, **89**, 220409.

- 42 F. Matsukura, Y. Tokura and H. Ohno, *Nat. Nanotechnol.*, 2015, **10**, 209–220.

- 43 Y. Wu, K. Garello, W. Kim, M. Gupta, M. Perumkunnil, V. Kateel, S. Couet, R. Carpenter, S. Rao, S. Van Beek, K. K. Vudya Sethu, F. Yasin, D. Crotti and G. Kar, *Phys. Rev. Appl.*, 2021, 15, 064015.

Nanoscale

- 45 L. Chen, M. Gmitra, M. Vogel, R. Islinger, M. Kronseder, D. Schuh, D. Bougeard, J. Fabian, D. Weiss and C. Back, *Nat. Electron.*, 2018, 1, 350–355.

- 46 Y. Yan, C. Wan, X. Zhou, G. Shi, B. Cui, J. Han, Y. Fan, X. Han, K. L. Wang, F. Pan, et al., Adv. Electron. Mater., 2016, 2, 1600219.

- 47 R. Liu, L. Chen, S. Urazhdin, Y. Du, et al., Phys. Rev. Appl., 2017, 8, 021001.

- 48 H. Fulara, M. Zahedinejad, R. Khymyn, M. Dvornik, S. Fukami, S. Kanai, H. Ohno and J. Åkerman, *Nat. Commun.*, 2020, 11, 1–7.

- 49 S. Ma, C. Con, M. Yavuz and B. Cui, *Nanoscale Res. Lett.*, 2011, **6**, 1–6.

- 50 H. Namatsu, Y. Takahashi, K. Yamazaki, T. Yamaguchi, M. Nagase and K. Kurihara, J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct. – Process., Meas., Phenom., 1998, 16, 69–76.

- 51 B. Bilenberg, M. Schøler, P. Shi, M. S. Schmidt, P. Bøggild, M. Fink, C. Schuster, F. Reuther, C. Gruetzner and A. Kristensen, J. Vac. Sci. Technol., B: Microelectron.

- Nanometer Struct. Process., Meas., Phenom., 2006, 24, 1776-1779.

- 52 E. Toomey, M. Colangelo and K. K. Berggren, J. Vac. Sci. Technol., B: Nanotechnol. Microelectron.: Mater., Process., Meas., Phenom., 2019, 37, 051207.

- 53 M. Ji, L. Pan, Y. Hu, M. Pan, L. Yang, J. Peng, W. Qiu, J. Hu, Q. Zhang and P. Li, AIP Adv., 2019, 9, 085317.

- 54 H. Ren, S.-Y. Wu, J. Z. Sun and E. E. Fullerton, APL Mater., 2021, 9, 091101.

- 55 R. Islam, B. Cui and G.-X. Miao, J. Vac. Sci. Technol., B: Nanotechnol. Microelectron.: Mater., Process., Meas., Phenom., 2020, 38, 050801.

- 56 S. Thoms and D. S. Macintyre, J. Vac. Sci. Technol., B: Nanotechnol. Microelectron.: Mater., Process., Meas., Phenom., 2014, 32, 06FJ01.

- 57 H. Fulara, M. Zahedinejad, R. Khymyn, A. Awad, S. Muralidhar, M. Dvornik and J. Åkerman, *Sci. Adv.*, 2019, 5, eaax8467.

- 58 J.-G. Choi, J. Park, M.-G. Kang, D. Kim, J.-S. Rieh, K.-J. Lee, K.-J. Kim and B.-G. Park, *arXiv preprint rs*-840717, 2021.

- 59 M. Lübben and I. Valov, *Adv. Electron. Mater.*, 2019, 5, 1800933.