## **Nanoscale**

## CORRECTION

View Article Online

Cite this: Nanoscale, 2021, 13, 10608

## Correction: 12-state multi-level cell storage implemented in a 128 Mb phase change memory chip

Zhitang Song, \*a Daolin Cai, \*a Yan Cheng, b Lei Wang, c Shilong Lv, a Tianjiao Xin and Gaoming Feng<sup>c</sup>

DOI: 10.1039/d1nr90100a

rsc li/nanoscale

Correction for '12-state multi-level cell storage implemented in a 128 Mb phase change memory chip' by Zhitang Song et al., Nanoscale, 2021, DOI: 10.1039/d1nr00100k.

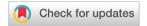

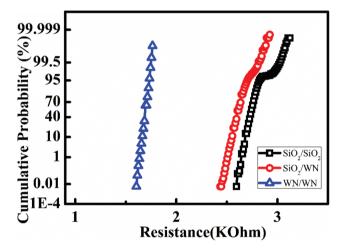

The authors regret that Fig. 2(a) and 4(a) of the original manuscript contained errors. In the previous Fig. 2(a), the blue curve was labelled as SiN/WN incorrectly - this should be changed to WN/WN. In addition, in Fig. 4(a), the red and blue curves are labelled SiO<sub>2</sub>/XY and XY/XY respectively, which contradicted the figure caption and the main text. These labels should be SiO<sub>2</sub>/ WN and WN/WN instead.

Updated versions of Fig. 2(a) and 4, with associated captions, are displayed below.

Fig. 2 TiN blade BEC electrical properties. (a) Cumulative probability distribution of resistance values for a 3 nm-thick TiN BEC with a quantity of 1k cells.

aState Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Micro-system and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China. E-mail: ztsong@mail.sim.ac.cn, caidl@mail.sim.ac.cn

bKey Laboratory of Polar Materials and Devices (MOE), Department of Electronics, East China Normal University, Shanghai 200241, China

<sup>&</sup>lt;sup>c</sup>Semiconductor Manufacturing International Corporation, Shanghai 201203, China

Nanoscale

(a) 10M (b) 7.0 Resistance(Ohm) 6.5 SiO<sub>2</sub>/WN 4.5 WN/WI 101 3 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 4 Log(Cycle\_Number) Current(mA) (c) (d) 6.5 Log(Resistance) og(Resistance) 6.0 5.5 Set 5.0 4.0 3.5

Fig. 4 128 Mb PCM chip performance. (a) Memory windows test of PCM devices with 3 types of coating layers. Endurance of PCM devices, and the BEC coating layers are: (b) SiO<sub>2</sub>/SiO<sub>2</sub>, (c) SiO<sub>2</sub>/WN, and (d) WN/WN.

The Royal Society of Chemistry apologises for these errors and any consequent inconvenience to authors and readers.

Log(Cycle\_Number)