# **RSC Advances**

## **PAPER**

View Article Online

View Journal | View Issue

Cite this: RSC Adv., 2019, 9, 35289

# Dielectric ceramics/TiO<sub>2</sub>/single-crystalline silicon nanomembrane heterostructure for high performance flexible thin-film transistors on plastic substrates

Guoxuan Qin, <sup>10</sup> \* Zhihui Pei, <sup>ab</sup> Yibo Zhang, <sup>ab</sup> Kuibo Lan, <sup>ab</sup> Quanning Li, <sup>c</sup> Lingxia Li, <sup>a</sup> Shihui Yu <sup>10</sup> and Xuejiao Chen\* <sup>c</sup>

A dielectric ceramics/ $TiO_2$ /single-crystalline silicon nanomembrane (SiNM) heterostructure is designed and fabricated for high performance flexible thin-film transistors (TFTs). Both the dielectric ceramics ( $Nb_2O_3 - Bi_2O_3 - MgO$ ) and  $TiO_2$  are deposited by radio frequency (RF) magnetron sputtering at room temperature, which is compatible with flexible plastic substrates. And the single-crystalline SiNM is transferred and attached to the dielectric ceramics/ $TiO_2$  layers to form the heterostructure. The experimental results demonstrate that the room temperature processed heterostructure has high quality because: (1) the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure has a high dielectric constant ( $\sim$ 76.6) and low leakage current. (2) The  $TiO_2$ /single-crystalline SiNM structure has a relatively low interface trap density. (3) The band gap of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure is wider than  $TiO_2$ , which increases the conduction band offset between Si and  $TiO_2$ , lowering the leakage current. Flexible TFTs have been fabricated with the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$ /SiNM heterostructure on plastic substrates and show a current on/off ratio over  $TiO_3$  threshold voltage of  $TiO_3$ 0, subthreshold swing (SS) as low as  $TiO_3$ 1 dieterostructure has great potential for high performance TFTs.

Received 21st August 2019 Accepted 20th October 2019

DOI: 10.1039/c9ra06572e

rsc.li/rsc-advances

### Introduction

Flexible electronics have drawn more and more interest and have been applied in a variety of applications including flexible displays, wearable devices, flexible photosensors, *etc.*<sup>1-6</sup> Single-crystalline silicon is considered to be the best candidate semiconductor material for flexible devices, for the advantages of high carrier mobility and being compatible with the industrial complementary metal oxide semiconductor (CMOS) process. Single-crystalline silicon nanomembrane (SiNM) has been employed in many flexible devices and circuits, *e.g.* flexible diodes,<sup>7</sup> flexible photodetectors<sup>8,9</sup> and flexible microwave switches.<sup>10</sup> In particular, flexible thin-film transistors (TFTs) are one of the most essential and fundamental devices, and flexible TFTs based on single-crystalline SiNM show great potential for high performance applications.<sup>11-15</sup>

However, limitations still exist for high performance flexible single-crystalline Si TFTs, *i.e.* high quality gate dielectric

materials and suitable structures designed for flexible devices. To date, the dielectric materials for flexible SiNM TFTs are mostly SiO<sub>r</sub> by low-temperature chemical vapor deposition (CVD) or SiO by evaporating, and have relatively low dielectric constant and electrical properties. 16,17 High-k dielectrics have been already used for high performance TFTs on bulk substrates, among which metal oxides are common, such as ZrO<sub>2</sub>, HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> as gate dielectric layer of TFT for a high current on/off ratio, low operating voltage and low power consumption.18-21 Investigations of high-k gate dielectrics on performance of CMOS and TFTs devices have been also conducted.22-25 However, most of these high-k materials are deposited by solution process or sputtering including postannealing (≥400 °C)<sup>18,19</sup> or atomic layer deposition (ALD)  $(\geq 300 \, ^{\circ}\text{C})^{20}$  which is incompatible with flexible substrates. Multilayer gate stacks with high-k and high band gap materials have been also investigated in recent years.26-34 The fabricating methods mainly include ALD, 28,29 solution process30,31 and sputtering.32-34 However, these multilayer structures are still not suitable for flexible TFTs. For example, ALD deposited or solution-processed gates with processing temperature at least 300 °C (such as TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> (ref. 28) and Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> (ref. 29) by ALD, TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> (TATAT)<sup>30</sup> and TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> (ref. 31) by solution process) exceed the maximum process

<sup>&</sup>quot;School of Microelectronics, Tianjin University, Tianjin, 300072, P. R. China. E-mail: gqin@tju.edu.cn

<sup>&</sup>lt;sup>b</sup>Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology, Tianjin, 300072, P. R. China

State Key Laboratory of Precision Measuring Technology and Instruments, Tianjin University, Tianjin, 300072, P. R. China. E-mail: chenxuejiao@tju.edu.cn

**RSC Advances**

temperature that flexible substrates can withstand. On the other hand, lowering the processing temperature or room-temperature magnetron sputtering will significantly degrade the electrical properties of these dielectrics, such as high trap density, higher leakage current, higher subthreshold swing and thus poor subthreshold characteristics, *etc.*<sup>32–34</sup> In addition, these single-layer or stacked dielectrics are mostly fabricated and employed for oxide semiconductor TFTs rather than Si TFTs. As a result, it is necessary to find high quality dielectric materials and design the gate structure with low process temperature for high performance flexible single-crystalline silicon TFTs.

In this paper, a dielectric ceramics/TiO<sub>2</sub>/single-crystalline SiNM heterostructure is designed and fabricated for high performance flexible TFT on plastic substrates. The dielectric ceramics Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO has relatively high dielectric constant and low leakage current. TiO<sub>2</sub> as a nontoxic and abundant ceramic material with high dielectric constant, high electrical properties and long-term stability has been applied in various optical and electrical fields, such as photocatalytic system, thin-film transistors and gas sensors.<sup>35-38</sup> In this work, both the dielectric ceramics Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO and TiO<sub>2</sub> are deposited by radio frequency (RF) magnetron sputtering at room temperature, which is compatible with the flexible plastic substrates. And the single-crystalline SiNM is transferred and attached to the dielectric ceramics/TiO<sub>2</sub> layers to form the heterostructure.

The flexible TFTs with dielectric ceramics Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM heterostructure on plastic substrates are fabricated and characterized. The experimental results demonstrate that the room-temperature processed heterostructure has high quality including: (1) the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/ TiO<sub>2</sub> heterostructure has high dielectric constant and low leakage current. (2) The TiO2/single-crystalline SiNM structure has relatively low interface trap density. (3) The band gap of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub> heterostructure is wider than TiO<sub>2</sub>, which increases the conduction band offset between Si and TiO<sub>2</sub>, lowering the leakage current. The flexible TFTs show a high current on/off ratio, low threshold voltage and subthreshold swing. The TFTs also indicate good performance stability under mechanical bending conditions. The results indicate that the dielectric ceramics/TiO<sub>2</sub>/SiNM heterostructure has great potential for high performance flexible TFTs.

## Experimental

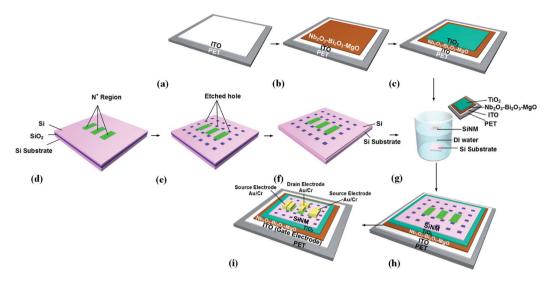

The fabrication process schematic of the flexible TFTs is shown in Fig. 1. The bottom-gate electrode indium-tin-oxide (ITO) ( $\sim\!100$  nm) was first deposited on polyethylene terephthalate (PET) substrate ( $\sim\!175~\mu m)$  by RF magnetron sputtering at room temperature. Then double gate dielectric layers Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO ( $\sim\!50$  nm) and TiO<sub>2</sub> ( $\sim\!50$  nm) were deposited from the Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO and TiO<sub>2</sub> ceramic targets by magnetron sputtering. The vacuum chamber was evacuated to 9.0  $\times$  10 $^{-6}$  torr before sputtering. Then high-purity Ar and O<sub>2</sub> from separated gas flow controller were introduced and the ratio of Ar/O<sub>2</sub> is 17 : 3. During the process of sputtering, the total pressure was

10 mTorr and the deposited power was set to be 100 W. The deposition parameters were optimized to achieve the best electrical properties for Nb2O3-Bi2O3-MgO and TiO2. The single-crystalline SiNM is the top template layer (~200 nm) of silicon on insulator (SOI) with buried oxide layer (~450 nm) and bottom Si handling substrate. The source and drain regions (N<sup>+</sup> regions) were first patterned on SOI by lithography process. Then phosphorus (P) ion implantation was carried out with 40 keV injection energy and  $4 \times 10^{15}$  cm<sup>2</sup> dose, followed by 45 min furnace annealing at 850  $^{\circ}$ C in  $N_2$  atmosphere. Next, a 15  $\mu$ m imes15 μm holes array with a pitch distance of 50 μm was etched on the top Si template layer by lithography and reactive iron etching (RIE). Afterward, SOI was put into diluted hydrofluoric acid (HF, 49% HF: water = 1:1) for 25 min to remove the buried oxide layer, after which the top SiNM was released from the handling substrate in deionized (DI) water, transferred and attached to Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub> gate dielectric layer on the plastic substrate. The source and drain electrodes with Cr ( $\sim$ 30 nm) and Au (~70 nm) stack were then deposited by electron beam evaporation. The frequency-capacitance and capacitance-voltage characteristics of the Nb2O3-Bi2O3-MgO/TiO2 and Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM heterostructures, as well as the direct-current (dc) characteristics of the flexible TFTs were measured by a Keithley 4200 SCS semiconductor characterization system. The spectra and band gap of Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/ TiO<sub>2</sub> heterostructure were measured using a UV-3600Plus ultraviolet-visible spectrophotometer.

## Results and discussion

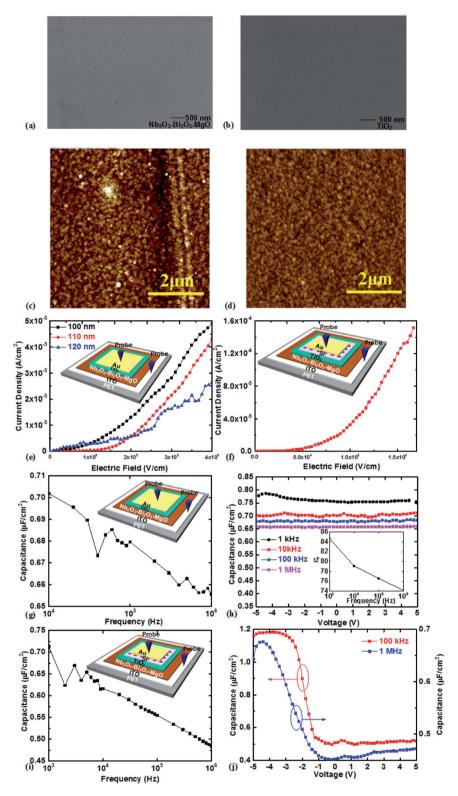

Fig. 2 shows the interface morphologies of  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  and the characteristics of  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  and  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2/SiNM$  heterostructures. The scanning electron microscope (SEM) images of interface morphologies of  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  are shown in Fig. 2a and b, respectively. The AFM images of  $Nb_2O_3$ – $Bi_2O_3$ –MgO and  $TiO_2$  layers are displayed in Fig. 2c and d. The calculated RMS of  $Nb_2O_3$ – $Bi_2O_3$ –MgO and  $TiO_2$  is  $\sim$ 4.13 nm and  $\sim$ 2.45 nm, respectively. The AFM image and RMS values show consistent results to the SEM data, indicating that the surface of  $TiO_2$  is much smoother than that of  $Nb_2O_3$ – $Bi_2O_3$ –MgO and has improved surface roughness to  $Nb_2O_3$ – $Bi_2O_3$ –MgO layer, which contributes to reducing the carrier scattering center and improving the interface quality with SiNM.

Fig. 2e shows the leakage current density of  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  heterostructure with different thickness, indicating low leakage current density of the heterostructure.  $\sim 100$  nm dielectrics is chosen in this work. Fig. 2f shows the leakage current density of the  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2/SiNM$  heterostructure, showing that the leakage current density is still very low even with the SiNM. The leakage current density of  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2/SiNM$  is lightly higher than that of  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$ , because SiNM is lightly P-doped in which there are carrier drift with applied voltage. Frequency–capacitance and capacitance–voltage characteristic of the  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  heterostructure at 1 kHz, 10 kHz, 100 kHz and 1 MHz are shown in Fig. 2g and h, respectively. The capacitance

**RSC Advances** Paper

Fig. 1 Process flow schematic of the flexible TFTs (drawn not to scale): (a) ITO deposited on the PET flexible substrate. (b) Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO deposited on the ITO/PET. (c) TiO<sub>2</sub> deposited on the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/ITO/PET. (d) Source and drain active regions patterned and doped on SOI. (e) Hole array patterned and etched. (f) Buried oxide layer removed in HF. (g) The top SiNM released in DI water. (h) SiNM transferred onto the TiO<sub>2</sub>/Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MqO/ITO/PET substrate. (i) Source and drain electrodes formed by evaporating Cr/Au (30 nm/70 nm)

slightly increases from  $\sim 0.655 \ \mu F \ cm^{-2}$  to  $\sim 0.75 \ \mu F \ cm^{-2}$  as frequency decreases from 1 MHz to 1 kHz, which indicates that the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub> heterostructure has low frequency sensitivity and the dielectric constant  $(\varepsilon_r)$  can be extracted from the following equation:

$$C_{\text{ox}} = \frac{\varepsilon_{\text{r}} \, \varepsilon_{0}}{t_{\text{ox}}} \tag{1}$$

where  $C_{\rm ox}$  is the unit capacitance of the heterostructure.  $\varepsilon_0$  is vacuum dielectric constant,  $t_{ox}$  is thickness of the heterostructure ( $\sim$ 100 nm).  $\varepsilon_{\rm r}$  is calculated to be  $\sim$ 74.2 at 1 MHz,  $\sim$ 76.6 at 100 kHz,  $\sim$ 79.1 at 10 kHz and  $\sim$ 84.7 at 1 kHz, respectively. The dielectric constant of the heterostructure is much higher than those of SiO, SiO<sub>x</sub> or most low-temperature processed dielectrics.

Frequency-capacitance and capacitance-voltage characteristic of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM heterostructure at 100 kHz and 1 MHz are shown in Fig. 2i and j, respectively. The capacitance of the heterostructure can be calculated as follows:

$$C = \left(\frac{1}{C_{\text{ox}}} + \frac{1}{C_{\text{Si}}}\right)^{-1} \tag{2}$$

where C is the capacitance of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM heterostructure, Cox is the capacitance of the Nb2O3-Bi2O3-MgO/TiO<sub>2</sub> heterostructure and C<sub>Si</sub> is the capacitance of SiNM, which is influenced by the depletion region width and inversion layer charge in SiNM. The capacitance of the Nb2O3-Bi2O3-MgO/TiO<sub>2</sub>/SiNM heterostructure decreases from  $\sim$ 0.72  $\mu$ F cm<sup>-2</sup> to  $\sim$ 0.47 µF cm $^{-2}$  with the frequency from 1 kHz to 1 MHz. The reason for this is that at low frequency, the mobile electrons accumulate in the surface of SiNM close to TiO2 and the capacitance of the heterostructure is almost same as  $C_{ox}$ .

The capacitance-voltage curves consist of accumulation and inversion regions at high frequency of 100 kHz and 1 MHz. When a negative gate voltage is applied, the capacitance works in accumulation region and it equals to  $C_{ox}$ . When the applied gate voltage increases, the inversion layer is formed at the Si/ TiO<sub>2</sub> interface and the capacitance of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/  $TiO_2/SiNM$  heterostructure is the series capacitances of  $C_{ox}$  and the depletion capacitance in SiNM. Therefore, the capacitance of the heterostructure decreases and eventually keep stable as the gate voltage increases.

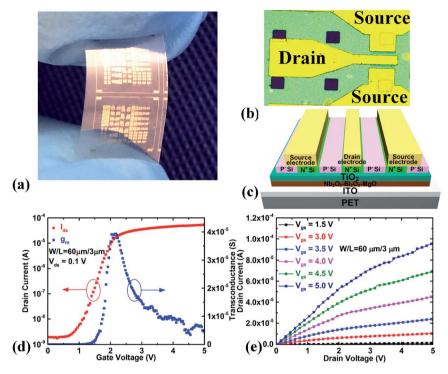

The optical image, microscope image and structure schematic of the flexible TFTs with Nb2O3-Bi2O3-MgO/TiO2/SiNM heterostructure fabricated on plastic substrates are shown in Fig. 3a-c, respectively. The transfer and I-V characteristics of TFT with channel width (W) and channel length (L) of 60  $\mu$ m and 3 µm are shown in Fig. 3d and e, respectively, as an example, in which  $I_{ds}$  is the drain current,  $g_{m}$  is the transconductance,  $V_{\rm ds}$  is the drain voltage and  $V_{\rm gs}$  is the gate voltage. The threshold voltage  $(V_{\rm th})$  extracted from Fig. 3d is  $\sim 1.2$  V, indicating that the flexible TFT has high drive capability. The saturation drain current of the flexible TFT is  $\sim$ 28  $\mu$ A with only ~nA leakage current when the gate voltage is 2.5 V, and the current on/off ratio is over 104. The maximum transconductance of the flexible TFT reaches to ~40 μS when gate voltage is 2.1 V. The subthreshold swing (SS) is calculated to be  $\sim 0.2 \text{ V dec}^{-1} \text{ by:}$

$$SS = \frac{\partial V_{gs}}{\partial (\lg (I_{ds}))}$$

(3)

The interfacial trap density  $(D_{it})$  can be calculated based on the SS value as follows:40

$$D_{\rm it} = \left(\frac{\text{SS} \times \lg e}{kT/q} - 1\right) \times \frac{C_{\rm ox}}{q^2} \tag{4}$$

RSC Advances Paper

Fig. 2 Surface morphologies and characteristics of  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  and  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2/SiNM$  heterostructures: (a) SEM image of surface morphology of  $Nb_2O_3 - Bi_2O_3 - MgO$ . (b) SEM image of surface morphology of  $TiO_2$ . (c) AFM image of surface morphology of  $Nb_2O_3 - Bi_2O_3 - MgO$ . (d) AFM image of surface morphology of  $TiO_2$ . (e) Leakage current density of  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure with different thickness. (f) Leakage current density of  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2/SiNM$  heterostructure. (g) Frequency-capacitance characteristics of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure. (h) Capacitance-voltage characteristics of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure. (i) Frequency-capacitance characteristics of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2/SiNM$  heterostructure. (j) Capacitance-voltage characteristics of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2/SiNM$  heterostructure.

**RSC Advances** Paper

Fig. 3 The optical image, microscope image, structure schematic and dc characteristics of the fabricated flexible TFTs: (a) the optical image of the flexible TFTs on a plastic substrate. (b) The microscope image of an example flexible TFT with double channels. (c) Structure schematic of the flexible TFT (drawn not to scale). (d) The transfer characteristics of an example flexible TFT with  $W/L = 60 \mu m/3 \mu m$ . (e) The I-V characteristics of the flexible TFT with  $W/L = 60 \mu m/3 \mu m$

where k is the Boltzman constant and T is absolute temperature. q is unit electron charge and  $C_{ox}$  is the unit capacitance of  $Nb_2O_3$ - $Bi_2O_3$ - $MgO/TiO_2$  heterostructure. The calculated  $D_{it}$  is  $\sim 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$ , which is relatively low for flexible singlecrystalline Si TFTs on plastic substrates.

Performance dependence of flexible TFTs on different dimensions are also investigated. Identical device structure is employed for the performance comparison.

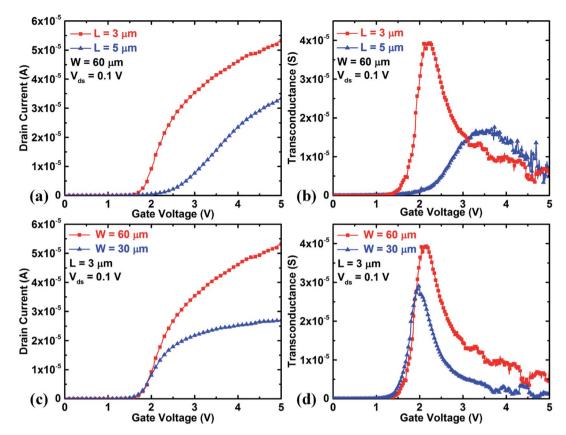

#### Dependence on L

Fig. 4a and b show the transfer characteristics of flexible TFTs with different L (3  $\mu$ m and 5  $\mu$ m) and same W (60  $\mu$ m) when  $V_{ds}$ is 0.1 V, respectively. The threshold voltage of flexible TFT with  $W/L = 60 \mu m/3 \mu m$  is  $\sim 1.2 V$ , which is slightly lower than that of TFT with  $W/L = 60 \mu m/5 \mu m$  ( $\sim 1.3 V$ ). This is because that when the depletion generated by applying gate voltage is partially overlapped with the source and drain depletion, the inversion layer charge in the Si and dielectric interface decreases, causing the threshold voltage to slightly decrease.

The drain current is observed to be inversely proportional to L. Quantitatively, the saturation drain current of flexible TFT of  $L=3 \mu m (\sim 53 \mu A)$  is  $\sim 1.6$  times of that of flexible TFT of L=5 $\mu$ m ( $\sim$ 33  $\mu$ A), which is good agreement with theory calculation:

$$I_{\rm ds} = \frac{W \times \mu_{\rm n} \times C_{\rm ox} \times \left[2(V_{\rm gs} - V_{\rm th}) \times V_{\rm ds} - V_{\rm ds}^2\right]}{2L}$$

$$0 < V_{\rm ds} < V_{\rm gs} - V_{\rm th} \tag{5}$$

$$I_{\rm ds} = \frac{W \times \mu_{\rm n} \times C_{\rm ox} \times (V_{\rm gs} - V_{\rm th})^2}{2L} 0 < V_{\rm gs} - V_{\rm th} < V_{\rm ds}$$

(6)

The transconductance of flexible TFTs is extracted from the following equation:

$$g_{\rm m} = \frac{\partial I_{\rm ds}}{\partial V_{\rm gs}} \tag{7}$$

It is also consistent with the experiment results and the highest transconductance reaches to  $\sim$ 40  $\mu$ S when the applied gate voltage is  $\sim$ 2.1 V.

#### Dependence on W

Fig. 4c and d show the transfer characteristics of flexible TFTs with different  $W(30 \mu \text{m} \text{ and } 60 \mu \text{m})$  and same  $L(3 \mu \text{m})$  when  $V_{ds}$ is 0.1 V, respectively. The drain current is proportional to W.

The saturation drain current of flexible TFT of  $W = 60 \mu m$ ( $\sim$ 53  $\mu$ A) is 1.96 times of that of flexible TFT of  $W = 30 \mu m$  ( $\sim$ 27 μA), which is also in good agreement with the theory calculation. The results show that the fabricated flexible TFTs with Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM heterostructure have performance consistency with different channel size.

Based on the experimental results, the advantages of the dielectric ceramics Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM

Fig. 4 The performance dependence of flexible TFTs on different dimensions: (a)  $I_{\rm ds}$  and (b) transconductance comparisons of flexible TFTs with different L (3  $\mu$ m and 5  $\mu$ m). (c)  $I_{\rm ds}$  and (d) transconductance comparisons of flexible TFTs with different W (30  $\mu$ m and 60  $\mu$ m).

heterostructure for flexible single-crystalline Si TFTs are analyzed and discussed as follows:

(1) The dielectric constant of the  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  dielectrics is extracted to be  $\sim$ 76.6 (Fig. 2). The number is lower than the dielectric constant of  $Nb_2O_3$ – $Bi_2O_3$ –MgO and higher than that of  $TiO_2$ . Nevertheless, the dielectric constant of the heterostructure is much higher than those of SiO,  $SiO_x$  or most low-temperature processed dielectrics, thus demonstrating that the heterostructure can be used as high-k gate dielectric material for high performance flexible devices.

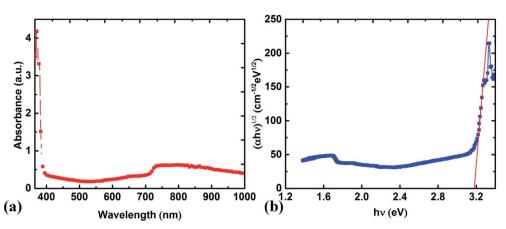

(2) The SEM images and AFM images show that the surface of TiO<sub>2</sub> is much smoother than that of Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO (Fig. 2) and the  $D_{\rm it}$  of Si and dielectric ( $\sim 10^{12}~{\rm eV}^{-1}~{\rm cm}^{-2}$ ) is relatively low, which indicates that inserting TiO<sub>2</sub> between SiNM and Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO can improve the interface quality. Additionally, the leakage current of Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO/TiO<sub>2</sub>/SiNM heterostructure is lower than that of TiO<sub>2</sub>/SiNM heterostructure. The reason for this is that dielectric ceramics layer Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO increases the conduction band offset between SiNM and TiO<sub>2</sub>, which can be explained from Fig. 5.

Fig. 5a shows the absorbance spectra of the  $Nb_2O_3$ – $Bi_2O_3$ – $MgO/TiO_2$  heterostructure with wavelength from 365 nm to 1000 nm. Based on the absorbance (Abs), the optical absorption coefficient ( $\alpha$ ) for the heterostructure can be calculated as follows:<sup>41</sup>

$$\alpha = 2.303(Abs/t_{ox}) \tag{8}$$

where  $t_{\rm ox}$  is the thickness of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub> heterostructure ( $\sim$ 100 nm).

The band gap of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub> heterostructure can be extracted by the following equation<sup>42</sup> as shown in the Fig. 5b:

$$\alpha h \nu = B(h \nu - E_{\rm g})^2 \tag{9}$$

where h is Planck's constant and  $\nu$  is the light frequency, B is absorption constant and  $E_{\rm g}$  is the band gap. The band gap of the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub> heterostructure is extracted to be  $\sim$ 3.19 eV, which is higher than that of TiO<sub>2</sub>, <sup>43-45</sup> proving that combing TiO<sub>2</sub> with high-k material Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO can improve the performance of TiO<sub>2</sub>.

Mechanical bending tests have been conducted for the fabricated flexible TFTs. The drain currents of the flexible TFTs are measured by attaching the devices onto molds with various curvature radii (from  $\sim\!\!77.5$  mm to  $\sim\!\!28.5$  mm). The flexible single-crystalline Si TFTs with Nb<sub>2</sub>O<sub>3</sub>–Bi<sub>2</sub>O<sub>3</sub>–MgO/TiO<sub>2</sub>/SiNM heterostructure on plastic substrates show slight performance variations, indicating good performance stability under mechanical bending conditions.

Fig. 5 The spectra and band gap of  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure: (a) the absorption spectra of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure with wavelength from 365 nm to 1000 nm. (b) The extracted band gap of the  $Nb_2O_3 - Bi_2O_3 - MgO/TiO_2$  heterostructure.

## Conclusions

Paper

High performance flexible thin-film transistors (TFTs) with ceramics/TiO<sub>2</sub>/single-crystalline membrane (SiNM) heterostructure is designed and fabricated in this paper. Both the dielectric ceramics (Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO) and TiO2 are deposited by radio frequency (RF) magnetron sputtering at room temperature and the single-crystalline SiNM is transferred and attached to the dielectric ceramics/TiO2 layers to form the heterostructure. The experimental results demonstrate that the Nb2O3-Bi2O3-MgO/TiO2 heterostructure has high dielectric constant ( $\sim$ 76.6) and wider band gap than TiO2, which increases the conduction band offset between Si and TiO<sub>2</sub>, lowering the leakage current. The TiO<sub>2</sub>/single crystalline SiNM structure has relatively low interface trap density. Flexible TFTs fabricated with the Nb<sub>2</sub>O<sub>3</sub>-Bi<sub>2</sub>O<sub>3</sub>-MgO/TiO<sub>2</sub>/SiNM heterostructure on plastic substrates show a current on/off ratio over  $10^4$ , threshold voltage of  $\sim 1.2$  V, subthreshold swing (SS) as low as  $\sim 0.2 \text{ V dec}^{-1}$ , interface trap density of  $\sim 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$ and good performance stability under mechanical bending conditions. The results indicate that the dielectric ceramics/ TiO2/SiNM heterostructure has great potential for high performance TFTs.

#### Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

This work was supported by the National Natural Science Foundation of China (61871285), and by Tianjin Natural Science Foundation (18JCYBJC15900).

#### References

1 S. Park, S. W. Heo, W. Lee, D. Inoue, Z. Jiang, K. Yu, H. Jinno, D. Hashizume, M. Sekino, T. Yokota, K. Fukuda, K. Tajima and T. Someya, *Nature*, 2018, **561**, 516–521.

- 2 W. Gao, S. Emaminejad, H. Y. Y. Nyein, S. Challa, K. V. Chen, A. Peck, H. M. Fahad, H. Ota, H. Shiraki, D. Kiriya, D. H. Lien, G. A. Brooks, R. W. Davis and A. Javey, *Nature*, 2016, 529, 509–514.

- 3 Y. Kim, A. Chortos, W. T. Xu, Y. X. Liu, J. Y. Oh, D. Son, J. Kang, A. M. Foudeh, C. X. Zhu, Y. Lee, S. M. Niu, J. Liu, R. Pfattner, Z. N. Bao and T. W. Lee, *Science*, 2018, 360, 998–1003.

- 4 B. C. K. Tee, A. Chortos, A. Berdnt, A. K. Nguyen, A. Tom, A. McGuire, Z. L. C. Liu, K. Tien, W. G. Bae, H. L. Wang, P. Mei, H. H. Chou, B. X. Cui, K. Deisseroth, T. N. Ng and Z. N. Bao, *Science*, 2015, **350**, 313–316.

- 5 Y. C. Liu, Y. X. Zhang, Z. Yang, H. C. Ye, J. S. Feng, Z. Xu, X. Zhang, R. Munir, J. Liu, P. Zuo, Q. X. Li, M. X. Hu, L. N. Meng, K. Wang, D. M. Smilgies, G. T. Zhao, H. Xu, Z. P. Yang, A. Amassian, J. W. Li, K. Zhao and S. Z. Liu, *Nat. Commun.*, 2018, 9, 5302.

- 6 H. H. Chou, A. Nguyen, A. Chortos, J. W. F. To, C. Lu, J. G. Mei, T. Kurosawa, W. G. Bae, J. B. H. Tok and Z. A. Bao, *Nat. Commun.*, 2015, 6, 8011.

- 7 G. X. Qin, H. C. Yuan, G. K. Celler, W. D. Zhou, J. G. Ma and Z. Q. Ma, *Microelectron. J.*, 2011, 42, 509–514.

- 8 M. J. Dang, H. C. Yuan, Z. Q. Ma, J. G. Ma and G. X. Qin, *Appl. Phys. Lett.*, 2017, **110**, 253104.

- 9 E. M. Song, Q. L. Guo, G. S. Huang, B. Jia and Y. F. Mei, *ACS Appl. Mater. Interfaces*, 2017, **9**, 12171–12175.

- 10 G. X. Qin, H. C. Yuan, G. K. Celler, J. G. Ma and Z. G. Ma, Microelectron. Eng., 2012, 95, 21–25.

- 11 S. W. Hwang, H. Tao, D. H. Kim, H. Y. Cheng, J. K. Song, E. Rill, M. A. Brenckle, B. Panilaitis, S. M. Won, Y. S. Kim, Y. M. Song, K. J. Yu, A. Ameen, R. Li, Y. W. Su, M. M. Yang, D. L. Kaplan, M. R. Zakin, M. J. Slepian, Y. G. Huang, F. G. Omenetto and J. A. Rogers, *Science*, 2012, 337, 1640–1644.

- 12 S. W. Hwang, X. Huang, J. H. Seo, J. K. Song, S. Kim, S. Hage-Ali, H. J. Chung, H. Tao, F. G. Omenetto, Z. Q. Ma and J. A. Rogers, *Adv. Mater.*, 2013, 25, 3526–3531.

13 S. W. Hwang, G. Park, H. Cheng, J. K. Song, S. K. Kang, 27 X. Wang,

L. Yin, J. H. Kim, F. G. Omenetto, Y. G. Huang, K. M. Lee and J. A. Rogers, *Adv. Mater.*, 2014, **26**, 1992–2000.

**RSC Advances**

- 14 S. W. Hwang, J. K. Song, X. Huang, H. Y. Cheng, S. K. Kang, B. H. Kim, J. H. Kim, S. Yu, Y. G. Huang and J. A. Rogers, *Adv. Mater.*, 2014, 26, 3905–3911.

- 15 S. W. Hwang, G. Park, C. Edwards, E. A. Corbin, S. K. Kang, H. Y. Cheng, J. K. Song, J. H. Kim, S. Yu, J. Ng, J. E. Lee, J. Kim, C. Yee, B. Bhaduri, Y. Su, F. G. Omennetto, Y. G. Huang, R. Bashir, L. Goddard, G. Popescu, K. M. Lee and J. A. Rogers, ACS Nano, 2014, 8, 5843–5851.

- 16 H. J. Yang, D. Y. Zhao, S. Chuwongin, J. H. Seo, W. Q. Yang, Y. C. Shuai, J. Berggren, M. Hammar, Z. Q. Ma and W. D. Zhou, *Nat. Photonics*, 2012, 6, 615–620.

- 17 E. M. Song, H. Fang, X. Jin, J. N. Zhao, C. S. Jiang, K. J. Yu, Y. D. Zhong, D. Xu, J. H. Li, G. H. Fang, H. N. Du, J. Z. Zhang, J. M. Park, Y. G. Huang, M. A. Alam, Y. F. Mei and J. A. Rogers, Adv. Electron. Mater., 2017, 3, 1700077.

- 18 A. Liu, H. H. Zhu, W. T. Park, S. J. Kang, Y. Xu, M. G. Kim and Y. Y. Noh, *Adv. Mater.*, 2018, **30**, 1802379.

- 19 J. Q. Song, C. Y. Han and P. T. Lai, *IEEE Trans. Electron Devices*, 2016, 63, 1928-1933.

- 20 H. J. Kwon, J. Jang and C. P. Grigoropoulos, *ACS Appl. Mater. Interfaces*, 2016, **8**, 9314–9318.

- 21 P. F. Ma, J. M. Sun, G. D. Liang, Y. P. Li, Q. Xin, Y. X. Li and A. M. Song, *Appl. Phys. Lett.*, 2018, **113**, 063501.

- 22 G. He, X. S. Chen and Z. Q. Sun, *Surf. Sci. Rep.*, 2013, **68**, 68–107.

- 23 G. He, J. W. Liu, H. S. Chen, Y. M. Liu, Z. Q. Sun, X. S. Chen, M. Liu and L. D. Zhang, J. Mater. Chem. C, 2014, 2, 5299– 5308.

- 24 J. W. Zhang, G. He, L. Zhou, H. S. Chen, X. S. Chen, X. F. Chen, B. Deng, J. G. Lv and Z. Q. Sun, *J. Alloy. Compd*, 2014, 611, 253–259.

- 25 G. He, J. Gao, H. S. Chen, J. B. Cui, Z. Q. Sun and X. S. Chen, *ACS Appl. Mater. Interfaces*, 2014, **6**, 22013–22025.

- 26 K. Kukli, M. Kemell, M. Vehkamaki, M. J. Heikkila, K. Mizohata, K. Kalam, M. Ritala, M. Leskela, I. Kundrata and K. Fronhlich, AIP Adv., 2017, 7, 025001.

- 27 X. Wang, H. X. Liu, C. X. Fei, L. Zhao, S. P. Chen and S. L. Wang, *AIP Adv.*, 2016, **6**, 065224.

- 28 J. W. Liu and Y. Koide, Sensors, 2018, 18, 813.

- 29 L. L. Zheng, S. B. Qian, Y. H. Wang, W. J. Liu and S. J. Ding, *IEEE J. Electron Devices Soc.*, 2016, 4, 347–352.

- 30 S. Jiang, X. Yang, J. H. Zhang and X. F. Li, AIP Adv., 2018, 8, 085109.

- 31 H. F. Pu, H. L. Li, Z. Yang, Q. F. Zhou, C. Y. Dong and Q. Zhang, *ECS Solid State Lett.*, 2013, 2, N35–N38.

- 32 X. W. Ding, J. H. Zhang, J. Li, W. M. Shi, H. Zhang, X. Y. Jiang and Z. L. Zhang, Superlattices Microstruct., 2014, 69, 204–211.

- 33 J. Li, F. Zhou, H. P. Lin, W. Q. Zhu, J. H. Zhang, X. Y. Jiang and Z. L. Zhang, *Curr. Appl. Phys.*, 2012, **12**, 1288–1291.

- 34 H. Zhang, Y. Zhang, X. Chen, C. Y. Li and X. W. Ding, *Mol. Cryst. Liq. Cryst.*, 2017, **651**, 228–234.

- 35 X. S. Rong, H. F. Chen, J. Rong, X. Y. Zhang, J. Wei, S. Liu, X. T. Zhou, J. C. Xu, F. X. Qiu and Z. R. Wu, *Chem. Eng. J.*, 2019, 371, 286–293.

- 36 V. K. Ashith, G. K. Rao, R. Smitha and S. N. Moger, *Ceram. Int.*, 2018, 44, 17623–17629.

- 37 Y. Y. Lin, C. C. Hsu, M. H. Tseng, J. J. Shyue and F. Y. Tsai, *ACS Appl. Mater. Interfaces*, 2015, 7, 22610–22617.

- 38 N. D. Chinh, C. Kim and D. Kim, *J. Alloys Compd.*, 2019, 778, 247–255.

- 39 G. X. Qin, Y. B. Zhang, K. B. Lan, L. X. Li, J. G. Ma and S. H. Yu, ACS Appl. Mater. Interfaces, 2018, 10, 12798–12806.

- 40 D. B. Ruan, P. T. Liu, Y. C. Chiu, P. Y. Kuo, M. C. Yu, K. Z. Kan, T. C. Chien, Y. H. Chen and S. M. Sze, *Thin Solid Films*, 2018, 660, 578-584.

- 41 M. C. Sekhar, N. N. K. Reddy, H. S. Akkera, B. P. Reddy, V. Rajendar, S. Uthanna and S. H. Park, *J. Alloys Compd.*, 2017, 718, 104–111.

- 42 M. Maimaiti, B. H. Zhao, M. Mamat, Y. Tuersun, A. Mijiti, Q. Wang and Y. F. Sun, *Mater. Res. Express*, 2019, **6**, 086408.

- 43 V. M. Naik, D. Haddad, R. Naik, J. Benci and G. W. Auner, *Mater. Res. Soc. Symp. Proc.*, 2003, 755, 413–418.

- 44 K. Kaur and C. V. Singh, Energy Procedia, 2012, 29, 291-299.

- 45 Y. F. Ju, M. H. Wang, Y. L. Wang, S. H. Wang and C. F. Fu, *Adv. Condens. Matter Phys.*, 2013, 365475.