# **RSC Advances**

PAPER

View Article Online

View Journal | View Issue

Cite this: RSC Adv., 2019, 9, 592

Suppression of  $GeO_x$  interfacial layer and enhancement of the electrical performance of the high-K gate stack by the atomic-layer-deposited AlN buffer layer on Ge metal-oxide-semiconductor devices

Chin-I. Wang, <sup>1</sup> Teng-Jan Chang, <sup>a</sup> Chun-Yuan Wang, <sup>a</sup> Yu-Tung Yin, <sup>a</sup> Jing-Jong Shyue, <sup>b</sup> Hsin-Chih Lin <sup>a</sup> and Miin-Jang Chen\*

For high-performance nanoscale Ge-based transistors, one important point of focus is interfacial germanium oxide ( $GeO_x$ ), which is thermodynamically unstable and easily desorbed. In this study, an atomic-layer-deposited AlN buffer layer was introduced between the crystalline  $ZrO_2$  high-K gate dielectrics and epitaxial Ge, in order to reduce the formation of interfacial  $GeO_x$ . The results of X-ray photoelectron spectroscopy and high-resolution transmission electron microscopy demonstrate that the AlN buffer layer suppressed the formation of interfacial  $GeO_x$ . Hence, significant enhancement of the electrical characteristics of Ge metal-oxide-semiconductor (MOS) capacitors was achieved with a two-orders-of-magnitude reduction in the gate leakage current, a 34% enhancement of the MOS capacitance, and a lower interfacial state density. The results indicate that the AlN buffer layer is effective in providing a high-quality interface to improve the electrical performance of advanced Ge MOS devices.

Received 14th September 2018 Accepted 3rd December 2018

DOI: 10.1039/c8ra07652a

rsc.li/rsc-advances

## 1. Introduction

Over the last decade, it has become increasingly difficult to improve the performance of silicon (Si) metal-oxidesemiconductor (MOS) field-effect transistors (FETs) via conventional device scaling. Due to high carrier mobility, germanium (Ge) and III-V compound MOSFETs have been regarded as very promising candidates for the further improvement of device performance and scaling.1-4 However, the lack of high-quality and thermodynamically stable gate dielectrics is a major problem in implementing Ge and III-V semiconductors as the channel materials.5-10 For Ge, it is difficult to suppress the formation of a low-K germanium oxide (GeO<sub>r</sub>) interfacial layer (IL) at the high-K and Ge interface, which limits the minimum achievable equivalent oxide thickness.11,12 In contrast to the SiO<sub>2</sub>/Si system, interfacial GeO<sub>x</sub> has been reported to be thermodynamically unstable. The smaller conduction band offset at the GeO<sub>x</sub>/Ge interface also results in an increase in the gate leakage current.13 Therefore, it is essential to prevent the formation of interfacial  $GeO_x$  in highperformance Ge-based MOSFETs. 13,14

Many methods have been used to passivate the defects and achieve a stable high-K/Ge interface, such as the use of ultrathin

Si, high-quality Ge oxides, and rare-earth oxides (Y<sub>2</sub>O<sub>3</sub>, SmGeO<sub>x</sub>, etc.).<sup>6,15-17</sup> One of the most widely used methods is the insertion of an Al<sub>2</sub>O<sub>3</sub> buffer layer between the high-*K* oxide and Ge because of the high bandgap and good thermal stability of Al<sub>2</sub>O<sub>3</sub>.<sup>18,19</sup> Besides, it has been reported that nitrogen incorporation into GeO<sub>x</sub> yields an improvement in the thermal stability and the dielectric constant.<sup>20,21</sup> However, an unstable GeO<sub>x</sub> is usually formed at the Al<sub>2</sub>O<sub>3</sub>/Ge and Ge-oxynitride/Ge interfaces. Furthermore, the use of germanium nitride (Ge<sub>3</sub>N<sub>4</sub> or GeN<sub>x</sub>) as the gate dielectric and the buffer layer has been demonstrated to exhibit well-behaved capacitance–voltage characteristics.<sup>22-25</sup> This improvement in the electrical performance may be the result of the suppression of interfacial GeO<sub>x</sub> because the preparation of the nitride does not involve the use of oxygen.

AlN is a good material for gate dielectrics and buffer layers because it has a higher dielectric constant than  $GeO_x$ , good chemical stability, and a wide bandgap of  $\sim 6.2$  eV.<sup>26–28</sup> AlN thin films are conventionally prepared by chemical vapor deposition (CVD) and sputtering.<sup>29,30</sup> However, the typical deposition temperature for AlN prepared using CVD is greater than 700 °C,<sup>31</sup> which is unfavorable for the integration of semiconductor processing. Besides, it is difficult to deposit high-quality nanoscale thin films using sputtering.<sup>32</sup> Recently, atomic layer deposition (ALD) has been reported for the preparation of high-quality nanoscale AlN thin films at low temperatures.<sup>26,31</sup> In this paper, remote plasma ALD (RP-ALD) was used to deposit a nanoscale AlN buffer layer between the

<sup>&</sup>lt;sup>a</sup>Department of Materials Science and Engineering, National Taiwan University, Taipei, Taiwan. E-mail: michen@ntu.edu.tw

<sup>&</sup>lt;sup>b</sup>Research Center for Applied Science, Academia Sinica, Taipei, Taiwan

Paper RSC Advances

crystalline  $ZrO_2$  high-K gate dielectrics and Ge. The interfacial  $GeO_x$  was suppressed by the AlN buffer layer, so the capacitance equivalent thickness (CET), the interfacial state density ( $D_{it}$ ) and the gate leakage current ( $J_g$ ) of Ge MOS capacitors were significantly improved.

## 2. Experiments

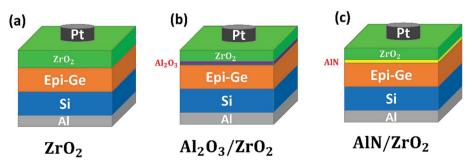

The gate stacks in MOS capacitors are plotted schematically in Fig. 1. A Ge epitaxial layer was grown by remote plasma chemical vapor deposition using GeH4 at 375 °C on a highly-doped  $(0.001-0.003 \Omega \text{ cm})$  n-type Si substrate. After pre-cleaning, the samples were immersed in dilute HF (1 min) and then rinsed with de-ionized water (30 s) for several cycles, in order to remove the native oxide on the Ge. The gate stacks, which were composed of ZrO2, Al2O3/ZrO2, and AlN/ZrO2, were then immediately deposited by RP-ALD (Fiji, Ultratech) at 250 °C. Tetrakis(dimethylamino)zirconium (TDMAZ), trimethylaluminum (TMA), O2 plasma, and N2/H2 plasma were respectively used as the precursors and reactants for Zr, Al, O, and N. A platinum (Pt) top electrode with an area of  $3 \times 10^{-4}$  cm<sup>2</sup> was deposited by radio-frequency sputtering, and then an aluminum (Al) back contact was then produced by thermal evaporation. Finally, all samples were annealed in a furnace at 450 °C in N<sub>2</sub> ambient for 30 minutes.

The chemical bonding in the gate stacks was determined by X-ray photoelectron spectroscopy (XPS) using Al K $\alpha$  radiation at 1486.6 eV. The cross-sectional images of the gate stacks were observed using high-resolution transmission electron microscopy (HRTEM, Philips Tecnai F20 G2 FEI-TEM, 200 kV). The crystalline phases of ZrO<sub>2</sub> were measured by grazing incident angle X-ray diffraction (GIXRD) using Cu K $\alpha$  radiation at an incident angle of 0.5°. The capacitance density *versus* voltage (C-V), the leakage current density *versus* voltage (I-V), and the conductance density *versus* the frequency (G-f) curves of the gate stacks were characterized using an Agilent B1500A semiconductor device analyzer at room temperature.

## 3. Results and discussions

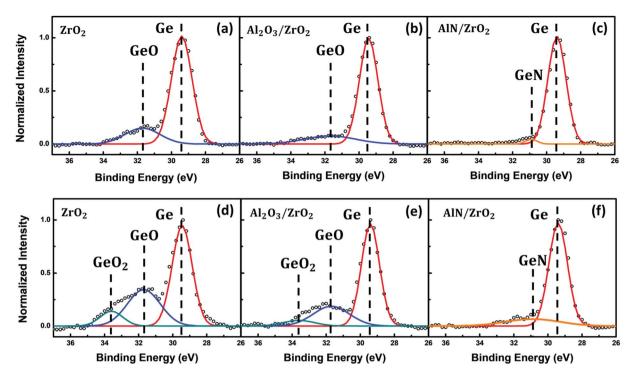

Fig. 2 shows the Ge 3d XPS spectra of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks with and without the annealing treatment, which reveals the oxidation states of Ge. The XPS spectra can be decomposed into the peaks corresponding to the binding

energies at 29.4 eV (Ge), 31.7 eV (GeO), 33.6 eV (GeO2), and 30.9 eV (Ge-N).19 The XPS spectra of the samples without the annealing treatment are shown in Fig. 2(a)-(c). The presence of the GeO oxidation state in the ZrO<sub>2</sub> sample (Fig. 2(a)) is attributed to the supply of oxygen from ZrO2. Fig. 2(b) reveals that the interfacial GeO was suppressed in the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> gate stack compared to that in the ZrO<sub>2</sub> sample, which can be deduced from the lower Gibbs free energy of Al<sub>2</sub>O<sub>3</sub> than that of ZrO<sub>2</sub>.<sup>33</sup> It can be seen in Fig. 2(c) that the AlN buffer layer led to the formation of Ge-N bonds, and the GeO oxidation states were almost absent in the AlN/ZrO<sub>2</sub> sample because oxygen was not involved during AlN deposition. The result also suggests that the diffusion of oxygen from ZrO<sub>2</sub> toward the interface was effectively blocked by the AlN buffer layer, and so the formation of interfacial GeOx was suppressed. Moreover, Fig. 2(d)-(f) are the XPS spectra of the samples treated with the annealing process. As compared with Fig. 2(a) and (b), the annealing treatment gave rise to an increase in the GeO signals and the formation of GeO<sub>2</sub> oxidation states in the ZrO2 and Al2O3/ZrO2 gate stacks:34

$$2\text{GeO} \rightarrow \text{GeO}_2 + \text{Ge}$$

The decomposition of GeO into  $GeO_2$  and Ge is ascribed to the lower Gibbs free energy of  $GeO_2$  than that of  $GeO.^{34}$  The outcome indicates that the annealing process facilitated the formation of interfacial  $GeO_x$ . Notice that no obvious interfacial  $GeO_x$  appeared in the XPS spectrum of the  $AlN/ZrO_2$  gate stack as shown in Fig. 2(f). The result confirms again that the AlN buffer layer could effectively restrain oxygen diffusion during the  $ZrO_2$  deposition and annealing processes.

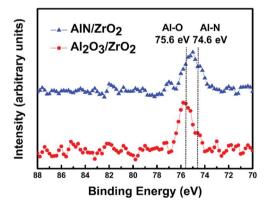

The Al 2p XPS spectra of the  $Al_2O_3/ZrO_2$  and  $AlN/ZrO_2$  gate stacks are shown in Fig. 3. The Al–O bond (75.6 eV) was present in the  $Al_2O_3/ZrO_2$  sample due to the introduction of the  $Al_2O_3$  buffer layer. The Al 2p peak of the  $AlN/ZrO_2$  sample was located near 74.6 eV, which is associated with the Al–N bond because AlN was substituted for the  $Al_2O_3$  buffer layer. <sup>35</sup> Depositing  $ZrO_2$  on the AlN buffer layer results in a slight shift in the Al 2p peak (~75 eV) from the standard Al–N bond at 74.6 eV toward the Al–O bond at 75.6 eV, indicating the partial oxidation of AlN.

The HRTEM images of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks are shown in Fig. 4. It is seen that the total physical thickness of all the samples was approximately 7.5 nm. The ZrO<sub>2</sub> layer featured a crystalline lattice in the images for all of the samples, which demonstrates that ZrO<sub>2</sub> was crystallized

Fig. 1 Schematic of the (a) ZrO<sub>2</sub>, (b) Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and (c) AlN/ZrO<sub>2</sub> gate stacks.

Fig. 2 The Ge 3d XPS spectra of the (a) ZrO<sub>2</sub>, (b) Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and (c) AlN/ZrO<sub>2</sub> gate stacks without the annealing treatment and the (d) ZrO<sub>2</sub>, (e)  $Al_2O_3/ZrO_2$ , and (f)  $AlN/ZrO_2$  gate stacks treated with the annealing process (in a furnace at 450 °C for 30 minutes in  $N_2$  ambient). The intensity of the Ge peak of each sample was normalized to one. The annealing treatment facilitated the formation of interfacial  $GeO_x$  in the  $ZrO_2$  and  $Al_2O_3/$  $ZrO_2$  gate stacks. The interfacial  $GeO_x$  was significantly suppressed in the  $AlN/ZrO_2$  gate stack.

Fig. 3 Al 2p XPS spectra of the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> and AlN/ZrO<sub>2</sub> gate stacks. The Al-O (75.6 eV) and Al-N (74.6 eV) bonds were present in the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> and AlN/ZrO<sub>2</sub> samples

during thermal annealing.<sup>36</sup> In Fig. 4(a), there is an obvious and rough interfacial GeO<sub>x</sub> layer in the ZrO<sub>2</sub> sample. An Al<sub>2</sub>O<sub>3</sub> buffer layer and interfacial  $GeO_x$  are observed in the  $Al_2O_3/ZrO_2$  gate stack as shown in Fig. 4(b). Fig. 4(c) reveals a sharp interface without interfacial GeO<sub>x</sub> between AlN and Ge, indicating that the AlN buffer layer was capable of suppressing interfacial GeO<sub>x</sub>. The HRTEM results are in good agreement with the Ge 3d XPS spectra shown in Fig. 2.

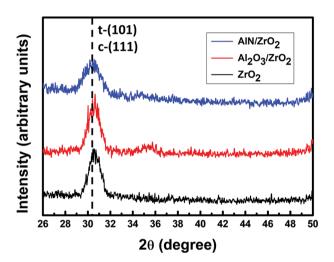

The GIXRD patterns of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks are shown in Fig. 5. There is an obvious diffraction peak at  $2\theta = 30.4^{\circ}$  in all of the samples, which corresponds to the tetragonal (101) phase (88-1007 JCPDS) or the cubic (111) phase (49-1642 JCPDS) of ZrO2.37 The tetragonal/cubic phase in ZrO<sub>2</sub> had a much higher dielectric constant than amorphous ZrO<sub>2</sub>, which allows further CET scaling.<sup>38</sup> Although tetragonal/ cubic ZrO<sub>2</sub> was thermodynamically stable at temperatures greater than 1170 °C,39,40 the tetragonal/cubic phase had been observed in nanoscale ZrO2 thin films.41 The presence of tetragonal/cubic ZrO2 in the nanoscale layers, as shown in Fig. 5, is consistent with the results of previous studies. 36,41

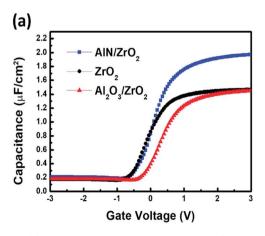

The C-V curves of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks are shown in Fig. 6(a). The capacitance of the AlN/ZrO<sub>2</sub> sample was much greater than that of the ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> samples. Table 1 shows the CET and the effective dielectric constant  $(k_{\text{eff}})$  of the  $\text{ZrO}_2$ ,  $\text{Al}_2\text{O}_3/\text{ZrO}_2$ , and  $\text{AlN/ZrO}_2$  gate stacks. These values were derived from the C-V curves. The CET and  $k_{\text{eff}}$ values of the ZrO2 sample are 2.35 nm and 12.42 nm, respectively. The  $k_{\text{eff}}$  of the  $\text{ZrO}_2$  sample is much lower than the dielectric constant of tetragonal/cubic ZrO2,42,43 which can be deduced from the presence of low-K interfacial GeOx in the ZrO2 sample, as shown in the XPS spectrum and the HRTEM image (Fig. 2(d) and 4(a)). Although the low-K interfacial  $GeO_x$  was suppressed by the Al<sub>2</sub>O<sub>3</sub> buffer layer, as demonstrated by the XPS spectrum (Fig. 2(e)), the introduction of the  $Al_2O_3$  buffer layer between ZrO2 and Ge still caused a slight degradation of the CET (2.38 nm) and  $k_{\rm eff}$  (12.29) of the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> gate stack because Al<sub>2</sub>O<sub>3</sub> has a lower dielectric constant than ZrO<sub>2</sub>. The substitution of AlN for Al2O3 as the buffer layer led to a significant decrease in the CET (1.75 nm) and an increase in the  $k_{\text{eff}}$

Paper

(a) (c) (b) 5 nm 5 nm

Fig. 4 Cross-sectional HRTEM images of the (a)  $ZrO_2$ , (b)  $Al_2O_3/ZrO_2$ , and (c)  $AlN/ZrO_2$  gate stacks. There is a sharp interface between AlN and Ge in the AlN/ZrO<sub>2</sub> sample.

Fig. 5 GIXRD patterns of ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks. The obvious diffraction peak at  $2\theta = 30.4^{\circ}$  is associated with tetragonal/cubic ZrO2

(16.72) of the AlN/ZrO<sub>2</sub> sample, which is mainly attributed to the suppression of the interfacial GeO<sub>x</sub>, as clearly shown in Fig. 2(f) and 4(c).

Fig. 6(b) and Table 1 show the I-V curves and the  $J_g$  of the ZrO2, Al2O3/ZrO2, and AlN/ZrO2 gate stacks. The ZrO2 sample had a high  $J_{\rm g}$  value of 1.82  $\times$  10<sup>-1</sup> A cm<sup>-2</sup> as a result of the leakage current path via the grain boundaries in crystalline ZrO<sub>2</sub>. Due to the high bandgap of Al<sub>2</sub>O<sub>3</sub>, the presence of the  ${\rm Al_2O_3}$  buffer layer resulted in a decrease in the  $J_{\rm g}$  (2.60  $\times$  10<sup>-2</sup> A cm<sup>-2</sup>) of the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> sample. There was a significant reduction in the  $J_{\rm g}$  (1.12  $\times$  10<sup>-3</sup> A cm<sup>-2</sup>) of the AlN/ZrO<sub>2</sub> gate stack, which is two orders of magnitude lower than that of the ZrO<sub>2</sub> sample because of the insertion of the AlN buffer layer. This can be understood from the suppressed growth of interfacial GeOx, which has a low conduction band offset of only ~0.8 eV.44

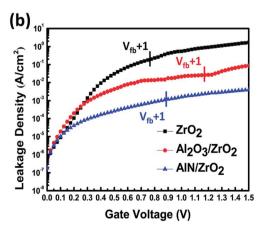

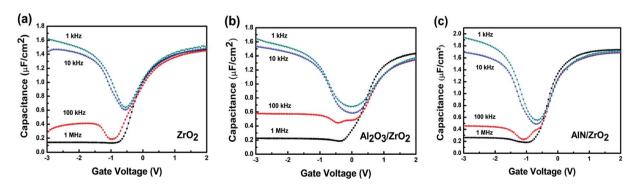

The Dit value was measured by the conductance (Nicollian-Goetzberger) method. 45,46 Fig. 7(a) shows the equivalent parallel conductance over the angular frequency  $(G_P/\omega)$  as a function of the frequency of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks. The value of  $D_{\rm it}$  was estimated from the maximum value of  $G_{\rm P}/\omega$ as:45

$$D_{\rm it} = \frac{2.5}{Aq} \left( \frac{G_{\rm P}}{\omega} \right)_{\rm max}$$

Fig. 6 (a) C-V and (b) I-V characteristics of the  $ZrO_2$ ,  $Al_2O_3/ZrO_2$ , and  $AlN/ZrO_2$  gate stacks. The  $AlN/ZrO_2$  gate stack had a higher capacitance and a lower  $J_g$  than the  $ZrO_2$  or  $Al_2O_3/ZrO_2$  samples.

**RSC Advances**

Table 1 The capacitance equivalent thickness (CET), the effective dielectric constant  $(k_{eff})$ , the gate leakage current  $(J_0)$ , and the interfacial state density (Dit) of the ZrO2, Al2O3/ZrO2, and AlN/ZrO2 gate stacks<sup>a</sup>

| Sample                                                                                       | CET (nm)             | $k_{ m eff}$            | $J_{ m g}$ (A cm $^{-2}$ )                                        | $D_{\rm it} \left({\rm cm}^{-2} \ {\rm eV}^{-1}\right)$           |

|----------------------------------------------------------------------------------------------|----------------------|-------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| ZrO <sub>2</sub><br>Al <sub>2</sub> O <sub>3</sub> /ZrO <sub>2</sub><br>AlN/ZrO <sub>2</sub> | 2.35<br>2.38<br>1.75 | 12.42<br>12.29<br>16.72 | $1.82 \times 10^{-1}$ $2.60 \times 10^{-2}$ $1.12 \times 10^{-3}$ | $9.08 \times 10^{12}$ $6.46 \times 10^{12}$ $3.85 \times 10^{12}$ |

<sup>&</sup>lt;sup>a</sup> These values were extracted from the C-V, I-V, and G-f curves as shown in Fig. 6 and 7. The leakage current density  $J_{\rm g}$  was determined at V<sub>fb</sub> (flat-band voltage) +1 V. The AlN/ZrO<sub>2</sub> gate stack exhibited a significant improvement in CET,  $k_{\rm eff}$ ,  $J_{\rm g}$ , and  $D_{\rm it}$  over the  ${\rm ZrO_2}$  and Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> samples.

where A is the area of the MOS capacitors. The  $D_{it}$  distributions in the bandgap of the ZrO2, Al2O3/ZrO2, and AlN/ZrO2 gate stacks are shown in Fig. 7(b). Since the weak inversion response results in the overestimation of  $D_{it}$  for Ge at room temperature,47 the minimum Dit values near the mid-gap were adopted to characterize the interfacial quality of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO2 gate stacks.48 As shown in Table 1, the minimum  $D_{\rm it}$  of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> samples were 9.08 imes $10^{12}~{\rm cm}^{-2}~{\rm eV}^{-1}$ ,  $6.46\times10^{12}~{\rm cm}^{-2}~{\rm eV}^{-1}$ , and  $3.85\times10^{12}~{\rm cm}^{-2}$ eV<sup>-1</sup>, respectively. Owing to the high thermal stability of the Al<sub>2</sub>O<sub>3</sub> buffer layer and the reduced growth of interfacial GeO<sub>x</sub>, the  $D_{\rm it}$  of the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> gate stack was lower than that of the ZrO2 sample. The introduction of the AlN buffer layer caused a further decrease in Dit of the AlN/ZrO2 gate stack, which is ascribed to the suppression of interfacial GeO<sub>r</sub> by the AlN buffer layer. Because remote N2/H2 plasma was used as the reactant in the deposition of the AlN buffer layer, hydrogen passivation of the interfacial states also led to decrease in Dit of the AlN/ZrO2 sample.49

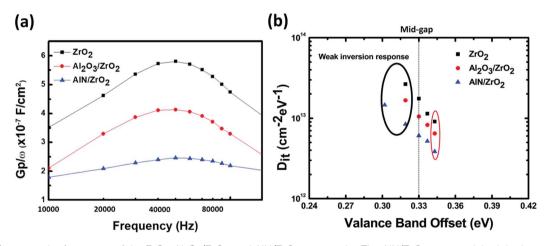

The C-V curves of the  $ZrO_2$ ,  $Al_2O_3/ZrO_2$ , and  $AlN/ZrO_2$  gate stacks at various frequencies are shown in Fig. 8. In the frequency range from 1 kHz to 100 kHz, the frequency dispersion is 4.2%, 2.2%, and 1.4% for the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks at an accumulation bias of 2 V. The larger capacitance at a high frequency of 1 MHz was deduced from the parasitic inductance. 50 The relatively low-frequency dispersion in the AlN/ZrO2 gate stack was correlated with the lower Dit as compared with the ZrO2 and Al2O3/ZrO2 samples.51

Fig. 7 (a)  $G_P/\omega$  versus the frequency of the  $ZrO_2$ ,  $Al_2O_3/ZrO_2$ , and  $AlN/ZrO_2$  gate stacks. The  $AlN/ZrO_2$  gate stack had the lowest value of  $G_P/\omega$  $\omega$ )<sub>max</sub>, and so the  $D_{it}$  of the AlN/ZrO<sub>2</sub> sample was lower than that of the ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> gate stacks. (b)  $D_{it}$  distributions versus bandgap energy, which were extracted from the conductance method, of the ZrO2, Al2O3/ZrO2, and AlN/ZrO2 gate stacks.

Fig. 8 The frequency dependence of the C-V curves of the (a)  $ZrO_2$ , (b)  $Al_2O_3/ZrO_2$ , and (c)  $AlN/ZrO_2$  gate stacks. Low-frequency dispersion was observed in the AlN/ZrO<sub>2</sub> sample.

Paper **RSC Advances**

#### Conclusion 4.

In this study, the electrical and structural characteristics of the ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>, and AlN/ZrO<sub>2</sub> gate stacks on Ge were investigated carefully. The introduction of an Al2O3 buffer layer between ZrO<sub>2</sub> and Ge resulted in a decrease of I<sub>0</sub> value due to the high bandgap of Al<sub>2</sub>O<sub>3</sub>. However, it is difficult to prevent the growth of unstable, low-K interfacial GeO<sub>x</sub> using an Al<sub>2</sub>O<sub>3</sub> buffer layer because oxygen was involved during the deposition of Al<sub>2</sub>O<sub>3</sub>. The formation of interfacial GeO<sub>x</sub> was significantly suppressed by an AlN buffer layer, as evidenced by the XPS and HRTEM characterizations. This produced a significant enhancement in the electrical characteristics, including the CET,  $k_{\text{eff}}$ ,  $J_g$ , and  $D_{\text{it}}$  of the AlN/ZrO<sub>2</sub> gate stack. The results of this study show that an AlN buffer layer is an effective approach to high-quality interfacial engineering for high-performance high-K gate stacks in advanced Ge MOS transistors.

## Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

The authors gratefully acknowledge the financial support of the Taiwan Semiconductor Manufacturing Company (TSMC) and the Ministry of Science and Technology (MOST 107-2622-8-002-018), Taiwan.

## References

- 1 S. Takagi, et al., IEDM'03 Technical Digest, IEEE International, 2003, pp. 3.3.1-3.3.4.

- 2 M. V. Fischetti and S. E. Laux, J. Appl. Phys., 1996, 80(4), 2234-2252.

- 3 K. Saraswat, C. O. Chui, T. Krishnamohan, D. Kim, A. Nayfeh and A. Pethe, Mater. Sci. Eng., B, 2006, 135(3), 242-249.

- 4 S. Takagi, M. Noguchi, M. Kim, S.-H. Kim, C.-Y. Chang, M. Yokoyama, et al., Solid-State Electron., 2016, 125, 82-102.

- 5 K. Prabhakaran, F. Maeda, Y. Watanabe and T. Ogino, Appl. Phys. Lett., 2000, 76(16), 2244-2246.

- 6 Y. Seo, T. I. Lee, C. M. Yoon, B.-E. Park, W. S. Hwang, H. Kim, et al., IEEE Trans. Electron Devices, 2017, 64(8), 3303-3307.

- 7 G. He, X. Chen and Z. Sun, Surf. Sci. Rep., 2013, 68(1), 68-107.

- 8 G. He, J. Gao, H. Chen, J. Cui, Z. Sun and X. Chen, ACS Appl. Mater. Interfaces, 2014, 6(24), 22013-22025.

- 9 G. He, B. Deng, H. Chen, X. Chen, J. Lv, Y. Ma, et al., APL Mater., 2013, 1(1), 012104.

- 10 G. He, J. Liu, H. Chen, Y. Liu, Z. Sun, X. Chen, et al., J. Mater. Chem. C, 2014, 2(27), 5299-5308.

- 11 Q. Xie, S. Deng, M. Schaekers, D. Lin, M. Caymax, A. Delabie, et al., Semicond. Sci. Technol., 2012, 27(7), 074012.

- 12 J. Zhang, G. He, L. Zhou, H. Chen, X. Chen, X. Chen, et al., J. Alloys Compd., 2014, 611, 253-259.

- 13 V. Afanas'ev and A. Stesmans, Appl. Phys. Lett., 2004, 84(13), 2319-2321.

- 14 Y. Fukuda, K. Kato, H. Toyota, T. Ono, Y. Nagasato and T. Ueno, Jpn. J. Appl. Phys., 2006, 45(9S), 7351.

- 15 R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, Appl. Phys. Lett., 2011, 98(11), 112902.

- 16 P. Zimmerman, et al., IEDM'06, IEEE International, 2006, pp. 1-4.

- 17 C.-C. Lin, Y.-H. Wu, C.-Y. Wu and C.-W. Lee, IEEE Electron Device Lett., 2014, 35(3), 384-386.

- 18 S. Iwauchi and T. Tanaka, Jpn. J. Appl. Phys., 1971, 10(2), 260.

- 19 R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka and S. Takagi, IEEE Trans. Electron Devices, 2012, 59(2), 335-341.

- 20 C. O. Chui, F. Ito and K. C. Saraswat, IEEE Electron Device Lett., 2004, 25(9), 613-615.

- 21 C. O. Chui, F. Ito and K. C. Saraswat, IEEE Trans. Electron Devices, 2006, 53(7), 1501-1508.

- 22 T. Maeda, T. Yasuda, M. Nishizawa, N. Miyata, Y. Morita and S. Takagi, Appl. Phys. Lett., 2004, 85(15), 3181-3183.

- 23 T. Maeda, M. Nishizawa, Y. Morita and S. Takagi, Appl. Phys. Lett., 2007, 90(7), 072911.

- 24 Y. Otani, Y. Itayama, T. Tanaka, Y. Fukuda, H. Toyota, T. Ono, et al., Appl. Phys. Lett., 2007, 90(14), 142114.

- 25 G. V. Rao, M. Kumar, T. Rajesh, D. R. K. Reddy, D. Anjaneyulu, B. Sainath, et al., Materials Today: Proceedings, 2018, 5(1), 650-656.

- 26 Y. J. Lee, J. Cryst. Growth, 2004, 266(4), 568-572.

- 27 A. Ahmed, A. Rys, N. Singh, J. Edgar and Z. Yu, J. Electrochem. Soc., 1992, **139**(4), 1146–1151.

- 28 M. Morita, S. Isogai, K. Tsubouchi and N. Mikoshiba, Appl. Phys. Lett., 1981, 38(1), 50-52.

- 29 X.-H. Xu, H.-S. Wu, C.-J. Zhang and Z.-H. Jin, Thin Solid Films, 2001, 388(1-2), 62-67.

- 30 A. C. Jones, C. R. Whitehouse and J. S. Roberts, Chem. Vap. Deposition, 1995, 1(3), 65-74.

- 31 D. Riihelä, M. Ritala, R. Matero, M. Leskelä, J. Jokinen and P. Haussalo, Chem. Vap. Deposition, 1996, 2(6), 277-283.

- 32 P. Kelly and R. Arnell, Vacuum, 2000, 56(3), 159-172.

- 33 G. Thompson, P. Skeldon, X. Zhou, K. Shimizu, H. Habazaki and C. Smith, Aircr. Eng., 2003, 75(4), 372-379.

- 34 S. Kai Wang, H.-G. Liu and A. Toriumi, Appl. Phys. Lett., 2012, **101**(6), 061907.

- 35 P. Motamedi and K. Cadien, Appl. Surf. Sci., 2014, 315, 104-109.

- 36 J.-J. Huang, L.-T. Huang, M.-C. Tsai, M.-H. Lee and M.-J. Chen, Appl. Surf. Sci., 2014, 305, 214-220.

- 37 C. Zhao, S. Taylor, M. Werner, P. Chalker, R. Murray, J. Gaskell, et al., J. Appl. Phys., 2009, **105**(4), 044102.

- 38 D. Vanderbilt, X. Zhao and D. Ceresoli, Thin Solid Films, 2005, 486(1-2), 125-128.

- 39 J. Robertson, Rep. Prog. Phys., 2005, 69(2), 327.

- 40 S. Bang, S. Lee, S. Jeon, S. Kwon, W. Jeong, S. Kim, et al., J. Electrochem. Soc., 2008, 155(9), H633-H637.

- 41 C. Scanlan, M. Gajdardziska-Josifovska and C. Aita, Appl. Phys. Lett., 1994, 64(26), 3548-3550.

- 42 Y.-H. Wu, L.-L. Chen, R.-J. Lyu, M.-Y. Li and H.-C. Wu, IEEE Electron Device Lett., 2010, 31(9), 1014-1016.

- 43 R. Hegde, D. Triyoso, S. Samavedam and B. White Jr, J. Appl. Phys., 2007, 101(7), 074113.

**RSC Advances**

- 45 R. Engel-Herbert, Y. Hwang and S. Stemmer, *J. Appl. Phys.*, 2010, **108**(12), 124101.

- 46 E. H. Nicollian, J. R. Brews and E. H. Nicollian, MOS (metal oxide semiconductor) physics and technology, Wiley, New York, 1982.

- 47 K. Martens, C. O. Chui, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, et al., IEEE Trans. Electron Devices, 2008, 55(2), 547.

- 48 C.-C. Hsu, W.-C. Chi, Y.-H. Tsai, M.-L. Tsai, S.-Y. Wang, C.-H. Chou, et al., J. Vac. Sci. Technol., B, 2018, 36(5), 051204.

- 49 A. Nayfeh, C. O. Chui, K. C. Saraswat and T. Yonehara, *Appl. Phys. Lett.*, 2004, **85**(14), 2815–2817.

- 50 C.-M. Lin, H.-C. Chang, I.-H. Wong, S.-J. Luo, C. Liu and C. Hu, *Appl. Phys. Lett.*, 2013, **102**(23), 232906.

- 51 F. Ji, J. Xu, P. Lai, C. Li and J. Liu, *IEEE Electron Device Lett.*, 2011, 32(2), 122–124.