# **RSC Advances**

PAPER

View Article Online

View Journal | View Issue

Cite this: RSC Adv., 2018, 8, 36584

# Potential solution-induced HfAlO dielectrics and their applications in low-voltage-operating transistors and high-gain inverters†

Recently, much attention has been paid to the investigation of solution-driven oxides for application in thin film transistors (TFTs). In current study, a fully solution-based method, using 2-methoxyethanol as solvent, has been adopted to prepare InZnO thin films and HfAlO<sub>x</sub> gate dielectrics. Amorphous HfAlO<sub>x</sub> thin films annealed at 600 °C have shown a high transparency (>85%), low leakage current density (6.9  $\times$  10<sup>-9</sup> A cm<sup>-2</sup> at 2 MV cm<sup>-1</sup>), and smooth surface. To verify the potential applications of HfAlO<sub>x</sub> gate dielectrics in oxide-based TFTs, fully solution-induced InZnO/HfAlO<sub>x</sub> TFTs have been integrated. Excellent electrical performance for InZnO/HfAlO<sub>x</sub> TFTs annealed at 450 °C has been observed, including a low operating voltage of 3 V, a saturated mobility of 5.17 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a high  $I_{\rm on}/I_{\rm off}$  of  $\sim$ 10<sup>6</sup>, a small subthreshold swing of 87 mV per decade, and a threshold voltage shift of 0.52 V under positive bias stress (PBS) for 7200 s, respectively. In addition, time dependent threshold voltage shift under PBS could be described by a stretched-exponential model, which can be due to charge trapping in the semiconductor/dielectric interface. Finally, to explore the possible application in logic operation, a resistor-loaded inverter based on InZnO/HfAlO<sub>x</sub> TFTs has been built and excellent swing characteristic and well dynamic behavior have been obtained. Therefore, it can be concluded that fully solution-driven InZnO/HfAlO<sub>x</sub> TFTs have demonstrated potential application in nontoxic, eco-friendly and low-power consumption oxide-based flexible electronics.

Received 20th September 2018 Accepted 10th October 2018

DOI: 10.1039/c8ra07813k

rsc.li/rsc-advances

## 1 Introduction

Large-area backplane electronics for upcoming displays have attracted more attention and demonstrated potential applications in next-generation active matrix displays and flexible electronics, such as smart windows, transparent tablets, interactive white boards, and so on.<sup>1,2</sup> To operate these frontier displays, transparent thin-film transistors (TFTs) with high performance should be built as switching or driving components. Currently, amorphous metal-oxide TFTs have obtained increasing interest owing to the high electron mobility, high transparency, excellent electrical performance for high-speed driving, and solution processability for advanced processing, which is superior to those of the conventional amorphous or poly silicon TFTs.<sup>3-5</sup> Among the various oxide semiconductor materials, indium–zinc oxide (IZO)-based oxide semiconductor has been considered a promising candidate for the active layer of oxide-based TFTs,

exhibiting an optical transmittance of more than 85%, an optical

Much effort has been dedicated to the investigation of binary high-*k* dielectric materials, such as ZrO<sub>2</sub>, TiO<sub>2</sub>, and HfO<sub>2</sub> in the oxide-based TFTs due to their high dielectric constant and wide band gap.<sup>13–15</sup> Considering their desirable electrical properties and good process compatibility with oxide semiconductors, Hf-based oxide dielectrics have been regarded as good candidates in the display industry.<sup>5,16</sup> However, the low crystallization temperature and the formation of the grain boundaries for Hf-based high-*k* gate dielectrics contribute to the electrical leakage paths and the increased gate leakage current.<sup>17,18</sup> The grain boundary of the crystalline structures in the gate insulator, which degrades the electrical performance, is a critical issue. To resolve this issue, amorphous high-*k* dielectrics have been developed as the potential candidates for the optimal operation of the gate insulator in TFTs.

To increase the crystallization temperature, additional dopants, for instance, Si, Ti, and La are introduced into HfO<sub>2</sub> to form amorphous Hf-based high-*k* oxides.<sup>19-21</sup> Consequently, the crystalline phase of the Hf-based gate dielectrics were suppressed

band gap of around 3.5 eV, and high mobility.<sup>6-9</sup> However, the high power consumption attributed to the high operating voltage impedes the application of oxide-based TFTs.<sup>10-12</sup> To realize the potential application of oxide-based TFTs in mobile and portable devices, high-*k* gate dielectrics have been selected to enhance the capacitive coupling and reduce the power consumption.

Much effort has been dedicated to the investigation of binary

<sup>&</sup>quot;School of Physics and Materials Science, Radiation Detection Materials & Devices Lab, Anhui University, Hefei 230601, P. R. China. E-mail: hegang@ahu.edu.cn

<sup>&</sup>lt;sup>b</sup>Institute of Physical Science and Information Technology, Anhui University, Hefei 230601, P. R. China

<sup>&</sup>lt;sup>c</sup>National Laboratory for Infrared Physics, Chinese Academy of Sciences, Shanghai Institute of Technical Physics, 500 Yutian Road, Shanghai 200083, P. R. China

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: 10.1039/c8ra07813k

Paper

up to 900 °C.22 However, the oxygen diffusion and the reduced dielectric constant after doping degrade the device's performance and prevent its application in TFTs devices. Fortunately, Al incorporating into HfO2 worked effectively with increased crystallization temperature and suppressed oxygen diffusion. 23,24 Furthermore, Al-doped Hf-based oxide showed a considerably low leakage current due to its larger band gap and suitable conduction band offset.25 However, the use of vacuum-based deposition method to obtain Al-doped Hf-based gate oxides, such as atomic layer deposition<sup>26</sup> (ALD) and chemical vapour deposition<sup>27</sup> (CVD), are limited and incompatible with large-scale production and low cost fabrication. Fortunately, solution-based methods such as inkjet printing, dip-coating, and spin-coating are appropriate for resolving this issue. Operational solutionprocessed oxide TFTs represent a vital part of this vision, and the stringent requirements on film quality and electrical characteristics make the realization of such TFTs a challenging goal and a key development milestone.28-30

In current work, we introduce a simple fabrication process with a large area and low-cost processability for a solutionprocessed amorphous hafnium-aluminum oxide (HfAlO<sub>x</sub>) gate insulator. The correlation between microstructure and dielectric properties of promising amorphous high-k HfAlO<sub>x</sub> films has been investigated. The surface morphology and leakage current behaviors of solution processed HfAlO<sub>r</sub> thin films as a function of annealing temperature were examined in terms of its application as gate insulators. To verify the possibility of the solution-derived amorphous HfAlO<sub>r</sub> thin film as gate dielectric in CMOS logics, all-solution-processed IZO-based TFTs and resistor-loaded inverters were also fabricated and examined systematically. Therefore, it can be concluded that the optimized IZO/HfAlO<sub>x</sub> TFTs exhibited optimized electrical performance under a low operating voltage of 3 V, including a high  $I_{\rm on}/I_{\rm off}$  of around 6.01  $\times$  $10^7$ , and a high  $\mu_{\rm sat}$  of 5.17 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup>. Meanwhile, the resistorloaded inverter based on IZO/HfAlOx TFT demonstrates full swing characteristics with a gain of 4.32 at 4.0 V.

# Experimental

#### Precursor solution preparation and characterization

The InZnO precursor solution was prepared by dissolving  $In(NO_3)_3 \cdot xH_2O$  and  $Zn(NO_3)_3 \cdot 6H_2O$  in 2-methoxyethanol. The concentration of IZO precursor solution is 0.1 M and the ratio of In: Zn is 1:1. The HfAlO precursor solution was prepared by dissolving HfCl<sub>4</sub> and Al(NO<sub>3</sub>)<sub>3</sub>·9H<sub>2</sub>O in 2-methoxyethanol. The purity of all the starting materials is 99.9% and purchased from Aladdin pharmaceuticals. The concentration of HfAlO precursor solution is 0.1 M and the ratio of Hf: Al is 2:1. All precursor solutions were stirred vigorously in 600 rpm for 6 h at room temperature. The thermal behaviors of InZnO and HfAlO xerogel were measured using a thermal-gravimetric analyzer (TGA) with a heating rate of 10 °C min<sup>-1</sup> (STA449F3) in air.

#### 2.2 Thin film fabrication and characterization

The substrate was heavily doped p-Si (0.0015  $\Omega$  cm) and acted as gate electrode. The substrates were ultrasonic cleaned in acetone, alcohol and deionized water in sequence for 10 min. The substrates were treated by oxygen plasma for 10 min to enhance hydrophilicity before deposition. The HfAlO solution was filtered through a 0.22 µm syringe filter and spun on the substrates at 5000 rpm for 20 s. Then the films were baked at 150 °C for 10 min and repeat previous procedure once. After deposition, the samples were treated by ultraviolet (UV) light for 30 min and annealed at 300, 400, 500 and 600 °C for 1 h in air. The power of UV lamp was 1 kW and the UV lamp was 20 cm from the samples. The microstructures of HfAlO<sub>r</sub> thin films were investigated by X-ray diffractometer (XRD, MXP 18AHF-MAC Science, Yokohama). The absorbance and transmittance of HfAlO<sub>x</sub> films deposited on quartz substrate were measured by a UV-Vis spectrophotometer (Shimadzu, UV-2550). The surface morphologies of HfAlO were measured by using atomic force microscope (AFM, Smart Lab, Multimode 8). The chemical compositions of HfAlO<sub>x</sub> were analyzed by X-ray photoelectron spectroscopy (XPS, ESCALAB 250Xi). C 1s peak at 284.6 eV was taken as a reference for charge correction. The charge neutralizations of X-ray bombarded samples were performed by flood guns and spectral deconvolution was performed by Shirley background subtraction using a Voigt function convoluting Gaussian and Lorentzian functions. The thicknesses of HfAlO<sub>x</sub> and IZO thin films were measured by spectroscopic ellipsometry (SE, SANCO Co, Shanghai, SC630). A MOS structure of Al/HfAlO/ p<sup>+</sup>-Si was used to measure the dielectric properties of HfAlO films by an impedance analyzer (Agilent 4294A).

#### 2.3 TFTs fabrication and characterization

The InZnO solution was spun on the HfAlO<sub>r</sub> films at 5000 rpm for 20 s. Then the samples were annealed at 350, 400, 450 and 500  $^{\circ}\mathrm{C}$ for 1 h in air. Finally, the Al source and drain electrodes were deposited on the films via a shadow mask. The channel length and width were 100 and 1000 um. In addition, the SiO<sub>2</sub>-based TFTs were preparation for comparison. The 200 nm-thick SiO<sub>2</sub> was obtained by heavily doped p-Si with the thermal oxidation procedure. The detailed schematic diagram of the solutionderived IZO and HfAlOx thin films and In2O3-based TFTs fabrication are demonstrated in Fig. S1 (ESI).† The electrical properties of the integrated TFTs were measured by using semiconductor parameter analyzers (Keithley 2636B; Agilent B1500A) in a dark box. The saturation mobility ( $\mu_{sat}$ ) was extracted from transfer characteristics using the following equation31

$$\mu_{\rm sat} = \frac{2L}{WC_{\rm i}} \left( \frac{\partial \sqrt{I_{\rm DS}}}{\partial V_{\rm GS}} \right)^2$$

where  $C_i$  is the areal capacitance of the gate dielectric, W and Lare the channel width and length of the TFT, VG is the gate voltage and  $V_{TH}$  is the threshold voltage, which was determined in the saturation region by linear fitting  $I_D^{1/2}$  vs.  $V_G$  plot. The density of interface states  $(D_{it})$  can be inferred using the following equation,31

$$D_{\mathrm{it}} = \left[ rac{\mathrm{SS} \, \log(e)}{rac{kT}{q}} - 1

ight] \, rac{C_{\mathrm{i}}}{q}$$

where k, T, and q are Boltzman's constant, absolute temperature, and charge quality, respectively.

# 3 Results and discussion

# 3.1 Microstructure analysis and surface morphology of solution-derived $HfAlO_x$ thin films

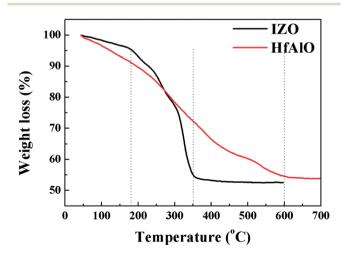

To investigate the thermal behavior of IZO and HfAlO<sub>r</sub> thin films, TGA measurement of HfAlO<sub>r</sub> and IZO precursor solutions was performed with a heating rate of 10 °C min<sup>-1</sup> and the experimental result is demonstrated in Fig. 1. For IZO xerogel, the initial decrease of weight for IZO below 180 °C is attributed to the decomposition of the residual nitrate species originating from the metal nitrate salt.32 The continuous decreased weight between 180 °C to 350 °C can is mainly due to the dihydroxylation.<sup>33</sup> When the temperature exceeds 350 °C, the reduction in mass has not been observed, suggesting that complete transformation from xerogel to IZO oxide has been completed. For HfAlO<sub>x</sub> xerogel, the transformation in the decomposition process of HfAlO<sub>r</sub> xerogel is not similar to IZO xerogel. It could be noted that the dehydroxylation and alloy reaction begin at the initial stage. A more pronounced, gradual mass loss over several hundred degrees have been detected. Conversion of the HfAlO precursor to the corresponding oxide is completed by 600 °C. Based on this dehydroxylation behavior, the annealing temperature range for clear gate switching modulation of successful oxide TFTs is estimated to range from 350 °C to 600 °C.

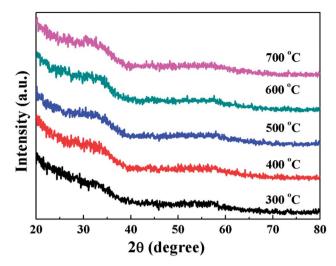

The evolution of the microstructure of the spin-coated  $HfAlO_x$  films annealed at various temperatures was investigated by XRD measurements and the results are demonstrated in Fig. 2. No apparent diffraction peaks of crystalline phase in XRD patterns have been observed in the films regardless of the annealing temperature, indicating that the  $HfAlO_x$  films are identified as amorphous phase. It is confirmed further that introducing appropriate amount of  $Al_2O_3$  in  $HfO_2$  would remarkably block the crystallization of the  $HfO_2$  films and lead to the increase of crystallization temperature of  $HfO_2$ , which is in good agreement with our previous investigation.<sup>34</sup> Being

Fig. 1 Thermal behavior of the solution-induced IZO and  ${\rm HfAlO}_x$  xerogel.

Fig. 2 Annealing temperature dependent XRD patterns of  $\mathrm{HfAlO}_{x}$  films.

a dielectric layer for the bottom-gated TFTs, the amorphous phase is more suitable than the crystalline phase owing to its smooth surface, low leakage current, and high breakdown electric field. According to the grain-boundary charge-trapping model, <sup>35</sup> the grain boundary usually acts as the trapping and scattering center in polycrystalline film, leading to the high leakage current and the degraded insulating reliability. <sup>33</sup> Such dielectrics certainly show high off-state current in TFT devices. In addition, the amorphous thin films generally exhibit smoother surface roughness compared with the crystalline ones, which is a prerequisite for expeditious charge carrier mobility in the TFT devices. <sup>36</sup>

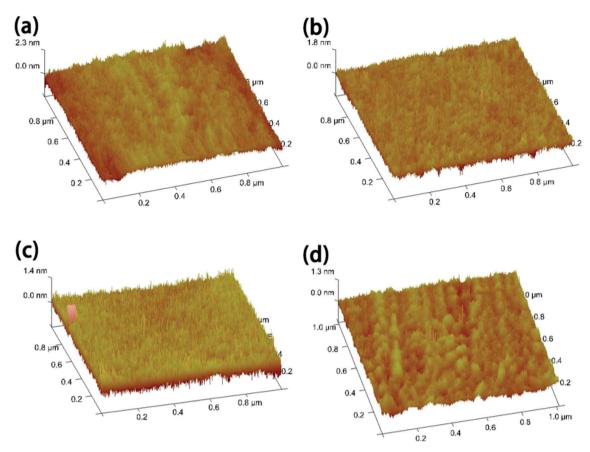

It is well known that high-performance TFTs should have dielectric layers with smooth surface as the carrier transport is affected by the interface between the channel and the dielectric layers. To investigate the evolution of the surface morphology of HfAlO<sub>x</sub> films as a function of annealing temperature, AFM images of the solution-derived  $HfAlO_x$  films are shown in Fig. 3. The root-mean-square (RMS) values of HfAlO films annealed at 300, 400, 500 and 600 °C are 0.266, 0.189, 0.205, and 0.147 nm, respectively. It is obvious to see that RMS values smaller than 1 nm are observed for solution-processed HfAlO<sub>r</sub> dielectrics, which is conductive to the growth of high-quality channel layer and improve the TFTs' performance. The smooth surface of the HfAlO films is not only attributed to their amorphous structure, but also to the use of UV annealing treatment. Based on the investigation from Tak et al., it can be noted that UV treatment consists of three main reactions (Fig. S2†). First, physical bonds are effectively converted into chemical bonds. It is proposed that the energy provided by UV light is sufficient to decompose residual weak chemical bonds in spin-coated oxide films, and the simultaneous thermal treatment induces the reorganization and rearrangement of the decomposed chemical bonds into strong chemical bonds. Second, UV treatment promoted the oxidation of the gate dielectric films and led to a lower number of uncoordinated oxygen species. Third, the increased surface energy of the oxide films indicates highly chemically reactive states and improved surface smooth. Therefore, it can be

Fig. 3 Surface morphologies of (a) 300 °C, (b) 400 °C, (c) 500 °C and (d) 600 °C-annealed HfAlO<sub>x</sub> films.

concluded that UV treatment can effectively accelerate the decomposition of organic ligands, reduce the nanopores in the films, and attribute the increased surface energy and the decreased surface roughness. 17,37,38

# 3.2 Optical properties analysis of solution-derived $HfAlO_x$ thin films

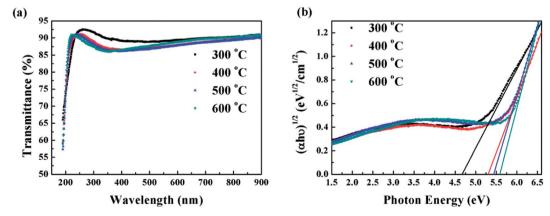

To investigate the optical properties of the  $HfAlO_x$  films, transmittance and absorbance of the  $HfAlO_x$  films were measured. Fig. 4 shows the optical transmittance and absorbance spectra of  $HfAlO_x$  films as a function of annealing

temperature. All the samples demonstrate high average optical transmittance values (>85%) in the visible region, indicating that  $HfAlO_x$  films can be considered as candidate dielectric materials for transparent devices. By using a standard Tauc plot method, the optical bandgap ( $E_g$ ) is calculated and the results are displayed in Fig. 4b. It can be seen that the  $E_g$  value increases from 4.76 to 5.57 eV when annealing temperature changes from 300 to 600 °C. Apparently, blue shift in band gap has been detected with the increase of the annealing temperature. For the low-temperature-driven  $HfAlO_x$  thin film, the presence of defects in the thin film would produce localized states in the bandgap, leading to the reduced bandgap energy of

Fig. 4 (a) Optical transmittance and (b) band gap of HfAlO<sub>x</sub> films annealed at different temperature

**RSC Advances** Paper

the film. After high temperature annealing, the annihilation of oxygen vacancies/defects results in a decrease of the density of states in the band structure, which leads to an increased bandgap energy of the  $HfAlO_x$  thin films.<sup>28</sup> The increased  $E_g$  is beneficial for suppressing the carrier transport from channel to gate dielectric.

#### Chemical bonding states of HfAlO<sub>x</sub> thin films 3.3

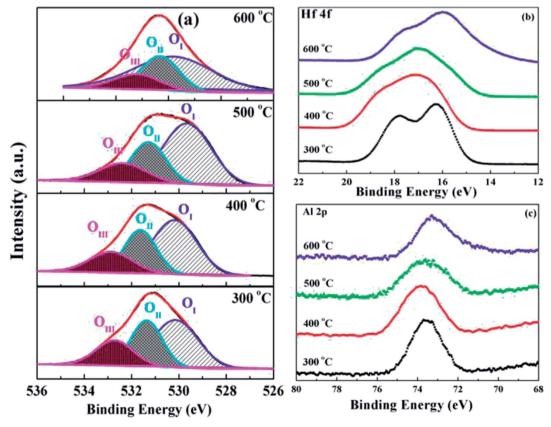

The chemical bonding states and compositions of sputteringderived HfAlOx thin films were analyzed by XPS. Fig. S3† displays the survey spectra of the HfAlO<sub>x</sub> thin films as a function of annealing temperature. It can be noted that Hf, Al, O, and C have been detected, suggesting that all the films are free from other contaminations and Al is successfully incorporated into the HfO<sub>2</sub> gate dielectrics. O 1s XPS spectra for HfAlO<sub>x</sub> thin films have been demonstrated in Fig. 5a and deconvoluted O 1s spectra centered at 530.14 eV, 531.36 eV and 532.73 eV, have been observed, respectively. The peak located at 530.14 eV is assigned to the metal-oxygen bond (O<sub>I</sub>) in HfAlO<sub>x</sub> lattice and the peak located at 531.36 eV is attributed to the oxygen vacancy (O<sub>II</sub>) in lattice.<sup>39,40</sup> The peak centered at 532.73 eV may be related to loosely bound oxygen on the surface of films, such as adsorbed H<sub>2</sub>O and -OH. 41 Increasing the annealing temperature from 300 to 600 °C, the fraction of O<sub>I</sub> in HfAlO<sub>x</sub> increases and O<sub>II</sub> and OIII species decrease, which indicates that high temperature annealing reduces the oxygen vacancy and hydroxyl species, and improves the metal-oxygen lattice. The presence

OII and OIII generally creates trap and defect states in the band gap of the dielectric film, leading to the increased leakage current and the reduced breakdown voltage.42 Therefore, higher temperature annealing is effective in controlling the oxygen vacancy and bonded oxygen content and obtain high quality high-k gate dielectric for application in TFT devices. To obtain more information on chemical bonding states from HfAlOx thin films, the evolution of the Hf 4f and Al 2p core-level XPS spectra related to annealing temperature has been investigated, as shown in Fig. 5b and c. Compared to HfO2, the doublet peaks corresponding to Hf 4f<sub>5/2</sub> and Hf 4f<sub>7/2</sub> for HfAlO<sub>x</sub> thin films shift towards higher binding energy sides, indicating the formation of Hf-aluminate.34 However, for the 600 °C-annealed sample, the shift of binding energy in Hf 4f peak towards lower energy side has been detected, which can be due to the decomposition of HfAlO<sub>x</sub> and partial formation of HfO<sub>2</sub>. The same trend has been observed for Al 2p core-level XPS spectra.

### 3.4 Dielectric and electrical properties of solution-derived HfAlOx thin films

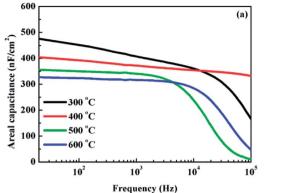

To investigate the annealing temperature dependence on the dielectric and electrical properties of the solution-driven HfAlOx thin films, MOS capacitors based on Al/HfAlO/p<sup>+</sup>-Si were constructed. Fig. 6a shows the areal capacitance (C) as a function of frequency (f) for HfAlOx capacitors. The areal capacitance of HfAlO capacitors annealed at 300, 400, 500 and 600 °C is 475, 404, 355, and 326 nF cm<sup>-2</sup> at 20 Hz, respectively. It can be noted

Fig. 5 XPS spectra of O 1s (a), Hf 4f (b), and Al 2p (c) peaks for HfAlO<sub>x</sub> dielectrics as a function of annealing temperature.

**RSC Advances** Paper

(a) Capacitance-frequency curves and (b) leakage current density-electric field curves of Al/HfAlO/p<sup>+</sup>-Si capacitor.

that reduction in the areal capacitance has been observed with the annealing temperature increasing from 300 to 600 °C. Generally speaking, water molecules can be absorbed by polarizable hydroxyl groups. Previous XPS results have confirmed the existence of the large number of polarizable hydroxyl groups in low-temperature-processed HfAlO<sub>r</sub> thin films. Therefore, absorbed water molecules would lead to the high capacitance owing to the high dielectric constant of water molecules. 43 At the same time, the slight decreases for the areal capacitance in the high frequency range can be attributed to the limited polarization response time. 44 To evaluate the leakage behavior of the HfAlO<sub>x</sub> thin films, the corresponding leakage current densities and electric field characteristics of MOS capacitors annealed at different temperatures have been shown in Fig. 6b. For the lowtemperature-annealing sample, the relatively large leakage current density may be attributed to the incomplete decomposition of hydroxyl groups. The reduced leakage current density has been observed with the increase in the annealing temperature, which probably originates from the gradually decomposition of residuals and the reduced defect density. For the 600 °Cannealed sample, the lowest leakage current density of 6.0  $\times$ 10<sup>-9</sup> A cm<sup>-2</sup> at 2 MV cm<sup>-1</sup> has been achieved. As a result, it can be inferred that the excellent electrical performance for 600 °Cannealed solution-processed HfAlO<sub>r</sub> dielectric thin films guarantees its potential application in low-voltage transistor.

#### Solution-driven IZO TFTs based on HfAlO<sub>x</sub> dielectric

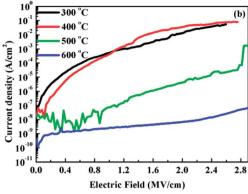

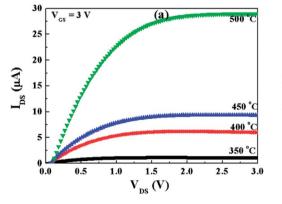

Based on above analysis, it can be noted that the 600 °C-processed HfAlO<sub>x</sub> gate dielectric completely meets the application requirements of TFTs. Before investigating the feasibility of solutionprocessed HfAlO<sub>r</sub> as gate dielectric in TFTs, the possibility of solution-derived IZO/SiO<sub>2</sub> TFTs with bottom-gate and top-contact architecture was evaluated. The solution-processed IZO channel layers were annealed at 350-500 °C. The output curves of each IZO/ SiO<sub>2</sub> TFTs are shown in Fig. S4† and the annealing temperature dependent output characteristics of the IZO/SiO2 TFTs, at a gate voltage of  $(V_{GS})$  of 40 V, are depicted in Fig. 7a. The low saturation current at 350 °C may mainly attributed to the existed hydroxyl groups and the formation of defect states. When increasing the annealing temperature, the increased saturation current has been observed, indicating the reduced lattice defects, such as hydroxides and residual impurities.45 The representative transfer characteristics of  $In_2O_3$  TFTs, at a drain voltage of  $(V_{DS})$  of 20 V, are displayed in Fig. 7b. The  $\mu_{\text{sat}}$  and threshold voltage  $(V_{\text{TH}})$  in the saturation region were determined from linear fits to the dependence of the square root of  $I_D$  on  $V_G$ . The subthreshold swing (SS) was extracted from the linear portion of a plot of the log ID versus  $V_{\rm G}$ . The extracted key TFTs performance parameters as a function of annealing temperature are summarized in Table 1. It can be seen that  $\mu_{\text{sat}}$  values increase from 0.15 to 3.08 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup> with the increase in annealing temperature, which can be due to the

Fig. 7 (a) Output and (b) transfer curves of IZO/SiO<sub>2</sub> TFTs as a function of annealing temperature

**RSC Advances**

Table 1 Electrical parameters of IZO/SiO<sub>2</sub> TFTs annealed at different temperature

|                          | $V_{\mathrm{TH}}$ (V) | $\Delta V_{\mathrm{TH}}$ (V) | $I_{\rm on}/I_{\rm off}$ | $\mu  (\mathrm{cm}^{-2}  \mathrm{V}^{-1}  \mathrm{s}^{-1})$ | SS (mV per decade) | $N_{\mathrm{T}} \left(\mathrm{cm}^{-2}\right)$ |

|--------------------------|-----------------------|------------------------------|--------------------------|-------------------------------------------------------------|--------------------|------------------------------------------------|

| 350 °C                   | 13.5                  | 2.5                          | $4 \times 10^6$          | 0.15                                                        | 633                | $9.57 \times 10^{11}$                          |

| 400 °C                   | 15.0                  | 3.2                          | $4\times 10^6$           | 0.40                                                        | 646                | $9.78 \times 10^{11}$                          |

| 450 °C                   | 13.9                  | 2.2                          | $8 \times 10^6$          | 1.42                                                        | 507                | $7.46 \times 10^{11}$                          |

| $500~^{\circ}\mathrm{C}$ | 13.0                  | 2.6                          | $4 \times 10^4$          | 3.08                                                        | 2469               | $4.02\times10^{12}$                            |

decomposition of organic groups and the formation of metaloxygen bonds. Meanwhile, increase in  $I_{on}/I_{off}$  and reduction in SS have been detected with the increased annealing temperature, which can be attributed to the reduced oxygen vacancy and free carrier concentration. However, further increasing the annealing temperature for IZO channel layer to 500 °C results in the degraded device performance, originating from the increased trap states near the IZO/SiO<sub>2</sub> interface, confirmed by the D<sub>it</sub> values shown in Table 1. On the basis of the extracted electrical parameters, it can be noted that the solution-derived 450 °C-annealed IZO/SiO<sub>2</sub> TFTs demonstrates the optimized electrical performance, including a high  $\mu_{\rm sat}$  of 1.41 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup>, a high  $I_{\rm on}/I_{\rm off}$  value of 10<sup>6</sup>, and a small SS value of 0.507 V dec<sup>-1</sup>, respectively. However, all the TFTs devices operate at high voltages and hence increase the power consumption due to the low dielectric constant for SiO<sub>2</sub>. To decrease the operation voltage and reduce the power consumption of solution-derived IZO TFTs, high-k gate dielectric should be explored.

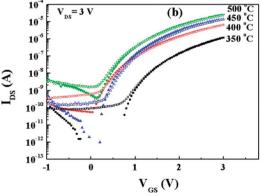

In order to validate the usefulness of high-k HfAlO<sub>r</sub> film as gate insulators for TFTs, bottom-gated fully solution-derived IZO/HfAlOx TFTs were fabricated. Previous 600 °C-annealed HfAlO<sub>x</sub> has been adopted to act as the dielectric layer due to its relatively low leakage current and good dielectric properties. A solution-processable IZO precursor solution was spin-coated on a HfAlOx/Si stack, followed by annealing from 350 to 500 °C to pursue the optimized TFTs device performance.

Fig. S5† displays the output curves of each TFT and the summarized output curves of IZO/HfAlO $_x$  TFTs at a  $V_{GS}$  of 3 V are shown in Fig. 8a. It can be seen that the output characteristics of IZO/HfAlOx TFTs exhibit typical n-channel conduction behavior with clear pinch-off voltage and current saturation. By comparing the transfer curves of IZO/HfAlOx TFTs with IZO/ SiO<sub>2</sub> TFTs, it can be seen that the off-current region increases

with decreasing  $V_{GS}$  for the IZO/HfAlO<sub>x</sub> TFTs while the IZO/SiO<sub>2</sub> TFTs remains flat, which can be due to the smaller band gap of HfAlO<sub>x</sub> compared with SiO<sub>2</sub>, and thus, the carrier injection into the HfAlO<sub>r</sub> will be much easier than into SiO<sub>2</sub>. Interestingly, by replacing SiO2 with high-k HfAlOx thin film, the operation voltage drastically reduces from 40 V to 3 V. As a result, the HfAlO<sub>x</sub>/IZO TFTs expend lower consumption than the SiO<sub>2</sub>/IZO TFTs. Because the field-induced current is proportional to the field-induced charge density, a reasonable technique to achieve low-voltage operation in TFT is to use HfAlO<sub>x</sub> as the gate dielectric, which can afford greater surface charge density at the semiconductor/dielectric interface. Fig. 8b shows the representative transfer characteristics of TFTs based on 600 °Cannealed HfAlOx films as a function of the annealing temperature. The extracted electrical characteristics, including the  $\mu_{\rm sat}$ ,  $I_{\rm on}/I_{\rm off}$ ,  $V_{\rm TH}$ ,  $D_{\rm it}$ , and SS, of HfAlO<sub>x</sub>/IZO TFTs with different annealing temperatures were summarized in Table 2. With the increase of the annealing temperature from 350 to 450 °C,  $V_{\rm TH}$ and SS decrease from 1.63 and 120 to 1.14 V and 87 mV  $dec^{-1}$ , while  $I_{\rm on}/I_{\rm off}$  and  $\mu_{\rm sat}$  increase from 10<sup>4</sup> and 0.80 to 10<sup>6</sup> and 9.50 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup>, respectively. Apparently, the optimized electrical performance has been achieved for 450 °C-annealed HfAlO<sub>x</sub>/IZO TFTs.

In the solution-derived channel layer thin films, oxygen vacancies form when dehydroxylation and polycondensation occur. Thus, it is expected that annealing at a higher temperature leads to the reduction of oxygen vacancy and the formation of more metal-oxygen bonds. As a result,  $V_{\text{TH}}$  shifts towards negative direction as the annealing temperature increases due to the reduced interfacial defects acting as the carrier trap at IZO/HfAlO<sub>x</sub> interface. With increasing the annealing temperature, the oxygen vacancy and free carrier concentration decrease. As a result,  $I_{\rm on}/I_{\rm off}$  initially increases because of the

(a) Output and (b) transfer curves of IZO/HfAlO TFTs as a function of annealing temperature.

$\mu \text{ (cm}^{-2} \text{ V}^{-1} \text{ s}^{-1})$  $\Delta V_{\mathrm{TH}}$  (V) SS (mV per decade)  $N_{\rm T} \, ({\rm cm}^{-2})$  $V_{\rm TH}$  (V)  $I_{\rm on}/I_{\rm off}$ 350 °C 1.63 0.06  $\sim 10^{4}$ 0.80 120  $1.98 \times 10^{12}$  $3.86\times10^{12}$ 400 °C  $\sim \! 10^4$ 1.23 0.10 2.52 177  $8.93\times10^{11}$ 450 °C 1.14 0.19  $\sim \! 10^6$ 5.17 87  $\textbf{4.06}\times\textbf{10}^{12}$ 500 °C 0.09  $\sim \! 10^5$ 9.50 183 1.16

Electrical parameters of IZO/HfAlO TFTs annealed at different temperature

reduced  $I_{\text{off}}$ . As we know, a small SS is expected to achieve a high operation speed and low power consumption. Normally, the SS value is dependent on the traps located in channel/dielectric interface.<sup>37</sup> With the increase in annealing temperature, the reduction in SS value may be attributed to the large areal capacitance of the HfAlOx dielectric layer and the electronicclean interface between IZO and HfAlOx. Based on Jeong's report,46 it can be observed that the conduction band minimum in the metal oxide semiconductors is primarily composed of dispersed vacant s states with short interaction distances for efficient carrier transportation, which can be achieved in ionic oxide but not obviously in hydroxide. Therefore, higher temperature annealing accelerates the decomposition of -OH groups and the alloy reaction and leads to the formation of metal-oxygen framework, which contributes fewer defects in both bulk and interface. For the top-gated TFTs, the carrier transport is limited in a narrow region at channel/dielectric interface. In this regard, the reduced defects at the IZO/ HfAlO<sub>x</sub> interface could achieve the rapid transport of the induced carriers, and thus enhanced  $\mu_{FE}$  would be expected.

From Table 2, it can be noted that the  $D_{it}$  values of IZO/ HfAlO<sub>x</sub> TFTs annealed at 350, 400, and 450 °C are calculated to be  $1.98 \times 10^{12}$ ,  $3.86 \times 10^{12}$ , and  $8.93 \times 10^{11}$  cm<sup>-2</sup>, respectively. A large  $D_{\rm it}$  has been observed in the 350 and 400 °C-annealed TFTs, which is attributed to the incomplete decomposition of residual organic groups and the existence of the defects states near IZO/HfAlO $_x$  interface. Smallest  $D_{it}$  has been obtained for 450 °C-annealed sample, which is lower than that of TFTs based on spin-coated MgO  $(1.1 \times 10^{13} \text{ cm}^{-2})^{47}$  and water-induced ScO<sub>x</sub>  $(1.1 \times 10^{13} \text{ cm}^{-2})$ . Such a small  $D_{\text{it}}$  is not only beneficial to carrier transport in the interface region, but also to the operation stability.

In spite of the high saturation current and the large  $\mu_{sat}$  for 500 °C-annealed IZO/HfAlOx TFTs, the degradation in some

important electrical performance has been observed. Dit for 500  $^{\circ}$ C-annealed IZO/HfAlO<sub>x</sub> TFTs is calculated to be 4.06 imes 10<sup>12</sup> cm<sup>-2</sup>, approaching nearly one magnitude larger than that of IZO/HfAlO<sub>x</sub> TFTs, which can be attributed to the increased trap states near the IZO/HfAlOx interface. Meanwhile, the reduced  $I_{\rm on}/I_{\rm off}$  value for 500 °C-annealed TFTs is mainly caused by the large off-state current ( $I_{\text{off}}$ ), which will lead to the inevitable static power consumption and degrade device performance.49 It is known that static power consumption is comparable to dynamic power in modern silicon chips or even become dominating in the future. 50 Therefore, the Ioff has been regarded as a critical parameter to evaluate the power consumption of a device in modern integrated circuits.

#### Bias stability characterization for solution-driven IZO 3.6 **TFTs**

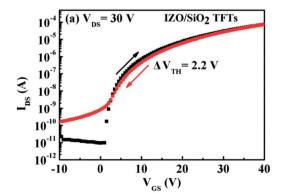

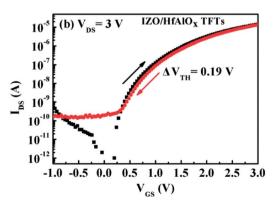

The operational device stability of a given FET is often characterized by the amount of hysteresis between the forward and reverse sweep. Based on Fig. 9, it can be noted that clockwise hysteresis phenomena ( $\Delta V_{\rm TH} = 2.2 \text{ V}$  for IZO/SiO<sub>2</sub> FETs and  $\Delta V_{\rm TH} = 0.19 \text{ V for IZO/HfAlO}_x \text{ TFTs}$ ) have been observed for both TFTs, indicating that accumulated electrons are trapped in the defect states located at dielectric/channel interface.51 During the forward sweeping of the gate voltage, some of the accumulated electrons are transferred into the unoccupied surface states. When the gate voltage is swept back, these states remain filled until the trapped electrons are thermally detrapped, which leads to the clockwise hysteresis. Compared to IZO/ SiO<sub>2</sub> FETs, the hysteresis in IZO/HfAlO<sub>r</sub> TFTs (see Fig. 9b) is reduced substantially, indicating the reduction in the interfacial trap states by the introduction of a high-k HfAlO<sub>x</sub> dielectric, which is consistent with the previous Dit value.

Transfer characteristics of (a) IZO/SiO<sub>2</sub> TFTs and (b) IZO/HfAlO<sub>x</sub> TFTs.

**RSC Advances**

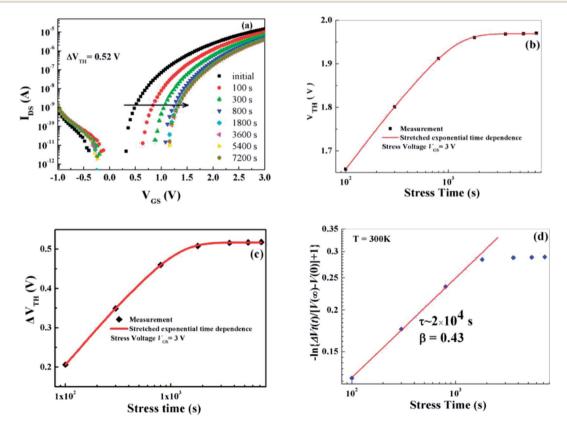

To achieve manufacturability of IZO-based TFT, it is crucial to solve the problems of the threshold-voltage  $(V_{\rm TH})$  shift of the transistor with time under prolonged bias. Any shift in the threshold voltage of the driving transistor under gate and drainbias stress conditions will cause a change in its output drain current, leading to circuit malfunction. Thus, device degradation due to bias-induced instability is a critical issue that must be solved. To investigate the bias stability of the IZO/HfAlO<sub>r</sub> TFTs, positive bias stress (PBS) tests were performed with the source and drain connected to the ground ( $V_{DS} = 0 \text{ V}$ ). Fig. 10a shows the evolution of typical transfer characterization of the 450 °Cannealed IZO/HfAlO, TFTs subjected to a positive gate-bias voltage of 1 V for different stress time at room temperature (T = 25 °C). It can be observed that a parallel shift of the transfer curve toward the positive direction, and the evolution of the shift is from rapid to slow with stress time increasing, indicating there is no additional defect creation at the channel/dielectric interface during bias stressing.4 After the transistor has undergone the gate-bias stressing, the negligible change in the SS and carrier mobility suggests that the creation of extra electron trapping states at the semiconductor/dielectric interface is not significant. At the same time, higher operation stability with a small threshold voltage shift ( $\Delta V_{\rm TH}$ ) of 0.52 V up to 7200 s for 450 °Cannealed IZO/HfAlOx TFTs has been detected, revealing that there are a small number of defects at the IZO/HfAlOx interface, which is confirmed by previous  $D_{it}$  data. The  $V_{TH}$  is presented as a function of stress time on a logarithmic scale in Fig. 10b. Based

on Fig. 10b, it can be noted that  $V_{\mathrm{TH}}$  is shifted significantly at the beginning of the bias stressing, and as the stress continues,  $V_{\text{TH}}$ approaches a saturation value. The shift of  $V_{TH}$  is not accompanied by the SS degradation (Fig. 10a), which indicates that the  $\Delta V_{\rm TH}$  in IZO is attributed to the trapping of electrons in the interface or bulk dielectric layers with negligible creation of additional interface traps. 52

The investigation of the time dependence of  $\Delta V_{\rm TH}$  can be used to confirm the dominant charge trapping mechanism causing the bias stress-induced  $\Delta V_{\rm TH}$  in TFTs.<sup>53</sup> To further investigate the bias stress-induced threshold voltage shift phenomenon in IZO/HfAlOx TFTs, the stress time dependences of  $\Delta V_{TH}$  under positive gate-bias voltage of 1 V at room temperature is examined and shown in Fig. 10c. The  $\Delta V_{\mathrm{TH}}$  is defined as  $\Delta V_{\text{TH}} = V_{\text{TH},t} - V_{\text{TH},i}$ , where  $V_{\text{TH},t}$  is the  $V_{\text{TH}}$  value at the measured time and  $V_{\text{TH,i}}$  is the initial  $V_{\text{TH}}$ . From Fig. 10c, it can be seen that the threshold voltage shifts rapidly and then is saturated quickly with the increase of stress time. Previous investigation on the bias stress-induced degradation of IGZObased TFTs have indicated that the time dependence of  $\Delta V_{TH}$ under bias stresses in IGZO TFTs is followed by a logarithmic time-dependence model,53 but current work shows that the time dependence of  $\Delta V_{TH}$  can be fitted well with a stretchedexponential equation for all stress conditions, which has been developed to model the  $\Delta V_{\mathrm{TH}}$  based on the charge trapping mechanism in α-Si TFT with high-k dielectric.52 The stretched exponential model of  $\Delta V_{\text{TH}}$  is defined as<sup>53</sup>

Fig. 10 (a) Transfer curves of 450  $^{\circ}$ C annealed IZO/HfAlO<sub>x</sub> TFTs under PBS test. (b) The  $V_{\text{TH}}$  as a function of stress time. (c) The time dependence of  $\Delta V_{TH}$  in the IZO/HfAlO TFTs under the bias stress of 3 V. (d) Threshold voltage shifts during bias stress at T=300 K on a  $\log_{10}[-\ln{\{\Delta V_t(t)/[V(\infty)-1\}\}}]$ V(0)] + 1]] vs.  $\log_{10}(t)$  plot. The data have been fitted to a stretched exponential  $\{1 - \exp[-(t/t_0)^{\beta}]\}$ , which reads a straight line in this format.

Paper

(b) (a)  $V_{\rm DD}=2$  V Gain (c) ō 2 1.0 0.0 0.5 1.5 2.0 2.5 (d)  $V_{IN}(V)$  $V_{in}(V)$ oltage swing (%) 4.0 3.5 3.0 2.5 2.0 1.0 0.5 5

Voltage Gain

Fig. 11 (a) The VTCs and (b) signal gain of resistor-loaded inverter coupled with 450 °C-IZO/HfAlO TFTs. (c) The voltage gain and the voltage swing of the inverter at various V<sub>DD</sub> values. (d) Dynamic switching behavior of the inverter under square-waves at 1 Hz. The inset in (c) shows the noise margin calculation from VTC curve collected at 4 V  $V_{\rm DD}$ .

3

Time (s)

$$\Delta V_{\rm TH} = \Delta V_{\rm TH0} \left[ 1 - e^{-\left(\frac{t}{\tau}\right)^{\beta}} \right]$$

Supply Voltage (V)

where  $\Delta V_{\text{TH0}}$  is the  $\Delta V_{\text{TH}}$  at infinite time, approximating the voltage drop across the insulator; t is the stress time;  $\tau$  is the characteristic detrapping time of carriers, and  $\beta$  is the stretched exponential exponent. In Fig. 10d, typical bias-stress curves for  $V_{\rm GS} = 3 \text{ V}, T = 300 \text{ K} \text{ are plotted as } -\ln{\{\Delta V_t(t)/[V(\infty) - V(0)] + 1\}}$ over t on a double-logarithmic scale, where  $V(\infty)$  is the applied gate bias and V(0) is the initial threshold voltage. In this format, a stretched exponential dependence gives a straight line. From the linear fits, a characteristic trapping time ( $\tau$ ) of 2 × 10<sup>4</sup> s and a stretched exponential constant ( $\beta$ ) of 0.43 have been determined. These results are consistent with those for InGaZnObased TFT, where charge trapping phenomenon is also considered as the dominant mechanism of bias-stress-induced  $\Delta V_{\mathrm{TH}}$ . 54

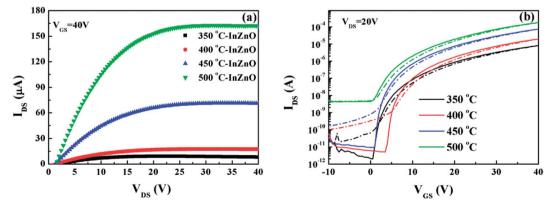

#### Resistor-loaded inverter

In spite of the improved electrical performance and traditional application in TFTs for solution-processed high-k gate dielectric films, the potential applications in more complex logic circuits were ignored. Encouraged by the excellent performance of 450 °C-derived IZO/HfAlO<sub>x</sub> TFTs, their applications in inverter were further explored to demonstrate the logic operations.<sup>53</sup> A simple unipolar resistor-loaded inverter was fabricated by coupling the 450 °C-annealed IZO/HfAlO<sub>x</sub> TFTs with a 2.0 M $\Omega$  resistor.

Fig. S6† shows the schematic diagrams and top views of the unipolar inverters, respectively. The  $V_{\rm in}$ ,  $V_{\rm out}$ , and  $V_{\rm DD}$  represent input voltage, output voltage, and supplied voltage, respectively. Fig. 11a shows voltage transfer characteristic (VTC) of the inverters logic circuit with the  $V_{\rm DD}$  changing from 1 to 4.0 V. Distinct inverter characteristics are observed for the logic inverters at various  $V_{DD}$ , in which the output voltage  $(V_{out})$  is switched between  $V_{\rm DD}$  and 0 V when scanning input voltage  $(V_{\rm in})$ from 0 to 3 V. If the  $V_{\rm in}$  is 0 V, the inverter operates in the offstage, resulting in  $V_{\rm out}$  close to  $V_{\rm DD}$ . If the  $V_{\rm in}$  is 3.0 V, the inverter turns on, resulting in  $V_{\rm out}$  close to the ground level. Thus, when the  $V_{\rm in}$  operates with a low and logical 0 signal, the  $V_{\rm out}$  responds a high and logical 1 signal. Likewise, when the  $V_{\rm in}$ operates with a high and logical 1 signal, the  $V_{\text{out}}$  responds a low and logical 0 signal. These results indicate that our logic circuit demonstrates full swing characteristics. The voltage gain, defined as  $-\partial V_{\text{out}}/\partial V_{\text{in}}$ , is displayed in Fig. 11b as a function of  $V_{\rm DD}$ . A linear dependence between the voltage gain and  $V_{\rm DD}$  is observed. The maximum voltage gain of 4.46 has been obtained for  $V_{\rm DD}$  at 4.0 V, which is larger than that of previous reported oxide TFT circuits at the same supply voltage.55 It should be noted here that a voltage gain of 2.5 is sufficient to drive the next stage component in a logic circuit.55 The voltage swing, which is defined as  $[V_{\rm out,max}-V_{\rm out,min}]/V_{\rm DD} imes 100\%$ , increases slightly from 82% to 91% when increasing  $V_{\rm DD}$  from 1 to 4 V (Fig. 11c). The wider voltage swing of the inverter improves the noise margin characteristics, which makes the inverter run more reliably in the complex logic system. The improvement in

**RSC Advances** Paper

voltage swing and gain with  $V_{\rm DD}$  can be attributed to a high capacitive efficiency.55 Another important parameter is the noise margin, which is usually used to evaluate the multistage circuit operation reliability. The noise margin calculation from VTC collected at  $V_{\rm DD}$  of 4 V is shown in the inset of Fig. 11c. The high  $(N_{\rm MH})$  and low  $(N_{\rm ML})$  noise margins of the inverter are defined as  $N_{\rm MH} = V_{\rm OH} - V_{\rm IH}$  and  $N_{\rm ML} = V_{\rm IL} - V_{\rm OL}$ , <sup>53</sup> where  $V_{\rm OH}$ and  $V_{\rm OL}$  represent output high and low voltage;  $V_{\rm IH}$  and  $V_{\rm OL}$ represent input high and low voltage, respectively, while  $\partial V_{\text{out}}$  $\partial V_{\rm in} = -1$ . The  $N_{\rm MH}$  and  $N_{\rm ML}$  of this inverter are calculated to be 2.48 V and 1.55 V at  $V_{\rm DD}$  of 4 V, revealing the potential application in multistage digital circuits.<sup>56</sup> To investigate the alternative current (AC) characteristic of the inverter, the dynamic behavior at 1 Hz under AC square wave signal was measured, as shown in Fig. 11d. It can be noted that the as-constructed inverter exhibits good logic inversion action and responds well to the  $V_{in}$  square-wave signal, demonstrating its potential application in complex logic circuits, such as ring oscillators.

# Conclusions

In summary, fully solution-processed IZO TFTs based on HfAlOx dielectric have been fabricated successfully and annealing temperature dependent electrical properties of IZO/HfAlO<sub>x</sub> TFTs has been investigated systematically. Amorphous HfAlO<sub>x</sub> thin films annealed at 600 °C have shown a high transparency (>85%), low leakage current density (6.9  $\times$  10<sup>-9</sup> A cm<sup>-2</sup> at 2 MV cm<sup>-1</sup>), and smooth surface. To verify the possible application of the HfAlO<sub>x</sub> thin films as dielectrics in low-temperatureprocessed CMOS logics, fully solution-derived IZO/HfAlOx TFTs have been successfully integrated to display a ultralow operating voltage of 3 V with optimized performance, including a high  $\mu_{\rm sat}$  of 5.17 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup>, an large  $I_{\rm on}/I_{\rm off}$  of 7.5  $\times$  10<sup>6</sup>, a small SS of 87 mV dec<sup>-1</sup>, an threshold voltage shift of 0.52 V under positive bias stress for 7200 s, respectively. To explore its potential application in complex logic circuits, a unipolar resistor-loaded inverter coupled with IZO/HfAlOx TFT has been built and excellent swing characteristic and well dynamic behavior have been obtained. Our strategy opens a simple and reliable path toward fabricating low-cost, low-power consumption, and large-area environmentally friendly oxide flexible electronics.

# Conflicts of interest

The authors declare no competing financial interest.

# Acknowledgements

The authors acknowledge the support from National Natural Science Foundation of China (11774001, 51572002), Open fund for Discipline Construction, Institute of Physical Science and Information Technology, Anhui University (S01003101), Technology Foundation for Selected Overseas Chinese Scholar, Ministry of Personnel of China (J05015131), Anhui Provincial Natural Science Foundation (1608085MA06).

## References

- 1 J. F. Wager, Science, 2003, 300, 1245.

- 2 J. A. Rogers, Z. Bao, K. Baldwin, A. Dodabalapur, B. Crone, V. R. Raju, V. Kuck, H. Katz, K. Amundson, J. Ewing and P. Drzaic, Proc. Natl. Acad. Sci. U. S. A., 2001, 98, 4835.

- 3 K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano and H. Hosono, Nature, 2004, 432, 488.

- 4 G. X. Liu, A. Liu, F. K. Shan, Y. Meng, B. C. Shin, E. Fortunato and R. Martins, Appl. Phys. Lett., 2014, 105, 113509.

- 5 E. Fortunato, P. Barquinha and R. Martins, Adv. Mater., 2012, 24, 2945.

- 6 R. Martins, P. Barquinha, A. Pimentel, L. Pereira and E. Fortunato, Phys. Status Solidi A, 2005, 202, R95.

- 7 P. Barquinha, A. Pimentel, A. Marques, L. Pereira, R. Martins and E. Fortunato, J. Non-Cryst. Solids, 2006, 352, 1749.

- 8 H. W. Park, K. Park, J. Y. Kwon, D. Choi and K. B. Chung, IEEE Trans. Electron Devices, 2017, 64, 159.

- 9 C. G. Choi, S. Seo and B. Bae, Electrochem. Solid-State Lett., 2008, 11, H7.

- 10 B. Zhang, Y. Liu, S. Agarwal, M. Yeh and H. E. Katz, ACS Appl. Mater. Interfaces, 2011, 3, 4254.

- 11 K. H. Lee, M. S. Kang, S. Zhang, Y. Gu, T. P. Lodge and C. D. Frisbie, Adv. Mater., 2012, 24, 4457.

- 12 J. Kim, S. H. Lim and Y. S. Kim, J. Am. Chem. Soc., 2010, 132, 14721.

- 13 B. G. Son, S. Y. Je, H. J. Kim, C. K. Lee, A. Y. Hwang, J. Y. Won, J. H. Song, R. Choi and J. K. Jeong, Phys. Status Solidi RRL, 2013, 7, 485.

- 14 J. W. Zhang, G. He, L. Zhou, H. S. Chen, X. S. Chen, X. F. Chen, B. Deng, J. G. Lv and Z. Q. Sun, J. Alloys Compd., 2014, 611, 253.

- 15 C. Avis, Y. G. Kim and J. Jang, J. Mater. Chem., 2012, 22,

- 16 A. Liu, Z. D. Guo, G. X. Liu, C. D. Zhu, H. H. Zhu, B. C. Shin, E. Fortunato, R. Martins and F. K. Shan, Adv. Electron. Mater., 2017, 3, 1600513.

- 17 J. Ko, J. Kim, S. Y. Park, E. Lee, K. Kim, K. H. Lee and Y. S. Kim, J. Mater. Chem. C, 2014, 2, 1050.

- 18 S. Park, B. L. Clak, D. A. Keszler, J. P. Bender, J. F. Wager, T. A. Reynolds and G. S. Herman, Science, 2002, 297, 65.

- 19 G. He, B. Deng, Z. Q. Sun, X. S. Chen, Y. M. Liu and L. D. Zhang, Crit. Rev. Solid State Mater. Sci., 2013, 38, 235.

- 20 G. He, Z. Q. Sun, G. Li and L. D. Zhang, Crit. Rev. Solid State Mater. Sci., 2012, 37, 131.

- 21 J. Gao, G. He, Z. Q. Sun, H. S. Chen, C. Y. Zheng, P. Jin, D. Q. Xiao and M. Liu, J. Alloys Compd., 2016, 667, 352.

- 22 Y. Yamamoto, K. Kita, K. Kyuno and A. Toriumi, Appl. Phys. Lett., 2006, 89, 032903.

- 23 S. H. Bae, C. H. Lee, R. Clark and D. L. Kwong, IEEE Electron Device Lett., 2003, 24, 556.

- 24 M. S. Joo, B. J. Cho, C. C. Yeo, S. S. Chan, S. J. Whoang, S. Mathew, L. K. Bera and D. L. Kwong, IEEE Trans. Electron Devices, 2003, 50, 2088.

- 25 J. Gao, G. He, M. Liu, J. G. Lv, Z. Q. Sun, C. Y. Zheng, P. Jin, D. Q. Xiao and X. S. Chen, J. Alloys Compd., 2017, 691, 504.

Paper

- 26 G. He, W. D. Li, H. H. Wei, S. S. Jiang, D. Q. Xiao, P. Jing and J. Gao, J. Alloys Compd., 2017, 695, 1591.

- 27 G. He and L. D. Zhang, J. Mater. Sci. Technol., 2007, 23, 433.

- 28 A. Liu, Z. D. Guo, G. X. Liu, C. D. Zhu, H. H. Zhu, B. C. Shin, E. Fortunato, R. Martins and F. K. Shan, Adv. Electron. Mater., 2017, 3, 1600513.

- 29 C. X. Fan, A. Liu, Y. Meng, Z. D. Guo, G. X. Liu and F. K. Shan, IEEE Trans. Electron Devices, 2017, 64, 4137.

- 30 J. M. Yu, G. X. Liu, A. Liu, Y. Meng, B. C. Shin, E. Fortunato and R. Martins, J. Mater. Chem. C, 2015, 3, 9509.

- 31 Y. Meng, G. X. Liu, A. Liu, H. J. Sun, Y. Hou, B. Shin and F. K. Shan, RSC Adv., 2015, 5, 37807.

- 32 K. Choi, M. Kim, S. Chang, T. Y. Oh, S. W. Jeong, H. J. Ha and B. K. Ju, Jpn. J. Appl. Phys., 2013, 52, 060204.

- 33 J. H. Park, Y. B. Yoo, K. H. Lee, W. S. Jang, J. Y. Oh, S. S. Chae, H. W. Lee, S. W. Han and H. K. Baik, ACS Appl. Mater. Interfaces, 2013, 5, 8067.

- 34 G. He, L. D. Zhang, G. W. Meng, G. H. Li, Q. Fang and J. P. Zhang, J. Appl. Phys., 2007, 102, 094103.

- 35 U. Myeonghun, H. I. Kwon, I. T. Cho, S. H. Jin and J. H. Lee, J. Korean Phys. Soc., 2014, 65, 286.

- 36 W. Xu, H. Wang, F. Xie, J. Chen, H. Cao and J. B. Xu, ACS Appl. Mater. Interfaces, 2015, 7, 5803.

- 37 A. Liu, G. X. Liu, H. H. Zhu, F. Xu, E. Fortunato, R. Martins and F. K. Shan, ACS Appl. Mater. Interfaces, 2014, 6, 17364.

- 38 Y. J. Tak, S. J. Kim, S. Kwon, H. J. Kim, K. B. Chung and H. J. Kim, J. Mater. Chem. C, 2018, 6, 249.

- 39 A. Liu, G. X. Liu, H. H. Zhu, B. C. Shin, E. Fortunato, R. Martins and F. K. Shan, RSC Adv., 2015, 5, 86606.

- 40 K. Umeda, T. Miyasako, A. Sugiyama, A. Tanaka, M. Suzuki, E. Tokumitsu and T. Shimoda, J. Appl. Phys., 2013, 113, 184509.

- 41 J. Y. Choi, S. S. Kim and S. Y. Lee, Appl. Phys. Lett., 2012, 100, 022109.

- 42 Y. B. Yoo, J. H. Park, K. H. Lee, H. W. Lee, K. M. Song, S. J. Lee and H. K. Baik, J. Mater. Chem. C, 2013, 1, 1651.

- 43 W. Xu, H. Wang, L. Ye and J. Xu, J. Mater. Chem. C, 2014, 2, 5389.

- 44 B. N. Pal, B. M. Dhar, K. C. See and H. E. Katz, Nat. Mater., 2009, 8, 898.

- 45 J. S. Lee, Y. J. Kwack and W. S. Choi, ACS Appl. Mater. Interfaces, 2013, 5, 11578.

- 46 S. H. Jeong, Y. G. Ha, J. H. Moon, T. J. Marks and A. Facchetti, Adv. Mater., 2010, 22, 1346.

- 47 G. X. Jiang, A. Liu, G. X. Liu, C. D. Zhu, Y. Meng, B. Shin, E. Fortunato, R. Martins and F. K. Shan, Appl. Phys. Lett., 2016, 109, 183508.

- 48 A. Liu, G. X. Liu, H. H. Zhu, H. J. Song, B. C. Shin, E. Fortunato, R. Martins and F. K. Shan, Adv. Funct. Mater., 2015, 25, 7180.

- 49 A. Javey, J. Guo, D. B. Farmer, Q. Wang, E. Yenilmez, R. G. Gordon, M. Lundstrom and H. J. Dai, Nano Lett., 2004, 4, 1319.

- 50 M. L. Geier, P. L. Prabhumirashi, J. J. McMorrow, W. Xu, J. W. Seo, K. Everaerts, T. J. Marks and M. C. Hersam, Nano Lett., 2013, 13, 4810.

- 51 J. H. Park, Y. B. Yoo, K. H. Lee, W. S. Jang, J. Y. Oh, S. S. Chae and H. K. Baik, ACS Appl. Mater. Interfaces, 2013, 5, 410.

- 52 I. T. Cho, J. M. Lee, J. H. Lee and H. I. Kwon, Semicond. Sci. Technol., 2009, 24, 015013.

- 53 L. Zhu, G. He, W. D. Li, B. Yang, E. Fortunato and R. Martins, Adv. Electron. Mater., 2018, 4, 1800100.

- 54 J. M. Lee, I. T. Cho, J. H. Lee and H. I. Kwon, Appl. Phys. Lett., 2008, 93, 093504.

- 55 S. K. Lee, S. M. H. Kabir, B. K. Sharma, B. J. Kim, J. H. Cho and J. Ahn, Nanotechnology, 2014, 25, 014002.

- 56 Y. Liu, X. Wan, L. Q. Zhu, Y. Shi and Q. Wan, IEEE Electron Device Lett., 2014, 35, 1257.