Cite this: RSC Adv., 2018, 8, 2837

## Polymer/oxide bilayer dielectric for hysteresis-minimized 1 V operating 2D TMD transistors†

Minho Yoon, ‡ Kyeong Rok Ko, ‡ Sung-Wook Min and Seongil Im\*

Despite their huge impact on future electronics, two-dimensional (2D) dichalcogenide semiconductor (TMD) based transistors suffer from the hysteretic characteristics induced by the defect traps located at the dielectric/TMD channel interface. Here, we introduce a hydroxyl-group free organic dielectric divinyl-tetramethyldisiloxane-bis (benzocyclobutene) (BCB) between the channel and conventional  $\text{SiO}_2$  dielectric, to practically resolve such issues. Our results demonstrate that the electrical hysteresis in the n-channel  $\text{MoS}_2$  and p-channel  $\text{MoTe}_2$  transistors were significantly reduced to less than  $\sim 20\%$  of initial value after being treated with hydrophobic BCB dielectric while their mobilities increased by factor of two. Such improvements are certainly attributed to the use of the hydroxyl-group free organic dielectric, since high density interface traps are related to hydroxyl-groups located on hydrophilic  $\text{SiO}_2$ . This concept of interface trap reduction is extended to stable low voltage operation in 2D  $\text{MoTe}_2$  FET with 30 nm BCB/10 nm  $\text{Al}_2\text{O}_3$  bilayer dielectric, which operates well at 1 V. We conclude that the interface engineering employing the BCB dielectric offers practical benefits for the high performance and stable operation of TMD-based transistors brightening the future of 2D TMD electronics.

Received 21st November 2017

Accepted 8th January 2018DOI: 10.1039/c7ra12641g

[rsc.li/rsc-advances](http://rsc.li/rsc-advances)

## Introduction

Two-dimensional (2D) dichalcogenide semiconductors (TMD) have been extensively studied during recent years due to their massive potential for next-generation electronics.<sup>1,2</sup> Compared to the gapless semiconductor graphene,<sup>3</sup> TMD such as molybdenum disulfide ( $\text{MoS}_2$ ),<sup>4</sup> molybdenum ditelluride ( $\text{MoTe}_2$ ),<sup>5</sup> and tungsten diselenide ( $\text{WSe}_2$ )<sup>6</sup> provide the tunable electronic bandgap which is dependent on the thickness of the layer itself. Due to their discrete bandgap, the TMD-based field effect transistors (FETs) often exhibit clear switching operation with its relatively high values of mobility and ON/OFF current ratio.<sup>7–10</sup> However, several reports reveal that the electrical performances of the devices are significantly degraded by the interface and surface states of the devices.<sup>11,12</sup> For a good candidate to minimize the interfacial defect states in FET, the hydrophobic hexagonal boron nitride (h-BN) as dielectric and passivation layer has been proposed.<sup>13,14</sup> Although this approach has been encouraging, h-BN is basically expensive due to its special growth processes for good crystalline quality control,<sup>15,16</sup> and furthermore, additional elaborate processes are still requested for h-BN flake to be incorporated in device fabrications. Hence, alternatives to replace h-BN have been suggested: self-assembled monolayers,<sup>17</sup> organic

insulating materials,<sup>18</sup> high-k oxide dielectrics,<sup>19</sup> and *etc.* Among these candidates, an organic insulating polymer, divinyl-tetramethyldisiloxane-bis(benzocyclobutene) (BCB) could be an appropriate option for TMD-channel FETs. BCB is a well-known non-polar organic polymer with hydroxyl-group free chemical structure and it has been widely used as a dielectric for stable high-performance organic transistors.<sup>20–22</sup> To the best of our limited knowledge, BCB has never been attempted for the TMD-based field effect transistors while it is easily formed by spin-casting.

In the present study, we report n-channel  $\text{MoS}_2$  and p-channel  $\text{MoTe}_2$  transistors with the BCB gate dielectric on oxide gate dielectric. According to our results, initial hysteresis in the  $\text{MoS}_2$  and  $\text{MoTe}_2$  transistors on 285 nm-thick  $\text{SiO}_2/\text{p}^+/\text{Si}$  back gate without BCB were  $\sim 15$  V in their transfer curve characteristics, but it reduced to  $\sim 4$  V in the devices with BCB. Based on these hysteresis minimization effects by BCB, we successfully extended our results to a more practical device application, 1 V operation of  $\text{MoTe}_2$  FET with 30 nm-thin BCB on 10 nm-thin atomic layer deposited (ALD)  $\text{Al}_2\text{O}_3$ . It is thus regarded that BCB dielectric layer offers benefits for the high performance and stable operation of TMD-based transistors. The main advantage of the BCB would be its non-polar hydrophobicity and process conveniences.

## Experimental detail

For basic investigations on 2D TMD device stability, 300 nm-thick organic insulating material, divinyl-tetramethyldisiloxane-bis

Institute of Physics and Applied Physics, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 120-749, Korea. E-mail: [semicon@yonsei.ac.kr](mailto:semicon@yonsei.ac.kr); Fax: +82-2-392-1592; Tel: +82-2-2123-2842

† Electronic supplementary information (ESI) available. See DOI: [10.1039/c7ra12641g](https://doi.org/10.1039/c7ra12641g)

‡ M. Y. and K. K. contributed equally to this work.

(benzocyclobutene) (BCB, CYCLOTENE, Dow Chemical) was formed on the 285 nm-thick  $\text{SiO}_2/\text{p}^+/\text{Si}$  substrate by spin-casting and subsequent thermal annealing at 300 °C for 10 minutes in nitrogen ambient. (But for extended practical device fabrication, 30 nm-thin BCB on 10 nm-thin atomic layer deposited  $\text{Al}_2\text{O}_3$  was formed on patterned Au gate). Then,  $\text{MoS}_2$  and  $\text{MoTe}_2$  flakes for n and p-type transistors were micromechanically exfoliated with polydimethylsiloxane (PDMS) stamps, respectively. Those TMD flakes are subsequently dry-transferred onto the two types of dielectric substrates: BCB/ $\text{SiO}_2$  and  $\text{SiO}_2$ . Then, 50 nm-thick Au for  $\text{MoS}_2$  and 100 nm-thick Pt for  $\text{MoTe}_2$  were sputter-deposited on the substrates for source/drain electrodes and patterned by conventional lift-off processes. The thickness of the flakes were confirmed with the atomic force microscopy (AFM) and also identified with Raman spectroscopy.

The current–voltage ( $I$ – $V$ ) measurements of the transistors were performed with a semiconductor parameter analyser (Model HP4155C, Agilent Technologies) and the capacitance–voltage ( $C$ – $V$ ) measurements of the devices were conducted with a LCR meter (Model HP4284A, Agilent Technologies). Electrical characterisations of the devices were carried out entirely in air ambient (relative humidity RH ~ 45%) at room temperature, but for one  $\text{MoTe}_2$  device sample was also measured in vacuum (less than 1 Torr) at 300 K, to investigate the hysteresis–induction effects of air molecules adsorbed on TMD channel surface.

## Results and discussion

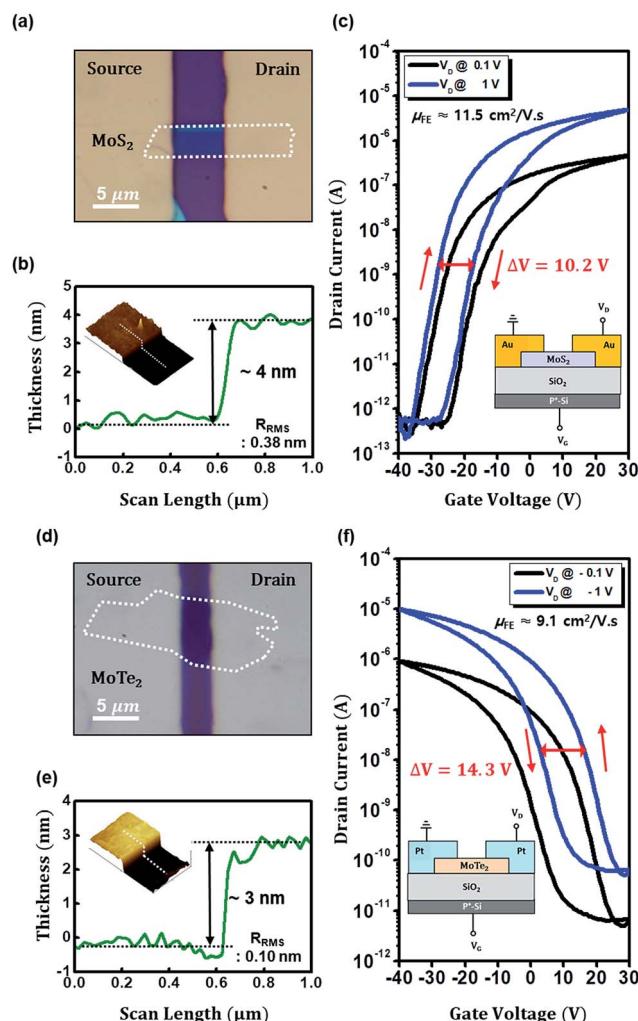

Fig. 1a and d show bottom-gate top-contact  $\text{MoS}_2$  and  $\text{MoTe}_2$  transistors on 285 nm thick  $\text{SiO}_2$  dielectric, respectively. Their thickness appears to be 4 nm for  $\text{MoS}_2$  and 3 nm for  $\text{MoTe}_2$  as measured by atomic force microscopy (AFM) scan in Fig. 1b and e. Identity of the two flakes was again confirmed by Raman spectroscopy whose results are seen in ESI section (Fig. S1†). Fig. 1c and f show the transfer characteristics ( $I_{\text{DS}}$  vs.  $V_{\text{GS}}$ ) of our bottom-gate top-contact  $\text{MoS}_2$  and  $\text{MoTe}_2$  transistors, respectively. Their insets are schematic cross sections of those devices. The  $\text{MoS}_2$  transistor with Au source/drain electrodes displays n-type conduction behaviour with the electron mobility of  $11.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and high on/off current ratio ( $>10^5$ ). The  $\text{MoTe}_2$  transistor with Pt source/drain electrodes presents p-type conduction with the hole mobility of  $9.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and high on/off current ratio ( $>10^5$ ) as well. Although the electrical performances of the devices are promising as reported previously by others,<sup>23,24</sup> it is very apparent that the devices much suffer from the gate bias-induced hysteresis ( $\Delta V = \sim 10.2 \text{ V}$  for n- $\text{MoS}_2$  and  $\sim 14.3 \text{ V}$  for p- $\text{MoTe}_2$  FET) in the present transfer characteristics, which should be minimized for practical device applications in electronics.

Numerous reasons count for the hysteresis in TMD-based 2D transistors as discussed enormously in the organic and inorganic transistors for decades,<sup>25–27</sup> and the reasons were classified into four main categories: the adsorption of water and oxygen molecules on semiconductor channel surface, defects in the semiconductor material, mobile trap charges in the dielectric, and the interface trap charges between the

Fig. 1 (a–c) Optical microscopy (OM) image, AFM image along with channel thickness profiles ( $\sim 4 \text{ nm}$ ), and transfer characteristics ( $I_{\text{DS}}$  vs.  $V_{\text{GS}}$ ) of n-type  $\text{MoS}_2$  FET on 285 nm-thick  $\text{SiO}_2$  dielectric with cross section scheme (inset). The channel width and length of the  $\text{MoS}_2$  FET are 4.1 and 5.4  $\mu\text{m}$ , respectively, and the device shows the electron mobility of  $11.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . The value of the clockwise hysteresis is around 10.2 V. (d–f) OM image, AFM image along with thickness profiles ( $\sim 3 \text{ nm}$ ), and the transfer characteristics of p-type  $\text{MoTe}_2$  FET on 285 nm-thick  $\text{SiO}_2$  dielectric with cross section scheme (inset). The channel width and length of the  $\text{MoTe}_2$  FET are 8.1 and 3.4  $\mu\text{m}$ , respectively, and the device shows the hole mobility of  $9.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . The value of the anticlockwise hysteresis is around 14.3 V.

semiconductor and the contacting dielectric. Here, we mainly focused on the interface effects because the single-crystalline-like 2D semiconducting channel would meet hydrophilic oxide dielectric in general and their interface becomes to contain high density charge traps which originate from the surface hydroxyl-group of the oxides dielectric.<sup>12,28</sup>

To this end, a hydrophobic organic insulator, BCB was conceived as an excellent option for the dielectric for the transistors because the BCB film has a hydroxyl-group free chemical structure and can be deposited by simple spin-casting.

Prior to exploiting the BCB as a dielectric layer for  $\text{MoS}_2$  and  $\text{MoTe}_2$  transistors, the dielectric properties and hydrophobicity

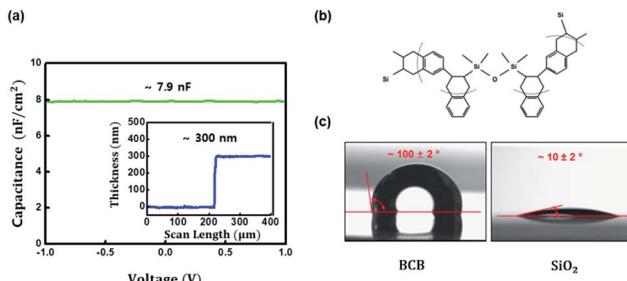

Fig. 2 (a) The geometrical capacitance of the BCB dielectric in Au/BCB/Au structure with the thickness of BCB dielectric (inset). (b) Chemical structure of the BCB. (c) The contact angle of D.I. water on the BCB and SiO<sub>2</sub>, respectively. The contact angle of D.I. water on the hydrophobic BCB dielectric was ~100° while that on a cleaned SiO<sub>2</sub> hydrophilic substrate was ~10°.

of the BCB layer were initially investigated. The capacitance of our BCB dielectric was measured to be ~7.9 nF cm<sup>-2</sup> at 1 kHz with top and bottom Au electrodes (Au/BCB/Au) in the Fig. 2a, where the thickness of the spin-casted BCB layer was ~300 nm (inset of the Fig. 2a) as scanned with a surface profiler. Deduced dielectric constant of the BCB dielectric at the thickness was ~2.67, which is in a good agreement with the previously reported value.<sup>29</sup> Furthermore, as shown in the Fig. 2c, the contact angle of D.I. water on the BCB dielectric was ~100° while that on a cleaned SiO<sub>2</sub> substrate was as low as ~10°; such contact angle measurements clearly indicate the hydrophobicity of the BCB layer surface due to its chemical structure (Fig. 2b).<sup>30</sup>

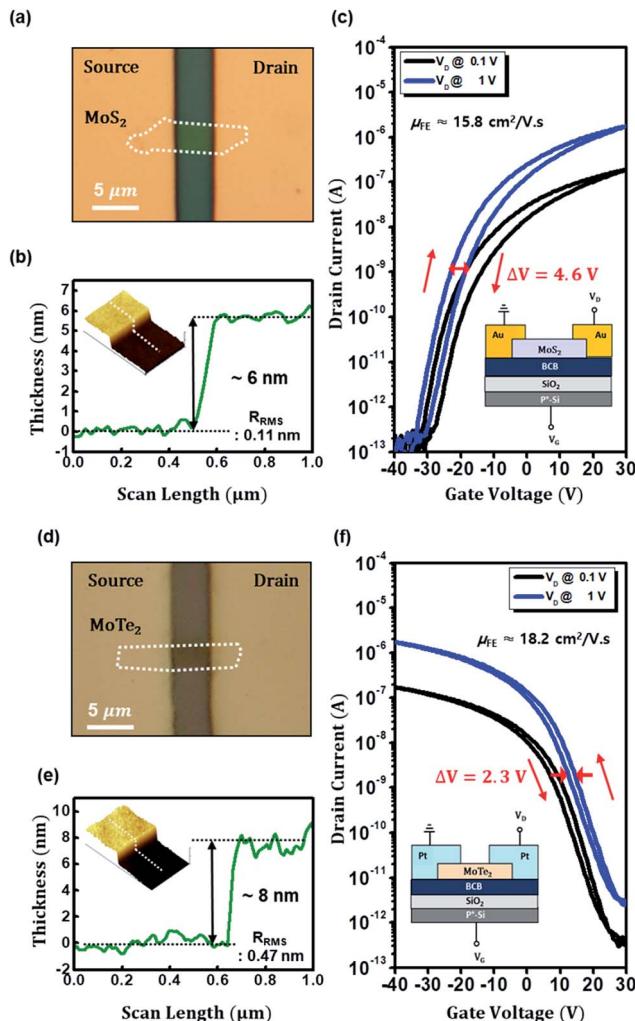

Fig. 3a and d show bottom-gate top contact MoS<sub>2</sub> and MoTe<sub>2</sub> transistors with BCB (300 nm)/SiO<sub>2</sub> dielectric, respectively. Their thickness appears to be 6 nm for MoS<sub>2</sub> and 8 nm for MoTe<sub>2</sub> as measured by atomic force microscopy (AFM) scan in Fig. 3b and e. Fig. 3c and f show the transfer characteristics ( $I_{DS}$ – $V_{GS}$ ) of the bottom-gate top contact MoS<sub>2</sub> and MoTe<sub>2</sub> transistors on the BCB/SiO<sub>2</sub> dielectric, respectively. Their insets are schematic cross sections of those devices. With BCB dielectric, the values of the hysteresis in the MoS<sub>2</sub> and MoTe<sub>2</sub> transistors were dramatically reduced to ~4.5 V and ~2.3 V. (Similar hysteresis reduction is also shown in the output characteristics of Fig. S2†). Furthermore, the field-effect mobility of the devices was significantly increased by the factor of two in both cases (from 11.5 to 15.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in MoS<sub>2</sub> transistors and from 9.1 to 18.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in MoTe<sub>2</sub> transistors). We thus regard that the BCB dielectric effectively minimizes the trap sites or passivates the electro-active hydroxyl groups at the dielectric/TMD channel interface improving the electrical performance and the stability of the devices. On the one hand, the linear mobility of our FETs was estimated with the following equation.<sup>31</sup>

$$\mu_{LIN} = \frac{1}{C_i V_{DS}} \frac{L}{W} \frac{\partial I_D}{\partial V_{GS}} \quad (1)$$

where  $C_i$  is the geometric dielectric capacitance,  $L$  is channel length and  $W$  is its width.

Based on aforementioned transfer characteristics from TMD-devices with and without BCB dielectric, we considered

Fig. 3 (a–c) Optical microscopy image, AFM image along with channel thickness profile (~6 nm), and the transfer characteristics ( $I_{DS}$  vs.  $V_{GS}$ ) of n-MoS<sub>2</sub> FET with 300 nm-thick BCB/SiO<sub>2</sub> dielectric with cross section scheme (inset). The channel width and length of the MoS<sub>2</sub> FET are 2.5 and 2.9 μm, respectively, and the device shows the electron mobility of 15.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The value of the clockwise hysteresis is around 4.6 V. (d–f) OM image, AFM image along with channel thickness profile (~8 nm), and the transfer characteristics of p-MoTe<sub>2</sub> FET with BCB/SiO<sub>2</sub> dielectric with cross section scheme (inset). The channel width and length of the MoTe<sub>2</sub> FET are 2.8 and 3.9 μm, respectively, and the device shows the hole mobility of cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The value of the anticlockwise hysteresis is around 2.3 V.

quantifying the effective interface trap density,  $D_{it}$  by deducing the values from the subthreshold swing (SS) of the transistors, which is expressed in the following equation.<sup>31</sup>

$$SS = \left( \frac{d(\log_{10} I_{DS})}{dV_{GS}} \right)^{-1} \approx \ln 10 \frac{kT}{q} \left( 1 + \frac{q^2 D_{it}}{C_i} \right) \quad (2)$$

where  $k$  is the Boltzmann constant,  $T$  is the temperature in Kelvin,  $q$  is the electronic charge, and  $C_i$  is the geometric capacitance of the dielectric.

We thought this type of approach is at least worthy even though this SS equation ignores any effects caused by contact resistance which is sometimes not ignorable at all.<sup>32</sup> The

subthreshold swing (SS) values of the  $\text{MoS}_2$  transistors with BCB/SiO<sub>2</sub> and SiO<sub>2</sub> dielectrics seem similar each other as about 2.2 V dec<sup>-1</sup> and 2.0 V dec<sup>-1</sup>, respectively, but their geometric capacitances are quite different, to be 4.8 nF cm<sup>-2</sup> and 12.1 nF cm<sup>-2</sup>. Thus, the estimated values of  $D_{it}$  become  $1.1 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$  and  $2.4 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$  for the n- $\text{MoS}_2$  transistors with and without BCB. Similarly, the SS values of p-MoTe<sub>2</sub> transistors with and without BCB dielectric were 3.6 V dec<sup>-1</sup> and 3.4 V dec<sup>-1</sup>, resulting in  $D_{it}$  values of  $1.9 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$  and  $4.4 \times 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$ , respectively. Likewise, devices with BCB dielectric appear to contain 2–3 times lower number density of traps at the interface in SS-based estimation. However, such SS-based approach and  $D_{it}$  results must be still unclear because SS behaviour cannot ignore contact resistance effects from TMD/source-drain electrode contact.<sup>33</sup> In addition, since the gate hysteresis of  $I_{DS}$ – $V_{GS}$  transfer characteristics ( $I$ – $V$  measurement system) unavoidably contains source/drain contact resistance effects in general.<sup>34</sup> Hence, it might be necessary to find other measurement scheme which is immune from contact effects.

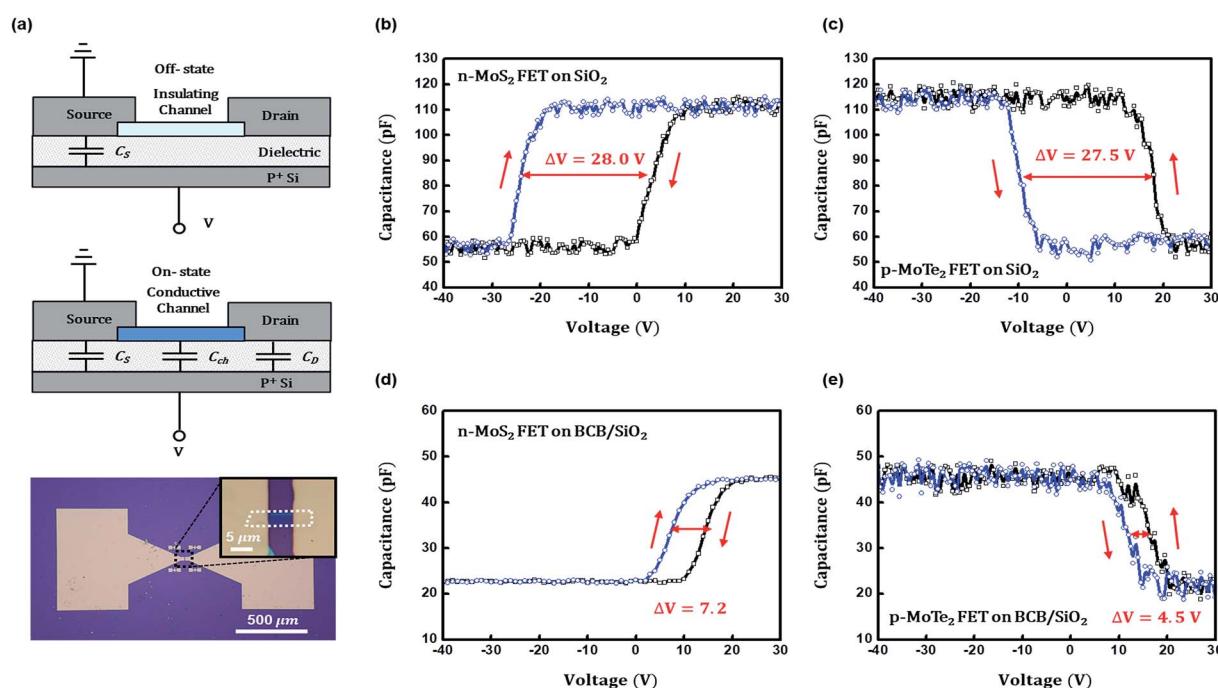

We thus conceived to perform capacitance–voltage ( $C$ – $V$ ) measurements for evaluating the trapped interface charges, because  $C$ – $V$  measurements are oriented to focus on the interface by gate bias without any interference from the contact resistance effects.<sup>35</sup> For the  $C$ – $V$  measurements on FET structure at high and low frequencies, DC and small signal AC voltages are applied to the gate electrode while source/drain (S/D) electrodes are grounded in general.<sup>36</sup> However, general  $C$ – $V$  method

on FET structure would not be effective if the channel area is too small compared to the S/D-to-gate overlap area; real capacitance signals from channel should be overridden by parasitic capacitance. Our device with small 2D channel would definitely meet such parasitic capacitance issue, so we modified the general  $C$ – $V$  measurements by grounding the source electrode only, considering that DC voltage sweep would eventually induce the capacitance of channel and drain electrode area by channel accumulation or channel conducting.<sup>15</sup> Since the trapped charges cannot respond at high frequency, the interface trap density can be extracted at a low frequency of 100 Hz, using the sample transistor architecture as shown in Fig. 4a. According to the schematic circuits of Fig. 4a, we meet with two cases during DC sweep: channel depletion and accumulation which are dependent on the DC bias. In the case of channel depletion, a capacitance ( $C_S$ ) is measured from the dielectric area under only one electrode (source), however such capacitance should be doubled-up by channel accumulation, which would connect the source and drain (the other electrode; now total capacitance becomes  $C_S + C_D = 2C_S$ ). According to the  $C$ – $V$  plots of Fig. 4b–e, the capacitance value is indeed doubled-up from 55 to 112 pF (for FETs without BCB but SiO<sub>2</sub>) or from 22 to 45 pF (for FETs with BCB). In our device (photo images of Fig. 1a and 4a), the channel area for channel capacitance ( $C_{ch}$ ) is too small (incomparable to electrode area) to be visibly counted for total capacitance. In spite of that, the TMD channels successfully performed as connecting/disconnecting (on/off) switches.

Fig. 4 (a) Schematic circuit and illustration of the modified  $C$ – $V$  measurements on our TMD FETs. In channel depletion, a capacitance ( $C_S$ ) is measured from the dielectric area under only one electrode (source), however such capacitance is doubled-up by channel accumulation (note the plots in (b–e)), which would connect the source and drain [the other electrode for  $C_D$  ( $=C_S$ )]. The channel area ( $\sim$ less than  $25 \mu\text{m}^2$  as seen in the inset OM) for  $C_{ch}$  is incomparably smaller than that of one electrode which is around  $4.55 \times 10^5 \mu\text{m}^2$ . According to the  $C$ – $V$  characteristics obtained from (b) MoS<sub>2</sub> on SiO<sub>2</sub>, (c) MoTe<sub>2</sub> on SiO<sub>2</sub>, (d) MoS<sub>2</sub> on BCB/SiO<sub>2</sub>, and (e) MoTe<sub>2</sub> on BCB/SiO<sub>2</sub>, the initial voltage hysteresis is dramatically reduced from  $\sim$ 28 V to 4.5–7.2 V due to the BCB effects.

Table 1 Summary of the mobility, subthreshold swing, hysteresis, and estimated trap densities of the devices

| Semicon.          | Dielec.              | Capacit. | Mobility | S.S (V dec <sup>-1</sup> ) | Hysteresis ( $\Delta V$ ) from |              | Trap density ( $\times 10^{12}$ cm <sup>-2</sup> ) from |              |

|-------------------|----------------------|----------|----------|----------------------------|--------------------------------|--------------|---------------------------------------------------------|--------------|

|                   |                      |          |          |                            | Transfer curves                | Modified C-V | S.S                                                     | Modified C-V |

| MoS <sub>2</sub>  | SiO <sub>2</sub>     | 12.1     | 11.5     | 2.0 ± 0.1                  | 10.2 ± 0.1                     | 28.0 ± 0.1   | 2.9 ± 0.1                                               | 2.12 ± 0.01  |

| MoS <sub>2</sub>  | BCB/SiO <sub>2</sub> | 4.8      | 15.8     | 2.2 ± 0.1                  | 4.6 ± 0.1                      | 7.2 ± 0.1    | 1.30 ± 0.03                                             | 0.22         |

| MoTe <sub>2</sub> | SiO <sub>2</sub>     | 12.1     | 9.1      | 3.4 ± 0.1                  | 14.3 ± 0.1                     | 27.5 ± 0.1   | 4.4 ± 0.1                                               | 2.08 ± 0.01  |

| MoTe <sub>2</sub> | BCB/SiO <sub>2</sub> | 4.8      | 18.2     | 3.6 ± 0.1                  | 2.3 ± 0.1                      | 4.5 ± 0.1    | 1.86 ± 0.03                                             | 0.14         |

Noticeable in Fig. 4b and c is that those TMD channels clearly show hysteresis from forward-to-backward sweep. Because trapping and de-trapping of charges at the interface are certainly related to the forward and backward sweep, respectively, it is anticipated that the interfacial trap density would be quite precisely estimated using the hysteresis voltage. For both n-MoS<sub>2</sub> and p-MoTe<sub>2</sub> FETs with only SiO<sub>2</sub> dielectrics, almost the same amount of large voltage hysteresis was obtained to be 27.5–28 V in Fig. 4b and c, respectively. The hysteresis was significantly reduced to be 7.2 and 4.5 V of for n- and p-FETs as seen in Fig. 4d and e. This result is readily expected from the related transfer curves in Fig. 3c and f. Small amount of hysteresis still remains as 4.5–7.2 V due to the small trap density at the BCB dielectric/TMD channel interface. But such number is only about 15–25% of previous trap density on SiO<sub>2</sub>. Based on our C-V results, it is very likely that the hysteresis observed from  $I_{DS}$ - $V_{GS}$  transfer characteristics is mainly from gate dielectric/channel interface, not from the TMD surface effects involved with air molecules. For further confirmation on the dielectric/channel interface-induced hysteresis, we subsidiary performed  $I_{DS}$ - $V_{GS}$  transfer characteristics of another MoTe<sub>2</sub> device with

BCB dielectric in vacuum ambient at 300 K. As shown in Fig. S3 of ESI,† already-reduced hysteresis by BCB application seems not decreased any further even in vacuum, which supports our assumption that such hysteresis is mainly related to the amount of interfacial traps.

With the results from C-V characteristics in Fig. 4a–e, we could easily estimate the interfacial trap densities of MoS<sub>2</sub> and MoTe<sub>2</sub>-based FETs with and without BCB, using the following simple equation,  $Q_{it} = C_i \Delta V / q$ , where  $\Delta V$  is the voltage hysteresis and  $C_i$  is the geometric capacitance (Farad cm<sup>-2</sup>) of the dielectric.  $C_i$  value can be obtained from the C-V curves in Fig. 4b and d because we already know the electrode area. From the equation, the estimated values of the interface trap charge density were  $2.08 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> and  $2.11 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> in the MoS<sub>2</sub> and MoTe<sub>2</sub> transistors on SiO<sub>2</sub> dielectric. But those values were an order of magnitude reduced to the values of  $2.2 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> and  $1.4 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> when BCB was inserted as a dielectric layer. Table 1 summarizes all the values on interface trap densities and device performances. Here, we assumed that the trap charges only stem from the dielectric/channel interface, and the trap density values by SS and  $D_{it}$

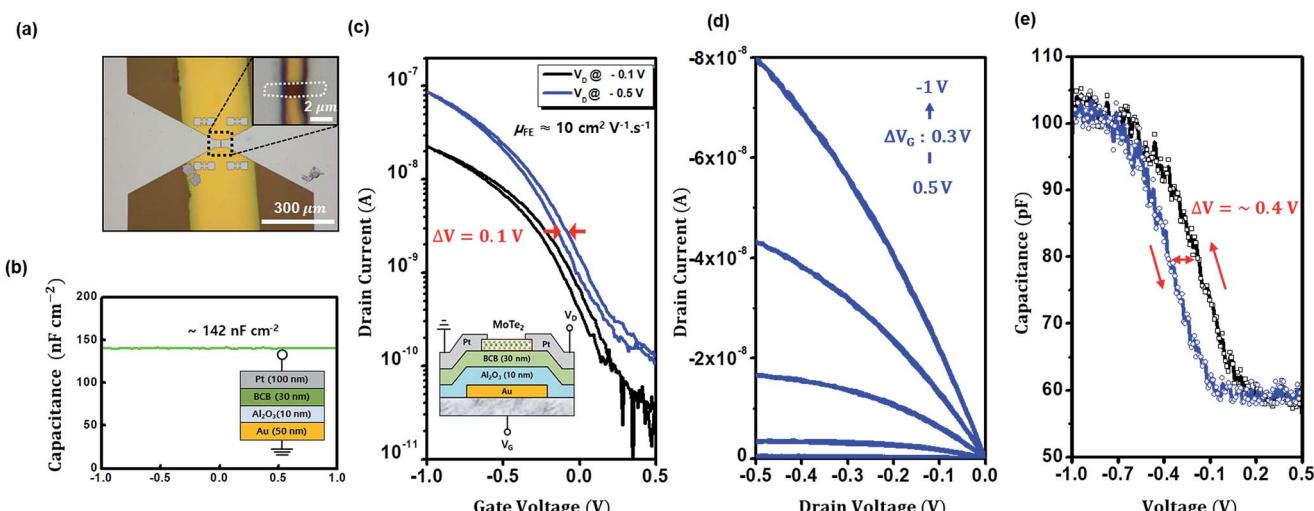

Fig. 5 (a) Optical image of our MoTe<sub>2</sub> FET with BCB/Al<sub>2</sub>O<sub>3</sub> dielectric and Au bottom gate, along with inset magnified image of 5 nm-thin MoTe<sub>2</sub> channel ( $W/L$  ratio  $\sim 1 \mu\text{m}/2 \mu\text{m} = 0.5$ ). (b) The geometrical capacitance of the thin BCB/Al<sub>2</sub>O<sub>3</sub> dielectric. (Inset: schematic illustration of device cross section) (c) transfer characteristics of MoTe<sub>2</sub> FET. ON/OFF  $I_D$  current ratio appears to be  $\sim 1000$ . (Inset: schematic illustration of device cross section. Au gate was patterned on thick SiO<sub>2</sub>/p<sup>+</sup>-Si wafer substrate). (d) Output characteristics show a very low operational voltage of 0.5–1 V. (f) C-V curve hysteresis voltage was measured, to be  $\sim 0.4$  V which leads to an estimated interface trap density of  $\sim 3.5 \times 10^{11}$  cm<sup>-2</sup>.

measurement were worked out as overall average trap density ( $D_{it} \times$  energy gap).<sup>24</sup> According to Table 1, SS-driven method always results in higher values of trap density than the values by *C-V* method whether the device has BCB dielectric or not, because any *I-V* method implicitly reflects the contact resistance effects.<sup>34</sup> The difference between SS-driven and *C-V* methods is very clear in the FETs with BCB dielectric, but such difference becomes relatively quite small in the other devices with high density traps (with only  $\text{SiO}_2$  dielectric).

Although we have mainly focused on minimizing the interfacial trap density in the present study, we also extended our results to a more practical device application as our final effort: low voltage operational  $\text{MoTe}_2$  FET with 30 nm-thin BCB on 10 nm-thin atomic layer deposited (ALD)  $\text{Al}_2\text{O}_3$ , Fig. 5a and its inset show optical images of our  $\text{MoTe}_2$  FET with BCB/ $\text{Al}_2\text{O}_3$  dielectric and Au bottom gate, where width-to-length ratio of the device was 1  $\mu\text{m}/2 \mu\text{m}$ . Capacitance of BCB/ $\text{Al}_2\text{O}_3$  was  $\sim 142 \text{ nF cm}^{-2}$  as obtained from metal-insulator-metal (MIM) *C-V* measurement (Fig. 5b). We also confirmed the BCB thickness of 30 nm with a mechanical profiler in Fig. S4a† and the  $\text{MoTe}_2$  thickness of 5 nm by AFM scan (Fig. S4b†). From the transfer characteristics, device mobility (linear regime) turned out to be  $\sim 10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , and ON/OFF  $I_D$  current ratio appears to be  $\sim 1000$  (Fig. 5c). Transfer and output characteristics (Fig. 5c and d) show a very low operational voltage of 0.5–1 V. The *C-V* curve hysteresis was measured in Fig. 5e, to be  $\sim 0.4$  V which leads to an estimated interface trap density of  $\sim 3.5 \times 10^{11} \text{ cm}^{-2}$ . Since the trap density is comparable to those from thick BCB/ $\text{SiO}_2$  in Table 1, it is well regarded that 30 nm-thin BCB polymer on 10 nm  $\text{Al}_2\text{O}_3$  keeps the function of trap minimization ensuring the practical low voltage operation as well. Such hysteresis-reduced low voltage operation in 2D TMD FET has rarely been demonstrated.<sup>17,37</sup>

## Conclusions

We have fabricated a few layer n- $\text{MoS}_2$  and p- $\text{MoTe}_2$  channel FETs with and without BCB dielectric on  $\text{SiO}_2/\text{p}^+\text{Si}$ . Our results from *C-V* measurements and *I-V* transfer characteristics display that the hysteresis in the  $\text{MoS}_2$  and  $\text{MoTe}_2$  transistors were significantly reduced to less than  $\sim 20\%$  of initial value after treated with hydrophobic BCB dielectric, while the linear mobilities of both p- and n-FETs increased by factor of two. Such improvements are certainly attributed to the hydroxyl-group free organic dielectric, BCB on  $\text{SiO}_2$ , since high density interface traps are related to hydroxyl-groups located on  $\text{SiO}_2$ . In particular, our modified *C-V* measurements turned out to be a more useful tool than *I-V* characteristics for the quantification of interface trap density. Our concept of interface trap reduction was successfully applied to stable low voltage operation in 2D  $\text{MoTe}_2$  FET with 30 nm BCB/10 nm  $\text{Al}_2\text{O}_3$  bilayer dielectric. We thus conclude that the interface engineering employing the BCB dielectric offers practical benefits for the high performance and stable operation of TMD-based transistors and brightens the future of 2D TMD electronics.

## Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

The authors acknowledge the financial support from NRF (NRL program: Grant No. 2017R1A2A1A05001278, SRC program: Grant No. 2017R1A5A1014862, vdWMRC center), Creative Materials Discovery Program through NRF funded by the Ministry of Science, ICT and Future Planning (Grant No. 2015M3D1A1068061). This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2017R1A6A3A11034195).

## Notes and references

- 1 D. Jariwala, V. K. Sangwan, L. J. Lauhon, T. J. Marks and M. C. Hersam, *ACS Nano*, 2014, **8**, 1102–1120.

- 2 Q. H. Wang, K. Kalantar-zadeh, A. Kis, J. N. Coleman and M. S. Strano, *Nat. Nanotechnol.*, 2012, **7**, 699–712.

- 3 K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, M. I. Katsnelson, I. V. Grigorieva, S. V. Dubonos and A. A. Firsov, *Nature*, 2005, **438**, 197–200.

- 4 K. F. Mak, C. Lee, J. Hone, J. Shan and T. F. Heinz, *Phys. Rev. Lett.*, 2010, **105**, 2–5.

- 5 I. G. Lezama, A. Arora, A. Ubaldini, C. Barreteau, E. Giannini, M. Potemski and A. F. Morpurgo, *Nano Lett.*, 2015, **15**, 2336–2342.

- 6 S. B. Desai, G. Seol, J. S. Kang, H. Fang, C. Battaglia, R. Kapadia, J. W. Ager, J. Guo and A. Javey, *Nano Lett.*, 2014, **14**, 4592–4597.

- 7 H.-J. Chuang, X. Tan, N. J. Ghimire, M. M. Perera, B. Chamlagain, M. M.-C. Cheng, J. Yan, D. Mandrus, D. Tománek and Z. Zhou, *Nano Lett.*, 2014, **14**, 3594–3601.

- 8 K. Kang, S. Xie, L. Huang, Y. Han, P. Y. Huang, K. F. Mak, C.-J. Kim, D. Muller and J. Park, *Nature*, 2015, **520**, 656–660.

- 9 S. H. H. Shokouh, P. J. Jeon, A. Pezeshki, K. Choi, H. S. Lee, J. S. Kim, E. Y. Park and S. Im, *Adv. Funct. Mater.*, 2015, **25**, 7208–7214.

- 10 S. Kim, A. Konar, W.-S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J.-B. Yoo, J.-Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi and K. Kim, *Nat. Commun.*, 2012, **3**, 1011.

- 11 J. P. Shu, G. T. Wu, Y. Guo, B. Liu, X. L. Wei and Q. Chen, *Nanoscale*, 2016, **8**, 3049–3056.

- 12 M. Y. Chan, K. Komatsu, S.-L. Li, Y. Xu, P. Darmawan, H. Kuramochi, S. Nakaharai, A. Aparecido-Ferreira, K. Watanabe, T. Taniguchi and K. Tsukagoshi, *Nanoscale*, 2013, **5**, 9572–9576.

- 13 G.-H. Lee, X. Cui, Y. D. Kim, G. Arefe, X. Zhang, C. Lee, F. Ye, K. Watanabe, T. Taniguchi, P. Kim and J. Hone, *ACS Nano*, 2015, **9**, 7019–7026.

- 14 X. Cui, G.-H. Lee, Y. D. Kim, G. Arefe, P. Y. Huang, C.-H. Lee, D. A. Chenet, X. Zhang, L. Wang, F. Ye, F. Pizzocchero, B. S. Jessen, K. Watanabe, T. Taniguchi, D. A. Muller,

T. Low, P. Kim and J. Hone, *Nat. Nanotechnol.*, 2015, **10**, 534–540.

15 S. M. Kim, A. Hsu, M. H. Park, S. H. Chae, S. J. Yun, J. S. Lee, D.-H. Cho, W. Fang, C. Lee, T. Palacios, M. Dresselhaus, K. K. Kim, Y. H. Lee and J. Kong, *Nat. Commun.*, 2015, **6**, 8662.

16 K. H. Lee, H. Shin, J. Lee, I. Lee, G. Kim, J. Choi and S. Kim, *Nano Lett.*, 2012, **12**, 714–718.

17 T. Kawanago and S. Oda, *Appl. Phys. Lett.*, 2016, **041605**, 108.

18 W. Bao, X. Cai, D. Kim, K. Sridhara and M. S. Fuhrer, *Appl. Phys. Lett.*, 2013, **042104**, 102.

19 H. Y. Chang, S. Yang, J. Lee, L. Tao, W. S. Hwang, D. Jena, N. Lu and D. Akinwande, *ACS Nano*, 2013, **7**, 5446–5452.

20 L. Chua, J. Zaumseil, J. Chang, E. C.-W. Ou, P. K.-H. Ho, H. Sirringhaus and R. H. Friend, *Nature*, 2005, **434**, 194–199.

21 T. D. Anthopoulos, B. Singh, N. Marjanovic, N. S. Sariciftci, A. Montaigne Ramil, H. Sitter, M. Cölle and D. M. De Leeuw, *Appl. Phys. Lett.*, 2006, **89**, 119–121.

22 S. R. Saudari, P. R. Frail and C. R. Kagan, *Appl. Phys. Lett.*, 2009, **023301**, 95.

23 H. S. Lee, S.-W. Min, Y.-G. Chang, M. K. Park, T. Nam, H. Kim, J. H. Kim, S. Ryu and S. Im, *Nano Lett.*, 2012, **12**, 3695–3700.

24 K. Choi, Y. T. Lee, J. S. Kim, S. W. Min, Y. Cho, A. Pezeshki, D. K. Hwang and S. Im, *Adv. Funct. Mater.*, 2016, **26**, 3146–3153.

25 J. Veres, S. Ogier and G. Lloyd, *Chem. Mater.*, 2004, **16**, 4543–4555.

26 H. Sirringhaus, *Adv. Mater.*, 2009, **21**, 3859–3873.

27 J. K. Jeong, *Semicond. Sci. Technol.*, 2011, **26**, 34008.

28 Y. Guo, X. Wei, J. Shu, B. Liu, J. Yin, C. Guan, Y. Han, S. Gao and Q. Chen, *Appl. Phys. Lett.*, 2015, **103109**, 106.

29 L. L. Chua, P. K. H. Ho, H. Sirringhaus and R. H. Friend, *Appl. Phys. Lett.*, 2004, **84**, 3400–3402.

30 L. Kong, Y. Cheng, Y. Jin, Z. Ren, Y. Li and F. Xiao, *J. Mater. Chem. C*, 2015, **3**, 3364–3370.

31 H. Klauk, *Chem. Soc. Rev.*, 2010, **39**, 2643.

32 J. S. Lee, S. Chang, H. Bouzid, S. M. Koo and S. Y. Lee, *Phys. Status Solidi A*, 2010, **207**, 1694–1697.

33 K. Choi, S. R. A. Raza, H. S. Lee, P. J. Jeon, A. Pezeshki, S. Min, J. S. Kim, W. Yoon, S. Ju, K. Lee and S. Im, *Nanoscale*, 2015, **7**, 5617–5623.

34 E. G. Bittle, J. I. Basham, T. N. Jackson, O. D. Jurchescu and D. J. Gundlach, *Nat. Commun.*, 2016, **7**, 10908.

35 M. Kimura, *Solid-State Electron.*, 2011, **63**, 94–99.

36 N. L. Cohen, R. E. Paulsen and M. H. White, *IEEE Trans. Electron Devices*, 1995, **42**, 2004–2009.

37 H. S. Lee, S. S. Baik, K. Lee, S. Min, P. J. Jeon, J. S. Kim, K. Choi, H. J. Choi, J. H. Kim and S. Im, *ACS Nano*, 2015, **9**, 8312–8320.