# Nanoscale

### PAPER

Check for updates

Cite this: Nanoscale, 2019, 11, 3619

# Graphene-Si CMOS oscillators†

Carlo Gilardi,<sup>a</sup> Paolo Pedrinazzi, <sup>b</sup><sup>a</sup> Kishan Ashokbhai Patel,<sup>a</sup> Luca Anzi, <sup>b</sup><sup>a</sup> Birong Luo,<sup>b</sup> Timothy J. Booth, <sup>b</sup><sup>b</sup> Peter Bøggild <sup>b</sup><sup>b</sup> and Roman Sordan <sup>b</sup>\*<sup>a</sup>

Graphene field-effect transistors (GFETs) offer a possibility of exploiting unique physical properties of graphene in realizing novel electronic circuits. However, graphene circuits often lack the voltage swing and switchability of Si complementary metal–oxide-semiconductor (CMOS) circuits, which are the main building block of modern electronics. Here we introduce graphene in Si CMOS circuits to exploit favorable electronic properties of both technologies and realize a new class of simple oscillators using only a GFET, Si CMOS D latch, and timing RC circuit. The operation of the two types of realized oscillators is based on the ambipolarity of graphene also allowed to turn the oscillators into pulse-width modulators (with a duty cycle ratio ~1:4) and voltage-controlled oscillators (with a frequency ratio ~1:8) without any circuit modifications. The oscillation frequency was in the range from 4 kHz to 4 MHz and limited only by the external circuit connections, rather than components themselves. The demonstrated graphene–Si CMOS hybrid circuits pave the way to the more widespread adoption of graphene in electronics.

Received 27th September 2018, Accepted 25th January 2019 DOI: 10.1039/c8nr07862a

rsc.li/nanoscale

#### 1 Introduction

The development of graphene electronic circuits is mostly guided by the state-of-the-art circuit design of Si transistor technology. Such circuits try to exploit very large mobility<sup>1</sup> and saturation velocity<sup>2</sup> of charge carriers in graphene to match the performance of the corresponding Si circuits. However, this approach has not yielded satisfactory results so far because graphene does not have a bandgap<sup>3-5</sup> and therefore graphene fieldeffect transistors (GFETs) exhibit insufficient drain current saturation<sup>6,7</sup> and cannot be turned off. For instance, graphene ring oscillators<sup>8</sup> can indeed match the speed of the Si CMOS ring oscillators but only at the expense of considerable static power dissipation, which is unacceptable in highly-integrated digital circuits.9 If graphene were to find applications in electronics, its unique properties, such as flexibility,<sup>10</sup> transparency,<sup>11</sup> and ambipolarity,<sup>3</sup> should be exploited to achieve either novel functionality or the same functionality with fewer transistors, rather than to mimic Si circuits. One of the truly unique electronic properties of graphene not exhibited by conventional semiconductors is ambipolarity. The ambipolarity of graphene has been used in

the past to realize very simple logic gates<sup>12</sup> and frequency multipliers.<sup>13</sup> However, the logic gates suffered from large power dissipation and the mixers from large conversion loss, rendering both types of circuits unusable in realistic applications.

Here we demonstrate a novel class of graphene-Si CMOS circuits that exploit the ambipolarity of graphene to simplify the circuit and provide additional functionality. To illustrate the concept, we experimentally demonstrate two types of simple oscillators comprising just a GFET, a Si CMOS D latch, and a timing RC circuit. The D latch provides switching and large voltage swing for controlling the GFET, while the RC circuit is used to set the oscillation frequency  $(f_{osc})$ . The highest obtained oscillation frequency was  $f_{osc}$  = 4.2 MHz, limited only by the connections between the used discrete components. The ambipolarity of graphene allows realization of pulse-width modulators (PWMs) and voltage-controlled oscillators (VCOs) from the same oscillators, i.e., without any circuit modifications. Oscillating signals with a duty cycle in the range from 20% to 80% and maximum-to-minimum frequency ratio of 7.7 were obtained in this way. The concept of exploiting favorable electronic properties of GFETs and Si CMOS is general and can be realized with any ambipolar material, although graphene is preferable for high-speed operation.

## 2 Results

Top-gated GFETs were fabricated from graphene grown by chemical vapor deposition<sup>14,15</sup> (CVD) and then transferred to

Open Access Article. Published on 11 února 2019. Downloaded on 04.09.2025 9:02:07.

View Article Online

<sup>&</sup>lt;sup>a</sup>L-NESS, Department of Physics, Politecnico di Milano, Via Anzani 42, 22100 Como, Italy. E-mail: Roman.Sordan@polimi.it; Tel: +39 031 332 7622

<sup>&</sup>lt;sup>b</sup>CNG, DTU Nanotech, Department of Micro- and Nanotechnology, Technical University of Denmark, Ørsted Plads, Building 345C, 2800 Lyngby, Denmark

<sup>†</sup> Electronic supplementary information (ESI) available: Discussions on the shape of the static voltage transfer characteristic of the graphene circuit used in the oscillators, the highest frequency waveforms measured in a parabolic oscillator, and calculated PWM and VCO characteristics of the oscillators. See DOI: 10.1039/C8NR07862A

#### Paper

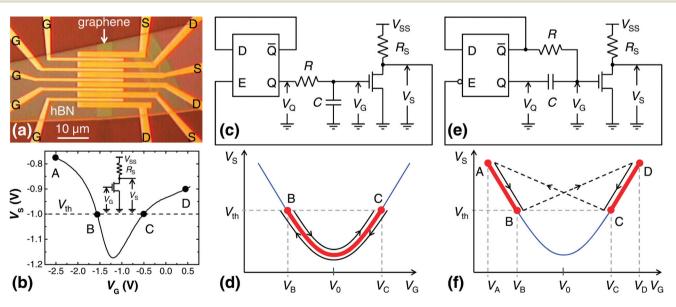

SiO<sub>2</sub>/Si substrates on which hBN<sup>16</sup> was previously exfoliated (Fig. 1(a)). The ambipolarity of graphene is reflected in the transfer curves of GFETs in which the same channel resistance  $(R_{\rm ch})$  is obtained at two different gate voltages  $(V_{\rm G})$ . These gate voltages are symmetrically distributed around the Dirac point  $(V_{\rm G} = V_0)$  at which  $R_{\rm ch}(V_{\rm G})$  reaches the maximum  $R_{\rm ch}(V_0)$ , as illustrated in ESI Fig. S1.† When a GFET is connected to a power supply  $(V_{SS})$  via a series resistor  $(R_S)$ , as shown in Fig. 1(b), the output voltage of such a simple graphene circuit is  $V_{\rm S} = V_{\rm SS} / (1 + R_{\rm S}/R_{\rm ch})$ .<sup>12</sup> Therefore, the output voltage  $V_{\rm S}$  has a maximum at the Dirac point for a positive supply  $(V_{SS} > 0)$  and minimum for a negative supply ( $V_{SS} < 0$ ), as shown in Fig. S1.<sup>†</sup> Throughout this work, a negative supply was used  $(V_{SS} = -2 \text{ V})$ because it allowed to obtain more symmetric digital signals, as discussed in the Experimental section. The measured static voltage transfer characteristic of such graphene circuit is shown in Fig. 1(b).

To simplify the oscillator circuit, the supply  $V_{\rm SS}$  of the graphene circuit was also used for the latch, hence the Si CMOS logic threshold was  $V_{\rm th} \approx V_{\rm SS}/2 = -1$  V. Therefore,  $V_{\rm SS} = -2$  V defined the low logic level (Boolean 0), while ground (0 V) defined the high logic level (Boolean 1). The output voltage  $V_{\rm S}$  of the graphene circuit was used to gate the Si CMOS logic, in this case a D latch. To be able to efficiently control, *i.e.*, change the state of the latch, the output voltage  $V_{\rm S}$  had to symmetrically swing around the threshold  $V_{\rm th}$ , as shown in Fig. 1(b). This was adjusted with the series resistor  $R_{\rm S}$ , which had to be below  $R_{\rm ch}(V_0)$  to ensure  $V_{\rm S}(V_0) < V_{\rm th}$ . Under these con-

ditions, the graphene circuit was able to trigger the latch in two operating points, denoted by B and C in Fig. 1(b), in which  $V_{\rm S} = V_{\rm th}$ .

Two types of oscillators were realized: parabolic (Fig. 1(c)) and bow tie (Fig. 1(e)), depending whether the Dirac point was a part of the oscillation cycle or not. In the first case, the operating point of the GFET oscillates between the points B and C moving through the Dirac point, as depicted in Fig. 1(d). In the case of the bow tie oscillator, the operating point oscillates outside of the operating range of the parabolic oscillator, *i.e.*, between the points A and B and between the points D and C in Fig. 1(f). In both cases, the D latch was operated in the toggle mode, *i.e.*, the latch changed its state whenever it was enabled, which was realized by connecting the complementary output ( $\overline{Q}$ ) of the latch to its data input (D). The latch in the parabolic oscillator was enabled for  $V_S > V_{\text{th}}$  and in the bow tie for  $V_S < V_{\text{th}}$ . The basic principle of operation of a D latch is briefly described in Fig. S2.<sup>†</sup>

In the parabolic oscillator, shown in Fig. 1(c), the high level at the output of the latch ( $V_Q = 0$  V, *i.e.*, Q = 1) charges the capacitor *C* through the resistor *R*, *i.e.*, the gate voltage  $V_G$ (equal to the capacitor voltage) increases. As  $V_G$  increases, the output voltage  $V_S$  of the GFET first decreases (for  $V_B < V_G < V_0$ ) and then increases (for  $V_0 < V_G < V_C$ ), as shown in Fig. 1(d). When  $V_G$  reaches  $V_C$  (the voltage in the operating point C), the output voltage of the graphene circuit reaches the threshold voltage  $V_{th}$  enabling the latch. This changes the state of the latch, *i.e.*, the output switches to the low state ( $V_Q = V_{SS} = -2$  V,

Fig. 1 Graphene–Si CMOS oscillators. (a) Optical image of 5 top-gated GFETs fabricated on an hBN flake. The source (S) and drain (D) contacts were made of Au while the gate (G) stack was made of  $Al/AlO_x$ . (b) The measured static voltage transfer characteristic of a circuit comprising a GFET connected to a supply  $V_{SS} = -2$  V via load  $R_S = 1.26$  k $\Omega$  (the circuit is shown in the inset). The load is realized as one of the neighboring GFETs in (a) with a floating (*i.e.*, not connected) gate. The output voltage  $V_S$  equals the threshold of the Si CMOS logic  $V_{th} \approx V_{SS}/2$  at the operating points B and C. (c) The schematic of a parabolic oscillator comprising the graphene circuit in (b), a Si CMOS D latch, and a timing RC circuit. The latch is enabled for  $V_S > V_{th}$ . (d) In the parabolic oscillator, the operating point oscillates between the operating points B and C (and therefore passes through the Dirac point). (e) The schematic of a bow tie oscillator comprising the same elements as the parabolic oscillator but with a latch which is enabled for  $V_S < V_{th}$ . (f) In the bow tie oscillator, the operating point oscillates along the segments AB and DC (and therefore does not pass through the Dirac point).

#### Nanoscale

*i.e.*, Q = 0) and the capacitor starts discharging through the same resistor. As  $V_G$  decreases,  $V_S$  decreases below the threshold  $V_{\rm th}$  disabling the latch. With the further decrease of  $V_G$ ,  $V_S$  first decreases (for  $V_0 < V_G < V_C$ ) and then increases (for  $V_B < V_G < V_0$ ), finally reaching the threshold voltage  $V_{\rm th}$  in the operating point B. This enables the latch again, which switches to the high state (Q = 1) and starts charging the capacitor. As  $V_S$  decreases, the latch disables and the entire cycle repeats again. In this way, the present relaxation oscillator keeps oscillating between the operating points B and C.

In the bow tie oscillator, shown in Fig. 1(e), when the latch is in the low state ( $V_{\rm O} = V_{\rm SS} = -2$  V, *i.e.*, Q = 0), the high state at the complementary output ( $\bar{Q} = 1$ ) charges the capacitor C through the resistor R, and the gate voltage increases to  $V_{\rm B}$ , as shown in Fig. 1(f). As  $V_{\rm G}$  increases, the output voltage  $V_{\rm S}$  of the graphene circuit decreases and when it reaches the threshold  $V_{\rm th}$  in the operating point B, the latch is enabled and switches to the high state ( $V_{\rm Q} = 0$  V, *i.e.*, Q = 1). The sudden increase of  $V_{\rm O}$  by  $|V_{\rm SS}|$  is transferred to the gate voltage  $V_{\rm G}$  because the capacitor voltage is a continuous function of time. As a consequence, the oscillator switches to the operating point D in which  $V_{\rm D} = V_{\rm B} + |V_{\rm SS}|$ . This disables the latch and the low state at the complementary output  $(\bar{Q} = 0)$  starts discharging the capacitor and therefore decreasing  $V_{\rm G}$ . Consequently,  $V_{\rm S}$ decreases from  $V_{\rm D}$  to  $V_{\rm C}$ , enabling the latch at the operating point C in which  $V_{\rm S} = V_{\rm th}$ . The latch switches to the low state again, instantly decreasing  $V_{\rm G}$  by  $|V_{\rm SS}|$ . The oscillator therefore switches to the operating point A in which  $V_{\rm A} = V_{\rm C} - |V_{\rm SS}|$  initiating the same cycle again.

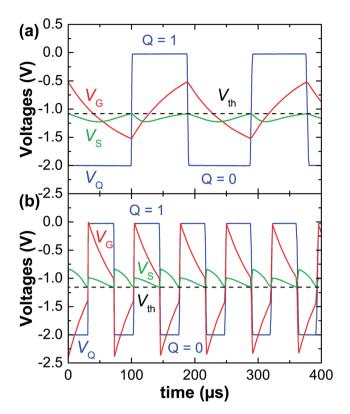

The measured signals in the oscillators are shown in Fig. 2, in which they were tuned to audio frequencies ( $f_{\rm osc}$  < 20 kHz) for clarity. The highest measured oscillation frequency was  $f_{\rm osc}$  = 4.2 MHz (Fig. S3<sup>†</sup>), limited by the off-chip connections between the graphene and Si CMOS chips. This limitation could be overcome by integrating both technologies in a single chip.<sup>17,18</sup> The oscillation frequency was set by the timing RC circuit, i.e., by the charging and discharging times of the capacitor. In the parabolic oscillator, the durations of the high state (Q = 1) and low state (Q = 0) are  $t_1 = RC \ln(V_B/V_C)$  and  $t_0 = RC \ln((V_{\rm C} - V_{\rm SS})/(V_{\rm B} - V_{\rm SS}))$ , respectively, which can easily be obtained from the transient response of a simple RC circuit.<sup>19</sup> In the bow tie oscillator, they are  $t_1 = RC \ln((V_B - C_B))$  $2V_{\rm SS}$ /( $V_{\rm C} - V_{\rm SS}$ )) and  $t_0 = RC \ln((V_{\rm C} + V_{\rm SS})/V_{\rm B})$ . This gives for the oscillation frequency  $f_{osc} = 1/T \propto 1/(RC)$ , where  $T = t_1 + t_0$  is the period.

The gate voltage levels  $V_{\rm B}$  and  $V_{\rm C}$ , at which  $V_{\rm S} = V_{\rm th}$ , mainly influence the duty cycle ( $D = t_1/T$ ) of the signals. The advantage of the oscillators is that the symmetric signals (D = 50%) are obtained for  $V_{\rm SS} = V_{\rm B} + V_{\rm C}$ , regardless of the asymmetry of the transfer curve of the GFET around the Dirac point (Fig. 1(b)). In this case, the output voltage  $V_{\rm S}$  of the GFET has the fundamental frequency of  $2f_{\rm osc}$ , *i.e.*, the oscillators are capable of generating the signals at frequencies  $f_{\rm osc}$  and  $2f_{\rm osc}$ at the same time. The asymmetry of the transfer curve of the GFET only causes the asymmetry of  $V_{\rm S}$  in Fig. 2, which is observable due to the large signal operation of the circuit.

**Fig. 2** The measured waveforms in the oscillators in air ambient for  $V_{SS} = -2 V$ ,  $R_S = 1.26 k\Omega$ , and C = 1 nF. (a) The waveforms in the parabolic oscillator with  $R = 85 k\Omega$  resulting in the oscillation frequency  $f_{osc} = 5.3 \text{ kHz}$  and duty cycle D = 46%. (b) The waveforms in the bow tie oscillator with  $R = 57 k\Omega$ ,  $f_{osc} = 13.8 \text{ kHz}$ , and D = 55%.

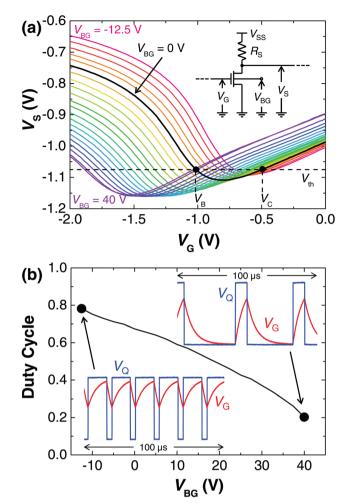

The gate voltage levels  $V_{\rm B}$  and  $V_{\rm C}$  and therefore the duty cycle D can be controlled by the GFET back-gate voltage, thus turning the oscillators into the PWMs without any circuit modifications. PWMs are typically used to digitally control the power supplies in electronic circuits.<sup>20</sup> Fig. 3(a) shows the static voltage transfer characteristic  $V_{\rm S}(V_{\rm G})$  at different backgate voltages ( $V_{BG}$ ). As the back-gate voltage is increased, a smaller top-gate voltage was required to reach the same carrier density in the channel, i.e., the transfer characteristic was shifted towards smaller voltages, as shown in Fig. 3(a). This decreased both  $V_{\rm B}$  and  $V_{\rm C}$  as  $V_{\rm BG}$  increased (Fig. S4<sup>+</sup>). In the parabolic oscillator, this increased  $t_0$  (Fig. S4<sup>†</sup>) and therefore decreased the duty cycle, as shown in Fig. 3(b). The measured duty cycle changed from 20% to 78% in one of the parabolic oscillators. In the bow tie oscillator, the duty cycle increased with  $V_{BG}$ , as the capacitor was charged in the low state (Fig. S4<sup>†</sup>) rather than in the high state as with the parabolic oscillator.

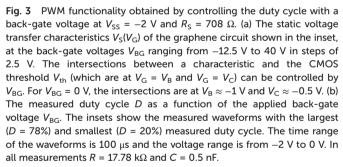

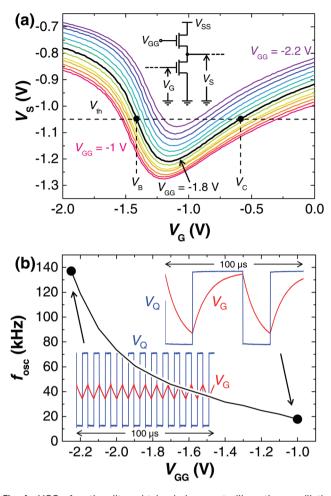

The graphene chip was fully integrated, *i.e.*, the fixed load resistor  $R_{\rm S}$  was integrated with the GFET as the channel of another GFET with a floating gate (Fig. 1(a)). However, the channel resistance  $R_{\rm S}$  could also be changed by connecting this gate to a voltage source  $V_{\rm GG}$ , as shown in Fig. 4(a). The increase of  $V_{\rm GG}$  decreased  $R_{\rm S}$  and therefore shifted the static

voltage transfer characteristic  $V_{\rm S}(V_{\rm G})$  to smaller output voltages  $V_{\rm S}$ , as shown in the same figure. This decreased  $V_{\rm B}$  and increased  $V_{\rm C}$  (Fig. S5†) and therefore increased both  $t_1$  and  $t_0$  in the parabolic oscillators, decreasing their oscillation frequency  $f_{\rm osc}$ . In this way, the gate voltage  $V_{\rm GG}$  was used to control  $f_{\rm osc}$  realizing the functionality of a VCO, one of the most used electronic circuits in communications systems.<sup>21</sup> By increasing  $V_{\rm GG}$ , the measured oscillation frequency decreased from 137 to 18 kHz in one of the parabolic oscillators, as shown in Fig. 4(b). In contrast, the increase of  $V_{\rm GG}$  decreased  $t_1$  and  $t_0$  (Fig. S5†) and therefore increased the oscillation frequency in the bow tie oscillators.

Fig. 4 VCO functionality obtained by controlling the oscillation frequency with a gate voltage at  $V_{SS} = -2$  V. (a) The static voltage transfer characteristics  $V_S(V_G)$  of the graphene circuit shown in the inset for different gate voltages  $V_{GG}$  of a load GFET which replaces the series resistor  $R_S$ .  $V_{GG}$  ranges from -2.2 V to -1 V in steps of 0.1 V.  $V_{GG}$  controls the GFET resistance  $R_S$  and consequently the vertical shift of the transfer characteristics. The intersections between a characteristic and the CMOS threshold  $V_{th}$  (which are at  $V_G = V_B$  and  $V_G = V_C$ ) are therefore controlled by  $V_{GG}$ . For  $V_{GG} = -1.8$  V, the intersections are at  $V_B ≈ -1.4$  V and  $V_C ≈ -0.6$  V. (b) The measured oscillation frequency  $f_{osc}$  as a function of the gate voltage  $V_{GG}$ . The insets show the measured waveforms with the highest ( $f_{osc} = 137$  kHz) and lowest ( $f_{osc} = 18$  kHz) measured oscillation frequency. The time range of the waveforms is 100 µs and the voltage range is from -2 V to 0 V. In all measurements R = 10 kΩ and C = 1 nF.

### 3 Discussion

For the same circuit components, the oscillation frequency of the bow tie oscillator is higher than that of the parabolic oscillator because the operating point of the bow tie oscillator stays only on one side of the Dirac point during each half period. Assuming a duty cycle of 50% in both oscillators, *i.e.*,  $V_{\rm SS} =$  $V_{\rm B} + V_{\rm C}$ , the bow tie oscillator oscillates at twice the frequency of the parabolic oscillator if  $V_{\rm B} = 0.742V_{\rm SS}$  and  $V_{\rm C} = 0.258V_{\rm SS}$ . The disadvantage of the bow tie oscillator is that its gate voltage can overshoot the supply voltage rails at the signal edges, *e.g.*,  $|V_G| > |V_{SS}|$  at the falling edge of *Q* in Fig. 2(b). This could be dangerous for other components in the circuit, primarily the GFET which has the gate voltage breakdown of ~2.9 V. In a bow tie PWM, the largest overshoots are at the two extremes of the duty cycle.

The present oscillators can be fabricated on a large scale because they do not require exfoliated hBN or a global back gate. The exfoliated hBN was used only because of the large doping of the GFETs on  $SiO_2$  in the used batch. Similarly, the global backgate was used in PWMs only for demonstration; in realistic devices this can easily be replaced by a local back gate so that each PWM is individually gated. Control voltages in PWMs and VCOs are typically obtained from the output of other circuits rather than separate power supplies. For example, a VCO is driven by a phase detector in a phase-locked loop (PLL).<sup>21</sup>

The demonstrated principle of operation is general, *i.e.*, the other ambipolar materials, *e.g.*, amorphous Si,<sup>22</sup> Si nanowires<sup>23</sup> or semiconducting carbon nanotubes,<sup>24</sup> could also be used. Although their ambipolarity has been exploited in applications<sup>25,26</sup> similar to that of graphene,<sup>12</sup> they have not been combined with Si CMOS logic so far. In contrast to other ambipolar materials, graphene has much larger carrier mobility<sup>1</sup> and saturation velocity<sup>2</sup> allowing much faster operation. The symmetric band structure of graphene<sup>27</sup> (*i.e.*, almost identical electron and hole mobilities) also leads to symmetric digital signals, which cannot easily be obtained in materials with different electron and hole mobilities.

In terms of the component count, the present oscillators are similar to the simplest Si field-effect transistor (FET) oscillators, because they were made of only 5 components. However, it should be noted that a gated D latch<sup>28</sup> is usually made of 10 FETs, resulting in 14 components in the oscillator. The commercial discrete D latches usually comprise more than 10 FETs because they also provide three-state outputs (which were not used here). For comparison, the simplest conventional astable multivibrators with vertical signal edges<sup>19</sup> have only 2 FETs, but also 10 other components, bringing the total component count to 12. The simplest Si CMOS ring oscillators<sup>29</sup> have 6 FETs but their oscillation frequency is determined by internal gate delays<sup>8,9</sup> rather than a timing RC circuit. Finally, the simplest Schmitt trigger inverter oscillators<sup>30</sup> have 8 components. Despite similar component count, the present oscillators provide additional functionalities of the PWMs and VCOs. Compared to graphene ring oscillators,<sup>8,9</sup> which have a limited output voltage swing, the output voltage swing in the present oscillators is determined by the Si CMOS part of the circuit providing rail-to-rail operation.

Although the oscillators use a GFET which cannot be turned off, the static power dissipation is not a critical factor because the relaxation oscillators do not spend any time in the idle state and dissipate the dynamic power continuously. This could also be understood from the ratio between the static power dissipation of the graphene circuit  $P_{\rm s} \sim V_{\rm SS}^2/(2R_{\rm s})$  and dynamic (switching) power dissipation  $P_{\rm d} \sim f_{\rm osc} CV_{\rm SS}^2/2$  of the timing RC circuit. Here it was assumed for simplicity that the

voltage on the capacitor oscillates between  $0.25V_{\rm SS}$  and  $0.75V_{\rm SS}$  (as in Fig. 2(a)) and that the power dissipation of the D latch is negligible. The ratio  $P_{\rm s}/P_{\rm d} \sim R/R_{\rm s}$ , because  $f_{\rm osc} \sim 1/(RC)$ , meaning that for large  $f_{\rm osc}$  (*i.e.*,  $R < R_{\rm s}$ ),  $P_{\rm s} < P_{\rm d}$ . For example,  $R/R_{\rm s} \sim 50$  in the low-frequency oscillators shown in Fig. 2, but  $R/R_{\rm s} \sim 0.25$  in the high-frequency oscillator shown in Fig. S3.†

The realized oscillators could be used to provide high-frequency reference required for the signal up/down conversion in high frequency transmitters/receivers. The D latch is not expected to limit the bandwidth of the fully integrated oscillators because high-speed Si CMOS technology is capable of operating at very high serial data rates (up to 120 Gb s<sup>-1</sup>).<sup>31</sup>

The realized oscillators could also be used to generate clock signals for digital data processing which requires the exact clock duty cycle of 50%. In microprocessors, this is typically achieved by running a VCO (inside the PLL) at twice the clock frequency and then dividing the frequency by two.<sup>32,33</sup> However, such realizations significantly increase the dynamic power dissipation and are not practical at very high frequencies. Our oscillators offer an alternative solution because both PWM (duty cycle tuning) and VCO (frequency tuning) are integrated in the same circuit.

The integration of graphene with Si CMOS technology should be considered in the context of 3D monolithic integrated circuits (ICs). Such ICs cannot be easily made in Si CMOS technology due to high temperatures required for the fabrication of each Si CMOS layer in a 3D stack. This problem can be overcome by stacking other transistor technologies, which do not require high-temperature fabrication, on top of Si CMOS.<sup>34</sup> Alternative transistor technologies also allow realization of additional functionalities which cannot be obtained with Si CMOS alone.<sup>34,35</sup> Graphene is a good candidate for the integration with Si CMOS in 3D monolithic ICs because it can be transferred to a target substrate at room temperature.

### 4 Conclusions

We exploited the symmetry of the transfer characteristics of GFETs to realize a new class of very simple electronic relaxation oscillators comprising a GFET, Si CMOS latch, and RC timing circuit. The difference between the two types of the realized oscillators was in the movement of the operating point, oscillating through the Dirac point in the first type and jumping over the Dirac point in the second type. The simplicity of the oscillators and additional PWM and VCO functionalities, obtained without any circuit modifications, stemmed from the ambipolarity of graphene. The switching and large voltage swing of generated waveforms were provided by Si CMOS logic. The introduction of graphene in Si CMOS logic may prove to be a feasible approach in simplifying it and providing additional functionality while at the same time overcoming barriers to entry of graphene in electronics.

### 5 Experimental

hBN was exfoliated on highly p-doped (>10<sup>19</sup> cm<sup>-3</sup>) Si substrates with a 300 nm thick top layer of SiO<sub>2</sub>. The back of the Si substrates was metallized and used as a global back-gate, if needed. Monocrystalline monolayer graphene was grown by CVD on Cu from the CH<sub>4</sub> precursor and then transferred (by a wet process) to the same substrates on which hBN was previously exfoliated. The GFETs were patterned by electron-beam (e-beam) lithography using poly(methyl methacrylate) resist. The GFET channels (the channel width  $W = 5 \mu m$ ) were defined by etching graphene in O<sub>2</sub> plasma both in parts of the substrates covered and uncovered by hBN flakes. This allowed fabrication of a large number of GFETs on hBN (the only selection criteria were the lateral size >5 µm and thickness <50 nm of the hBN flakes) and control GFETs on SiO<sub>2</sub> in the same chips.

The rest of the fabrication process was the same in both cases. Top-gates were patterned first by e-beam lithography followed by e-beam evaporation of 100 nm of Al. Al oxidized after a few days in air ambient creating a thin (~4 nm) native layer of AlO<sub>x</sub> on all surfaces of Al, including the interface with graphene.<sup>36–40</sup> This formed an AlO<sub>x</sub>/Al gate stack with a top-gate oxide capacitance<sup>8,40</sup>  $C_{\text{ox}} = 1.37 \,\mu\text{F cm}^{-2}$ . Source and drain Au contacts (100 nm) were finally fabricated by e-beam lithography and e-beam evaporation. The gate length was  $L = 1 \,\mu\text{m}$ , source-to-drain distance  $L_{\text{SD}} = 1.2 \,\mu\text{m}$  (*i.e.*, the access length from both sides of the gate was 100 nm), and length of the source and drain contacts was 2  $\mu$ m.

The oscillators worked both with a positive and negative power supply. However, we found that a negative supply allowed more symmetric digital signals at  $|V_{\rm SS}| \sim 2$  V, *i.e.*, the signals with a duty cycle closer to 50%. This is because the unbiased GFETs on hBN had the Dirac voltage  $V_0 \approx -0.5$  V, which changed to  $\approx V_0 + V_{\rm SS}/4$  when  $V_{\rm SS}$  was applied (because  $R_{\rm ch} \approx R_{\rm S}$  at the Dirac point). The signal symmetry requires  $V_{\rm H} - V_{\rm C} = V_{\rm B} - V_{\rm L}$ , *i.e.*, that the Dirac voltage is approximately half way between the voltage rails. This means  $V_0 + V_{\rm SS}/4 \approx$  $V_{\rm SS}/2$ , *i.e.*,  $V_{\rm SS} \approx 4V_0$ , which is the reason the supply  $V_{\rm SS} = -2$  V was used. The series resistance  $R_{\rm S}$  was realized as either an external discrete resistor or another GFET with a floating gate. The output voltage swing of the graphene circuit depends on  $R_{\rm S}$ , *e.g.*, the highest swing in the parabolic oscillator is obtained for  $R_{\rm S} = \sqrt{R_{\rm ch}(V_0)R_{\rm ch}(V_{\rm B})}$ .

The GFETs were made on hBN substrate because the lower  $|V_0|$  allowed the use of lower supply voltages  $|V_{SS}|$ , as described above. We also found that GFETs on hBN had much better long-term stability than GFETs on SiO<sub>2</sub>. The same GFETs on hBN were repeatedly measured in the oscillators for months without any apparent degradation of their electrical properties.

The Si CMOS part of the oscillator circuit (including the timing RC circuit) was built on a breadboard (in low-frequency oscillators) or printed circuit board (in high-frequency oscillators) and connected to the GFET *via* a FormFactor probe station. The Si CMOS gated D latch was 74HC375AP or 74AC573P. The dc characteristics were measured by Keithley

2611A source measure units, while the waveforms were measured by Keysight Infiniium DSO9404A oscilloscope and Keysight N2795A and 1158A active probes.

### Conflicts of interest

There are no conflicts to declare.

#### Acknowledgements

This research was supported by the EU H2020 Graphene Flagship Core 2 Grant No. 785219.

#### References

- A. S. Mayorov, R. V. Gorbachev, S. V. Morozov, L. Britnell, R. Jalil, L. A. Ponomarenko, P. Blake, K. S. Novoselov, K. Watanabe, T. Taniguchi and A. K. Geim, *Nano Lett.*, 2011, **11**, 2396–2399.

- 2 V. E. Dorgan, M.-H. Bae and E. Pop, *Appl. Phys. Lett.*, 2010, **97**, 082112.

- 3 K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva and A. A. Firsov, *Science*, 2004, **306**, 666–669.

- 4 Y.-W. Son, M. L. Cohen and S. G. Louie, *Phys. Rev. Lett.*, 2006, **97**, 216803.

- 5 M. Y. Han, B. Özyilmaz, Y. Zhang and P. Kim, *Phys. Rev. Lett.*, 2007, 98, 206805.

- 6 B. N. Szafranek, G. Fiori, D. Schall, D. Neumaier and H. Kurz, *Nano Lett.*, 2012, **12**, 1324–1328.

- 7 E. Guerriero, P. Pedrinazzi, A. Mansouri, O. Habibpour, M. Winters, N. Rorsman, A. Behnam, E. A. Carrion, A. Pesquera, A. Centeno, A. Zurutuza, E. Pop, H. Zirath and R. Sordan, *Sci. Rep.*, 2017, 7, 2419.

- 8 E. Guerriero, L. Polloni, M. Bianchi, A. Behnam, E. Carrion, L. G. Rizzi, E. Pop and R. Sordan, *ACS Nano*, 2013, 7, 5588– 5594.

- 9 M. Bianchi, E. Guerriero, M. Fiocco, R. Alberti, L. Polloni, A. Behnam, E. A. Carrion, E. Pop and R. Sordan, *Nanoscale*, 2015, 7, 8076–8083.

- 10 T. Carey, S. Cacovich, G. Divitini, J. Ren, A. Mansouri, J. M. Kim, C. Wang, C. Ducati, R. Sordan and F. Torrisi, *Nat. Commun.*, 2017, 8, 1202.

- 11 P. Blake, E. W. Hill, A. H. Castro Neto, K. S. Novoselov, D. Jiang, R. Yang, T. J. Booth and A. K. Geim, *Appl. Phys. Lett.*, 2007, **91**, 063124.

- 12 R. Sordan, F. Traversi and V. Russo, *Appl. Phys. Lett.*, 2009, 94, 073305.

- 13 H. Wang, D. Nezich, J. Kong and T. Palacios, *IEEE Electron Device Lett.*, 2009, **30**, 547–549.

- 14 X. Li, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner,

A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee,

L. Colombo and R. S. Ruoff, *Science*, 2009, 324, 1312–1314.

Paper

This article is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported Licence.

Open Access Article. Published on 11 února 2019. Downloaded on 04.09.2025 9:02:07.

- 15 J. D. Wood, S. W. Schmucker, A. S. Lyons, E. Pop and J. W. Lyding, *Nano Lett.*, 2011, **11**, 4547–4554.

- 16 C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard and J. Hone, *Nat. Nanotechnol.*, 2010, 5, 722–726.

- 17 M. C. Lemme, T. J. Echtermeyer, M. Baus and H. Kurz, *IEEE Electron Device Lett.*, 2007, **28**, 282–284.

- 18 S. K. Hong, C. S. Kim, W. S. Hwang and B. J. Cho, ACS Nano, 2016, 10, 7142–7146.

- 19 J. Millman and H. Taub, *Pulse, Digital, and Switching Waveforms*, McGraw-Hill, Kogakusha, 1965.

- 20 D. G. Holmes and T. A. Lipo, *Pulse Width Modulation for Power Converters: Principles and Practice*, Wiley-IEEE Press, Hoboken, 2003.

- 21 S. Voinigescu, *High-Frequency Integrated Circuits*, Cambridge University Press, Cambridge, 2013.

- 22 H. Pfleiderer and W. Kusian, *Solid-State Electron.*, 1986, **29**, 317–319.

- 23 S.-M. Koo, M. D. Edelstein, Q. Li, C. A. Richter and E. M. Vogel, *Nanotechnology*, 2005, **16**, 1482.

- 24 R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K. K. Chan, J. Tersoff and P. Avouris, *Phys. Rev. Lett.*, 2001, 87, 256805.

- 25 R. Sordan, K. Balasubramanian, M. Burghard and K. Kern, *Appl. Phys. Lett.*, 2006, **88**, 053119.

- 26 D. Sacchetto, Y. Leblebici and G. D. Micheli, *IEEE Electron Device Lett.*, 2012, **33**, 143–145.

- 27 K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, M. I. Katsnelson, I. V. Grigorieva, S. V. Dubonos and A. A. Firsov, *Nature*, 2005, **438**, 197–200.

- 28 R. C. Jaeger and T. N. Blalock, *Microelectronic Circuit Design*, McGraw-Hill, New York, 2011.

- 29 B. Razavi, *Design of Analog CMOS Integrated Circuits*, McGraw-Hill, Boston, 2001.

- 30 R. J. Baker, *CMOS Circuit Design, Layout, and Simulation*, Wiley-IEEE Press, Hoboken, 2010.

- 31 K. K. Tokgoz, S. Maki, J. Pang, N. Nagashima, I. Abdo, S. Kawai, T. Fujimura, Y. Kawano, T. Suzuki, T. Iwai, K. Okada and A. Matsuzawa, 2018 IEEE Int. Solid - State Circuits Conf. - (ISSCC), 2018, pp. 168–170.

- 32 I. A. Young, J. K. Greason and K. L. Wong, *IEEE J. Solid-State Circuits*, 1992, 27, 1599–1607.

- 33 S. Tam, S. Rusu, U. N. Desai, R. Kim, J. Zhang and I. Young, *IEEE J. Solid-State Circuits*, 2000, 35, 1545–1552.

- 34 M. M. Shulaker, G. Hills, R. S. Park, R. T. Howe, K. Saraswat, H. S. P. Wong and S. Mitra, *Nature*, 2017, 547, 74–78.

- 35 T. Palacios, Nat. Nanotechnol., 2011, 6, 464-465.

- 36 H. Miyazaki, S. Li, A. Kanda and K. Tsukagoshi, *Semicond. Sci. Technol.*, 2010, 25, 034008.

- 37 E. Guerriero, L. Polloni, L. G. Rizzi, M. Bianchi,G. Mondello and R. Sordan, *Small*, 2012, 8, 357–361.

- 38 C.-C. Lu, Y.-C. Lin, C.-H. Yeh, J.-C. Huang and P.-W. Chiu, ACS Nano, 2012, 6, 4469–4474.

- 39 C.-H. Yeh, Y.-W. Lain, Y.-C. Chiu, C.-H. Liao, D. R. Moyano, S. S. H. Hsu and P.-W. Chiu, ACS Nano, 2014, 8, 7663–7670.

- 40 C. D. English, K. K. Smithe, R. Xu and E. Pop, Int. El. Devices Meet., San Francisco, CA, USA, 2016, pp. 5.6.1– 5.6.4.