# Nanoscale

### Accepted Manuscript

This is an *Accepted Manuscript*, which has been through the Royal Society of Chemistry peer review process and has been accepted for publication.

Accepted Manuscripts are published online shortly after acceptance, before technical editing, formatting and proof reading. Using this free service, authors can make their results available to the community, in citable form, before we publish the edited article. We will replace this Accepted Manuscript with the edited and formatted Advance Article as soon as it is available.

You can find more information about *Accepted Manuscripts* in the **Information for Authors**.

Please note that technical editing may introduce minor changes to the text and/or graphics, which may alter content. The journal's standard <u>Terms & Conditions</u> and the <u>Ethical guidelines</u> still apply. In no event shall the Royal Society of Chemistry be held responsible for any errors or omissions in this *Accepted Manuscript* or any consequences arising from the use of any information it contains.

www.rsc.org/nanoscale

# ARTICLE TYPE

## Ultralow Power Complementary Inverter Circuits Using Axially Doped p- and n-channel Si Nanowire Field Effect Transistors

Ngoc Huynh Van<sup>1,†</sup>, Jae-Hyun Lee<sup>2,†</sup>, Dongmok Whang<sup>2</sup>, and Dae Joon Kang<sup>1,\*</sup>

## s Received (in XXX, XXX) XthXXXXXXX 20XX, Accepted Xth XXXXXXXX 20XX DOI: 10.1039/b000000x

We successfully synthesized axially doped p- and n-type regions on a single Si nanowire (NW). Diode and complementary metal-oxidesemiconductor (CMOS) inverter devices using single axial p- and n-channel Si NW field-effect transistors (FETs) were fabricated. We show that the threshold voltages of both p- and n-channel Si NW FETs can be lowered to nearly zero by effectively controlling the

<sup>10</sup> doping concentration. Because of the high performance of the p- and n-type Si NW channel FETs, especially with regard to the low threshold voltage, the fabricated NW CMOS inverters have a low operating voltage (<3 V) while maintaining a high voltage gain (~6) and ultralow static power dissipation ( $\leq 0.3 \text{ pW}$ ) at an input voltage of  $\pm 3 \text{ V}$ . This result offers a viable way to fabricate a highperformance high-density logic circuit using a low-temperature fabrication process, which makes it suitable for flexible electronics.

#### 15 1. Introduction

Complementary metal-oxide-semiconductor (CMOS) inverter devices involving both p- and n-type field-effect transistors (FETs) are among the most common building blocks in logic circuit designs.<sup>1</sup> The current downscaling of mainstream Si <sup>20</sup> CMOS technology has increased the speed of logic circuits.

- <sup>20</sup> Civio's technology has increased the speed of logic circuits. However, it has also increased the dissipated power. Moreover, the current top-down miniaturization trend is expected to reach fundamental physical limits soon, motivating the development of new device structures as well as functional materials to be <sup>25</sup> implemented in nanoscale electronic devices.<sup>2–5</sup>

- In particular, one-dimensional nanostructures such as nanowires (NWs), carbon nanotubes (CNTs), and graphene nanoribbons are promising candidates for conducting channels in FETs owing to their fascinating electrical transport properties and

- <sup>30</sup> consequent application potential to overcome the technical and physical limitations encountered by traditional lithography-based thin-film transistors (TFTs).<sup>6–8</sup>

The superior carrier mobility and small size of CNTs and graphene ribbons have been exploited to surpass Si in terms of <sup>35</sup> the operation speed in logic device applications. Despite advances in these materials, a large gap still exists between the status of CNT- and graphene-nanoribbon-based FETs and industrial application requirements.<sup>9–12</sup> Therefore, Si NWs have been intensively investigated by many research groups as a

- <sup>40</sup> replacement for standard CMOS-based TFT technology.<sup>3,4,13</sup> In particular, Si nanowires containing p-n junctions are fundamental building blocks for CMOS device applications. Different methods of synthesizing an axially doped p-n junction on a single Si NW have been reported, but currently the applications in which they

- <sup>45</sup> are implemented, such as photovoltaics<sup>14–17</sup> and tunnelling transistors,<sup>18</sup> are based on p-n junction diodes. The transport

properties of the n- and p-type FETs that make up a CMOS inverter must be compatible. Single n- and p-type NW devices for logic circuits have been reported.<sup>19,20</sup> Owing to the difficulty of <sup>50</sup> controlling the transport properties of each part of the axial p-n Si NWs in previous reports, a CMOS inverter based on an axial p-n Si NW has not been demonstrated.<sup>18,21,22</sup>

In this communication, we first present a simple method of synthesizing highly ordered axially doped p- and n-type regions <sup>55</sup> on a single Si NW, where the transport properties of each p- and n-type region can be modulated by effectively controlling the doping concentration. A p-n junction diode and CMOS inverter, each of which can be selectively fabricated on a single Si NW, are then measured, and the results are analysed and discussed. <sup>60</sup> The inverter devices exhibit high performance characteristics, a low operating voltage, and low static power dissipation, making them suitable for high-density, high-performance, and flexible<sup>23-</sup> <sup>25</sup> logic device applications.

#### 2. Experimental

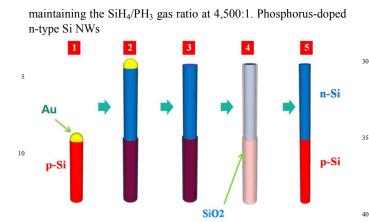

Synthesis of axially doped p- and n-type regions on a single Si NW and removal of the radial growth layer: The processes used to synthesize axially doped p- and n-type regions on a single Si NW and to remove the radial growth layer are shown in Fig. 1. The p-n Si NWs were grown on (100) Si substrates by a vapour-70 liquid-solid method catalysed by 40-nm Au nanoclusters in a low-pressure chemical vapour deposition (CVD) reactor, as reported in detail by Koo *et al.*<sup>14</sup> First, 20-µm-long p-type Si NWs were nucleated and grown with Au tips for 20 min. Boron was introduced as a p-type dopant directly during growth with a 75 silane (SiH<sub>4</sub>)/diborane (B<sub>2</sub>H<sub>6</sub>) gas ratio maintained at 5,500:1. When p-type growth was completed, an n-type dopant gas was introduced by switching from B<sub>2</sub>H<sub>6</sub> to phosphine (PH<sub>3</sub>) and

<sup>15</sup> Fig.1 Synthesis of axially doped p- and n-type regions on a single Si NW, and removal of the radial growth layer. (1) Growth of the p-type Si NW, (2) growth of the n-type Si NW on top of the p-type Si NW, (3) etching of the Au catalyst, (4) thermal oxidation of the Si NW, (5) etching of the oxide shell.

20 µm in length were subsequently grown from the ends of the ptype Si NWs with Au tips for 30 min. Both vertical growth of ntype Si NWs on top of the p-type Si NWs and radial growth of an n-type shell layer on the p-type region of each Si NW were 25 observed. To expose the p-type region, the n-type shell grown on the ptype region was removed by thermal oxidation of the shell and subsequent chemical etching of the oxide. After CVD growth, the <sup>30</sup> substrate with the p-n Si NWs was dipped in a solution of potassium iodide and iodine (KI/I<sub>2</sub>) to remove the Au tips. After the Au residue was removed, the NWs were thermally oxidized in a furnace at 800 °C for 15 min in air and then cleaned in oxygen plasma (50 W, 0.3 Torr, O<sub>2</sub> 100 sccm, 300 s). Finally, the formed <sup>35</sup> oxide shell was removed in 10% hydrofluoric acid for ~30 s until the surface of the substrate became hydrophobic.

To optimize the operating voltage of the CMOS inverter based on the p-n Si NW, the doping concentrations of both the p- and ntype regions were varied. The SiH<sub>4</sub>/PH<sub>3</sub> gas ratio was varied from  $_{40}$  3,000:1 to 6,000:1 for the n-type Si region, whereas the SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub> gas ratio was varied from 3,500:1 to 6,500:1 for the p-type Si region.

Fabrication and measurement of p-n junction diode and CMOS inverter based on axial p-n Si NWs: Single-crystalline <sup>45</sup> axially doped p-n Si NWs with a typical diameter of 45–55 nm (after removal of the n-type radial growth layer on the p-type region) were first dispersed via ultrasonication in isopropanol; a drop of the liquid suspension of the Si NWs was then transferred to a silicon substrate using a pipette. A heavily doped p-type Si <sup>50</sup> substrate (0.005  $\Omega$ cm) was employed as a back gate with a 100nm-thick, thermally oxidized SiO<sub>2</sub> top layer as a gate oxide layer. Multiple electrodes were patterned on the NW by a conventional

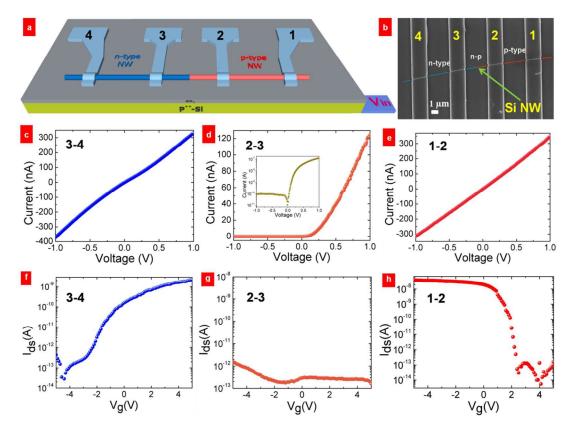

**Fig. 2** Schematic drawing, scanning electron microscope (SEM) image, and electrical characteristics of the p-n Si NW device. (a) Schematic drawing of the axially doped p-n Si NW device. (b) SEM image of the p-n Si NW in the device configuration. Current–voltage ( $I_{ds}-V_{ds}$ ) characteristics measured (c) between two contacts in the n-type region, (d) across the p-n diode region, Inset shows the p-n junction diode in log scale, and (e) between two contacts in the p-type region, all with a back-gate voltage of  $V_g = 0$  V. Transfer characteristics ( $I_{ds}-V_g$ ) at  $V_{ds} = 0.1$  V (f) in the n-type region, (g) across the p-n region, and (h) in the p-type region.

photolithography process. Before deposition of the metal electrodes, the samples were immersed in a buffered 1% hydrofluoric acid solution for 15 s to remove the native oxide layer that formed on the surface of the Si NWs during <sup>5</sup> processing.<sup>14</sup> The contact electrodes were subsequently deposited by electron-beam evaporation as follows to form ohmic contacts: a 20-nm-thick nickel–chrome layer (NiCr; 80% Ni and 20% Cr)

- was first evaporated, followed by an 80-nm-thick Au layer. The electrical characteristics of the devices were measured in air using 10 a probe station with a Keithley SCS-4200 system.

- Synthesis of n- and p-type Si NWs: The n- and p-type Si NWs used in this study were grown on Si (100) substrates with Au catalysts using a vapour-liquid-solid method, as reported in detail by T. Koo *et al.*<sup>14</sup>In this experiment, n- and p-type Si NWs were <sup>15</sup> doped with phosphorus or boron directly during growth. The silane (SiH<sub>4</sub>)/phosphine (PH<sub>3</sub>) gas ratio was varied from 4,000:1 to 10,000:1 for n-type Si NWs, whereas the boron-doped p-type Si NWs were grown with a silane (SiH<sub>4</sub>)/diborane (B<sub>2</sub>H<sub>6</sub>) gas ratio varied from 3,000:1 to 6,500:1.

- the metal electrodes. It also proves that the rectifying diode characteristics (Fig. 2d), with the p-n junction diode ideality factor was calculated from log scale of inserted Fig.2d is 1.8, and <sup>40</sup> near absence of gate effects in the transfer characteristics (Fig. 2g) measured between contacts 2 and 3 originate from the p-n junction rather than the Schottky characteristics of the metal–Si contacts. Moreover, the ambipolar gate effect was observed in Si NWs p-n junction diode when the forward bias voltage was set at <sup>45</sup> 1 V, above the rectifying voltage of p-n junction diode (Fig. S1 in the Supplementary Information). The diode should work at ON state. Thus, the region close to the p–n junction exhibit a clear gate effect. <sup>21</sup>

- To fabricate a CMOS inverter based on single p-n Si NW <sup>50</sup> FETs, the position of the inverter output metal contact was adjusted to be over the p-n junction region. The operation of NW CMOS inverters was demonstrated in our previous report.<sup>26</sup> A larger threshold voltage requires a larger gate voltage for the device to function as an inverter. To use the CMOS NW as a low-<sup>55</sup> operating-voltage inverter, the threshold voltages of the p- and n-

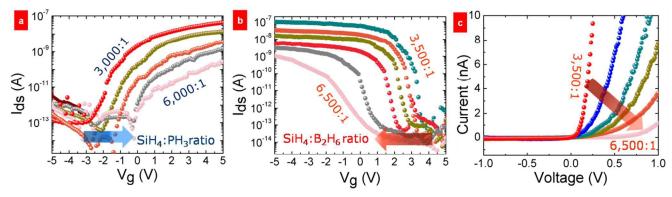

**Fig. 3** Tunable threshold voltage and diode behavior at various doping concentrations. (a)  $I_{ds}-V_g$  transfer characteristics of the n-type region of the p-n Si NW FETs at different doping concentrations (SiH<sub>4</sub>/PH<sub>3</sub> ratios of 3,000:1 to 6,000:1), showing a positive shift of the threshold voltage. (b)  $I_{ds}-V_g$  transfer characteristics of the p-type region of the p-n Si NW FETs at different doping concentrations (SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub> gas ratios of 3,500:1 to 6,500:1), showing a positive shift of the threshold voltage. (c) Diode behavior at different doping concentrations (SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub> gas ratios of 3,500:1 to 6,500:1), showing a positive shift of the threshold voltage. (c) Diode behavior at different doping concentrations.

#### 20 3. Results and Discussion

The processes used to synthesize axially doped p- and n-type regions on a single Si NW (a p-n Si NW) and to remove the radial growth layer are shown in Fig. 1. The electrical characteristics of the diode based on a p-n Si NW were measured by four <sup>25</sup> electrodes and a back gate, as shown in the schematic drawing in

- Fig. 2a. Because either the n- or p-type NW region in contact with metal electrodes could possibly show metal–Si Schottky contact diode characteristics, the positions of the metal contacts were adjusted so that the two contacts were positioned on each wide of the n n investign. For exercise, the next 2 the linear exercise

- <sup>30</sup> side of the p-n junction. For contacts 1 and 2, the linear currentvoltage  $(I_{ds}-V_{ds})$  characteristics (Fig. 2e) and back-gate transfer characteristics  $(I_{ds}-V_g)$  at  $V_{ds} = 0.1$  V(Fig. 2h) were those of a ptype FET, whereas contacts 3 and 4 exhibited n-type FET characteristics (Fig. 2c,f). The linearity of these  $I_{ds}$ - $V_{ds}$  value of the sector residues and that an

- $_{35}$   $V_{\rm ds}$  characteristics suggests a low contact resistance and that an Ohmic contact forms between both the p- and n-type regions and

type regions should be shifted as close to 0 V as possible. Several schemes have been proposed to make n-type ZnO NW FETs operate in an enhancement mode by tuning the diameter and surface conditions of the ZnO NWs,<sup>27-29</sup> working with the 60 electrode work functions,<sup>30</sup> or employing proton irradiation.<sup>20</sup> In this study, the threshold voltages of the p- and n-type regions of the Si NW are shifted negatively and positively, respectively, toward zero by changing the doping concentrations. The SiH<sub>4</sub>/PH<sub>3</sub> gas ratios (i.e. the doping concentrations) were varied, 65 and several FETs based on the p-n Si NWs were constructed; each region, p-type and n-type, was then measured extensively. The effects of the doping concentration on the conductance and threshold voltages of the p-n Si NW FETs are shown in Fig. 3a,b, respectively. The transfer characteristics, that is, the drain current <sup>70</sup> versus gate-source voltage  $(I_{ds}-V_{\sigma})$ , of several n-type regions of the Si NW FETs at different doping concentrations, were obtained by sweeping the gate voltage continuously from -5 to +5 V with a

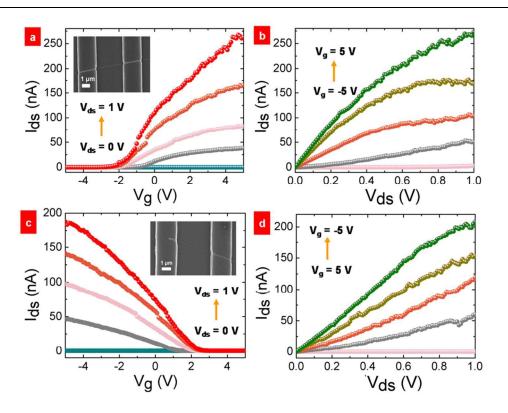

Fig. 4 Electrical transport properties of the p-n Si NW FETs under ambient conditions. (a and c)  $I_{ds}-V_g$  transfer characteristics and (b and d)  $I_{ds}-V_{ds}$  output characteristics of the n- and p-type regions of the p-n Si NW FETs, respectively.

drain voltage of 0.1 V. The negative threshold voltage shifted positively from approximately -3.5 V to close to -0.5 V as the doping concentration was reduced. The transconductance, electron mobility, subthreshold swing, and carrier concentration

- <sup>5</sup> were estimated from the transfer characteristics. The average transconductance was estimated to be between 0.9 and 14.3 nS; the electron mobility ranged from 3.3 to 52.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, the subthreshold swing ranged from 83.5 to 248.8 mV dec<sup>-1</sup>, and the electron carrier concentration ranged from  $1.5 \times 10^{17}$  to  $1.1 \times 10^{18}$

- <sup>10</sup> e cm<sup>-3</sup> with an increasing doping concentration (SiH<sub>4</sub>/PH<sub>3</sub>gas ratio changing from 6,000:1 to 3,000:1). Additionally, the ON current reduced from  $10^{-7}$  to  $10^{-9}$  A when the electron carrier concentration was reduced by reducing the doping concentration. A similar approach was applied to the p-type regions of the p-n Si

- <sup>15</sup> NW FETs. The  $I_{ds}-V_g$  characteristics of several p-type regions of the p-n Si NW FETs at different doping concentrations were obtained by sweeping the gate voltage continuously from +5 to – 5 V. The positive threshold voltage shifted negatively from approximately +4 V to close to 1.5 V as the doping concentration

- <sup>20</sup> was reduced by varying the SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub> gas ratio. The average transconductance was estimated to be between 6.0 and 58.3 nS; the hole mobility ranged from 22.3 to 215.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, the subthreshold swing ranged from 108.4 to 217.9 mV dec<sup>-1</sup>, and the hole carrier concentration ranged from  $4.5 \times 10^{17}$  to  $1.2 \times 10^{18}$  h

- $_{25}$  cm<sup>-3</sup>withan increasing doping concentration (SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub>gas ratio changing from 6,500:1 to 3,500:1). The ON current also increased from ~10<sup>-9</sup> to 10<sup>-7</sup> A (See Table S1 in the Supplementary Information). Note that the NW diameter did not

vary with the doping concentration in either the p- or n-type <sup>30</sup> regions.

A positive shift of the knee voltage of the p-n junction diode was also observed in this study, as shown in Fig. 3c. The knee voltage shifted from 0.15 to 0.8 V when the p-type region dopant was reduced (SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub> gas ratio was changed from 3,500:1 to <sup>35</sup> 6,500:1) and when the n-type region dopant was maintained at a 4,500:1 SiH<sub>4</sub>/PH<sub>3</sub> gas ratio. The positive shift of the knee voltage is a result of the reduction in the carrier concentration in the ptype region that occurs when the doping concentration is reduced. This leads to a wider depletion region, so a higher forward <sup>40</sup> voltage is required to overcome the barrier potential.

A schematic diagram of a simplified depletion model for the n-type region of Si NW FETs with different doping concentrations at a constant negative gate voltage was proposed by Van et al.<sup>26</sup> On the basis of the work of Hong et al.,<sup>28</sup> the 45 electron carrier concentration  $(n_e)$  was calculated using the equation  $n_e = C_{ox}(V_g - V_{th})/e\pi r^2 L$ , where  $C_{ox}$  is the gate oxide capacitance, L is the NW conducting channel length, and r is the NW radius. When the gate voltage is 0 V, this equation reveals that the threshold voltage of the n-type region of the p-n Si NW 50 FETs is proportional to the carrier concentration. Furthermore, at a constant negative gate voltage, the lower electron density easily induces full depletion within the NW. Therefore, reducing the doping concentration leads to fewer electrons in the conducting n-type channel of the p-n Si NW FETs, resulting in reduced 55 conductance and a positive shift in the threshold voltage. However, further reductions in the threshold voltage also degrade the performance (conductivity, transconductance, mobility, and

$I_{ON}/I_{OFF}$  ratio) of the FET. The transport properties of the n- and p-type FETs that make up a CMOS inverter must be compatible. Further, to maintain a sufficient  $I_{ON}/I_{OFF}$  ratio exceeding 10<sup>5</sup> and to achieve a high inverter gain in CMOS inverter devices based <sup>5</sup> on p-n Si NWs, the doping concentration was optimized at a 4,500:1 SiH<sub>4</sub>/PH<sub>3</sub> gas ratio, yielding a threshold voltage of approximately -2 V. A similar approach was applied to the ptype region of the p-n Si NW FETs; the optimized doping concentration was achieved at a 5,500:1 SiH<sub>4</sub>/B<sub>2</sub>H<sub>6</sub> ratio, <sup>10</sup> resulting in a threshold voltage of ~2.5 V. V. The field-effect electron mobility ( $\mu_e$ ) and resistivity ( $\rho$ ) for the p-n Si NWs were calculated from four-probe measurements and found to be 39.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 0.18  $\Omega$ cm, respectively (Fig. S2c in the Supporting Information). The electron carrier concentration ( $n_e$ ) was calculated to be 6.0 ×  $10^{17}$  e cm<sup>-3</sup> using the equation  $n_e = C_{\alpha x} V_{th} / e\pi r^2 L$ .<sup>27</sup> The subthreshold swing, given by  $S = \log[dV_g/d(\log I_{ds})]$ , was 40 estimated to be 181.9 V dec<sup>-1</sup>. The same calculation method is applicable to the p-type regions of the p-n Si NW FETs. A  $V_{th}$  of 2.5 V,  $g_m$  of 142.4 nS, and field-effect hole mobility ( $\mu_h$ ) of 52.6

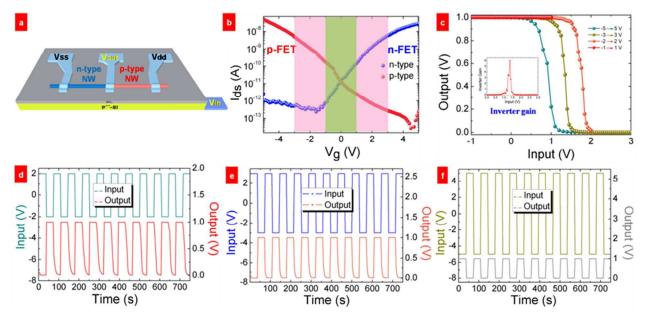

**Fig. 5** CMOS inverter based on axially doped p-n Si NW FETs, and its electrical properties. (a) Schematic view of the back-gate inverter device. (b)  $I_{ds}-V_g$  transfer characteristics of p- and n-type regions of the axial p-n Si NW FETs. (c)  $V_{in}-V_{out}$  inverter characteristics. Inset shows the inverter gain. Dynamic response of the inverter to square-wave input pulses of (d) -2 and 2 V, (e) -3 and 3 V, and (f) -5 and 5 V, where  $V_{dd}$  is set to 1 V.

and  $I_{ds} - V_{ds}$  output The  $I_{ds}-V_g$  transfer characteristics characteristics of the p-n Si NW FETs were measured, as shown in Fig. 4. Figure 4b shows the drain current versus the drainsource voltage  $(I_{ds}-V_{ds})$  curves for the n-type region of the p-n Si 15 NW FETs. The conductance of the NW increased monotonically as the gate potential increased from -5 V to +5 V, exhibiting typical n-type Si NW FET behaviour. Figure 4a shows the drain current versus gate-source voltage  $(I_{ds}-V_g)$  curves for the n-type region obtained by sweeping the gate voltage continuously from 20-5 V to 5 V at a drain voltage ranging from 0 to 1 V. The transconductance  $(g_m)$  and field-effect electron mobility  $(\mu_e)$  of the back-gate p-n Si NW FETs were determined from the  $I_{ds}$ - $V_g$  curves using the following equations:  $g_m = dI_{ds}/dV_g$  and  $\mu_e =$  $g_m L^2/C_{ox} V_{ds}^{31}$  The gate oxide capacitance ( $C_{ox}$ ) of a cylindrical <sup>25</sup> wire on a planar substrate can be estimated as  $C_{ox} = 2\pi \varepsilon_r \varepsilon_0 L/\cos h^2$  $(1 + t_{ox}/r)$  using a relative dielectric constant ( $\varepsilon_r$ ) of 3.9, a  $SiO_2$  gate dielectric layer thickness ( $t_{ox}$ ) of 100 nm, a NW conducting channel length (L) of approximately 3.5 µm, and a NW radius (r) of approximately 25 nm. For the n-type region of 30 the p-n Si NW FETs on a SiO<sub>2</sub>/Si substrate, a threshold voltage

$(V_{th})$  of -2 V and a transconductance  $(g_m)$  of 108.2 nS were extrapolated from the linear region of the  $I_{ds}-V_g$  curve at  $V_{ds} = 1$

cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> were calculated from the plots in Fig. 4c,d, and *ρ* was estimated to be 0.07Ωcm from four-probe measurements (Fig. 45 S2d in the Supporting Information). The hole carrier concentration ( $n_h$ ) was estimated to be 7.5 × 10<sup>17</sup> h cm<sup>-3</sup> using the equation  $n_h = C_{ox}V_{th}/q\pi r^2 L$ .<sup>32</sup> The subthreshold swing (*S*) was approximately 177.9 mV dec<sup>-1</sup>. The subthreshold swings of the n-and p-type regions of the p-n Si NW FETs are small enough for 10w-power-consumption devices. The electrical characteristics of the p-n Si NW FETs in this study and other FETs made from single p-type and n-type Si NWs reported elsewhere are summarized in Table S2 and S3 in the supplementary information, respectively.

The input-output characteristics of a CMOS inverter based on single p-n Si NW FETs were measured in a FET device with three top electrodes and a back gate, as shown in the schematic illustration in Fig. 5a. The  $I_{ds}$ - $V_g$  transfer characteristics of the pn Si NW FETs are shown in Fig. 5b. The input-output 60 characteristics for a supply voltage ( $V_{dd}$ ) of 1 V, with the input voltage ( $V_{in}$ ) swept from -1 to 1 V, -2 to 2 V, -3 to 3 V, and -5 to 5 V, are shown in Fig. 5c. Owing to the differences in the threshold voltages and conduction states of the p- and n-type regions of the p-n Si NW FETs, the input voltage was swept through different ranges. When the input voltage was swept from -3 to 3 V, sharp switching output swings were observed, which correspond to large inverter gains  $(dV_{out}/dV_{in})$  of approximately 6 (inset of Fig. 5c). The key advantage of the NW CMOS inverter

- s is the ultralow low consumption of static power owing to the small current flow from  $V_{dd}$  to the ground. This is irrespective of whether the input voltage is low and the n-type region of the p-n Si NW FET is OFF, or the input voltage is high and the p-type region of the p-n Si NW FET is OFF. The static current is less

- <sup>10</sup> than 0.3 pA at  $V_{dd} = 1$  V when  $V_{in}$  is 0 or 1 V; thus, the static power dissipation is less than 0.3 pW. The dynamic responses of the inverter to square-wave input signals at -2 and 2 V, -3 and 3 V, and -5 and 5 V, all at a frequency of 0.02 Hz and  $V_{dd} = 1$  V, are shown in Fig. 5d,e, and f, respectively. The logic NOT

- $_{15}$  function output voltage stayed close to 0 and 1 V when the input pulse voltages were 3 and –3 V, respectively.

#### 4. Conclusions

A simple method of synthesizing highly ordered axially doped pand n-type regions on a single Si NW was demonstrated, where

- <sup>20</sup> the transport properties of each region can be modulated by controlling the doping concentration. The synthesis and removal of the radial oxide layer were optimized. Using single axially doped p-n Si NWs as conducting channels, p-n junction diodes and CMOS inverters were selectively fabricated. The optimized

- <sup>25</sup> doping concentrations were determined to be a 4,500:1 silane (SiH<sub>4</sub>)/phosphine (PH<sub>3</sub>) ratio with a threshold voltage of -2 V for the n-type region, and a 5,500:1 silane (SiH<sub>4</sub>)/diborane (B<sub>2</sub>H<sub>6</sub>) ratio with a threshold voltage of 2.5 V for the p-type region of the p-n Si NW FET, all while maintaining a sufficient  $I_{ON}/I_{OFF}$  ratio

- <sup>30</sup> exceeding  $10^5$ . Therefore, the axial p-n Si NW can be used as a conducting channel in the CMOS inverter. The device performance was carefully characterized in terms of the electrical transport and inverter input–output characteristics. The inverter has a low operating voltage of approximately  $\pm 3$  V, resulting in inverter devices devices using the electrical transport.

- <sup>35</sup> inverter devices with extremely low power consumption. The results imply that such p-n Si NWs show promise as nextgeneration building blocks for high-performance, high-density diodes, as well as for logic circuits such as NOT, NOR, NAND, and SRAM for use in flexible electronic applications.

#### Acknowledgements

This work was supported by the Center for BioNano Health-Guard funded by the Ministry of Science, ICT & Future Planning (MSIP) of Korea as a Global Frontier Project 45 (HGUARD\_2013M3A6B2) and the National Research Foundation of Korea grant funded by the Korean government

(NRF-2014R1A2A1A11052965).

#### Notes and references

[\*] Prof. Dae Joon Kang, Ngoc Huynh Van<sup>†</sup>

<sup>50</sup> <sup>1</sup>Department of Physics, Sungkyunkwan University, 2066, Seobu-ro, Jangan-gu, Suwon 16419, Republic of Korea.

Jae-Hyun Lee<sup>†</sup>, Prof. Dongmok Whang

<sup>2</sup>School of Advanced Materials Science and Engineering, SKKU <sup>55</sup> Advanced Institute of Nanotechnology, Sungkyunkwan

- University, 2066, Seobu-ro, Jangan-gu, Suwon 16419, Republic of Korea.

- † These authors contributed equally to this work

- \*E-mail address:djkang@skku.edu

- 60 Tel.: +82-31-290-5906; Fax: +82-31-290-5947

- F. M. Wanlass, C. T. Sah, International Solid State Circuits Conference Digest of Technical Papers, 1963,32. DOI: 10.1109/ISSCC.1963.1157450.

- <sup>65</sup> 2 S. N. Cha, J. E. Jang, Y. Choi, G. A. J. Amaratunga, G. W. Ho, M. E. Welland, D. G. Hasko, D.-J. Kang, J. M. Kim, *Appl. Phys. Lett.*, 2006,**89**, 263102.

- 3 J. Xiang, W. Lu, Y. Hu, Y. Wu, H. Yan, C. M. Lieber, *Nature*, 2006,441, 489.

- 70 4 Y. Cui, Z. Zhong, D. Wang, W. U. Wang, C. M. Lieber, *Nano Lett.*, 2003,3, 149.

- 5 P.-C. Chang, Z. Fan, C.-J. Chien, D. Stichtenoth, C. Ronning, J. G. Lu, *Appl. Phys. Lett.*, 2006,89, 133113.

- 6 J. Appenzeller, J. Knoch, M. T. Björk, H. Riel, H. Schmid, 75 W. Riess, *IEEE Trans. Electron Devices*, 2008,**55**, 2827.

- J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy and R. Murphy, *Nat Nano*, 2010, 5, 225.

- 80 8 A. M. Ionescu, Nat. Nano., 2010,5, 178.

- 9 F. Schwierz, Nat. Nano., 2010,5, 487.

- 10 T. Palacios, Nat. Nano., 2011,6, 464

- 11 J. Svensson, N. Lindahl, H. Yun, M. Seo, D. Midtvedt, Y. Tarakanov, N. Lindvall, O. Nerushev, J. Kinaret, S. Lee and E. E. B. Campbell, *Nano Lett.*, 2011,11, 3569

- E. E. B. Campbell, *Nano Lett.*, 2011,11, 3569

A. D. Franklin, Z. Chen, *Nat. Nano.*, 2010,5, 858.

- 13 Y. Cui, C. M. Lieber, Science, 2001,291, 851.

- 14 T. W. Koo, D. S. Kim, J. H. Lee, Y. C. Jung, J. W. Lee, Y. S.

Yu, S. W. Hwang, D. Whang, *J. Phys. Chem. C*, 2011,115, 23552.

- 15 A. D. Mohite, D. E. Perea, S. Singh, S. A. Dayeh, I. H. Campbell, S. T. Picraux and H. Htoon, *Nano Lett.*, 2012, 12, 1965.

- 16 T. J. Kempa, B. Tian, D. R. Kim, H. Jinsong, Z. Xiaolin and

- 95 C. M. Lieber, Nano Lett., 2008,8, 3456.

- 17 C. Yang, C. J. Barrelet, F. Capasso, C. M. Lieber, *Nano Lett.*, 2006,6, 2929.

- 18 A. L. Vallett, S. Minassian, S. Datta, J. M. Redwing, T. S. Mayer, *Device Research Conference*,2010,273. DOI: 10.1109/DRC.2010.5551962.

- 19 D. Wang, B. A. Sheriff, J. R. Heath, Small, 2006,2, 1153.

- 20 G. Jo, W. K. Hong, J. I. Sohn, M. Jo, J. Shin, M. E. Weiland, H. Hwang, K. E. Ceckeler and T. Lee, *Adv. Mater.*, 2009,21, 2156.

- <sup>105</sup> 21 Z. Jiang, Q. Qing, P. Xie, R. Gao and C. M. Lieber, *Nano Lett.*, 2012, **12**, 1711-1716.

- 22 A. W. Dey, J. Svensson, B. M. Borg, M. Ek and L.-E. Wernersson, *Nano Lett.*, 2012, **12**, 5593-5597.

- 23 W. Jin, K. Zhang, Z. Gao, Y. Li, L. Yao, Y. Wang and L.

<sup>110</sup> Dai, *ACS Appl. Mater. Inter.*, 2015, 7, 13131-13136.

- 24 C. Celle, A. Carella, D. Mariolle, N. Chevalier, E. Rouviere and J.-P. Simonato, *Nanoscale*, 2010, **2**, 677-680.

- 25 E.-A. Chung, J. Koo, M. Lee, D.-Y. Jeong and S. Kim, *Small*, 2009, **5**, 1821-1824.

#### Nanoscale

- 26 N. H. Van, J. H. Lee, J. I. Sohn, S. N. Cha, D. Whang, J. M. Kim, D. J. Kang, *Nanoscale*, 2014,6, 5479.

- P. Woojin, H. Woong-Ki, J. Gunho, W. Gunuk, C. Minhyeok, M. Jongsun, K. Yung Ho and L. Takhee,

*Nanotechnology*, 2009, 20, 475702.

- 28 W.-K. Hong, J. I. Sohn, D.-K. Hwang, S.-S. Kwon, G. Jo, S. Song, S.-M. Kim, H.-J. Ko, S.-J. Park, M. E. Welland and T. Lee, *Nano Lett.*, 2008,8, 950.

- G. Jo, W. K. Hong, J. Maeng, M. Choe, W. Park and T. Lee,

*Appl. Phys. Lett.*, 2009,94, 173118.

- 30 Y. T. Lee, J. K. Kim, R. Ha, H.-J. Choi, S. Im, *Appl. Phys. Lett.*, 2011,99,153507.

- 31 L. Liao, H. J. Fan, B. Yan, Z. Zhang, L. L. Chen, B. S. Li, G. Z. Xing, Z. X. Shen, T. Wu, X. W. Sun, J. Wang, T. Yu, *ACS Nano*, 2009,3, 700.

- 32 J. Goldberger, D. J. Sirbuly, M. Law, P. Yang, *J. Phys. Chem. B*, 2005,109, 9.