# **RSC Advances**

View Article Online

View Journal | View Issue

## PAPER

Check for updates

Cite this: RSC Adv., 2017, 7, 52517

Received 20th September 2017 Accepted 8th November 2017

DOI: 10.1039/c7ra10448k

rsc.li/rsc-advances

### Introduction

## Tuning the electrical performance and bias stability of a semiconducting SWCNT thin film transistor with an atomic layer deposited $AIZrO_x$ composite

Jun Li,<sup>ab</sup> Chuan-Xin Huang<sup>a</sup> and Jian-Hua Zhang<sup>b</sup>\*<sup>b</sup>

Solution-processed semiconducting single-walled carbon nanotube (s-SWCNT) thin film transistors (TFTs) based on different atomic layer deposited AlZrO<sub>x</sub> insulators are fabricated and characterized. It is found that increasing the Al concentration in the AlZrO<sub>x</sub> insulator can reduce leakage current and decrease the surface roughness of the AlZrO<sub>x</sub> insulator. Compared with the device with a ZrO<sub>2</sub> insulator, the electrical performance, including subthreshold swing,  $I_{on}/I_{off}$  and hysteresis, and negative bias stability of s-SWCNT TFTs with the AlZrO<sub>x</sub> insulator has been significantly improved. The s-SWCNT TFT based on AlZrO<sub>x</sub> with a ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> cycle ratio of 1/2 reveals a superior electrical performance with an average mobility of 35.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a high on/off ratio of  $3.7 \times 10^5$ , a low subthreshold swing of 0.09, a small hysteresis of 0.1 V, and a small threshold voltage shift of 1.62 V under a negative bias stress of -3 V for 1800 s. The improvement of electrical performance and stability for the s-SWCNT TFT with the AlZrO<sub>x</sub> insulator is attributed to the smooth surface and less AlZrO<sub>x</sub>/s-SWCNT interface traps. Our results suggest that using a AlZrO<sub>x</sub> film as a gate insulator can be a useful technique to achieve high performance and more reliable solution-processed s-SWCNT TFTs.

Single-walled carbon nanotube (SWCNT) thin film transistors (TFTs) have shown potential in the next generation flexible electronic devices due to their high carrier mobility, high chemical stability, transparency and excellent mechanical properties.1-3 However, conventional SWCNTs contain both metallic and semiconducting SWCNTs, which results in a poor on/off current ratio and high off state current.4-8 In order to improve the on/off current ratio, solution-processed preseparated high-purity semiconducting SWCNTs were recently reported for high performance TFTs. Selective removal of metallic CNTs via electrical breakdown has been studied to increase the on/off current ratio. However, these methods cause serious destruction of the remaining nanotubes in the networks.9-11 In order to achieve low-cost fabrication, solution processed semiconducting SWCNTs have been used for application in transistors. Many methods, such as gradient ultracentrifugation,<sup>12,13</sup> gel chromatography,<sup>14,15</sup> and selective extraction by conjugated polymers,16,17 have demonstrated the effective isolation of semiconducting SWCNTs. Despite the separation of metallic and semiconducting SWCNTs, the choice

of gate dielectric is still a key issue in electrical improvement of semiconducting SWCNT TFTs because the electrical properties of SWCNT-TFTs are strongly dependent on the surface conditions, dielectric constant and leakage current of the dielectric layer. In previous works, thermally grown SiO<sub>2</sub> gate insulator is frequently studied for semiconducting SWCNT TFT. However, the process temperature and low dielectric constant of thermally grown SiO<sub>2</sub> insulator is difficult to require the demand of high performance and flexible SWCNT TFT.18 High k materials, such as ZrO<sub>2</sub>,<sup>19</sup> HfO<sub>2</sub>,<sup>20</sup> have been prepared for high performance SWCNT TFT. Although ZrO<sub>2</sub> shows a high permittivity of 20-25, it suffers from its high leakage current due to a narrow band gap and existing oxygen vacancies. To address this disadvantage, cation doping is considered as a feasible method to improve band gap and suppress oxygen vacancies of ZrO<sub>2</sub>. Recently, yttrium-scandium oxide high-k dielectric is deposited by a solution process for TFT application.<sup>21</sup> Sputtered amorphous strontium titanate film can be used as gate insulator of low-voltage TFTs.<sup>22</sup> Furthermore, Al<sub>2</sub>O<sub>3</sub> is a promising gate dielectric material because of its amorphous structure, lowleakage current, acceptable dielectric constant (6.5-9), and wide band gap (5.6-7.8 eV).23 Combining both advantages of  $ZrO_2$  and  $Al_2O_3$ , it is expected to develop a novel dielectric material AlZrO<sub>r</sub> to meet the requirement of high performance semiconducting SWCNT TFTs. Compared to other deposition methods, atomic layer deposition (ALD) is capable of producing high quality conformal film with control of the thickness and composition of the films at the atomic level.<sup>24</sup> Ultimately, AlZrO<sub>x</sub>

<sup>&</sup>quot;School of Material Science and Engineering, Shanghai University, Jiading, Shanghai 201800, People's Republic of China

<sup>&</sup>lt;sup>b</sup>Key Laboratory of Advanced Display and System Applications, Ministry of Education, Shanghai University, Shanghai 200072, People's Republic of China. E-mail: jhzhang\_li@163.com

gate dielectric with high dielectric constant and low leakage current can be optimized by tuning the Al content.

In the work, AlZrO<sub>x</sub> high-k gate insulators with different Al contents are firstly prepared and semiconducting SWCNT TFTs with different AlZrO<sub>x</sub> insulators were fabricated. The influence of Al content on the electrical performance, structure, and surface topography of AlZrO<sub>x</sub> insulators are investigated. The electrical performance and temperature stress stability of SWCNT TFTs with different AlZrO<sub>x</sub> insulators are analyzed. The work aims to supply a facile strategy to enhance performance and bias stability of semiconducting SWCNT thin film transistor with atomic layer deposited AlZrO<sub>x</sub> composite.

### Experimental

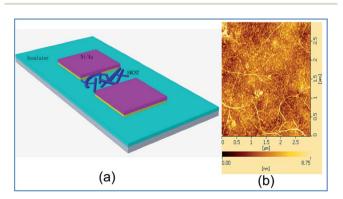

The bottom gate top-contact-type TFTs were fabricated on the highly-doped Si substrate with  $ZrO_2$  and  $AlZrO_x$  thin films grown by atom layer deposition as gate insulators. The structure of device is shown in Fig. 1(a). During deposition process, precursors for Zr, Al and O were Tetrakis dimethyl amino zirconium (TDMAZr), Al(CH<sub>3</sub>)<sub>3</sub> (TMA), and H<sub>2</sub>O, respectively. TDMAZr and TMA precursors are purchased from Jiangsu Fu Na Electronic Technology Co., Ltd (China) and Air Liquid Holding Co. Ltd (France). The deposition temperature is about 250 °C. Typical pulsing sequences during ALD process are 1/5/3/5 s (TDMAZr/Ar purge/H<sub>2</sub>O/Ar purge) and 1/4/2/5 s (TMA/Ar purge/ H<sub>2</sub>O/Ar purge) for the growth of ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> film, respectively. The Al doping concentration in the  $AlZrO_x$  film was controlled by adjusting the cycle ratio of the Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub> processes. The cycle ratio of ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> are 2/1, 1/1, and 1/2 for  $AlZrO_{x-1}$ ,  $AlZrO_{x-2}$ , and  $AlZrO_{x-3}$ , respectively. The thickness of all AlZrO<sub>x</sub> films was controlled by the total deposition cycles and fixed at 170 nm. For the Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub> film, the overall reactions between the precursors and the surface can be shown:25,26

$$2\mathrm{Al}(\mathrm{CH}_3)_3 + 3\mathrm{H}_2\mathrm{O} \to \mathrm{Al}_2\mathrm{O}_3 + 3\mathrm{CH}_4 \tag{1}$$

$$Zr(N(CH_3)_2)_4 + 2H_2O \rightarrow ZrO_2 + 4H(N(CH_3)_2)$$

(2)

Fig. 1 (a) Schematic structure of Semiconducting SWCNT thin film transistors. (b) The surface morphology of the semiconducting SWCNTs by AFM.

This article is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported Licence. pen Access Article. Published on 13 November 2017. Downloaded on 8/20/2024 11:54:39 AM

The Ni (10 nm)/Au (90 nm) source and drain electrodes were patterned onto the Si/AlZrO<sub>x</sub> wafer by a photolithography process with the channel width (*W*) of 20 µm and channel length (*L*) of 10 µm. Next, the well-sonicated 99.9% semi-SWCNTs (Nanointegris, Arc discharge nanotube, average diameter range of 1.4 nm and average length of 1 µm) precursor solution was drop-casted onto the channel region as the active material of p-channel transistors with the solution concentration of 0.1 mg mL<sup>-1</sup> and the volume of 20 µL at room temperature. The semiconducting SWCNTs were enriched by polymer extraction, so the channel region was cleaned by toluene to remove the polymer. The surface morphology of the semiconducting SWCNTs is shown in Fig. 1(b).

The thickness of thin film was measured by the alpha step (Alpha-Step IO). The electrical characteristics of semi-SWCNTs TFTs were measured using Agilent E3647A Dual output DC power supply and Keithley 6485 Picoammeter. The capacitance characteristics were measured by Agilent E4980A LRC meter. The surface morphology of thin films was investigated using atomic force microscopy (SII NanoTechnology SPI 4000) with tapping mode. The roughness parameters are as measured over  $1.5 \times 1.5 \ \mu\text{m}^2$ , and evaluated using the software supplied with the instrument. The structure of AlZrO<sub>x</sub> thin films was measured by grazing incidence X-ray diffraction (GIXRD) scans using Cu Ka radiation. The X-ray source was composed of a sealed X-ray tube, a multilayer monochromator able to select a parallel beam of Cu Ka radiation and a system of crossed slits defining a beam of appropriate size. GIXRD spectra were collected on a position sensitive detector (Inel CPS120). The angle of incidence  $\omega = 0.5^{\circ}$  was chosen as not widely exceeding the critical angle for total external reflection of  $AIZrO_x$ . The chemical bonding states of films were carried out with the X-ray photoelectron spectroscopy (XPS) (Thermo-ESCALAB250XL)) in ultrahigh vacuum (UHV).

### Results and discussion

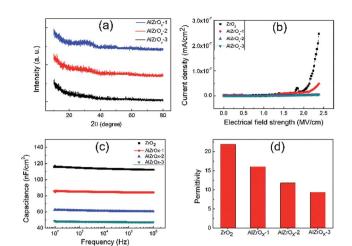

Fig. 2(a) shows the GIXRD patterns of  $AIZrO_x$  films with different Al contents. In the previous work,<sup>27</sup> it is verified that ZrO<sub>2</sub> film shows a crystalline structure with a sharp diffraction peak of  $35.2^{\circ}$ . When Al content is doped into  $ZrO_2$  film, diffraction peak is not observed in the XRD patterns. It suggests that AlZrO<sub>x</sub> film shows the amorphous nature. The crystallization-to-amorphous transition is achieved by adding a suitable dopant, because the original bond structure order is distorted.28 In addition, the amorphous AlZrO<sub>r</sub> film is suitable to prepare large-size and uniform thin films. The insulating properties of AlZrO<sub>x</sub> films with different Al content are characterized by measuring the leakage current versus bias voltage, as shown in Fig. 2(b). The leakage current density of  $ZrO_2$  thin film is  $2.2 \times 10^{-8}$  mA cm<sup>-2</sup> at the electrical field strength of 2 MV cm<sup>-1</sup>. The increased leakage current density is attributed to crystalline grain boundaries of ZrO<sub>2</sub>, which can acts as current leakage paths and defect/ break-down centers.29 For comparison, the leakage current density of  $AIZrO_x$  film is decreased with increasing Al content. The leakage current density of AlZrO<sub>x-3</sub> thin film is  $3.5 \times 10^{-9}$ mA cm<sup>-2</sup> at the electrical field strength of 2 MV cm<sup>-1</sup>. The value

#### Paper

Fig. 2 (a) The GIXRD patterns of  $AIZrO_x$  films with different Al contents. (b) The leakage current *versus* bias voltage of  $AIZrO_x$  films. (c) The areal capacitance of  $AIZrO_x$  film as a function of the frequency. (d) The dielectric permittivity of  $AIZrO_x$  and  $ZrO_2$  film.

is better than that of other high-k insulators by sputtering and solution process.<sup>30,31</sup> To characterize the capacitance properties of AlZrO<sub>x</sub> thin films, a capacitor with the structure of Al/AlZrO<sub>x</sub>/  $p^+$ -Si is prepared. Fig. 2(c) shows the areal capacitance of AlZrO<sub>x</sub> film as a function of the frequency. The capacitance of ZrO<sub>2</sub>, AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub> at a frequency of 1 kHz is 114.0, 84.1, 61.5, and 48.2 nF cm $^{-2}$ , respectively. AlZrO<sub>x</sub> films show a smaller frequency dispersion of the capacitance than  $ZrO_2$  film, indicating that  $AlZrO_x$  films exhibit a low defect density and oxygen vacancies. The similar results were reported by the previous work.<sup>32,33</sup> T. J. Park et al. have also verified that Al doping can reduce the electrical defects in atomic layer deposited HfO<sub>2</sub> films.<sup>34</sup> The dielectric permittivity ( $\varepsilon_r$ ) can be calculated by the following equation:  $C = \varepsilon_0 \varepsilon_r S/d$ , where S is the area, d is the thickness of film. The dielectric permittivity of ZrO<sub>2</sub>, AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub> and AlZrO<sub>x-3</sub> thin film are 21.9, 16.1, 11.8 and 9.7, respectively. The details are shown in Fig. 2(d). The dielectric permittivity of AlZrOx film decreases with increasing Al content. It can be explained by considering the dielectric constants of Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>.

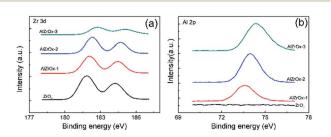

Fig. 3 shows XPS spectra of Zr 3d and Al 2p. All the XPS peaks are calibrated with C 1s peak centered at 284.8 eV. As shown in Fig. 2(a), the peak positions of Zr  $3d_{5/2}$  and Zr  $3d_{3/2}$  for ZrO<sub>2</sub> film are at 181.9 eV and 184.3 eV, respectively. The binding energy of

Fig. 3 XPS spectra of the samples with various Al contents: (a) Zr 3d. (b) Al 2p.

Al 2p of AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub> is 73.6, 74.0, and 74.3 eV, respectively. It is easily seen that the binding energy of Al 2p of all AlZrO<sub>x</sub> films are lower than that of Al<sub>2</sub>O<sub>3</sub> (74.8 eV).<sup>35,36</sup> Both Zr 3d and Al 2p peaks for AlZrO<sub>x</sub> thin films shift to higher binding energy with increasing Al concentration. It is found that the leading contribution is the charge transfer contribution. The charges transfer can be estimated with DFT-LDA calculations. The similar result is previously reported.<sup>37</sup> In addition, it suggests that the AlZrO<sub>x</sub> films mainly consist of Zr– O–Al bonds and present a homogenous structure with negligible phase-separated ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>. The similar result is reported by other groups.<sup>18</sup> The real concentrations of Al are 20.99%, 25.74%, and 30.0% for AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub>, respectively.

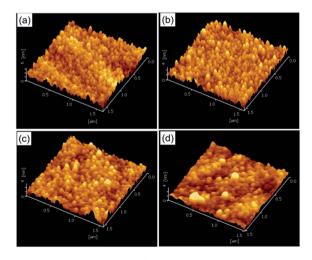

Fig. 4 shows the AFM images of  $A|ZrO_x$  insulators with different Al content. The root mean square (rms) of  $ZrO_2$ ,  $A|ZrO_{x-1}$ ,  $A|ZrO_{x-2}$  and  $A|ZrO_{x-3}$  film is 1.2, 0.86, 0.66 and 0.46 nm, respectively. It suggests that Al doping can reduce rms of  $A|ZrO_x$  film and improve the surface roughness of  $A|ZrO_x$ . In previous XRD analysis, Al doping can suppress the formation of grain boundaries. It is reported that smooth insulator surface could induce much less interface defects and obtain a better insulator–channel interface, which leads to higher mobility of TFTs.<sup>38</sup> Thus, smooth  $A|ZrO_x$  insulator is expected to fabricate high performance semiconducting SWCNT TFTs.

Fig. 5 shows the transfer characteristics and hysteresis of semiconducting SWCNT TFTs with different AlZrO<sub>x</sub> insulators. The transfer characteristic of SWCNT TFTs is measured between gate voltage of 3 V and -3 V with a fixed drain bias voltage of -3 V. The low operating voltage suggests that it is suitable to fabricate electronic devices with low power consumption. The turn-on voltage ( $V_{on}$ ) shows a negative voltage direction shift with the increase in the Al concentration. It is ascribed to the decrease in capacitance with the increase in the Al concentration of AlZrO<sub>x</sub> film. The field mobility ( $\mu$ ) and threshold voltage ( $V_{T}$ ) can be extracted from the following equation<sup>39</sup>

Fig. 4 The AFM images of AlZrO<sub>x</sub> insulators with different Al content. (a)  $ZrO_2$ , (b)  $AlZrO_{x-1}$ , (c)  $AlZrO_{x-2}$ , (d)  $AlZrO_{x-3}$ .

Fig. 5 The transfer characteristics and hysteresis of semiconducting SWCNT TFTs with different gate insulators. (a)  $ZrO_2$ , (b)  $AlZrO_{x-1}$ , (c)  $AlZrO_{x-2}$ , (d)  $AlZrO_{x-3}$ .

$$I_{\rm DS} = (V_{\rm GS} - V_{\rm T})^2 \times W \mu C_{\rm i} / 2L, V_{\rm DS} > V_{\rm GS} - V_{\rm T}$$

(3)

where  $I_{DS}$  is the drain-source current, *W* is the width of channel, *L* is the length of channel,  $V_{GS}$  is the gate voltage, and  $C_i$  is the intrinsic capacitance. For SWCNT transistors, the intrinsic capacitance can be calculated using eqn (4) by considering the effect of electrostatic coupling between semi-SWCNTs.<sup>40</sup>

$$C_{i} = \left\{ \frac{1}{2\pi\epsilon_{0}\epsilon_{i}} \times \ln\left[\frac{A_{0}}{R} \times \frac{\sinh\left(\frac{2\pi t_{i}}{A_{0}}\right)}{\pi}\right] + \frac{1}{C_{Q}} \right\}^{-1} \times A_{0}^{-1} \quad (4)$$

where  $\epsilon_0$  is the vacuum permittivity,  $\epsilon_i$  is dielectric constant of dielectric layer,  $t_i$  is the thickness of dielectric layer,  $C_0 =$  $4 \times 10^{-10}$  F m<sup>-1</sup> is the quantum capacitance of semi-SWCNTs, R = 1 nm is the average radius of semi-SWCNTs and  $\Lambda_0^{-1} = 2.25$ tubes per µm is the linear density of semi-SWCNTs. In our case, the calculated intrinsic capacitance is estimated to be approximately 24.5%, 27.0%, 31.2%, and 29.9% of the gate capacitance based on the parallel plate model, respectively. Consequently, the average intrinsic  $\mu$  of ZrO<sub>2</sub>, AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub> based TFTs are calculated to be 28.7, 30.6, 33.3, and 35.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively. The average intrinsic  $\mu$  of the devices are tested from the total of 25 devices. The results shows a very strong control on the electrical performance of s-SWCNT TFT by controlling the Al concentration in  $AIZrO_x$  insulator. The average mobility improvement of SWCNT TFTs with  $AIZrO_{x-3}$ insulator is attributed to smooth surface and low interface trap states, leading to the reduced probability of carrier scattering. The threshold voltage of the device is reduced from 3.2 to -0.5 V with increasing Al content. The result is attributed to the increased capacitance with increasing Al content. More details are shown in Table 1.

The hysteresis of the device is observed in the  $I_{\text{DS}}$  versus  $V_{\text{GS}}$  characteristics as shown in Fig. 5. The hysteresis of  $\text{AlZrO}_{x-3}$

Table 1

The average electrical performance of SWCNT TFTs with different gate insulators

| Device               | $\mu$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $V_{\rm T}$ (V) | SS (V dec <sup>-1</sup> ) | $I_{\rm op}/I_{\rm off}$ | Hysteresis<br>(V) |

|----------------------|----------------------------------------------------------|-----------------|---------------------------|--------------------------|-------------------|

|                      | ( )                                                      | 1()             | ( )                       | on on                    | ()                |

| $ZrO_2$              | 28.7                                                     | 3.2             | 0.15                      | $1.2	imes 10^4$          | 1.43              |

| $AlZrO_{x-1}$        | 30.6                                                     | 2.3             | 0.12                      | $2.5	imes10^4$           | 1.01              |

| $AlZrO_{x-2}$        | 33.3                                                     | 1.8             | 0.10                      | $8	imes 10^4$            | 0.2               |

| AlZrO <sub>r-3</sub> | 35.2                                                     | -0.5            | 0.09                      | $3.7	imes10^5$           | 0.1               |

based TFT shows a small hysteresis of 0.1 V, which is obviously smaller than that (1.43 V) of  $ZrO_2$  based TFT. Generally, hysteresis in the SWCNT transistor is attributed to trap states in the dielectric or SWCNT/dielectric interface.41 It is reported that hydroxyl groups (-OH) present on the surface of dielectric layer is considered to be interface defects and significant contributors to hysteresis.<sup>42</sup> Upon applying a gate bias of 3 V, the negative charges formed on the surface of gate insulator can be trapped by -OH group. It facilitates the conduction during the forward sweep in gate voltage. Thus, the threshold voltage of the transistor will shift toward the positive direction. Conversely, a negative gate bias discharges -OH groups into their neutral states, thereby reducing the conductivity for hole transport during the reverse sweep. It suggests that Al doping can effectively reduce the trap states in the ZrO<sub>2</sub> and SWCNT/insulator interface. The results also verified the above XRD and XPS analysis. The effect trap density of states  $(N_{trap})$  of semiconducting SWCNT TFTs can be estimated by the following equation41,43

$$SS = dV_{GS}/d(Log I_{DS})$$

(5)

$$SS = \frac{kT \ln 10}{e} \left[ 1 + \frac{e^2}{C_i} N_{trap} \right]$$

(6)

where SS is the subthreshold swing, k is the Boltzmann constant, T is temperature, and  $C_i$  is the intrinsic capacitance. The effective trap density for ZrO<sub>2</sub>, AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub> based TFTs are estimated to be  $4.33 \times 10^{11}$ ,  $2.82 \times 10^{11}$ ,  $1.92 \times 10^{11}$ , and  $1.34 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>, respectively. AlZrO<sub>x-3</sub> based TFTs shows a smaller trap density, which is attributed to smooth surface and less trap in AlZrO<sub>x-3</sub> film. The effective trap density is obviously smaller than that of SWCNT-TFTs with SiO<sub>2</sub> and SiN<sub>x</sub> gate dielectric.<sup>44</sup>

The negative gate bias stability of semiconducting SWCNT TFTs with different AlZrO<sub>x</sub> insulators is evaluated. Fig. 6 shows the transfer characteristics ( $V_{\rm DS} = -3$  V) before and after bias stress at a  $V_{\rm GS}$  of -3 V for 1800 s in ambient air. For all devices, the transfer characteristics shift slightly toward the negative direction with increasing the stress time. The  $V_{\rm T}$  shift ( $\Delta V_{\rm T}$ ) of the device with AlZrO<sub>x</sub> insulator is smaller than that of the device with ZrO<sub>2</sub> insulator under similar stress condition.  $\Delta V_{\rm T}$  of ZrO<sub>2</sub>, AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub> based TFTs for 1800 s stress time is 5.01, 3.24, 2.5, and 1.62 V, respectively. It suggests that the negative bias stability is improved with increasing the Al content in AlZrO<sub>x</sub> insulator. The negative gate bias instabilities of semiconducting SWCNT TFTs are generally considered to be due to the hole trapping at the interface between the

Fig. 6 The negative gate bias stability of semiconducting SWCNT TFTs with different gate insulators. (a)  $ZrO_2$ , (b)  $AlZrO_{x-1}$ , (c)  $AlZrO_{x-2}$ , (d)  $AlZrO_{x-3}$ .

semiconducting SWCNT channel layer and  $ZrAlO_x$  gate insulator or  $ZrAlO_x$  bulk gate insulator. The accumulated hole slowly fills up these trap states under negative gate bias stress. After removal of the stress voltage, the trapped charge can be slowly released again. In addition, the origin of the threshold voltage shift with stress time can be expressed by the stretched exponential model:<sup>45</sup>

$$|\Delta V_{\rm T}| = \Delta V_{\rm T0} \{1 - \exp[-(t/\tau)^{\beta}]\}$$

(7)

where  $\Delta V_{\text{T0}}$  is the saturated threshold voltage at infinite time,  $\beta$  and  $\tau$  are the exponent of the trapping rate and the relaxation time of the trapped charges, respectively. The obtained  $\tau$  values are  $6.59 \times 10^2$ ,  $8.24 \times 10^2$ ,  $1.24 \times 10^3$ , and  $2.63 \times 10^3$  s for semiconducting SWCNT TFT with ZrO<sub>2</sub>, AlZrO<sub>x-1</sub>, AlZrO<sub>x-2</sub>, and AlZrO<sub>x-3</sub>, respectively. It demonstrates that the degradation of AlZrO<sub>x</sub> based TFT is slower than that of ZrO<sub>2</sub>-based TFT under a long-time operation. The long trapping time leads to capturing holes frequently at the gate dielectric or at the interface between the gate insulator and channel. Thus, it results in a small threshold voltage shift at the same stress conditions. Detailed comparison of the previous works has been shown in Table 2. It is easily seen that our SWCNT transistors have a high mobility and good stability.

The impact of temperature stress on the electrical performance of semiconducting SWCNT TFTs is also characterized. Fig. 7 shows the transfer curves of semiconducting SWCNT TFTs with temperature varying from 293 to 353 K. For all of the devices, the on-state current and the mobility are enhanced with increasing temperature. It is reported that temperature dependent measurements of SWCNT TFTs is consistent with thermally activated transport.<sup>52</sup> Thus, the thermally activated drain current can be described by the following relation:  $I_{\rm DS} \propto \exp(-E_a/kT)$ ,

View Article Online RSC Advances

Table 2 Comparison of electrical performance for SWCNT TFTs

| Ref.                                | $\mu$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $V_{\mathrm{T}}\left(\mathrm{V} ight)$ | $I_{\rm on}/I_{\rm off}$ | $\Delta V_{\mathrm{T}} \left( \mathrm{V}  ight) $ (PBS) |

|-------------------------------------|----------------------------------------------------------|----------------------------------------|--------------------------|---------------------------------------------------------|

| SiO <sub>2</sub> /CNT <sup>46</sup> | 15.03                                                    | -0.45                                  | ${\sim}10^5$             | _                                                       |

| SiO <sub>2</sub> /CNT <sup>47</sup> | $\sim 38$                                                | 0-1                                    | ${\sim}10^5$             | _                                                       |

| SiO <sub>2</sub> /CNT <sup>48</sup> | 18                                                       | 0                                      | ${\sim}10^{6}$           | —                                                       |

| Ion-gel/CNT <sup>49</sup>           | >100                                                     | -1.0-1.5                               | 138                      | _                                                       |

| BTO/CNT <sup>50</sup>               | 0.21                                                     | -1.8                                   | ${\sim}10^3$             | _                                                       |

| PV3D3/CNT <sup>51</sup>             | 9.76                                                     | <4V                                    | $3	imes 10^4$            | —                                                       |

| Our work                            | 35.2                                                     | -0.5                                   | $3.7	imes10^5$           | 1.62                                                    |

Fig. 7 The transfer curves of semiconducting SWCNT TFTs with temperature varying from 293 to 353 K. (a)  $ZrO_2$ , (b)  $AlZrO_{x-1}$ , (c)  $AlZrO_{x-2}$ , (d)  $AlZrO_{x-3}$ .

where *T* and  $E_a$  are temperature and activation energy, respectively. At high temperature, polarons are thermally activated to hop between localized states in a faster manner, resulting in high mobility. In addition, the threshold voltage shift of the device under same temperature stress decreases with increasing Al content in the AlZrO<sub>x</sub> insulator. The device with AlZrO<sub>x-3</sub> shows a small threshold voltage shift of 1.18 V under the temperature stress of 353 K. It is reported that the threshold voltage shift is correlated with the total density of states, consisting of the density of states of the bulk channel and interface trap density.<sup>53</sup> Thus, a smaller threshold voltage shift can be attributed to the fact that adding Al into ZrO<sub>2</sub> film can improve the surface roughness and reduce interface trap states. The result is consistent with the previous conclusion.

### Conclusions

In summary,  $AIZrO_x$  films with different Al contents have been successfully prepared by atomic layer deposition. Increasing Al concentration in the  $AIZrO_x$  insulator can reduce leakage current and decrease the surface roughness of  $AIZrO_x$  insulator. AlZrO<sub>x-3</sub> thin film shows a low leakage current density of  $3.5 \times 10^{-9}$  mA cm<sup>-2</sup> at the electrical field strength of 2 MV cm<sup>-1</sup> and a small rms of 0.46 nm. The SWCNT TFT based on AlZrO<sub>x</sub> with AlZrO<sub>x-3</sub> gate insulator exhibits a superior electrical performance with an average mobility of  $35.2 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , a high on/ off ratio of  $3.7 \times 10^5$ , a low subthreshold swing of 0.09, and a little hysteresis of 0.1 V, and a small threshold voltage shift of 1.62 V under negative bias stress of -3 V for 1800 s. The improvement of electrical performance and stability for SWCNT TFT with AlZrO<sub>x</sub> insulator is attributed to the smooth surface and less AlZrO<sub>x</sub>/SWCNT interface trap. It suggests that AlZrO<sub>x</sub> film combining the advantage of ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> is a promising candidate as gate insulator for achieving high performance and more reliable solution-processed semiconducting SWCNT TFTs.

## Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

The authors would like to acknowledge the financial support given by the Natural Science Foundation of China (61774100, 51302165), Shanghai Science and Technology Commission (15JC1402000) and National Key Research and Development Program of China (2016YFB0401105).

## Notes and references

- C. M. Homenick, R. James, G. P. Lopinski, J. Dunford, J. Sun, H. Park, Y. Jung, G. Cho and P. R. L. Malenfant, ACS Appl. Mater. Interfaces, 2016, 8, 27900.

- 2 C. Qiu, Z. Zhang, M. Xiao, Y. Yang, D. Zhong and L. M. Peng, *Science*, 2017, 355, 271.

- 3 C. Cao, J. B. Andrews, A. Kumar and A. D. Franklin, *ACS Nano*, 2016, **10**, 5221.

- 4 B. Kim, S. Jang, M. L. Geier, P. L. Prabhumirashi, M. C. Hersam and A. Dodabalapur, *Appl. Phys. Lett.*, 2014, 104, 062101.

- 5 K. R. Reddy, K. P. Lee, A. I. Gopalan, M. S. Kim, A. M. Showkat and Y. C. Nho, *J. Polym. Sci., Part A: Polym. Chem.*, 2006, **44**, 3355.

- 6 M. U. Khan, K. R. Reddy, T. Snguanwongchai, E. Haque and V. G. Gomes, *Colloid Polym. Sci.*, 2016, **294**, 1599.

- 7 M. Cakici, K. R. Reddy and F. Alonso-Marroquin, *Chem. Eng. J.*, 2017, **309**, 151.

- 8 B. Mortazavi, Carbon, 2017, 118, 25.

- 9 S. J. Kang, C. Kocabas, T. Ozel, M. Shim, N. Pimparkar, M. A. Alam, S. V. Rotkin and J. A. Rogers, *Nat. Nanotechnol.*, 2007, 2, 230.

- 10 B. K. Sarker, N. Kang and S. I. Khondaker, *Nanoscale*, 2014, 6, 4896.

- 11 K. R. Reddy, B. C. Sin, C. H. Yoo, W. Park, K. S. Ryu, J. S. Lee, D. Sohn and Y. Lee, *Scr. Mater.*, 2008, **58**, 1010.

- 12 M. S. Arnold, A. A. Green, J. F. Hulvat, S. I. Stupp and M. C. Hersam, *Nat. Nanotechnol.*, 2006, 1, 60.

- 13 M. Jang, S. Kim, H. Jeong and S. Y. Ju, *Nanotechnology*, 2016, 27, 41LT01.

- 14 B. S. Flavel, K. E. Moore, M. Pfohl, M. M. Kappes and F. Hennrich, *ACS Nano*, 2014, **8**, 1817.

- 15 H. Liu, T. Tanaka and H. Kataura, Nano Lett., 2014, 14, 6237.

- 16 Z. Li, J. Ding, J. Lefebvre and P. R. L. Malenfant, *Org. Electron.*, 2015, **26**, 15.

- 17 T. Lei, X. Chen, G. Pitner, H. S. Philip Wong and Z. Bao, *J. Am. Chem. Soc.*, 2016, **138**, 802.

- 18 R. S. Park, M. M. Shulaker, G. Hills, L. S. Liyanage, S. Lee, A. Tang, S. Mitra and H. S. P. Wong, ACS Nano, 2016, 10, 4599.

- 19 B. Kim, S. Jang, P. L. Prabhumirashi, M. L. Geier, M. C. Hersam and A. Dodabalapur, *Appl. Phys. Lett.*, 2013, 103, 082119.

- 20 C. W. Lee, S. K. R. Pillai, X. N. Luan, Y. L. Wang, C. M. Li and M. B. Chan-Park, *Small*, 2012, 8, 2941.

- 21 W. Hu, B. Frost and R. L. Peterson, J. Phys. D: Appl. Phys., 2016, 49, 115109.

- 22 S. Yadav and S. Ghosh, *ACS Appl. ACS Appl. Mater. Interfaces*, 2016, **8**, 10436.

- 23 D. W. Park, S. Mikael, T. H. Chang, S. Gong and Z. Ma, *Appl. Phys. Lett.*, 2015, **106**, 102106.

- 24 Y. Lee, W. Jeon, Y. Cho, M. H. Lee, S. J. Jeong, J. Park and S. Park, *ACS Nano*, 2016, **10**, 6659.

- 25 Y. Widjaja and C. B. Musgravea, *Appl. Phys. Lett.*, 2002, **80**, 3304.

- 26 J. H. Zhang, H. Zhang, Y. Q. Zheng, M. J. Wei, H. Ding, B. Wei and Z. L. Zhang, *Nanotechnology*, 2017, 28, 044002.

- 27 J. Meyer, H. Schmidt, W. Kowalsky, T. Riedl and A. Kahn, *Appl. Phys. Lett.*, 2010, 96, 243308.

- 28 J. Oh, S. Shin, J. Park, G. Ham and H. Jeon, *Thin Solid Films*, 2016, **599**, 119.

- 29 W. Hu, B. Frost and R. L. Peterson, J. Phys. D: Appl. Phys., 2016, 49, 115109.

- 30 P. Jin, G. He, D. Xiao, J. Gao, M. Liu, J. Lv, Y. Liu, M. Zhang,

P. Wang and Z. Sun, *Ceram. Int.*, 2016, 42, 6761.

- 31 S. S. Jiang, G. He, J. Gao, D. Q. Xiao, P. Jin, W. D. Li, J. G. Lv, M. Liu, Y. M. Liu and Z. Q. Sun, *Ceram. Int.*, 2016, 42, 11640.

- 32 M. D. Morales-Acosta, M. A. Quevedo-López and R. Ramírez-Bon, *Mater. Chem. Phys.*, 2014, **146**, 380.

- 33 A. Bhoolokam, M. Nag, A. Chasin, S. Steudel, J. Genoe, G. Gelinck, G. Groeseneken and P. Heremans, *J. Inf. Disp.*, 2015, 16, 31.

- 34 T. J. Park, J. H. Kim, J. H. Jang, C. K. Lee, K. D. Na, S. Y. Lee, H. S. Jung, M. Kim, S. Han and C. S. Hwang, *Chem. Mater.*, 2010, **22**, 4175.

- 35 X. D. Huang, R. P. Shi, J. K. O. Sin and P. T. Lai, *IEEE Trans. Device Mater. Reliab.*, 2016, 16, 38.

- 36 R. Suri, C. J. Kirkpatrick, D. J. Lichtenwalner and V. Misra, *Appl. Phys. Lett.*, 2010, **96**, 042903.

- 37 M. J. Guittet, J. P. Crocombette and M. Gautier-Soyer, *Phys. Rev. B*, 2001, **63**, 125117.

- 38 L. Zhang, J. Li, X. W. Zhang, X. Y. Jiang and Z. L. Zhang, *Appl. Phys. Lett.*, 2009, **95**, 072112.

- 39 A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. Mcintyre, P. Mceuen, M. Lundstrom and H. J. Dai, *Nat. Mater.*, 2002, 1, 241.

- 40 Q. Cao, M. G. Xia, C. Kocabas, M. Shim, J. A. Rogers and S. V. Rotkin, *Appl. Phys. Lett.*, 2007, **90**, 023516.

- 41 T. J. Ha, D. Kiriya, K. Chen and A. Javey, ACS Appl. Mater. Interfaces, 2014, 6, 8441.

- 42 S. H. Jin, A. E. Islam, T. Kim, J. Kim, M. A. Alam and J. A. Rogers, *Adv. Funct. Mater.*, 2012, 22, 2276.

- 43 J. Li, C. X. Huang, J. H. Zhang, W. Q. Zhu, X. Y. Jiang and Z. L. Zhang, *RSC Adv.*, 2015, 5, 9621.

- 44 T. J. Ha, Electron. Mater. Lett., 2017, 13, 287.

- 45 S. W. Lee, S. Y. Lee, S. C. Lim, Y. D. Kwon, J. S. Yoon, K. Uh and Y. H. Lee, *Appl. Phys. Lett.*, 2012, **101**, 053504.

- 46 X. Cao, F. Wu, C. Lau, Y. Liu, Q. Liu and C. Zhou, *ACS Nano*, 2017, **11**, 2008.

- 47 Z. Li, J. Ding, J. Lefebvre and P. R. L. Malenfant, Org. Electron., 2015, 26, 15.

- 48 J. Y. Jeon and T. J. Ha, *IEEE Trans. Electron Devices*, 2016, 63, 827.

- 49 J. Vaillancourt, H. Zhang, P. Vasinajindakaw, H. Xia, X. Lu, X. Han, D. C. Janzen, W. S. Shih, C. S. Jones, M. Stroder, M. Y. Chen, H. Subbaraman, R. T. Chen, U. Berger and M. Renn, *Appl. Phys. Lett.*, 2008, 93, 243301.

- 50 J. Noh, M. Jung, K. Jung, G. Lee, S. Lim, D. Kim, S. Kim, J. M. Tour and G. Cho, *Org. Electron.*, 2011, **12**, 2185.

- 51 D. Lee, J. Yoon, J. Lee, B. H. Lee, M. L. Seol, H. Bae, S. B. Jeon, H. Seong, S. G. Im, S. J. Choi and Y. K. Choi, *Sci. Rep.*, 2016, 6, 26121.

- 52 D. E. Johnston, M. F. Islam, A. G. Yodh and A. T. Johnson, *Nat. Mater.*, 2005, 4, 589.

- 53 C. X. Huang, J. Li, Y. Z. Fu, J. H. Zhang, X. Y. Jiang and Z. L. Zhang, *Appl. Phys. Lett.*, 2015, **107**, 213504.